CDP1852C

CDP1852C is Byte-Wide Input/Output Port manufactured by GE.

- Part of the CDP1852 comparator family.

- Part of the CDP1852 comparator family.

Features

:

- Static silicon-gate CMOS circuitry

- Parallel B-bit data register and buffer

- Handshaking via service request flip-flop

- Low quiescent and operating power

- Interfaces directly with CDP1BOO-series microprocessors

- Single voltage supply

- Full military temperature range (-55°C to +125°C)

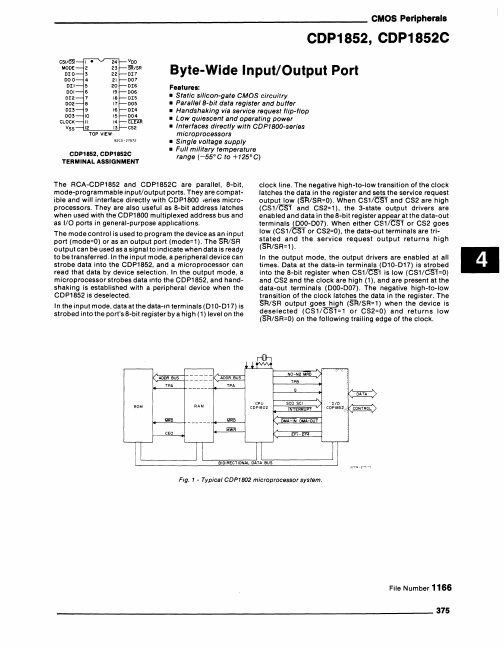

The ACA-CDP1852 and CDP1852C are parallel, 8-bit, mode-programmable input/output ports. They are patible and will interface directly with CDP1800,eries microprocessors. They are also useful as 8-bit address latches when used with the CDP1800 multiplexed address bus and as li D ports in general-purpose applications.

The mode...