CY7C1916CV18

Overview

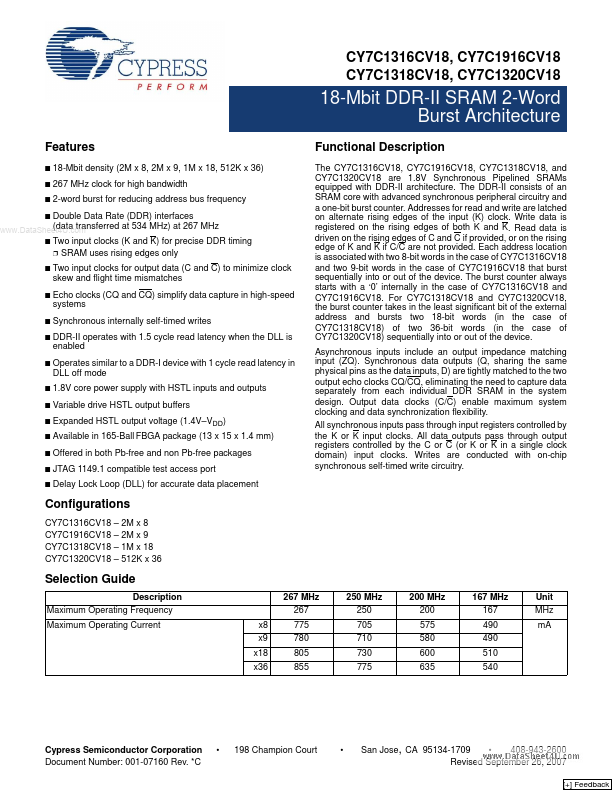

- Functional Description The CY7C1316CV18, CY7C1916CV18, CY7C1318CV18, and CY7C1320CV18 are 1.8V Synchronous Pipelined SRAMs equipped with DDR-II architecture. The DDR-II consists of an SRAM core with advanced synchronous peripheral circuitry and a one-bit burst counter. Addresses for read and write are latched on alternate rising edges of the input (K) clock. Write data is registered on the rising edges of both K and K. Read data is driven on the rising edges of C and C if provided, or on the rising edge of K and K if C/C are not provided. Each address location is associated with two 8-bit words in the case of CY7C1316CV18 and two 9-bit words in the case of CY7C1916CV18 that burst sequentially into or out of the device. The burst counter always starts with a ‘0’ internally in the case of CY7C1316CV18 and CY7C1916CV18. For CY7C1318CV18 and CY7C1320CV18, the burst counter takes in the least significant bit of the external address and bursts two 18-bit words (in the case of CY7C1318CV18) of two 36-bit words (in the case of CY7C1320CV18) sequentially into or out of the device. Asynchronous inputs include an output impedance matching input (ZQ). Synchronous data outputs (Q, sharing the same physical pins as the data inputs, D) are tightly matched to the two output echo clocks CQ/CQ, eliminating the need to capture data separately from each individual DDR SRAM in the system design. Output data clocks (C/C) enable maximum system clocking and data synchronization flexibility. All synchronous inputs pass through input registers controlled by the K or K input clocks. All data outputs pass through output registers controlled by the C or C (or K or K in a single clock domain) input clocks. Writes are conducted with on-chip synchronous self-timed write circuitry. 18-Mbit density (2M x 8, 2M x 9, 1M x 18, 512K x 36) 267 MHz clock for high bandwidt