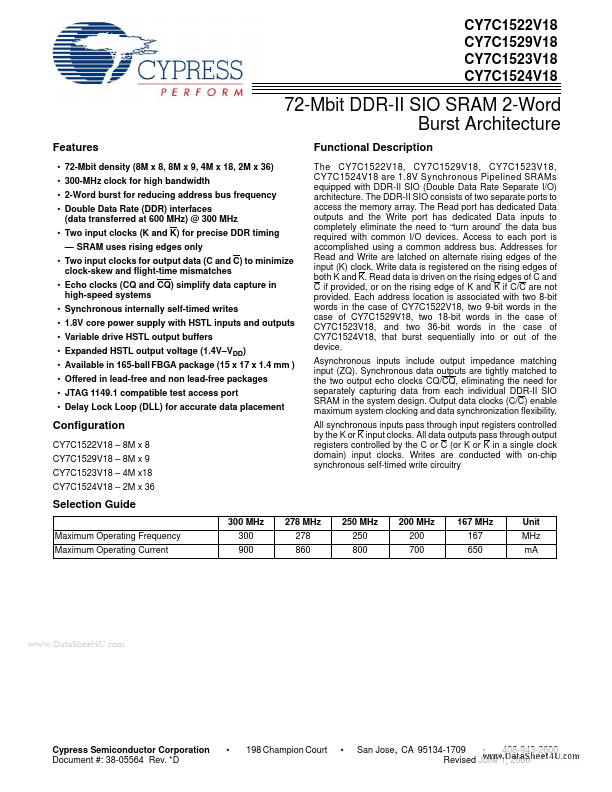

| Part | CY7C1522V18 |

|---|---|

| Description | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| Manufacturer | Cypress |

| Size | 491.53 KB |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CY7C1320AV18 | Cypress | 18-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C25422KV18 | Cypress | 72-Mbit QDR II+ SRAM Two-Word Burst Architecture |

| CY7C2245KV18 | Cypress | 36-Mbit QDR II+ SRAM Four-Word Burst Architecture |