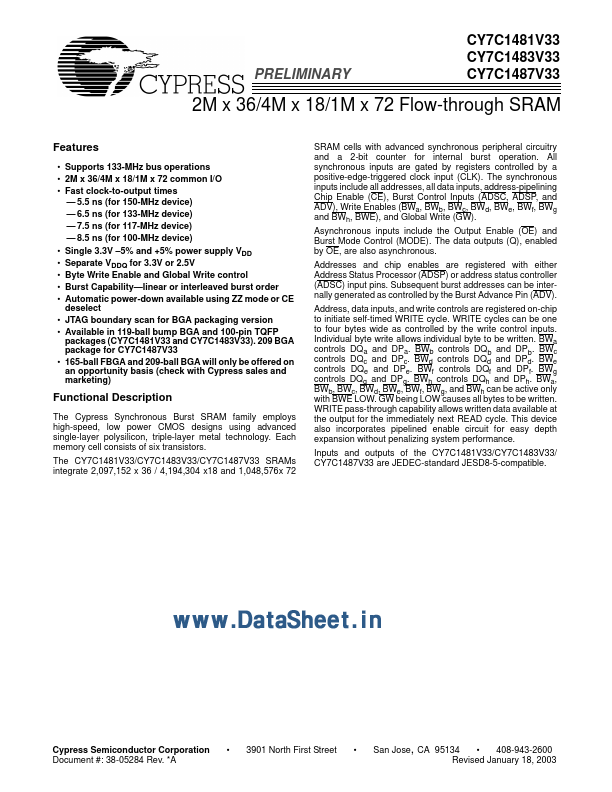

| Part | CY7C1487V33 |

|---|---|

| Description | 2M x 36/4M x 18/1M x 72 Flow-Through SRAM |

| Manufacturer | Cypress |

| Size | 612.36 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| LH52256C-10LL | Sharp Corporation | 256K SRAM |

| HM628512 | Hitachi Semiconductor | 4 M SRAM (512-kword x 8-bit) |

| HY62256A | Hyundai | 32K x 8-Bit CMOS SRAM |