CY7C1347F

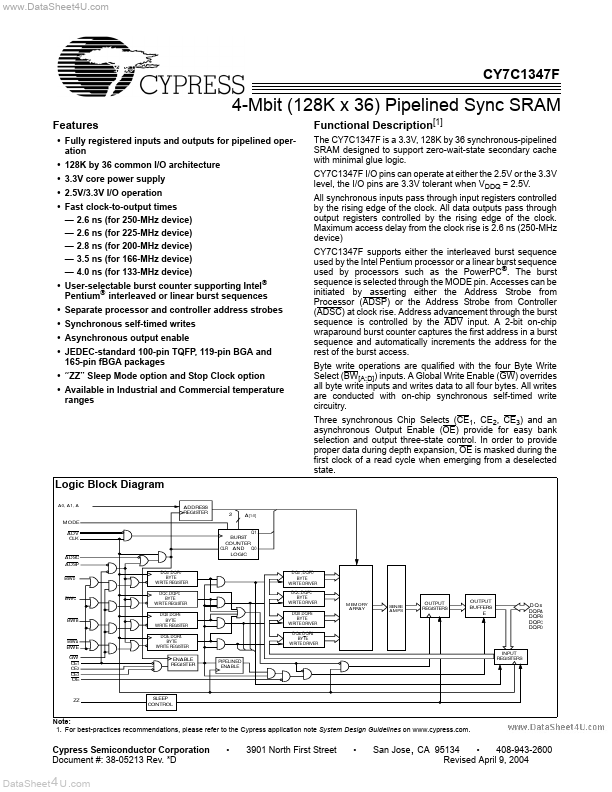

CY7C1347F is 4-Mbit (128K x 36) Pipelined Sync SRAM manufactured by Cypress.

..

4-Mbit (128K x 36) Pipelined Sync SRAM

Features

- Fully registered inputs and outputs for pipelined operation

- 128K by 36 mon I/O architecture

- 3.3V core power supply

- 2.5V/3.3V I/O operation

- Fast clock-to-output times

- 2.6 ns (for 250-MHz device)

- 2.6 ns (for 225-MHz device)

- 2.8 ns (for 200-MHz device)

- 3.5 ns (for 166-MHz device)

- 4.0 ns (for 133-MHz device)

- User-selectable burst counter supporting Intel Pentium interleaved or linear burst sequences

- Separate processor and controller address strobes

- Synchronous self-timed writes

- Asynchronous output enable

- JEDEC-standard 100-pin TQFP, 119-pin BGA and 165-pin fBGA packages

- “ZZ”...