CY7C340 Overview

Key Specifications

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Max Frequency: 18 MHz

Description

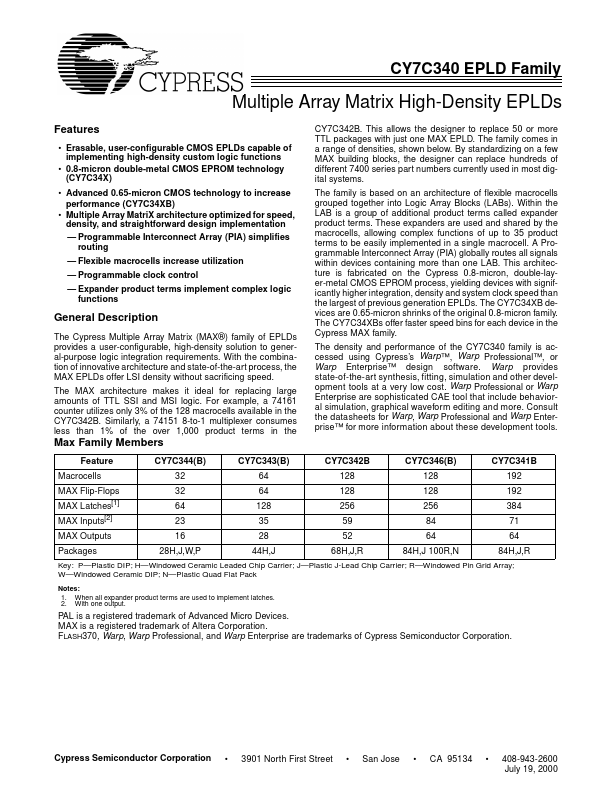

The Cypress Multiple Array Matrix (MAX®) family of EPLDs provides a user-configurable, high-density solution to general-purpose logic integration requirements. With the combination of innovative architecture and state-of-the-art process, the MAX EPLDs offer LSI density without sacrificing speed.

Key Features

- Erasable, user-configurable CMOS EPLDs capable of implementing high-density custom logic functions

- 0.8-micron double-metal CMOS EPROM technology (CY7C34X)

- Advanced 0.65-micron CMOS technology to increase performance (CY7C34XB)

- Multiple Array MatriX architecture optimized for speed, density, and straightforward design implementation

- Programmable Interconnect Array (PIA) simplifies routing