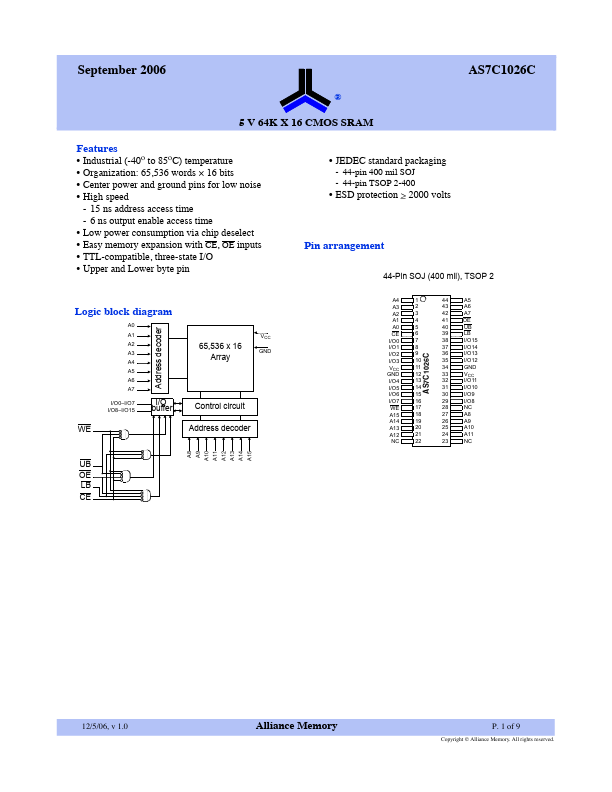

| Part | AS7C1026C |

|---|---|

| Description | 5V 64K x 16 CMOS SRAM |

| Manufacturer | Alliance Semiconductor |

| Size | 287.41 KB |

Pricing from 8.47 USD, available from Newark and Mouser.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Newark | 0 | 160+ : 8.47 USD 250+ : 7.06 USD 500+ : 6.86 USD |

View Offer |

| Mouser | 29 | 1+ : 10.13 USD 10+ : 9.42 USD 50+ : 8.9 USD 100+ : 8.9 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AS7C1025B | Alliance Semiconductor Corporation | 5V 128K x 8 CMOS SRAM |

| AS7C1024B | Alliance Semiconductor Corporation | 5V 1Mb FAST Asynchronous SRAM |