# 3A Ultra Low Dropout Linear Regulator

## General Description

The uP8801S is a 3A ultra low dropout linear regulator specifically designed for motherboard, notebook and graphic card applications. This device works with dual supplies, a control input for the control circuitry and a power input as low as 1.2V for providing current to output. The uP8801S delivers high-current and ultra-low-drop output voltage as low as 0.8V for applications where  $\rm V_{OUT}$  is very close to  $\rm V_{IN}$ .

The uP8801S features comprehensive control and protection functions: a power on reset (POR) circuit for monitoring both control and power inputs for proper operation; an EN input for enabling or disabling the device, a power OK with time delay for indicating the output voltage status, a foldback current limit function, and a thermal shutdown function.

The uP8801S is available in PSOP - 8L or WDFN3x3 - 10L packages with very low thermal resistance.

## Applications

- Desktop PCs, Notebooks, and Workstations

- Graphic Cards

- Low Voltage Logic Supplies

- Microprocessor and Chipset Supplies

- Split Plane Microprocessor Supplies

- Advanced Graphics Cards Supplies

- SoundCards and Auxiliary Power Supplies

- SMPS Post Regulators

# \_\_\_\_\_ Features

- Works with 1.2V~5.5V V<sub>IN</sub>

- Adjustable Output Voltage, Down to 0.8V

- 1.5% Initial Accuracy

- Excellent Line and Load Regulation

- □ 3A Guaranteed Output Current

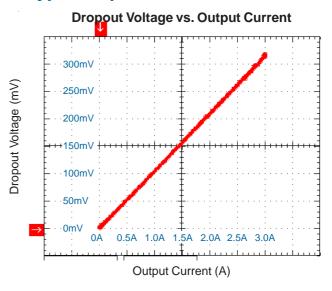

- 300mV @ 3A Dropout Voltage

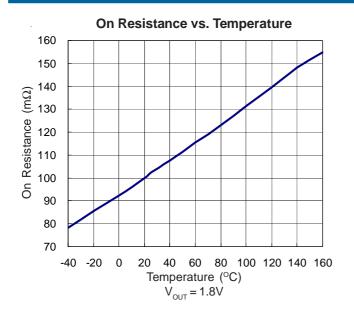

- Very Low On-Resistance

- 100mΩ typical

- V<sub>OUT</sub> Pull Low Resistance when Disabled

- V<sub>ouт</sub> Power OK Signal

- □ Fast Transient Response

- Low External Component Count

- Low Cost and Easy to Use

- Over Current and Over Temperature Protection

- RoHS Compliant and Halogen Free

# Ordering Information

| Order Number | Package     | Top Marking |

|--------------|-------------|-------------|

| uP8801SSW8   | PSOP-8L     | uP8801S     |

| uP8801SDDA   | WDFN3x3-10L | uP8801S     |

#### Note:

- (1) Please check the sample/production availability with uPI representatives.

- (2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

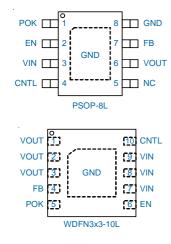

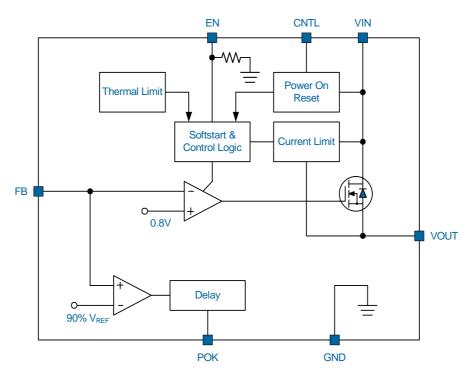

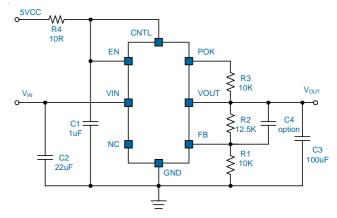

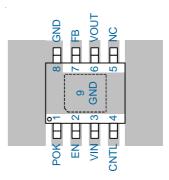

# Pin Configuration & Typical Application Circuit

# Functional Pin Description

| Pin No.     |         |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-------------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SSW8        | SDDA    | Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 1           | 5       | POK  | <b>Power OK Indication.</b> This pin is an open-drain output and is set high impedance once $V_{\text{OUT}}$ reaches 92% of its rating voltage.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

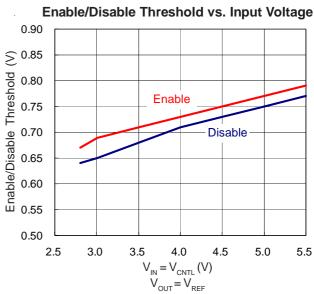

| 2           | 6       | EN   | <b>Enable Input.</b> Pulling this pin below 0.4V turns the regulator off, reducing the quiescent current to a fraction of its operating value. If this pin is left floating, the regulator will enter shutdown mode.                                                                                                                                                                                                                                                       |  |  |  |  |

| 3           | 7, 8, 9 | VIN  | <b>Input Voltage.</b> This is the drain input to the power device that supplies current to the output pin. Large bulk capacitors with low ESR should be placed physically close to this pin o prevent the input rail from dropping during large load transient. A 4.7uF ceramic capacitor is recommended at this pin. $V_{\rm IN}$ cannot be forced higher than $V_{\rm CNTL}$ otherwise the current limit function may be false triggered and disable the output voltage. |  |  |  |  |

| 4           | 10      | CNTL | <b>Supply Input for Control Circuit.</b> This pin provides bias voltage to the control circuitry and driver for the pass transistor. The driving capability of output current is proportioned to the $V_{\text{CNTL}}$ . For the device to regulate, the voltage on this pin must be at least 1.5V greater than the output voltage, and no less than $V_{\text{CNTL\_MIN.}}$ $V_{\text{CNTL}}$ input voltage must be ready before VN I input voltage.                      |  |  |  |  |

| 5           |         | NC   | Not Internally Connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 6           | 1, 2, 3 | VOUT | <b>Output Voltage.</b> This pin is power output of the device. A pull low resistance exists when the device is disabled by pulling low the EN pin. To maintain adequate transient response to large load change, typical value of 1000uF AI electrolytic capacitor with 10uF ceramic capacitors are recommended to reduce the effects of current transients on VOUT.                                                                                                       |  |  |  |  |

| 7           | 4       | FB   | <b>Feedback Voltage.</b> This pin is the inverting input to the error amplifier. A resistor divider from the output to GND is used to set the regulation voltage as $V_{OUT} = 0.8x(R1+R2)/R1$ (V)                                                                                                                                                                                                                                                                         |  |  |  |  |

| 8           |         | GND  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Exposed Pad |         | Pad  | <b>Ground.</b> The exposed pad acts the dominant power dissipation path and should be soldered to well designed PCB pads as described in the <i>Application Informations Chapter</i> .                                                                                                                                                                                                                                                                                     |  |  |  |  |

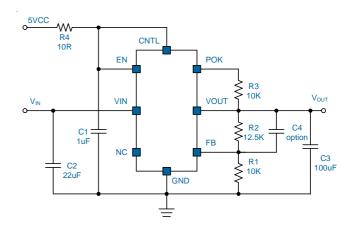

# Functional Block Diagram

## . Functional Description

#### **Definitions**

Some important terminologies for LDO are specified below.

### **Dropout Voltage**

The input/output voltage differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output drops 2% below its nominal value. Dropout voltage is affected by junction temperature, load current and minimum input supply requirements.

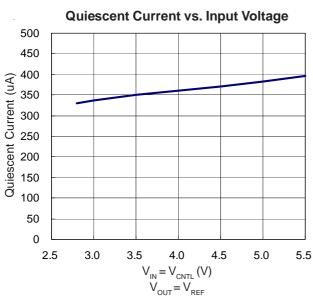

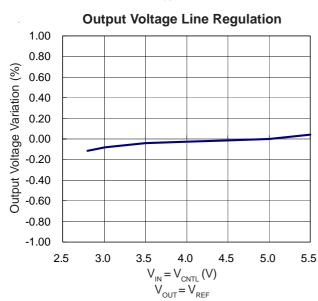

#### Line Regulation

The change in output voltage for a change in input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that average chip temperature is not significantly affected.

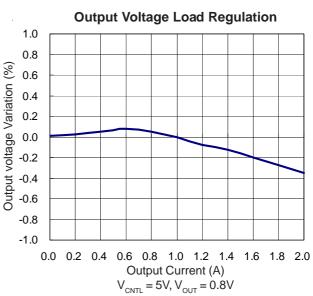

### **Load Regulation**

The change in output voltage for a change in load current at constant chip temperature. The measurement is made under conditions of low dissipation or by using pulse techniques such that average chip temperature is not significantly affected.

#### **Maximum Power Dissipation**

The maximum total device dissipation for the regulator will operate within specifications.

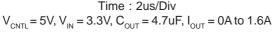

### **Quiescent Bias Current**

Current which is used to operate the regulator chip is not delivered to the load.

The quiescent current  $I_Q$  is defined as the supply current used by the regulator itself that does not pass into the load. It typically includes all bias currents required by the LDO and any drive current for the pass transistor.

## Initialization

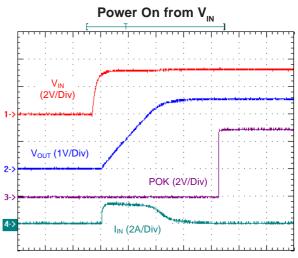

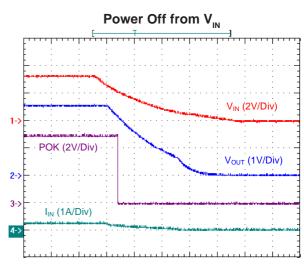

The uP8801S automatically initiates upon the receipt of supply voltage and power voltage. A power on reset circuit continuously monitors VIN and CNTL pins voltages with rising threshold levels of 0.6V and 2.7V respectively.

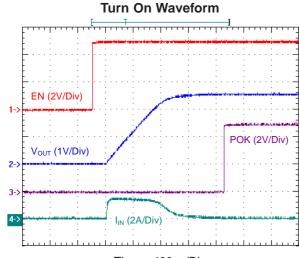

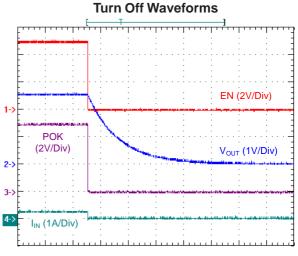

### Chip Enable and Soft Start

The uP8801S features an enable pin for enable/disable control of the chip. Pulling  $\rm V_{EN}$  lower than 0.4V disables the chip and reduces its quiescent current down to 20uA. When disabled, an internal MOSFET of  $50\Omega$   $\rm R_{DS(ON)}$  turns on to pull output voltage to ground. Pulling  $\rm V_{EN}$  higher than 1.4V enables the output voltage, providing POR is recognized. The uP8801S features soft start function that limits inrush current for charging the output capacitors. The soft start time is typically 1ms.

### **Output Voltage Programming**

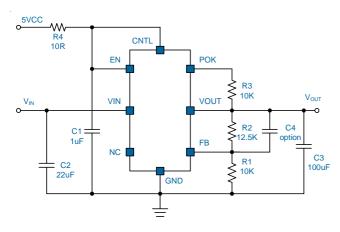

Figure 1 shows a typical application of 2.5V to 1.8V conversion with a 5.0V control supply. The output voltage is sensed through a voltage divider and regulated to internal reference voltage  $V_{\text{REF}}$ . The output voltage is programmed as:

$$V_{OUT} = V_{REF} \times (R_1 + R_2) / R_1 = 0.8V \times (22.5k/10k) = 1.8V$$

It's recommended to maintain 50-100uA through the output divider network for a tight load and line regulation. The internal voltage reference is  $V_{\rm REF} = 0.8V$  with 1.5% initial accuracy. This commands the use of 0.5% or better accuracy resistors to build a precision power supply.

Figure 1. Typical application of 2.5V to 1.8V conversion with a 5.0V control supply

## **Over Current and Short Circuit Protection**

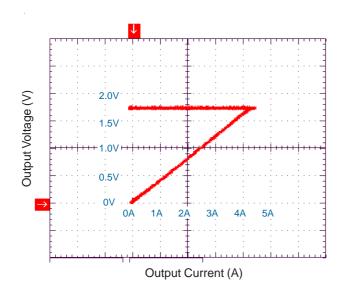

The uP8801S features a foldback over current protection function as shown in Figure 2. The current limit threshold level is proportional to  $V_{\text{OUT}}/V_{\text{NOM}}$  and is typically 4A when  $V_{\text{OUT}} = V_{\text{NOM}}$ , where  $V_{\text{NOM}}$  is the target output voltage. If the output continuously demands more current than the maximum current, output voltage will eventually drops below its nominal value. This, in turns, will lower its OCP threshold level. This will limit power dissipation in the device when over current limit happens.

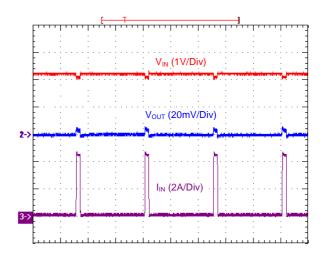

When output short circuit occurs, the uP8801S will try to rebuild the output voltage with maximum allowable current as shown if Figure 3. The duty cycle is about 10% and the averaged short circuit current is about 400mA.

# Functional Description

Figure 2. Current Limit Behavior

Time : 2ms/Div

Figure 3. Output Short Circuit Protection

|                                              | Absolute Maximum Rating            |

|----------------------------------------------|------------------------------------|

| (Note 1)                                     |                                    |

| Control Input Voltage V                      |                                    |

| Power Input Voltage V                        |                                    |

| Other Pins                                   | 0.3V to (V <sub>CNTL</sub> + 0.3V) |

|                                              |                                    |

|                                              | 150°C                              |

| , , ,                                        | 260°C                              |

| ESD Rating (Note 2)                          |                                    |

|                                              | 2kV                                |

| MM (Machine Mode)                            | 200V                               |

|                                              | Thermal Information                |

|                                              | Thermal information                |

| Package Thermal Resistance (Note 3/4)        |                                    |

|                                              | 47°C/W                             |

|                                              | 17.9°C/W                           |

| WDFN3x3 - 10L $\theta_{JA}$                  | 68°C/W                             |

|                                              | 6°C/W                              |

| Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                    |

|                                              | 2.13W                              |

| WDFN3x3 - 10L                                | 1.47W                              |

| ·                                            | Recommended Operation Conditions   |

| (Note 5)                                     | Recommended operation conditions   |

| ,                                            |                                    |

|                                              |                                    |

| Supply Input Voltage, Voltage                | +3.0V to +5.5V                     |

| Power Input Voltage, V.,                     | +1.0V to V <sub>CNTI</sub>         |

| · · · · · · · · · · · · · · · · · · ·        | CNIL                               |

# $(V_{CNTL} = 5V, T_A = 25^{\circ}C, \text{ unless otherwise specified})$

| Parameter                         | Symbol                 | Test Conditions                                                                   | Min   | Тур  | Max               | Units |  |

|-----------------------------------|------------------------|-----------------------------------------------------------------------------------|-------|------|-------------------|-------|--|

| Supply Input Voltage              |                        |                                                                                   |       |      |                   |       |  |

| Control Input Voltage             | V <sub>CNTL</sub>      | $V_{OUT} = V_{REF}$                                                               | 2.9   |      | 6                 | V     |  |

| POR Threshold                     | V <sub>CNTLRTH</sub>   |                                                                                   | 2.5   | 2.7  | 2.9               | V     |  |

| POR Hysteresis                    | V <sub>CNTLHYS</sub>   |                                                                                   | 0.1   | 0.2  |                   | V     |  |

| Power Input Voltage               | V <sub>IN</sub>        | $V_{OUT} = V_{REF}$                                                               | 1.0   |      | V <sub>CNTL</sub> | V     |  |

| Control Input Current in Shutdown | CNTL_SD                | $V_{CNTL} = V_{IN} = 5.0V, I_{OUT} = 0A, V_{EN} = 0V$                             |       | 20   | 30                | uA    |  |

| Control Input Current             | I <sub>CNTL</sub>      | $V_{CNTL} = V_{IN} = V_{EN} = 5.0V, I_{OUT} = 0A, V_{OUT} = V_{REF}$              |       | 0.3  | 0.6               | mA    |  |

| Quiescent Current                 | I <sub>Q</sub>         | $V_{CNTL} = V_{IN} = V_{EN} = 5.0V, I_{OUT} = 0A, V_{OUT} = V_{REF}$              |       | 0.3  | 0.6               | mA    |  |

| Feedback Voltage                  |                        |                                                                                   |       |      |                   |       |  |

| Reference Voltage                 | $V_{REF}$              | $V_{CNTL} = V_{IN} = V_{EN} = 5.0V, I_{OUT} = 0A, V_{OUT} = V_{REF}$              | 0.788 | 8.0  | 0.812             | V     |  |

| Feedback Input Current            | I <sub>FB</sub>        |                                                                                   |       | 20   |                   | nA    |  |

| V <sub>IN</sub> Line Regulation   | V <sub>REF(LINE)</sub> | $1.2V < V_{IN} < 5.0V, V_{CNTL} = V_{EN} = 5.0V, I_{OUT} = 0A, V_{OUT} = V_{REF}$ |       | 0.01 | 0.1               | %/V   |  |

| V <sub>CNTL</sub> Line Regulation |                        |                                                                                   |       | 0.01 | 0.1               | %/V   |  |

Electrical Characteristics

## **Electrical Characteristics**

| Parameter                             | Symbol                 | Test Conditions                                                                                                                                    | Min | Тур | Max | Units |

|---------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Feedback Voltage                      | •                      |                                                                                                                                                    |     | -   | •   |       |

| Load Regulation (Note6)               | V <sub>REF(LOAD)</sub> | $0 \text{mA} < I_{\text{OUT}} < 3.0 \text{A}, \ V_{\text{CNTL}} = V_{\text{EN}} = 5.0 \text{V}, \ V_{\text{IN}} = V_{\text{OUT}} + 0.5_{\text{V}}$ |     | 0.8 | 1.5 | %/A   |

| On Resistance                         | R <sub>DS(ON)</sub>    | $I_{OUT} = 100 \text{mA}, V_{CNTL} = V_{EN} = 5.0 \text{V}, V_{OUT} = 1.6 \text{V}$                                                                | -   | 100 | 160 | mΩ    |

| Dropout Voltage (Note7)               | V <sub>DROP</sub>      | $I_{OUT} = 3A$ , $V_{CNTL} = V_{EN} = 5.0V$ , $V_{IN} = V_{OUT,NOMINAL} - 100 \text{mV}$                                                           |     | 300 | 500 | mV    |

| V <sub>OUT</sub> Pull Low Resistance  |                        | $V_{CNTL} = V_{IN} = 5.0V, V_{EN} = 0V,$                                                                                                           |     | 50  |     | Ω     |

| Enable                                |                        |                                                                                                                                                    |     | •   |     |       |

| Enable High Level                     | V <sub>EN</sub>        |                                                                                                                                                    | 1.4 |     |     | V     |

| Disable Low Level                     | V <sub>SD</sub>        |                                                                                                                                                    |     |     | 0.4 | V     |

| EN Input Impedance                    | Z <sub>EN</sub>        |                                                                                                                                                    |     | 500 |     | kΩ    |

| Output Voltage Ramp Up Time           |                        |                                                                                                                                                    |     | 1   |     | ms    |

| PWROK                                 |                        |                                                                                                                                                    |     |     |     | •     |

| FB Power OK Threshold                 | V <sub>POKTH</sub>     | $I_{OUT} = 0A$ , $V_{CNTL} = V_{IN} = V_{EN} = 5.0V$ , $V_{OUT} = V_{REF}$                                                                         |     | 92  |     | %     |

| Power OK Hysteresis                   | V <sub>POKHYS</sub>    | $I_{OUT} = 0A$ , $V_{CNTL} = V_{IN} = V_{EN} = 5.0V$ , $V_{OUT} = V_{REF}$                                                                         |     | 8   |     | %     |

| POK Delay Time                        |                        | From V <sub>OUT</sub> > 92% V <sub>NOM</sub> to POK rising                                                                                         |     | 1   |     | ms    |

| Over Current Protection               |                        |                                                                                                                                                    |     |     |     |       |

| OCP Threshold Level (Note8)           | I <sub>OCP</sub>       | $V_{CNTL} = V_{IN} = V_{EN} = 5.0V, V_{OUT} = V_{REF}$                                                                                             | 3.6 | 4   | 6   | А     |

| Averaged Output Short Circuit Current | I <sub>sc</sub>        | $V_{CNTL} = V_{IN} = V_{EN} = 5.0V, V_{OUT} = 0V$                                                                                                  | 100 | 440 |     | mA    |

| Thermal Protection                    |                        |                                                                                                                                                    |     | ,   | •   |       |

| Thermal Shutdown<br>Temperature       | T <sub>SD</sub>        | $I_{OUT} = 0A, V_{CNTL} = V_{IN} = V_{EN} = 5.0V, V_{OUT} = V_{REF}$                                                                               |     | 170 |     | °C    |

| Thermal Shutdown<br>Hysteresis        | T <sub>SDHYS</sub>     | $I_{OUT} = 0A, V_{CNTL} = V_{IN} = V_{EN} = 5.0V, V_{OUT} = V_{REF}$                                                                               |     | 30  |     | °C    |

- **Note 1.** Stresses listed as the above *Absolute Maximum Ratings* may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}\text{C}$  on a low effective thermal conductivity test board of JEDEC 51-5 thermal measurement standard.

- Note 4. The case temp location for measuring  $\theta_{\text{JC}}$  is on the top of the package.

- **Note 5.** The device is not guaranteed to function outside its operating conditions.

- **Note 6.** This test item is tested under constant junction temperature which does not exceed absolute maximum ratings. In this test, a 5ms current pulse is applied at the output for measuring required data without exceeding junction temperature AMR.

- **Note 7.** This test item is tested under constant junction temperature which does not exceed absolute maximum ratings. In this test, the dropout voltage is measured as  $V_{IN}^-V_{OUT}^-$  where  $V_{IN}^-$  equals  $V_{OUT,NOMINAL}^-$ -100mV, and  $V_{OUT}^-$  decreases lower than  $V_{OUT,NOMINAL}^-$  due to IR drop.

- Note 8. OCP threshold level is not guaranteed to function outside its linear region.

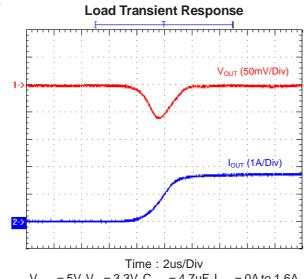

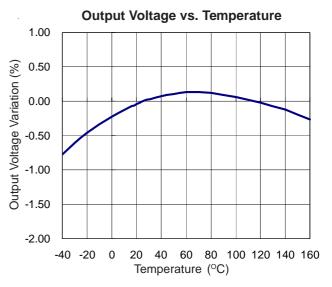

# **Typical Operation Characteristics**

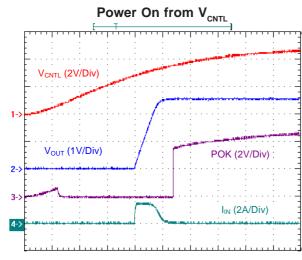

Time : 1ms/Div  $\rm V_{CNTL} = 5V, \, V_{IN} = 3.3V, \, C_{OUT} = 470uF, \, No \, \, Load$

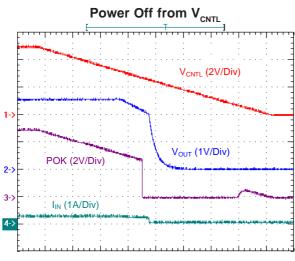

$\label{eq:constraint} \begin{aligned} & \text{Time : 20ms/Div} \\ & \text{V}_{\text{CNTL}} = \text{5V, V}_{\text{IN}} = 3.3\text{V, C}_{\text{OUT}} = 470\text{uF, R}_{\text{L}} = 11\Omega \end{aligned}$

$\label{eq:continuous} \begin{aligned} & \text{Time: 400us/Div} \\ & \text{V}_{\text{CNTL}} = \text{5V, V}_{\text{IN}} = 3.3\text{V, C}_{\text{OUT}} = 470\text{uF, No Load} \end{aligned}$

$\label{eq:time:dous} \mbox{Time: 400us/Div} \\ \mbox{V}_{\mbox{\tiny CNTL}} = \mbox{5V}, \mbox{ V}_{\mbox{\tiny IN}} = \mbox{3.3V}, \mbox{ C}_{\mbox{\tiny OUT}} = \mbox{470uF}, \mbox{No Load}$

$\label{eq:continuous} Time: 10 \text{ms/Div} \\ V_{\text{CNTL}} = 5 \text{V, V}_{\text{IN}} = 3.3 \text{V, C}_{\text{OUT}} = 470 \text{uF, R}_{\text{L}} = 11 \Omega$

$\label{eq:volume} Time: 4 \text{ms/Div} \\ \text{V}_{\text{CNTL}} \text{= 5V, V}_{\text{IN}} \text{= 3.3V, C}_{\text{OUT}} \text{= 470uF, R}_{\text{L}} \text{= 11}\Omega$

# **Typical Operation Characteristics**

# **Typical Operation Characteristics**

## Application Information

The uP8801S is a high performance linear regulator specifically designed to deliver up to 3A output current with very low input voltage and ultra low dropout voltage. With dual-supply configuration, the uP8801S operates with a wide input voltage  $V_{\text{IN}}$  range from 1.2V to 5.5V and is ideal for applications where  $V_{\text{OUT}}$  is very close to  $V_{\text{IN}}$ .

## Supply Voltage for Control Circuit $V_{CNTL}$

Unlike other linear regulators that use a P-Channel MOSFET as the pass transistor, the uP8801S uses an N-Channel as the pass transistor. N-Channel MOSFET provides lower on-resistance and better stability meeting stringent requirements of current generation microprocessors and other sensitive electronic devices. The drain of N-Channel MOSFET is connected to VIN and the source is connected to VOUT. This requires that the supply voltage  $V_{\text{CNTL}}$  for control circuit is at least 1.5V higher than the output voltage to provide enough overdrive capability for the pass transistor thus to achieve low dropout and fast transient response. It is highly recommended to bias the device with 5V voltage source if available.

Use a minimum 1uF ceramic capacitor plus a  $10\Omega$  resistor to locally bypass the control voltage.

#### Input/Output Capacitor Selection

The uP8801S has a fast transient response that allows it to handle large load changes associated with high current applications. Proper selection of the output capacitor and its ESR value determines stable operation and optimizes performance. The typical application circuit shown in Figure 1 was tested with a wide range of different capacitors. The circuit was found to be unconditionally stable with capacitor values from 10uF to 1000uF and ESR ranging from  $0.5 m\Omega$  to greater then  $75 m\Omega$ .

Figure 1. Typical Application Circuit

**Input capacitor:** A minimum of 4.7uF ceramic capacitor is recommended to be placed directly next to the VIN pin.

This allows for the device being some distance from any bulk capacitance on the rail. Additionally, bulk capacitance may be added closely to the input supply pin of the uP8801S to ensure that  $V_{\rm IN}$  does not sag, improving load transient response.

Output capacitor: A minimum bulk capacitance of 10uF, along with a 0.1uF ceramic decoupling capacitor is recommended. Increasing the bulk capacitance will improve the overall transient response. The use of multiple lower value ceramic capacitors in parallel to achieve the desired bulk capacitance will not cause stability issues. Although designed for use with ceramic output capacitors, the uP8801S is extremely tolerant of output capacitor ESR values and thus will also work comfortably with tantalum output capacitors.

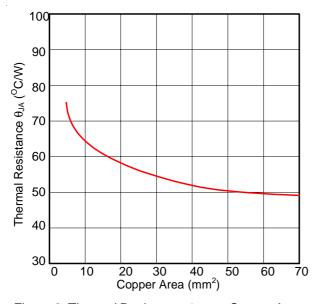

#### **Thermal Consideration**

The uP8801S integrates internal thermal limiting function to protect the device from damage during fault conditions. However, continuously keeping the junction near the thermal shutdown temperature may remain possibility to affect device reliability. It is highly recommended to keep the junction temperature below the recommended operation condition 125°C for maximum reliability.

Power dissipation in the device is calculated as:

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{CNTL} \times I_{CNTL}$$

It is adequate to neglect power loss with respective to control circuit  $V_{CNTL}$  x  $I_{CNTL}$  when considering thermal management in uP8801S Take the following moderate operation condition as an example:  $V_{IN} = 3.3V$ ,  $V_{OUT} = 1.5V$ ,  $I_{OUT} = 1A$ , the power dissipation is:

$$P_D = (3.3V-1.5V) \times 1A = 1.8W$$

This power dissipation is conducted through the package into the ambient environment, and, in the process, the temperature of the die ( $T_J$ ) rises above ambient. Large power dissipation may cause considerable temperature raise in the regulator in large dropout applications. The geometry of the package and of the printed circuit board (PCB) greatly influences how quickly the heat is transferred to the PCB and away from the chip. The most commonly used thermal metrics for IC packages are thermal resistance from the chip junction to the ambient air surrounding the package  $(\theta_{1\Delta})$ :

$$\theta_{JA} = (T_J - T_A) / P_D$$

$\theta_{JA}$  specified in the *Thermal Information* section is measured in the natural convection at  $T_A=25^{O}C$  on a high effective thermal conductivity test board (4 Layers, 2S2P) of JEDEC 51-7 thermal measurement standard. The case point of  $\theta_{JC}$  is on the exposed pad for PSOP-8L package.

## **Application Information**

Given power dissipation  $P_D$ , ambient temperature and thermal resistance  $\theta_{JA}$ , the junction temperature is calculated as:

$$T_J = T_A + \Delta T_{JA} = T_A + P_D \times \theta_{JA}$$

To limit the junction temperature within its maximum rating, the allowable maximum power dissipation is calculated as:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum operation junction temperature 125°C,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.  $\theta_{JA}$  of PSOP-8 packages is 75°C/W on JEDEC 51-7 (4 layers, 2S2P) thermal test board with minimum copper area. The maximum power dissipation at  $T_A$  = 25°C can be calculated as:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / 75^{\circ}C/W = 1.33W$$

The thermal resistance  $\theta_{JA}$  highly depends on the PCB design. Copper plane under the exposed pad is an effective heatsink and is useful for improving thermal conductivity. Figure 3 show the relationship between thermal resistance  $\theta_{JA}$  vs. copper area on a standard JEDEC 51-7 (4 layers, 2S2P) thermal test board at  $T_A = 25^{\circ}$ C. A 50mm² copper plane reduces  $\theta_{JA}$  from 75°C/W to 52°C/W and increases maximum power dissipation from 1.33W to 1.9W.

Figure 3. Thermal Resistance  $\theta_{JA}$  vs. Copper Area

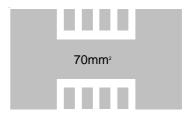

Figure 4. Copper Area of Thermal Pad =  $70 \text{mm}^2$ ,  $\theta_{1\Delta} = 45^{\circ}\text{C/W}$

Figure 4 shows a 70mm² copper on a standard JEDEC 51-5 (4 layers, 2S2P+Via) high effective thermal conductivity test board.  $\theta_{JA}$  of PSOP-8L package is 45°C/W. The maximum power dissipation depends on thermal shutdown temperature  $T_{J(MAX)}$  = 170°C and thermal resistance  $\theta_{JA}$  = 45°C/W at  $T_A$  = 25°C can be calculated as:

$$P_{D(MAX)} = (170^{\circ}C - 25^{\circ}C) / 45^{\circ}C/W = 3.22W$$

However, it is highly recommended to keep the junction temperature below the recommended operation condition 125°C for maximum reliability.

Figure 5 illustrates the recommended PCB layout for best thermal performance.

Figure 5. Recommended PCB Layout.

## **Layout Consideration**

- Place a local bypass capacitor as closed as possible to the VIN pin. Use short and wide traces to minimize parasitic resistance and inductance.

- The exposed pad should be soldered on GND plane with maximum area and with multiple vias to inner layer of ground place for improving thermal performance.

- Connect voltage divider directly to the point where regulation is required. Place voltage divider close to the device.

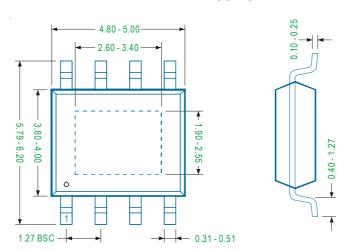

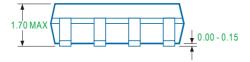

# Package Information

#### PSOP-8L

## Note

- 1. Package Outline Unit Description:

- BSC: Basic. Represents theoretical exact dimension or dimension target

- MIN: Minimum dimension specified.

- MAX: Maximum dimension specified.

- REF: Reference. Represents dimension for reference use only. This value is not a device specification.

- TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

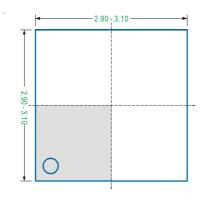

# Package Information

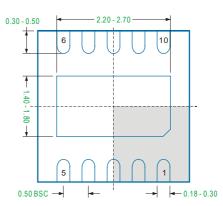

### WDFN3x3-10L

### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

## **Important Notice**

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

uPI products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment. However, no responsibility is assumed by uPI or its subsidiaries for its use or application of any product or circuit; nor for any infringements of patents or other rights of third parties which may result from its use or application, including but not limited to any consequential or incidental damages. No uPI components are designed, intended or authorized for use in military, aerospace, automotive applications nor in systems for surgical implantation or life-sustaining. No license is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (c) 2014, UPI SEMICONDUCTOR CORP.

## uPI Semiconductor Corp.

Headquarter 9F.,No.5, Taiyuan 1st St. Zhubei City, Hsinchu Taiwan, R.O.C.

TEL: 886.3.560.1666 FAX: 886.3.560.1888

Sales Branch Office 12F-5, No. 408, Ruiguang Rd. Neihu District, Taipei Taiwan, R.O.C.

TEL: 886,2.8751,2062 FAX: 886,2.8751,5064