## uP1741P-B1 Wide Input Range, 8A, Synchronous-Rectified Buck Converter

### **General Description**

The uP1741P-B1 is a high performance synchronous buck converter. The synchronous buck of the uP1741P-B1 uPI's proprietary robust constant on-time (RCOT<sup>™</sup>) PWM scheme that features easy-to-use, low external component count, fast transient response and quasi-constant frequency operation over the operation range.

The uP1741P-B1 has complete functions including under voltage protection, over current protection, over voltage protection, power-up sequencing, power OK output, and thermal shutdown. The uP1741P-B1 is available in WQFN4x4-32L package.

### **Features**

- □ Wide Input Voltage Range from 4.5V to 26V

- □ Fast Load Transient Response

- Output Current Up to 8A

- □ RCOT<sup>™</sup> Control Topology

- Discharge Output When Disable

- Fixed 1.5V, 1.8V Output or Adjustable from 0.75V to 3.3V

- D POR, OVP, UVP and Thermal Shutdown

- RoHS Compliant and Halogen Free

### **Applications**

- Desktop PCs, Notebooks, and Workstations

- □ Microprocessor and Chipset Supplies

### **Ordering Information**

| Order Number  | Package Type | Top Marking |

|---------------|--------------|-------------|

| uP1741PQMI-B1 | WQFN4x4-32L  | uP1741P     |

Note:

(1) Please check the sample/production availability with uPI representatives.

(2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

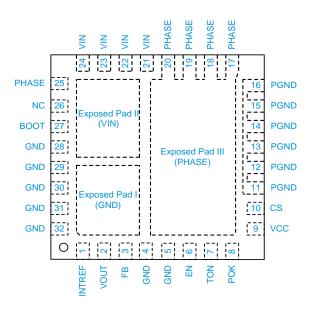

## **Pin Configuration**

1

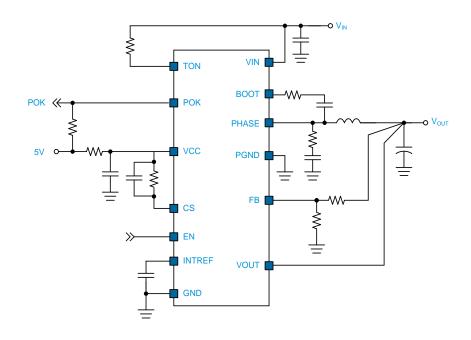

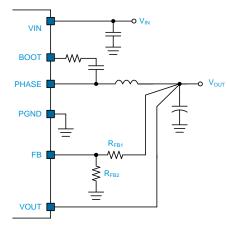

## **Typical Application Circuit**

## **Functional Pin Description**

| Pin No.                    | Name   | Pin Function                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                          | INTREF | Internal Reference. Bypass this pin with 0.1uF ceramic capacitor to GND.                                                                                                                                                                                                                                                 |  |  |  |

| 2                          | VOUT   | <b>Output Voltage Sense.</b> Connect this pin to output point of converter. A discharge resistor is connected when disable.                                                                                                                                                                                              |  |  |  |

| 3                          | FB     | <b>Voltage Feedback Input.</b> This pin is the inverting input of the error amplifier. A resistor divider from output to GND is used to set the regulator output voltage. For fixed output voltage application, connect this pin to VCC for fixed output 1.8V, or connect this pin to GND for fixed output 1.5V.         |  |  |  |

| 4, 5,<br>28~32             | GND    | Signal Ground for the IC. All voltage levels are measured with respect to this pin.                                                                                                                                                                                                                                      |  |  |  |

| 6                          | EN     | EN Enable. This pin is for the chip enable and disable. Pulling this pin to logic high/lov evel to enable/disable the IC.                                                                                                                                                                                                |  |  |  |

| 7                          | TON    | <b>On-Time Setting Pin.</b> Connect a resistor from this pin to $V_{\text{IN}}$ to set the on-time for the upper MOSFET.                                                                                                                                                                                                 |  |  |  |

| 8                          | РОК    | <b>Power OK Indication.</b> POK is the open-drain architecture that indicates the output volt is ready or not. This pin is set to high impedance when the output voltage is wi regulation and the soft-start ends. POK is pulled low immediately when either output i soft-start, standby, shutdown or fault protection. |  |  |  |

| 9                          | VCC    | <b>5V Power Supply Input.</b> This pin provides power for internal circuit. Bypass this pin with a 1uF ceramic capacitor to GND.                                                                                                                                                                                         |  |  |  |

| 10                         | CS     | <b>CS Current Limit Threshold Setting.</b> Connect this pin through the setting resistor to VCC for inductor current limit threshold setting.                                                                                                                                                                            |  |  |  |

| 11~16                      | PGND   | <b>Power Ground.</b> This pin is dedicated for lower MOSFET gate driver and should be directly connected to the source of the lower MOSFET with an isolated path.                                                                                                                                                        |  |  |  |

| 17~20, 25                  | PHASE  | <b>Switch Node.</b> This pin is used as the sink for the upper MOSFET gate driver. This pin is also monitored by the shoot-through protection circuitry to determine when the upper MOSFET has turned off. Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET.                         |  |  |  |

| 21~24                      | VIN    | Supply Input. Input voltage that supplies current to the output voltage.                                                                                                                                                                                                                                                 |  |  |  |

| 26                         | NC     | Not Internally Connected.                                                                                                                                                                                                                                                                                                |  |  |  |

| 27                         | BOOT   | <b>Bootstrap Supply for the Floating Upper MOSFET Gate Driver.</b> The bootstrap capacitor provides the charge to turn on the upper MOSFET. Connect this bootstrap capacitor between BOOT pin and the PHASE pin to form a bootstrap circuit.                                                                             |  |  |  |

| Exposed Pad I<br>(GND)     |        | Signal Ground for the IC. All voltage levels are measured with respect to this pin.                                                                                                                                                                                                                                      |  |  |  |

| Exposed Pad II<br>(VIN)    |        | Supply Input. Input voltage that supplies current to the output voltage.                                                                                                                                                                                                                                                 |  |  |  |

| Exposed Pad III<br>(PHASE) |        | <b>Switch Node.</b> This pin is used as the sink for the upper MOSFET gate driver. This pin is also monitored by the shoot-through protection circuitry to determine when the upper MOSFET has turned off. Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET.                         |  |  |  |

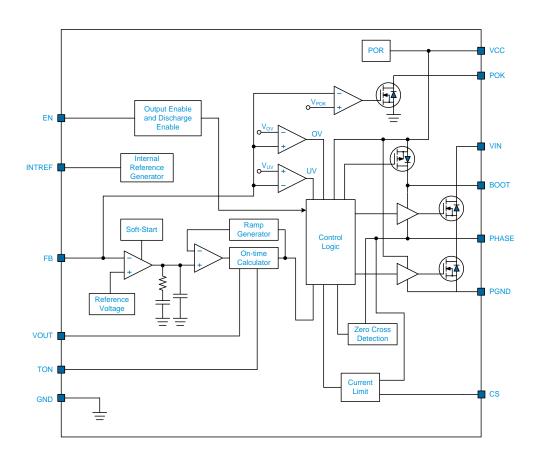

## **Functional Block Diagram**

### **Functional Description**

The uP1741P-B1 is a high performance synchronous buck converter with wide input range.

The buck converter adopts RCOT<sup>™</sup> PWM scheme that features easy-to-use, low external component count, fast transient response and quasi-constant frequency operation over the operation range.

The uP1741P-B1 has complete functions including over current protection, over voltage protection, thermal shutdown, power-up sequencing, power OK output, and thermal shutdown. The uP1741P-B1 is available in space-saving WQFN4x4-32L package.

#### **Output Voltage Selection**

As shown in Table 1, uP1741P-B1 can support fixed 1.8V/1.5V or adjustable output voltage by connecting resistor divider to the FB pin

| FB Connection    | VOUT       |

|------------------|------------|

| VCC              | 1.8V       |

| GND              | 1.5V       |

| Resistor Divider | Adjustable |

Table 1. Output Voltage Selection

The uP1741P-B1 can adjust output voltage by connecting a resistive voltage divider between VOUT and GND as shown in Figure 1. Choose  $R_{FB2}$  to be approximately 10k $\Omega$  and solve  $R_{FB1}$  using the equation as below:

$V_{OUT}$  =  $V_{REF}$   $\times$  (1 +  $\frac{R_{FB1}}{R_{FB2}}$ ), where  $V_{REF}$  is 0.75V (typ.)

Figure 1. Output Voltage Setting

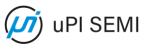

#### **On-Time Setting**

The uP1741P-B1 adopts a compensated constant-on-time control scheme. A resistor  $R_{TON}$  connected to TON pin programs the constant on time according to equation:

$T_{\rm ON} = \frac{3.8 \times 10^{-12} \times VOUT \times R_{\rm TON}}{VIN - 0.5V},$

where  $R_{TON}$  is in k $\Omega$ , VIN is the supply input voltage and VOUT is the sensed output voltage

#### uP1741P-B1-DS-F0000, Apr. 2022

## **Functional Description**

Figure 2. Switching Frequency vs.  $R_{TON}$

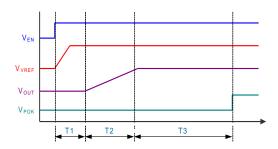

#### Soft Start and POK

The soft-start function of the uP1741P-B1 is achieved by ramping up reference as shown in Figure 3. After EN is set high, the VREF is rising. There is a time delay between VREF ramping up and VOUT rising. After that, the uP1741P-B1 initiates soft-start operation.

The POK is an open-drain output. The uP1741P-B1 asserts POK high impedance output if the output voltage is within regulation with a time delay after soft-start end. Anytime the fault protection is triggered, the POK signal will go low immediately.

Figure 2. Soft Start and POK Timing

### **Light Load Operation**

The uP1741P-B1 automatically reduces switching frequency at light load to maintain high efficiency. As the output current decreases from heavy-load condition, the inductor current will also be reduced, and eventually comes to the point that its valley touches zero current, which is the boundary between continuous conduction and discontinuous conduction modes. By emulating the behavior of diodes, the lower MOSFET allows only partial of negative current when the inductor freewheeling current reaches negative. As the load current is further decreased, it takes longer time to discharge the output capacitor to the level than requires the next ON cycle.

### **Output Discharge Control**

The uP1741P-B1 has internal discharge resistor 15Ω, which is connected from VOUT to GND.

### **Functional Description**

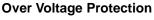

### **Output Current Limit**

The synchronous buck output monitors the inductor valley current by lower MOSFET  $R_{DS(ON)}$  when it turns on. The over current limit is triggered once the sensing current level is higher than  $V_{OCSET}$ . When triggered, the over current limit will keep upper MOSFET off even the voltage loop commands it to turn on. Converter will latch off if CS pin is open during VCC power on or enable.

The output voltage will decrease if the load continuously demands more current than current limit level. Further increase in load current higher than the current limit level will eventually let  $V_{OUT}$  decrease to trip UVP to shut down the uP1741P-B1.

The current limit threshold is set by connecting a resistor from CS to VCC. The CS pin will sink a 10uA current source and create a voltage drop across  $R_{CS}$  as the  $V_{OCSET}$ .

$V_{OCSET}$  = 10uA x R<sub>CS</sub> When the voltage drop across the lower MOSFET equals the voltage across the setting resistor, the current limit will be activated.

The current limit level is calculated as:

$I_{\text{LIM}} = \frac{V_{\text{OCSET}}}{R_{\text{DS}(\text{ON})}} + \frac{I_{\text{RIPPLE}}}{2}$

where  $I_{\ensuremath{\mathsf{R}}\xspace{\mathsf{IPPLE}}}$  is the peak-to-peak inductor ripple current at steady state.

### **Over Voltage/Under Voltage Protection**

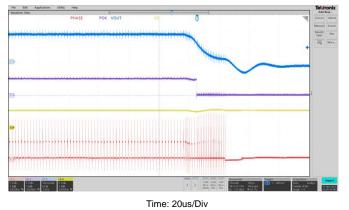

The uP1741P-B1 monitors FB voltage to detect overvoltage and undervoltage condition of output. When the FB voltage becomes higher than 115% of the target voltage, the OVP is triggered. Then, upper MOSFET is off and lower MOSFET is on. When the FB voltage is lower than 70% of the target voltage, the UVP is triggered after 30us fault detection. Then, upper MOSFET and lower MOSFET are latched off. This function is enabled 2ms after EN goes high to ensure startup.

### VCC UVLO

The VCC has under voltage lockout protection (UVLO). When the VCC voltage is lower than UVLO threshold voltage, all functions are turned off. This is non-latch protection.

### **Thermal Protection**

The uP1741P-B1 monitors the temperature of itself. If the temperature exceeds typical 150°C, the uP1741P-B1 will be turned off. This is non-latch protection.

## **Absolute Maximum Rating**

| (Note 1)                             |               |

|--------------------------------------|---------------|

| VCC to GND                           |               |

| VIN to GND                           | 0.3V to +30V  |

| BOOT to PHASE                        | 0.3V to +6V   |

| PHASE to GND                         |               |

| DC                                   |               |

| < 50ns                               |               |

| Other Pins                           | 0.3V to +6V   |

| Storage Temperature Range            |               |

| Junction Temperature                 | _             |

| Lead Temperature (Soldering, 10 sec) | <b> 260</b> ℃ |

| EDS Rating (Note 2)                  |               |

| HBM (Human Body Mode)                | 1kV           |

| MM (Machine Mode)                    | 200V          |

### **Thermal Information**

| Package Thermal Resistance (Note 3)                     |     |

|---------------------------------------------------------|-----|

| WQFN4x4-32L θ <sub>JA, controller</sub> 55°C            | ./W |

| WQFN4x4-32L θ <sub>JA, HS</sub> 45°C                    | ./W |

| WQFN4x4-32L θ <sub>JA, LS</sub> 39℃                     | ./W |

| WQFN4x4-32L $\theta_{JC, \text{ controller}}$ 21°C      | ./W |

| WQFN4x4-32L θ <sub>JC, HS</sub> 12℃                     | ./W |

| WQFN4x4-32L θ <sub>JC, LS</sub> 7°C                     | ./W |

| Power Dissipation, $P_D @ T_A = 25^{\circ}C$            |     |

| WQFN4x4-32L P <sub>D</sub> , <sub>controller</sub> 1.8' | 1W  |

| WQFN4x4-32L P <sub>D</sub> , <sub>HS</sub> 2.22         | 2W  |

| WQFN4x4-32L P <sub>D</sub> , <sub>LS</sub> 2.56         | 3W  |

|                                                         |     |

### **Recommended Operation Conditions**

| (Note 4)                              |                |

|---------------------------------------|----------------|

| Supply Input Voltage, V <sub>IN</sub> | +4.5V to +26V  |

| Control Voltage, VCC                  | +4.5V to +5.5V |

| Operating Junction Temperature Range  | 40℃ to +125℃   |

| Operating Ambient Temperature Range   | 40℃ to +85℃    |

- **Note 1.** Stresses listed as the above *Absolute Maximum Ratings* may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity test board of *JEDEC 51-7* thermal measurement standard.

- Note 4. The device is not guaranteed to function outside its operating conditions

### **Electrical Characteristics**

| $(V_{IN} = 12V, V_{CC} = 5V, T_A = +25$<br>Parameter | Symbol              | Test Conditions                                                         | Min   | Тур  | Max   | Units |

|------------------------------------------------------|---------------------|-------------------------------------------------------------------------|-------|------|-------|-------|

| Falalletei                                           | Symbol              | Test conditions                                                         |       | тур  | IVIAX | Units |

| Supply Current                                       |                     |                                                                         |       |      |       |       |

| VCC Current                                          | I <sub>VCC</sub>    | Supply current, EN = 5V, force FB above regulation level (no switching) |       | 470  | 1000  | uA    |

|                                                      |                     | Shutdown current, EN = 0V                                               |       | 1    | 10    | 7     |

| TON Current                                          |                     | Operating current, $R_{TON} = 1M\Omega$                                 |       | 15   |       |       |

|                                                      | I <sub>TON</sub>    | Shutdown current, EN = 0V                                               |       | 0.1  | 5     | – uA  |

| Reference Voltage                                    |                     |                                                                         |       |      |       |       |

| FB Reference Voltage                                 |                     | $V_{VCC} = 4.5V$ to 5.5V                                                | 0.742 | 0.75 | 0.758 |       |

|                                                      | $V_{REF}$           | Connect FB pin to VCC                                                   |       | 1.8  |       | V     |

|                                                      |                     | Connect FB pin to GND                                                   |       | 1.5  |       |       |

| FB Input Bias Current                                | I <sub>FB</sub>     | $V_{FB} = 0.75V$                                                        | -1    | 0.1  | 1     | uA    |

| VOUT                                                 |                     |                                                                         |       |      |       |       |

| Input Resistance                                     | R <sub>VOUT</sub>   |                                                                         |       | 100  |       | kΩ    |

| Discharge Resistance                                 |                     | EN = 0V                                                                 |       | 15   |       | Ω     |

| On Time                                              |                     |                                                                         |       |      |       |       |

| On-Time                                              | T <sub>ON</sub>     | R <sub>TON</sub> = 510kΩ, VOUT = 1.35V                                  | 182   | 228  | 274   | ns    |

| Minimum On-Time                                      | T <sub>ONMIN</sub>  |                                                                         |       | 80   |       | ns    |

| Minimum Off-Time                                     | T <sub>OFFMIN</sub> |                                                                         | 250   | 400  | 550   | ns    |

| Power OK                                             |                     |                                                                         |       |      |       |       |

| POK Rising Threshold                                 | V <sub>THPOKH</sub> | Measured at FB, with respect to reference voltage                       | 87    | 90   | 93    | %     |

|                                                      |                     | Hysteresis                                                              |       | 5    |       | 1     |

| POK Propagation Delay                                | Т <sub>РОК</sub>    | From FB forced below POK falling threshold to POK go low                |       | 2.5  |       | us    |

| POK Leakage Current                                  | I <sub>LK_POK</sub> | High state, POK = 5V                                                    |       |      | 1     | uA    |

| POK Output Low Voltage                               | $V_{POK\_L}$        | Sink current = 1mA                                                      |       |      | 0.4   | V     |

| Logic Input Threshold                                |                     | <u>.</u>                                                                | •     |      |       | •     |

| High Level Input Voltage                             | V <sub>IH</sub>     | EN high                                                                 | 2     |      |       | V     |

| Low Level Input Voltage                              | V <sub>IL</sub>     | EN low                                                                  |       |      | 0.8   | V     |

| Logic Input Leakage Current                          | V <sub>INLEAK</sub> | EN = 5V/ 0V                                                             | -1    |      | 1     | uA    |

| Internal Bootstrap Switch                            |                     | ·                                                                       | •     |      | •     | •     |

| Internal Boost Charging<br>Switch On-Resistance      | R <sub>BOOT</sub>   | VCC to BOOT, I <sub>BOOT</sub> = 5mA                                    |       |      | 80    | Ω     |

## **Electrical Characteristics**

| Parameter                    | Symbol                   | Test Conditions                                   | Min | Тур  | Max | Units  |

|------------------------------|--------------------------|---------------------------------------------------|-----|------|-----|--------|

| Power Switches               |                          | · · · · · · · · · · · · · · · · · · ·             |     |      |     |        |

| Upper Switch Resistance      | R <sub>UG,DSON</sub>     |                                                   |     | 21.5 | 26  | mΩ     |

| Lower Switch Resistance      | R <sub>LG,DSON</sub>     |                                                   |     | 9    | 11  | mΩ     |

| Protection: Current Limit    |                          |                                                   |     |      |     |        |

| CS Sink Current              | I <sub>CS</sub>          | $V_{CS} > 4.5V$                                   | 9   | 10   | 11  | uA     |

| CS Current Temp. Coefficient | T <sub>CICS</sub>        | On the basis of 25°C (Note 5)                     |     | 4700 |     | ppm/°C |

| OCP Comparator Offset        | V <sub>OCLoff</sub>      | $GND - V_{PHASE}, R_{CS} = 5k\Omega$              | -15 |      | 15  | mV     |

| Zero Current Threshold       | V <sub>ZC</sub>          | GND – V <sub>PHASE</sub> ,                        | -5  |      | 10  | mV     |

| Protection: UVP and OVP      |                          |                                                   |     |      |     |        |

| OVP Trip Threshold           | V <sub>OVP</sub>         | Measured at FB, with respect to reference voltage | 110 | 115  | 120 | %      |

| OVP Propagation Delay        | TOVPDEL                  | Force FB above OVP trip threshold                 |     | 20   |     | us     |

| UVP Trip Threshold           | V <sub>UVP</sub>         | Measured at FB, with respect to reference voltage | 60  | 70   | 80  | %      |

| UVP Propagation Delay        | TUVPDEL                  | Force FB above UVP trip threshold                 |     | 30   |     | us     |

| UVP Enable Delay             | T <sub>UVPEN</sub>       | From EN signal go high                            |     | 2    |     | ms     |

| Protection: UVLO             |                          |                                                   |     |      |     |        |

|                              | V <sub>UVLO</sub>        | Rising edge                                       | 3.9 | 4.2  | 4.5 | - V    |

| VCC UVLO Threshold           |                          | Hysteresis                                        |     | 0.12 |     |        |

| Protection: Thermal Shutdow  | vn                       | · · · · · · · · · · · · · · · · · · ·             |     | •    | •   |        |

|                              | -                        | Shutdown temperature                              |     | 150  |     | 0.0    |

| Thermal Shutdown Threshold   | reshold T <sub>SDN</sub> | Hysteresis                                        |     | 20   |     | °C     |

Note 5. Guaranteed by design

### **Application Information**

### PCB Layout Considerations

High speed switching and relatively large peak currents in a synchronous-rectified buck converter make the PCB layout a very important part of design. Fast current switching from one device to another in a synchronous-rectified buck converter causes voltage spikes across the interconnecting impedances and parasitic circuit elements. The voltage spikes can degrade efficiency and radiate noise that result in overvoltage stress on devices. Careful component placement layout and printed circuit board design minimizes the voltage spikes induced in the converter.

Follow the layout guidelines for optimal performance of uP1741P-B1.

- Place VIN and VCC decoupling capacitor as near as possible to the device.

- Keep analog and non-switching components away from switching components.

- Keep the snubber loop between the PHASE to PGND be as short as possible.

- Keep the pattern lines for current delivery path broad.

- Keep the PHASE node physically small and short as possible to minimize radiated emissions.

- Do not allow switching current to flow under the device.

- Make a single point connection from the signal ground to power ground.

- Providing sufficient via for VIN, PHASE and PGND.

- Voltage feedback loop should be as short as possible, and preferably with ground shield.

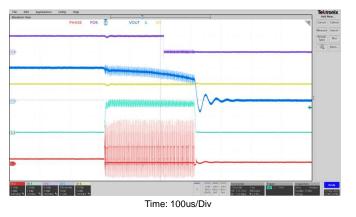

## **Typical Operation Characteristics**

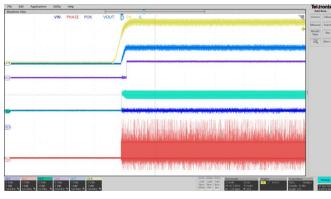

#

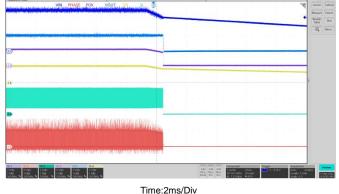

#### Time: 2ms/Div

$\label{eq:ch1=VIN(2V/div),CH2=PHASE(5V/div),CH3=IL(2A/div),CH4=POK(5V/div),\\ CH5=VOUT(1V/div),CH6=EN(5V/div),V_{IN}=V_{EN}=5V,V_{OUT}=1V,Load=2A$

EN On

Time: 2ms/Div

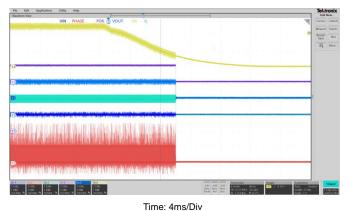

$\label{eq:ch1=VIN(5V/div),CH2=PHASE(5V/div),CH3=IL(5A/div),CH4=POK(5V/div)} \\ CH5=VOUT(1V/div),CH6=EN(2V/div),V_{IN}=5V,V_{OUT}=1V,Load=5A \\ \label{eq:ch1}$

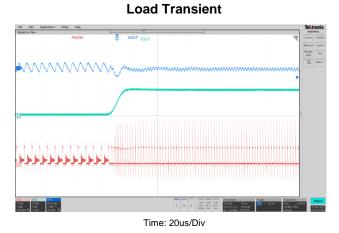

CH2=PHASE(5V/div), CH3=IOUT(5A/div), CH5=VOUT(50mV/div)

$V_{IN}=V_{EN}=5V$ ,  $V_{OUT}=1V$ , Load=0.8A~8A, L=0.68uH

Power Off from VIN

CH1=VIN(2V/div),CH2=PHASE(5V/div),CH3=IL(2A/div),CH4=POK(5V/div), CH5=VOUT(1V/div),CH6=EN(5V/div),V<sub>IN</sub>=V<sub>EN</sub>=5V,V<sub>OUT</sub>=1V,Load=2A

**EN Off**

CH1=VIN(5V/div),CH2=PHASE(5V/div),CH3=IL(5A/div),CH4=POK(5V/div) CH5=VOUT(1V/div),CH6=EN(2V/div),Vin=5V,Vout=1V,Load=5A

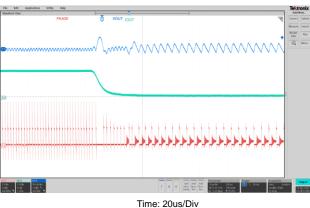

Load Transient

CH2=PHASE(5V/div), CH3=IOUT(5A/div), CH5=VOUT(50mV/div)

$V_{IN}=V_{EN}=5V$  ,  $V_{OUT}=1V$ , Load=8A~0.8A, L=0.68uH

### uP1741P-B1-DS-F0000, Apr. 2022

## uP1741P-B1 Typical Operation Characteristics

### **Under Voltage Protection**

CH2=PHASE(5V/div),CH4=POK(5V/div),CH5=VOUT(500mV/div),CH6=EN(5V/div)

#### V<sub>IN</sub>=5V ,V<sub>OUT</sub>=1V

CH2=PHASE(5V/div),CH4=POK(5V/div),CH5=VOUT(500mV/div),CH6=EN(5V/div)

$V_{IN}=5V$  , $V_{OUT}=1V$

CH2=PHASE(5V/div),CH3=IL(5A/div),CH4=POK(5V/div) CH5=VOUT(500mV/div),CH6=EN(5V/div),V<sub>IN</sub>=5V,V<sub>OUT</sub>=1V

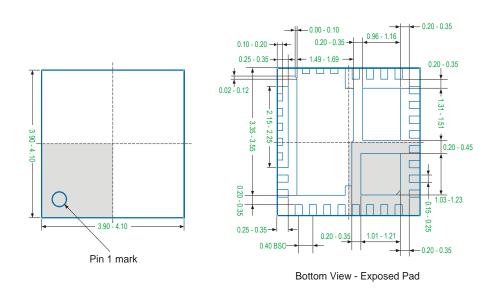

## **Package Information**

### Note

- 1. Package Outline Unit Description:

- MIN: Minimum dimension specified.

NOM: Nominal. Provided as a general value.

MAX: Maximum dimension specified.

BSC: Basic. Represents theoretical exact dimension or dimension target.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

## **Legal Notice**

The contents of this document are provided in connection with uPI Semiconductor Corp. ("uPI") products. uPI makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice.

No license, whether express, implied, arising by estoppels or otherwise, to any intellectual property rights, is granted by this publication. Except as provided in uPI's terms and conditions of sale for such products, uPI assumes no liability whatsoever, and uPI disclaims any express or implied warranty relating to sale and/or use of uPI products, including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. uPI products are not designed, intended, authorized or warranted for use as components in systems intended for medical, life-saving, or life sustaining applications. uPI reserves the right to discontinue or make changes to its products at any time without notice.

Copyright 2022 ©, uPI Semiconductor Corp. All rights reserved. uPI, uPI design logo, and combinations thereof, are registered trademarks of uPI Semiconductor Corp.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.