**Data Sheet**

September 2003

#### **Features**

- Quad Band GSM (800/900/1800/1900 MHz) Compatible

- Dual Band IS136 (800/1900 MHz) Compatible

- · GPRS Class 12 and EDGE Capable

- Fully Integrated Dual Band Transceiver

- · Receive IF to Baseband I and Q

- Transmit Baseband I / Q to RF

- Integrated Filters

- FM Demodulator

- RF and IF Synthesizers

- Fully Programmable via serial bus

- 3 Volt operation

- · Small scale package

## **Applications**

- GAIT IS136/GSM/EDGE Mobile Telephones

- Dual Band (850/PCS1900) TDMA/AMPS Mobile Telephones

- Cellular 850MHz TDMA/AMPS Mobile Telephones

- PCS1900 TDMA Mobile Telephones

- 2.5G World Phones Quad Band (850/900/1800/1900)

- Cellular Telematic Systems

# Ordering Information

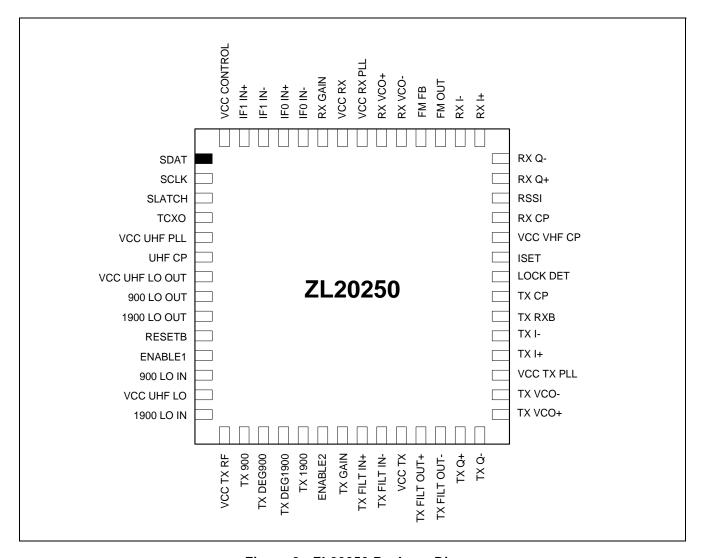

ZL20250/LCE (Tubes) 56 pin QFN ZL20250/LCF (Tape and Reel) 56 pin QFN

-40°C to +85°C

### **Description**

The ZL20250 is a fully integrated transceiver for multimode IS136/GSM/GPRS/EDGE handsets. The dual IF inputs to the receive path are amplified and down-converted to baseband I and Q signals. Gain control and baseband filtering are provided. A FM demodulator is also provided where AMPS compatibility is required.

The transmit path consists of a quadrature modulator, gain control at IF and up-conversion to RF. Dual band RF outputs are provided.

ZL20250 also includes a fractional N RF synthesizer and two IF synthesizers to provide all local oscillator signals required.

Flexible programming is provided via a 3 wire serial bus. Additional control pins allow accurate timing control when switching between modes.

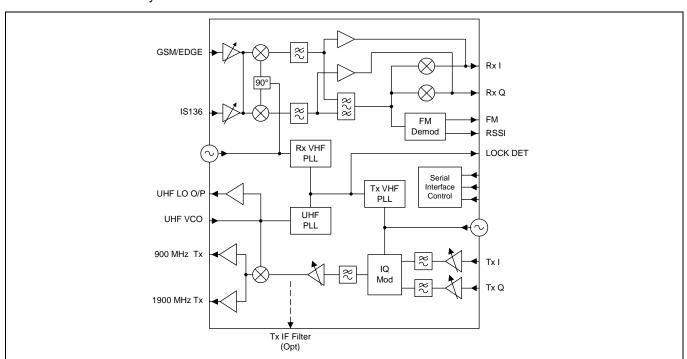

Figure 1 - Block Diagram

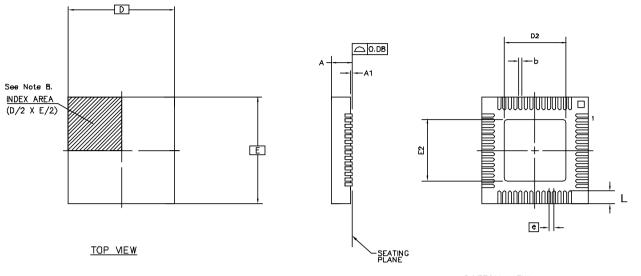

# **Package Diagram**

Figure 2 - ZL20250 Package Diagram

# **Pin Description Table**

| No | Pin Name       | Туре   | Description                                                          |

|----|----------------|--------|----------------------------------------------------------------------|

| 1  | SDAT           | Input  | Serial Interface - Data                                              |

| 2  | SCLK           | Input  | Serial interface - Clock                                             |

| 3  | SLATCH         | Input  | Serial Interface - Latch                                             |

| 4  | TCXO           | Input  | Reference input from TCXO                                            |

| 5  | VCC UHF PLL    | Power  | Power                                                                |

| 6  | UHF CP         | Output | UHF PLL Charge Pump Output                                           |

| 7  | VCC UHF LO OUT | Power  | Power to LO output stages                                            |

| 8  | 900 LO OUT     | Output | 900 MHz buffered LO output to external receiver mixer                |

| 9  | 1900 LO OUT    | Output | 1900 MHz buffered LO output to external receiver mixer               |

| 10 | RESETB         | Input  | Reset (Active low)                                                   |

| 11 | ENABLE1        | Input  | Mode Control                                                         |

| 12 | 900 LO IN      | Input  | 900 MHz LO input                                                     |

| 13 | VCC UHF LO     | Power  | Power to UHF LO input stage                                          |

| 14 | 1900 LO IN     | Input  | 1900 MHz LO input                                                    |

| 15 | VCC TX RF      | Power  | Power to transmit RF output stages                                   |

| 16 | TX 900         | Output | 900 MHz transmit output                                              |

| 17 | TX DEG900      |        | Degeneration for 900 MHz output                                      |

| 18 | TX DEG1900     |        | Degeneration for 1900 MHz output                                     |

| 19 | TX 1900        | Output | 1900 MHz transmit output                                             |

| 20 | ENABLE2        | Input  | Mode Control                                                         |

| 21 | TX GAIN        | Input  | Transmit gain control                                                |

| 22 | TX FILT IN+    | Input  | Input from transmit IF filter (optional)                             |

| 23 | TX FILT IN-    | Input  |                                                                      |

| 24 | VCC TX         | Power  | Power to transmit stages                                             |

| 25 | TX FILT OUT+   | Output | Output to transmit IF filter (optional)                              |

| 26 | TX FILT OUT-   | Output |                                                                      |

| 27 | TX Q+          | Input  | Q transmit signal from baseband                                      |

| 28 | TX Q-          | Input  |                                                                      |

| 29 | TX VCO+        |        | Transmit Oscillator tank circuit                                     |

| 30 | TX VCO-        |        |                                                                      |

| 31 | VCC TX PLL     | Power  | Power to Transmit VHF PLL                                            |

| 32 | TX I+          | Input  | I transmit signal from baseband                                      |

| 33 | TX I-          | Input  |                                                                      |

| 34 | TX RXB         | Input  | Transmit / Receive control                                           |

| 35 | TX CP          | Output | Transmit VHF PLL charge pump output                                  |

| 36 | LOCK DET       | Output | PLL Lock Detect Output                                               |

| 37 | ISET           |        | Connect 50 kohm resistor to ground to set internal reference current |

| 38 | VCC VHF CP     | Power  | Power to VHF charge pump outputs                                     |

# **Pin Description Table (continued)**

| No | Pin Name    | Туре   | Description                                                      |

|----|-------------|--------|------------------------------------------------------------------|

| 39 | RX CP       | Output | Receive VHF PLL charge pump output                               |

| 40 | RSSI        | Output | RSSI Output                                                      |

| 41 | RX Q+       | Output | Baseband Q signal                                                |

| 42 | RX Q-       | Output |                                                                  |

| 43 | RX I+       | Output | Baseband I signal                                                |

| 44 | RX I-       | Output |                                                                  |

| 45 | FM OUT      | Output | Demodulated FM output                                            |

| 46 | FM FB       |        | Feedback to FM output stage                                      |

| 47 | RX VCO-     |        | Receive second LO Oscillator tank circuit                        |

| 48 | RX VCO+     |        |                                                                  |

| 49 | VCC RX PLL  | Power  | Power to receive VHF PLL. Connect to VCC through 10 ohm resistor |

| 50 | VCC RX      | Power  | Power to receive stages                                          |

| 51 | RX GAIN     | Input  | Receive gain control                                             |

| 52 | IF0 IN-     | Input  | IF Input (0)                                                     |

| 53 | IF0 IN+     | Input  | GSM                                                              |

| 54 | IF1 IN-     | Input  | IF Input (1)                                                     |

| 55 | IF1 IN+     | Input  | IS136 Input                                                      |

| 56 | VCC CONTROL | Power  | Power to serial interface logic                                  |

# **Table of Contents**

| 1.0 General Description                                                          |    |

|----------------------------------------------------------------------------------|----|

| 1.1 Receive Path                                                                 | 9  |

| 1.1.1 IS136                                                                      | 9  |

| 1.1.2 AMPS FM                                                                    | 11 |

| 1.1.3 GSM                                                                        | 14 |

| 1.2 Transmit                                                                     | 16 |

| 1.3 UHF LO and Frequency Doubler                                                 | 19 |

| 1.4 UHF Frequency Synthesizer                                                    | 19 |

| 1.5 VHF Frequency Synthesizer                                                    | 22 |

| 1.6 Internal Clock Generation                                                    | 23 |

| 1.7 VHF VCO                                                                      | 23 |

| 1.8 Power Supply Connections                                                     | 24 |

| 2.0 Programming and Control                                                      | 25 |

| 2.1 Power Control Registers - Address 0 to 3                                     |    |

| 2.1.1 Power Control Modes - TDMA (GSM and IS136)                                 |    |

| 2.1.2 Power Control Modes - AMPS                                                 |    |

| 2.2 Operating Register Address 4                                                 |    |

| 2.3 Synthesizer Register - Address 5                                             |    |

| 2.3.1 UHF PLL and LO                                                             |    |

| 2.3.2 UHF PLL Charge Pump Current                                                |    |

| 2.3.3 Receive LO Set Up                                                          |    |

| 2.3.4 Transmit LO Set Up                                                         |    |

| 2.4 Control Register - Address 6                                                 | 35 |

| 2.4.1 IS136 Baseband Gain                                                        | 35 |

| 2.4.2 TCXO Reference Selection                                                   | 36 |

| 2.4.3 Discriminator Output Filtering                                             | 36 |

| 2.4.4 Transmit baseband Gain                                                     | 37 |

| 2.4.5 Mode Control                                                               | 37 |

| 2.5 GSM/EDGE Baseband Control Register - Address 7                               | 37 |

| 2.5.1 Q Channel Gain Adjust                                                      |    |

| 2.5.2 Baseband Offset Correction                                                 |    |

| 2.6 Test Mode Register - Address 8                                               |    |

| 2.7 UHF PLL Divider Programming Register - Address 9                             |    |

| 2.8 UHF PLL Reference Divider and Fractional N Programming Register - Address 10 |    |

| 2.9 Receive VHF PLL Divider Programming Register - Address 11                    |    |

| 2.10 Receive VHF PLL Reference Divider Programming Register - Address 12         |    |

| 2.11 Transmit VHF PLL Divider Programming Register - Address 13                  | 40 |

| 2.12 Transmit VHF PLL Reference Divider Programming Register Address 14          | 40 |

| 2.13 PLL Lock Detect & Fractional N Compensation Programming Register Address 15 |    |

| 2.13.1 Fractional N Compensation                                                 |    |

| 2.13.2 PLL Lock detect counters                                                  |    |

| 3.0 Absolute Maximum Ratings                                                     |    |

| 4.0 Operating Conditions                                                         | 41 |

| 5.0 Electrical Characteristics                                                   | 43 |

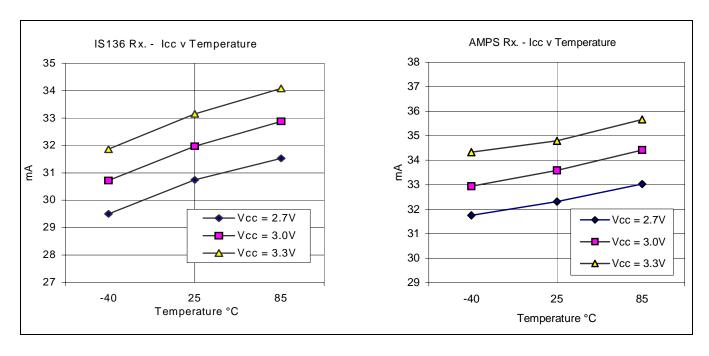

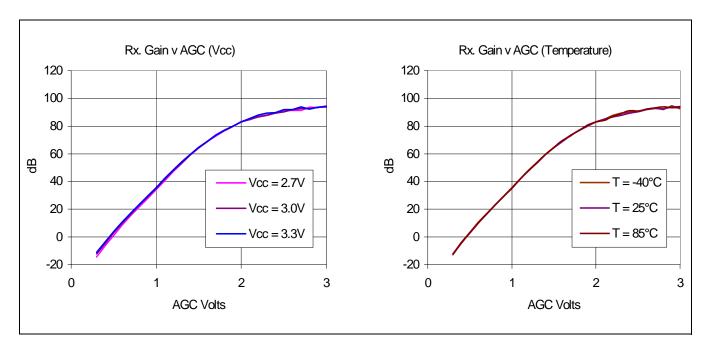

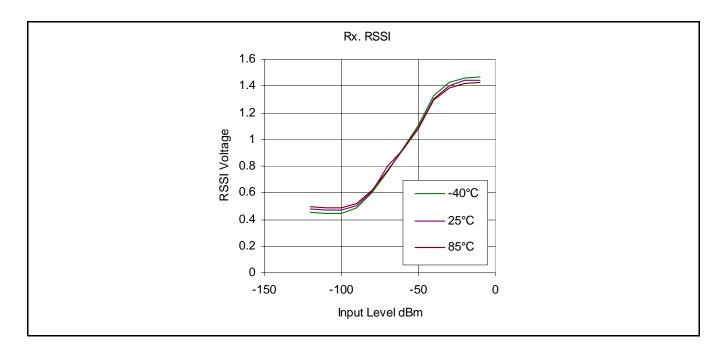

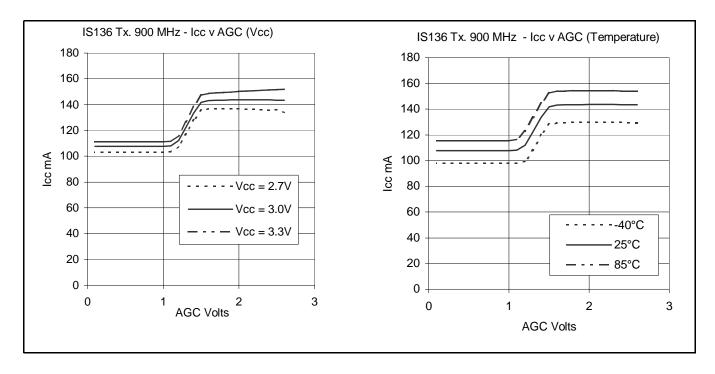

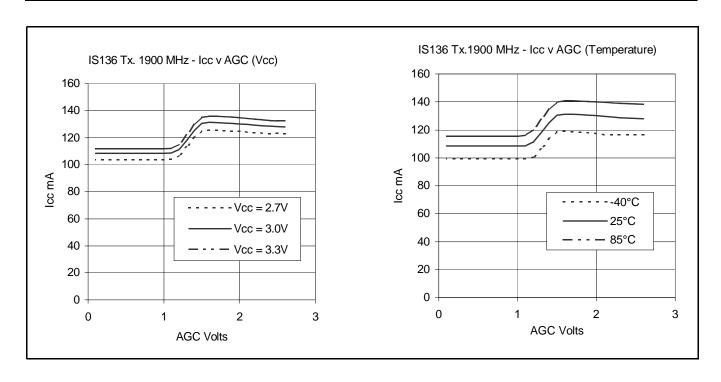

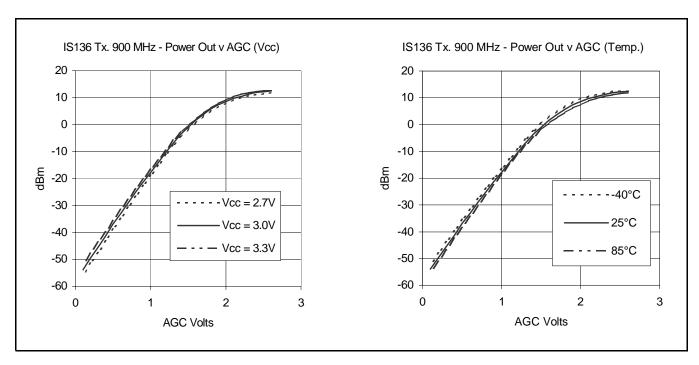

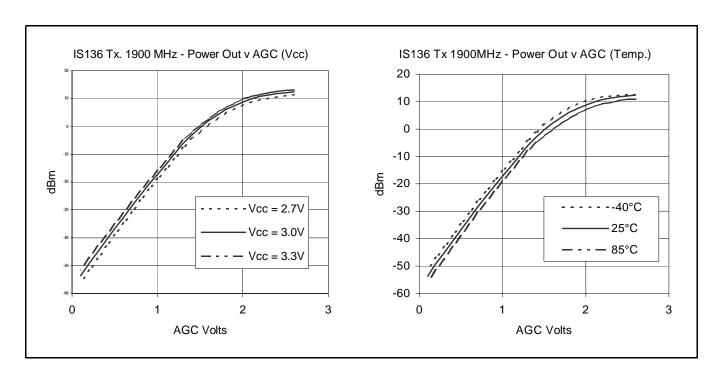

| 6.0 Typical Performance Curves                                                   | 51 |

| 6.1 Receive                                                                      |    |

| 6.2 Transmit                                                                     |    |

# ZL20250

# **List of Figures**

| Figure 1 - Block Diagram                                        | 1  |

|-----------------------------------------------------------------|----|

| Figure 2 - ZL20250 Package Diagram                              | 2  |

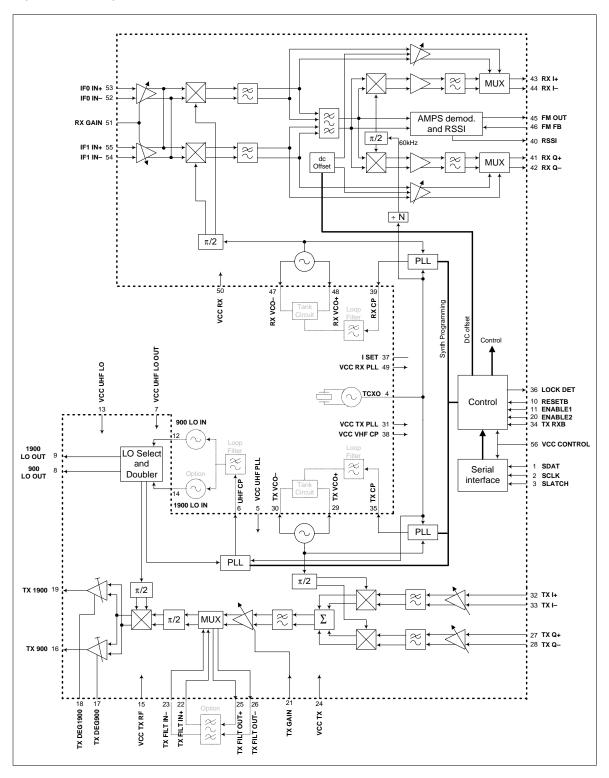

| Figure 3 - ZL20250 Detailed Block Diagram                       | 8  |

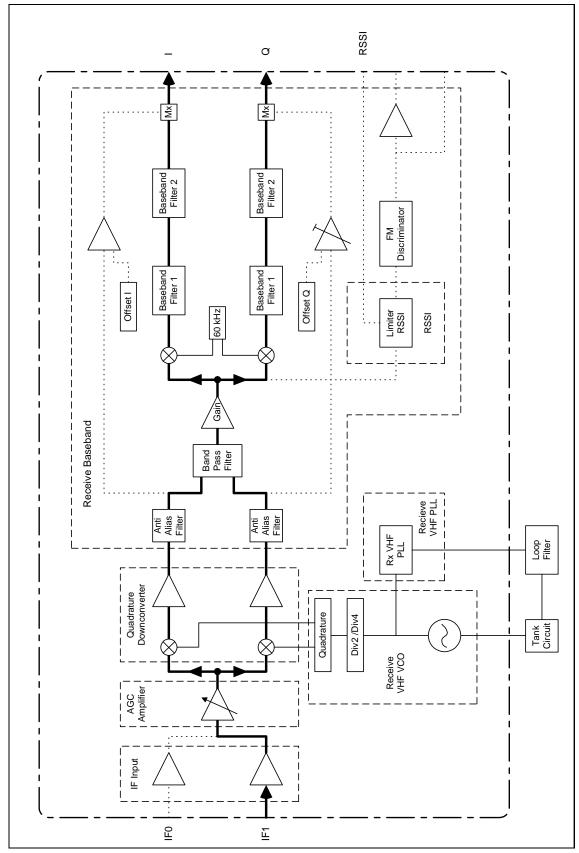

| Figure 4 - IS136 Receiver Signal Flow                           |    |

| Figure 5 - AMPS Receive Signal Flow                             | 13 |

| Figure 6 - GSM Receive Signal Flow                              |    |

| Figure 7 - Transmit Path                                        | 18 |

| Figure 8 - External Transmit IF Filter                          | 19 |

| Figure 9 - UHF Synthesizer                                      | 19 |

| Figure 10 - Count Sequence for UHF PLL with 4 modulus prescaler |    |

| Figure 11 - UHF Synthesizer - Fractional N Operation            |    |

| Figure 12 - VHF Frequency Synthesizer                           |    |

| Figure 13 - Typical VCO Tank Circuit                            |    |

| Figure 14 - Serial Bus Timing                                   |    |

| Figure 15 - Transmit Output Stage Current versus Gain Control   |    |

ZL20250

# **List of Tables**

| Table 1 - IS136 Receive Gain and Filter Distribution   | ١ |

|--------------------------------------------------------|---|

| Table 2 - AMPS FM Receive Gain and Filter Distribution | ľ |

| Table 3 - GSM Receive Gain and Filter Distribution     | 4 |

| Table 4 - Transmit Circuit blocks                      | ( |

# 1.0 General Description

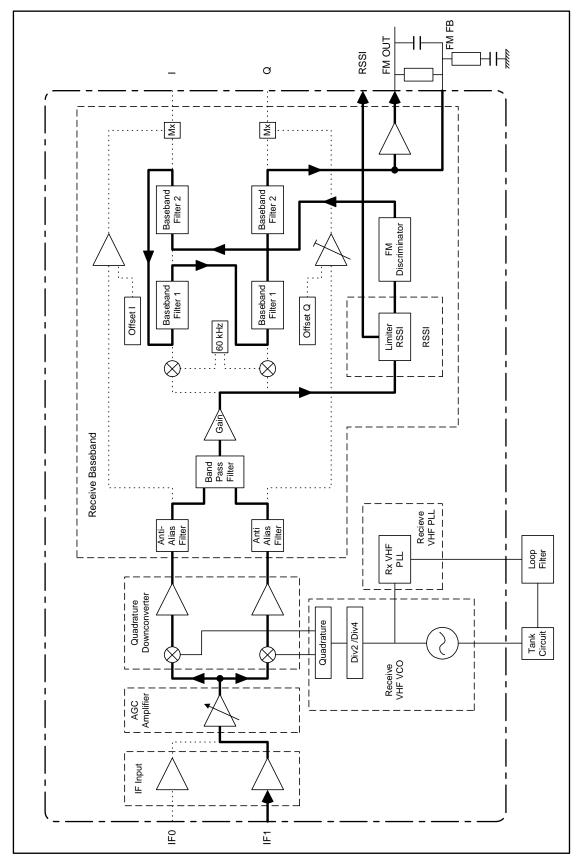

A detailed block diagram is shown in Figure 3. This shows the receive and transmit paths plus the LO generation circuitry. Control is via a serial bus with the addition of direct inputs to control receive and transmit modes and optimize power consumption.

Figure 3 - ZL20250 Detailed Block Diagram

#### 1.1 Receive Path

There are two IF inputs which will receive an input signal from IS136/AMPS and GSM IF filters. The differential input stages are identical and are followed by an agc amplifier. Gain control is provided from an external analogue voltage. After the agc amplifier the signal is then down-converted either to a low IF frequency or baseband and the signal flow then depends on the mode selected. All internal signals are differential. The LO frequency for the down conversion is derived from an on chip oscillator and PLL. The LO frequency can be programmed to be either oscillator frequency divided by 2 or 4. When in divide by 2 mode a DLL (Delay Locked Loop) circuit can be selected to maintain accurate quadrature. It is particularly important to have good quadrature in IS136/AMPS modes using a low IF frequency, to achieve the required image rejection in conjunction with the following polyphase bandpass filter. It is also possible to programme high side or low LO injection. Each receive mode will now be described in more detail

#### 1.1.1 IS136

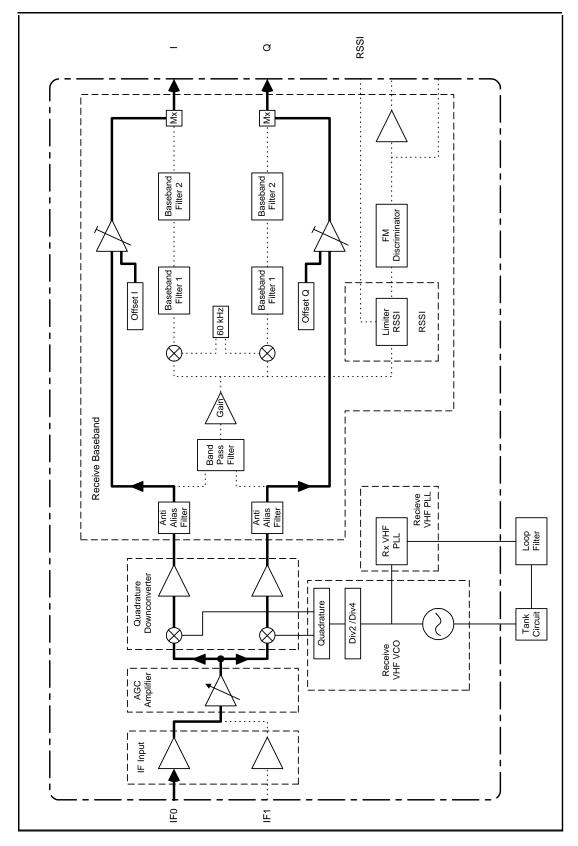

The IS136 receive signal path is shown in detail in Figure 4 and performance for each stage is summarized in the following table.

| Circuit<br>Block             | Gain<br>(dB) | Filter<br>Bandwidth<br>(If Applicable) | Description                                                                                                                                               |

|------------------------------|--------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| IF Input (IF0)               | 26           |                                        | Differential IF input stage                                                                                                                               |

| AGC Amplifier                | max          |                                        | AGC Amplifier - Gain control range 90dB                                                                                                                   |

| Quadrature<br>Down-converter | 47           |                                        | Down-conversion to 60kHz IF                                                                                                                               |

| Anti-alias filter            |              | 230 kHz                                | Low pass Butterworth (n= 3)                                                                                                                               |

| Band Pass Filter             |              | +/- 20 kHz                             | Switched capacitor polyphase Chebyshev. Also provides typically 30 dB image rejection. Centre frequency = 60 kHz. Clock frequencies 1.44 MHz and 720 kHz. |

| Gain Stage                   |              |                                        |                                                                                                                                                           |

| Baseband Down-converter      |              |                                        | Down conversion to baseband I and Q signals                                                                                                               |

| Baseband filter 1            | 7            | 37.5 kHz                               | Switched capacitor low pass Chebyshev. Clock frequency = 240 kHz                                                                                          |

| Baseband filter 2            |              | 60 kHz                                 | Smoothing filter. Low pass Butterworth                                                                                                                    |

Table 1 - IS136 Receive Gain and Filter Distribution

The output of the agc amplifier is down-converted using a quadrature mixer to a low IF of 60kHz. High side or low side LO injection can be selected. The In Phase (I) and Quadrature (Q) signals at 60 kHz are then passed through anti alias filter stage to remove any high frequency signals prior to subsequent sampling. The 60 kHz IF signals are then fed into a switched capacitor polyphase bandpass filter which not only provides filtering but also provides image rejection. This switched capacitor filter provides very stable performance and no calibration is required. After the bandpass filter the 60 kHz IF signal is further amplified and then mixed down to baseband I and Q signals. Additional filtering is required at baseband to remove spurii from the down-converter. This filtering is provide in two stages, the first stage is a switched capacitor filter with the second stage being a smoothing filter to remove clock breakthrough from the preceding switched capacitor filter. The differential baseband outputs can then be fed directly into analogue to digital converters on a baseband processor.

Figure 4 - IS136 Receiver Signal Flow

#### 1.1.2 AMPS FM

FM demodulation can be performed using the I and Q baseband signals if supported by the baseband. However the ZL20250 also contains an FM demodulator, the AMPS receive signal path using this mode is shown in detail in Figure 5 and performance for each stage is summarized in the following table.

| Circuit<br>Block                 | Gain<br>(dB) | Filter<br>Bandwidth<br>(If Applicable) | Description                                                                                                                                              |

|----------------------------------|--------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| IF Input (IF0)                   | 200          |                                        | Differential IF input stage                                                                                                                              |

| AGC Amplifier                    | 26<br>max    |                                        | AGC Amplifier - Gain control range 90dB. Includes IF input stage gain.                                                                                   |

| Quadrature<br>Down-converter     |              |                                        | Down-conversion to 60kHz IF                                                                                                                              |

| Anti-alias filter                |              | 230 kHz                                | Low pass Butterworth                                                                                                                                     |

| Band Pass Filter                 | 73           | +/- 16 kHz                             | Switched capacitor polyphase Chebyshev. Also provides typically 30dB image rejection. Centre frequency = 60 kHz. Clock frequency 1.44 MHz and 720 kHz.   |

| Limiter                          |              |                                        | Provides limited output to discriminator. Also provides RSSI output.                                                                                     |

| FM Discriminator                 |              |                                        | Digital FM discriminator                                                                                                                                 |

| Baseband filter 2 (I<br>Channel) |              | 30 kHz                                 | Smoothing filter. Low pass Butterworth. Provides filtering of FM discriminator output.                                                                   |

| Baseband filter 1<br>(I Channel) |              | 25 kHz                                 | Switched capacitor low pass Chebyshev. Clock frequency = 240 kHz. Provides additional filtering of discriminator output. Selected using PDF and LPC bits |

| Baseband filter 1<br>(Q Channel) |              | 25 kHz                                 | Switched capacitor low pass Chebyshev. Clock frequency = 240 kHz. Provides additional filtering of discriminator output. Selected using PDF and LPC bits |

| Baseband filter 2 (Q<br>Channel) |              | 60kHz                                  | Smoothing filter. Low pass Butterworth. Provides filtering of FM discriminator output.                                                                   |

| FM Output                        |              | 30kHz                                  | Configured using external components as bandpass filter.                                                                                                 |

Table 2 - AMPS FM Receive Gain and Filter Distribution

The signal path is initially the same as for IS136 with the down conversion to 60 kHz and channel filtering in the bandpass filter. In FM mode however, the baseband I and Q output stages are disabled, and the 60 kHz IF signal from the bandpass filter is input to a limiting amplifier and FM discriminator. The FM discriminator consists of a shift register acting as a delay line. The output of the discriminator is a digital signal which must then be filtered to recover the audio signal. The discriminator output is therefore routed through the baseband I and Q filters. The default condition is to use the cascaded I and Q smoothing filters (baseband filter 2) with the cut-off frequency set to 30kHz. This connection is automatically selected when programming FM mode. There is an option to use the cascaded switched capacitor filters (baseband filter 1) with the cut off frequency set to 25 kHz to provide extra filtering. These filters are selected using the PDF and LPC bits in control register 6 and are inserted between the smoothing filters as shown in Figure 5. The final output stage uses external feedback components to provide a bandpass filter with a bandwidth of at least 300 Hz to 10 KHz to cover the demodulated audio and control signals. The feedback components can be modified to change the output level to optimise compatibility with baseband.

A RSSI output is provided. This is a full wave rectified output of the 60 kHz IF and therefore has a high 120 kHz content. This requires an external low pass filter - typically 10kohm and 2.7nF. There is a trade-off between settling

time and filtering. This is different to conventional RSSI circuits which operate at typically 450 kHz which is much easier to filter.

Although the AMPS receive path includes a limiting amplifier, gain control is also required. This is because the band pass filter has limited dynamic range (50dB). At low signal levels the agc should be set to 1.6 volts to set the gain 20dB below maximum to obtain optimum signal handling and noise performance. At higher signal levels the gain setting should be reduced to maintain the RSSI level approximately 10dB below maximum. Gain control would be provided by the baseband controller which would also monitor the RSSI level. Fine gain control is not required and can be implemented in large steps eg 20dB, allowing the use of a relatively slow gain control loop giving optimum performance under fading conditions.

Figure 5 - AMPS Receive Signal Flow

#### 1.1.3 GSM

The GSM receive signal path is shown in detail in Figure 6 and performance for each stage is summarized in the following table.

| Circuit<br>Block             | Gain<br>(dB) | Filter<br>Bandwidth<br>(If Applicable) | Description                                                                                            |

|------------------------------|--------------|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| IF Input (IF0)               |              |                                        | Differential IF input stage                                                                            |

| AGC Amplifier                | 26<br>max    |                                        | AGC Amplifier - Gain control range 90dB. Includes IF input stage gain.                                 |

| Quadrature<br>Down-converter | - 1          |                                        | Down-conversion to baseband                                                                            |

| Anti-alias filter            | 54           | 230 kHz                                | Low pass Butterworth. Provides channel filtering in GSM/EDGE mode                                      |

| Baseband Gain                |              |                                        | Baseband gain with offset correction.  Nominal gain is 35 dB and can be reduced in 3 dB steps to 14 dB |

Table 3 - GSM Receive Gain and Filter Distribution

In GSM mode the bandpass filter and IS136 baseband stages are disabled. After passing through the agc amplifier the signal is mixed down to baseband I and Q signals rather than to a low IF. The baseband signal must be dc coupled and this can introduce a dc offset in the output, which may vary with different gain settings. The ZL20250 therefore includes the facility to correct the dc offset for each channel using an 8 bit offset correction word that must be supplied by the baseband via the serial bus.

GSM Baseband gain can be programmed via serial bus. Reducing the baseband gain can be used to improve output signal to noise ratio. The IF gain should be increased to maintain the total overall gain. In practice a gain reduction of 6 or 9 dB would give optimum performance

Figure 6 - GSM Receive Signal Flow

#### 1.2 Transmit

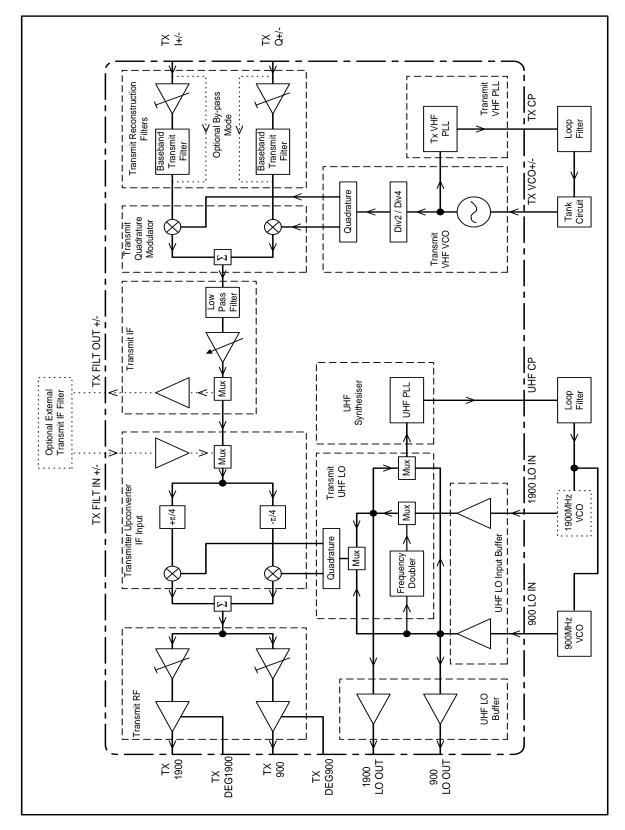

Transmit operation is similar for all modes and a detailed diagram is shown in Figure 7. This diagram also shows the UHF LO generation circuit blocks. A summary of the characteristics of the transmit path circuit blocks are given in the table below. All circuit blocks are differential with the exception of the transmit RF outputs.

| Circuit<br>Block       | Gain<br>(dB) | Bandwidth<br>(If Applicable)             | Description                                                                                                                                                                                                                                                                                      |

|------------------------|--------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reconstruction Filters | 0 -12        | IS136/AMPS<br>12.5 kHz<br>GSM<br>100 kHz | Baseband input stage. Gain is programmable in 3 dB steps from 0 to 12 dB. Filter bandwidth is selected for IS136/AMPS or GSM. There is also a by-pass mode so that the baseband I and Q signal can go direct to the modulator                                                                    |

| Quadrature Modulator   |              |                                          | Generates a modulated IF signal                                                                                                                                                                                                                                                                  |

| Transmit IF            |              | 400 MHz                                  | Provides gain control at IF frequency. This stage also includes a low pass filter to remove harmonics and spurii from modulator output. This stage also includes a buffered IF output which can be used with an external IF filter.                                                              |

| Up-converter           |              |                                          | SSB up-converter to RF frequency. The IF path includes phase shift networks for the up-converter. This stage also includes the input circuit from the optional external IF filter                                                                                                                |

| Transmit RF            |              |                                          | The 900 MHz and 1900 MHz RF stages each consist of 2 stages. The first stage gain be set from -6 to +3 dB in 3 dB steps. Output stage current is controlled by agc signal to reduce current consumption at low output power levels. Each output stage requires an external degeneration inductor |

**Table 4 - Transmit Circuit blocks**

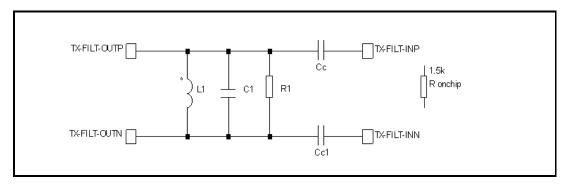

Differential baseband transmit I and Q signals from a baseband processor are input to the ZL20250. The baseband signals are passed through filters - the filter bandwidth is selected for the appropriate mode i.e. IS136 or GSM. A quadrature modulator modulates these baseband signals on to the transmit IF which is typically around 200 MHz. This modulated IF signal is passed through an on chip low pass filter which removes harmonics of the IF and then into a gain controlled amplifier. This amplifier is controlled by an external analogue signal and provides greater than 60dB gain control The output of the gain controlled amplifier can then be up-converted to RF or alternatively the output can be sent to an off chip filter to provide further filtering and removal of noise before up-conversion. This filter is a parallel tuned circuit as shown in Figure 8. The choice of component values is dependent on the IF frequency being used. The filter output is then fed back on chip to the up-converter. A SSB mixer is used for the up-conversion to remove the unwanted image. High side or low side LO injection can be selected

A buffer amplifier after the up-conversion provides a further 9 dB gain control in 3 dB increments. This gain is programmable via the serial bus and can be used to optimize noise and linearity performance in particular applications. Finally there are two RF output stages for 900 MHz and 1900 MHz frequency bands. Each RF output is single ended and requires a simple matching network. The supply current of the output stages is automatically reduced at low transmit gain control voltages improving the efficiency of the output buffer at low output power levels. The supply current of the output buffer can also be controlled via the serial bus. This allows the supply current to be reduced which is particularly useful when using AMPS or GSM where the linearity performance is less critical.

The FM modulation for AMPS can be done using I,Q modulation if available. Alternatively FM modulation can be applied direct to the transmit IF VCO. The loop bandwidth for the transmit VHF PLL should be low ( ~100 Hz) to ensure the PLL does not remove the modulation. A dc voltage should be applied across the Tx I+, Tx I- and the Tx Q+, Tx Q- inputs to switch the modulator and generate an IF carrier signal. With a baseband gain of 0dB a dc voltage of at least 1.5 volts should be applied; a lower voltage can be used with the baseband gain increased to compensate. It is assumed that this bias can be provided by the baseband however if this is not possible then the simplest solution is to connect 200kohm resistors between I+, Q+ inputs and Vcc and 200kohm resistors between I+,Q- inputs and

ground assuming the transmit outputs from the baseband are in a high impedance state in AMPS mode. These resistors do produce a small dc offset in TDMA mode however this is insignificant if the output impedance of baseband transmit outputs is less than 1 kohm. As the FM modulation is applied direct to the VCO in this mode and is external to the ZL20250, any necessary filtering of the FM signal must be provided externally.

Figure 7 - Transmit Path

Figure 8 - External Transmit IF Filter

#### 1.3 UHF LO and Frequency Doubler

Figure 8 also shows the UHF LO buffering and frequency doubler. The ZL20250 is designed to operate either with separate external UHF VCOs for the 900 and 1900 MHz frequency bands, or alternatively a single 900 MHz VCO can be used with the on-chip frequency doubler providing the LO for the 1900 MHz band. A UHF synthesizer is included. The input to the UHF synthesizer will normally be the active UHF LO signal, however when using the frequency doubler mode for 1900 MHz LO generation, the synthesizer input can be selected to be either the frequency doubler output or the 900 MHz input LO signal. The UHF LO input buffer minimizes any load pulling effects on the UHF VCO when internal modes are switched.

UHF LO output buffers are also provided. These can be used to drive an external mixer for the receive section. If not required these buffers can be powered down.

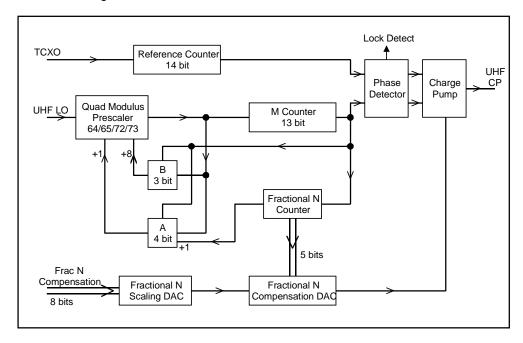

#### 1.4 UHF Frequency Synthesizer

A fractional N UHF synthesizer is included on the ZL20250 to provide LO signals for the transmit up-converter and the external receive RF down-converters. The UHF synthesizer operates with an external VCO. A block diagram of the synthesizer is shown in Figure 9.

Figure 9 - UHF Synthesizer

The synthesizer uses a 4 modulus prescaler with an 'M' counter and 'A' and 'B' swallow counters together with a fractional N counter in the UHF counter allowing maximum flexibility. The reference counter is a simple 14 bit counter. All counter values are programmed via the serial bus and programming details are shown in the programming section. Each of the counters operates as count down. At the start of a count the counters are loaded with their respective values. The initial prescaler ratio is dependent on the values loaded into the A and B counters; when both the A and B counters reach zero the prescaler ratio is 64 and then remains until the M counter reaches zero. The complete process is then repeated.

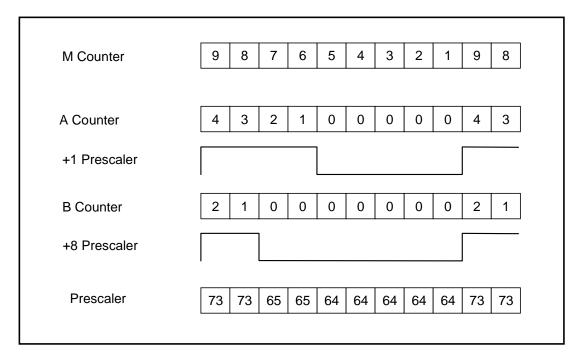

This can be shown in a simple example where M = 9, A = 4 and B = 2 which gives a total divide ratio of 596. The count sequence is shown in Figure 10.

Figure 10 - Count Sequence for UHF PLL with 4 modulus prescaler

At the start of the count sequence the '+1' and '+8' controls to the prescaler are both asserted and the prescaler ratio is 73. After 2 cycles only the '+1' control is asserted and the divide ratio is 65. After a further 2 cycles the A counter reaches zero as well and the prescaler ratio is 64 for the remainder of the count sequence. At the end of the sequence all counters are reloaded and the sequence repeats.

The total divide ratio (N) for this type of counter is given by

N = 64\*M + 8\*B + A

M is always greater then A or B

A value of A = 0 does not support fractional N operation. Valid values of A are 1 to 8.

The values of M, B and A can be easily calculated from the total divide ratio as shown below.

M = INT ((N - 1)/64)

B = INT (((N - 1) - 64\*M)/8)

A = N - 64\*M - 8\*B

The value of M must always be greater than A or B. The maximum value of B is 7.

The UHF synthesizer also includes a fractional N capability which allows the use of higher comparison frequencies but maintain narrow channel spacing. The use of higher comparison frequencies allows faster loop settling and reduces comparison spur level. This is particularly important in TDMA mode where settling times of < 1.5 ms are required and still obtain good spur performance.

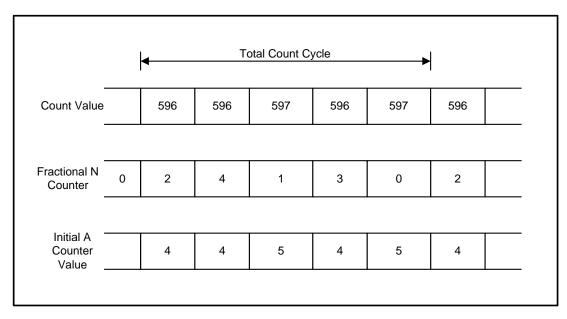

Fractional N allows the use of non-integer divide ratios. For example if the total divide ratio is N + 1/5 the counter will divide by N for 4 count cycles and N+1 on the fifth cycle giving the required total divide ratio over five cycles. The ZL20250 can use 5,8,13 or 20 as the fractional denominator (also referred to as the fractional modulus) allowing maximum flexibility in the choice of comparison frequencies.

An extra counter - fractional N counter - is required. The input to this counter is from the M counter output. The fractional N modulus can be programmed to be 5,8,13, or 20. Each output pulse from the M counter will increment the fractional N divided by the required fractional numerator. For example if the fraction is 2/5 then the fractional N counter will increment by 2 for each output pulse from the M counter. When the fractional N counter overflows the A counter is incremented by 1, thus generating an additional '+1' count sequence.

An example is shown in Figure 11 for a divide ratio of 596+2/5. The values for M, A, B are calculated using the integer value (596) as in the previous example. The fractional denominator is programmed as 5 and the fractional numerator as 2. At the end of the first count cycle (596) the fractional counter is incremented to 2. At the end of the third count cycle the fractional N counter overflows, incrementing the A counter by 1 which gives a subsequent count cycle of 597. After five count cycles the sequence repeats with a total count of 2982 over the five count cycle giving a mean value of 596 + 2/5.

Figure 11 - UHF Synthesizer - Fractional N Operation

A result of this count sequence is that the output phase of the total counter changes through the count cycle, which causes the output pulse from the phase detector, and therefore the charge pump, to vary. This would cause large fractional spurs on the synthesizer output. These spurs can be compensated by applying a current pulse with the opposite polarity to the charge pump output. This compensation pulse has a fixed width of two reference clock (TCXO) periods; the amplitude is proportional to the value in the fractional N counter. The correction current is scaled by a 8 bit compensation DAC, with an externally provided input from the serial bus. This allows performance to be optimized in a given application.

The compensation value can be calculated from the following formula:

Comp Value = 255 - INT((Icp \* Ftcxo)/(0.0245 \* 6 \* MOD \*Fvco))

where

lcp = charge pump current (uA)

Ftcxo = Reference frequency

MOD = Fractional Modulus

Fvco = UHF VCO Frequency

The synthesizer provides a lock detect output. When the output pulse from the phase detector is less than half a reference clock period an in-lock signal is generated. These in-lock signals then clock a 4 bit counter into which a threshold value has been programmed. When the required number of successive in-lock pulses have been generated the lock detect output is set.

The ZL20250 has a single lock detect output pin for the UHF synthesizer and VHF synthesizers. The lock detect signal is asserted when all active synthesizers are in lock. If a synthesizer has not been enabled in the power control registers then that synthesizer will be inactive and will have no effect on the lock detect output.

#### 1.5 VHF Frequency Synthesizer

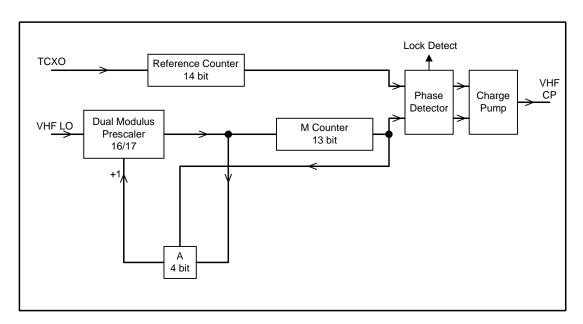

The ZL20250 includes two VHF synthesizers to generate the second LO for the receiver and the transmit IF. They operate with their respective on-chip VHF VCO's and off-chip loop filters. The tank circuits and tuning components for the VCO's are also off chip. The two synthesizers are identical and are shown in Figure 12.

Figure 12 - VHF Frequency Synthesizer

The synthesizer uses a 2 modulus 16/17 prescaler with an 'M' counter and an 'A' swallow counter. This allows maximum flexibility when using this synthesizer. The reference counter is a simple 14 bit counter. All counter values are programmed via the serial bus and programming details are shown in the programming section. Both counters operate as count down. At the start of a count the counters are loaded with their respective values. The initial

prescaler ratio is 17 assuming A > 0; when the A counter reaches zero the prescaler ratio is 16 until the M counter reaches zero. The complete process is then repeated.

The total divide ratio (N) for this type of counter is given by

N = 16\*M + A

M is always greater then A

The values of M and A can be easily calculated from the total divide ratio N.

M = INT (N/16)

A = N - 16\*M

The maximum value for A is 15 and M must always be greater than A.

The VHF PLLs do not have fractional N capability however it is recommended that thay are operated at as high a comparison frequency as allowed by the chosen frequency plan to minimise spurs levels.

Both VHF synthesizers have lock detection circuits. These operate in the same way as described for the UHF synthesizer.

#### 1.6 Internal Clock Generation

ZL20250 can use 14.4 MHz or 19.44MHz reference frequency (standard for IS136), or 13 MHz or 26 MHz (standard for GSM). The appropriate reference must be programmed via the serial bus. The clock signals for the switched capacitor filters and FM demodulator are generated from the reference TCXO signal. The internal divide ratios are switched to give the optimum ratio. For dual mode applications (GSM/IS136) a 13 MHz or 26 MHz reference should be used. This will give a small error in the switched capactor clock frequency used for IS136 but has negligible effect on performance.

### 1.7 VHF VCO

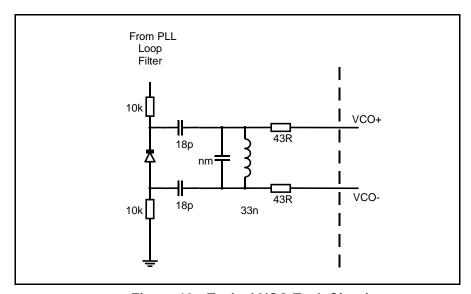

ZL20200 has two VHF VCOs which operate with the VHF PLLs to provide the IF LO signals for both receive and transmit IF signals. The oscillators are a differential design and require an external tank circuit. A basic circuit with varactor is shown in Figure 13. It is recommended to include series resistors (eg 43 ohms) in each arm of the tank circuit to prevent any spurious high frequency oscillation due to parasitic capacitances.

Figure 13 - Typical VCO Tank Circuit

## 1.8 Power Supply Connections

The circuit blocks within ZL20250 have separate supply connections to minimize interaction between circuit blocks. Details are shown in the earlier 'Pin Names' section. These supplies are also grouped to allow different groups of supply pins to be connected to separate supplies for example, receive or transmit. These groups are shown below:

| VCC – Control Supply |                |  |

|----------------------|----------------|--|

| Pin No.              | Pin Name       |  |

| 56                   | VCC CONTROL    |  |

| VCC – TxRx Com       | mon (Synth)    |  |

| Pin No.              | Pin Name       |  |

| 5                    | VCC UHF PLL    |  |

| 7                    | VCC UHF LO OUT |  |

| 13                   | VCC UHF LO     |  |

| 38                   | VCC VHF CP     |  |

| 8                    | 900 LO OUT     |  |

| 9                    | 1900 LO OUT    |  |

| VCC – Rx             |                |  |

| Pin No.              | Pin Name       |  |

| 49                   | VCC RX PLL     |  |

| 50                   | VCC RX         |  |

| VCC – Tx             |                |  |

| Pin No.              | Pin Name       |  |

| 15                   | VCC TX RF      |  |

| 24                   | VCC TX         |  |

| 31                   | VCC TX PLL     |  |

| 16                   | TX 900         |  |

| 19                   | TX 1900        |  |

The LO OUT and TX 900/1900 pins require bias and are normally connected to VCC through an inductor.

All supply pins within a group must be powered together. Each group of pins can be powered up independent of the other groups.

# 2.0 Programming and Control

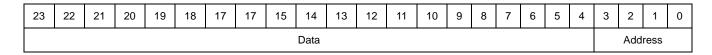

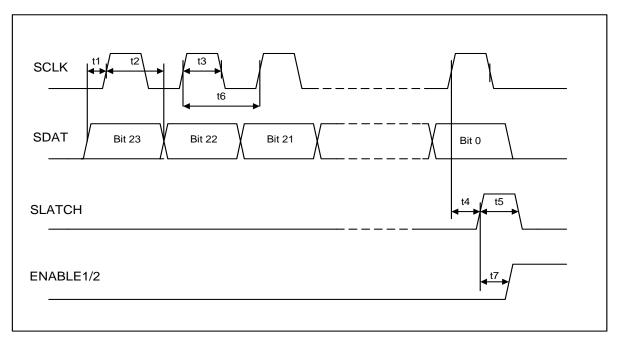

Programming via the serial bus is via 24 bit words with a 4 bit address as shown below

Bit23 (MSB) is loaded first. Bits 3:0 are used as address bits for the control registers. Details of serial bus timing are shown in Figure 14.

Figure 14 - Serial Bus Timing

## 2.1 Power Control Registers - Address 0 to 3

These registers are used in conjunction with the TX RXB and ENABLE1 and ENABLE2 control pins to power up the required sections of the device for any required mode. This enables power consumption to be optimized under all conditions. Figures 4 - 7, which show the receive and transmit paths in detail, show which sections are powered up by each control bit.

The assignment is common for each of the registers 0 to 3 and is shown below.

| Bit | Circuit Section          |

|-----|--------------------------|

| 23  | Not used                 |

| 22  | Receive Baseband section |

| 21  | UHF LO Buffer            |

| 20  | Receive VHF VCO          |

| Bit | Circuit Section                   |

|-----|-----------------------------------|

| 19  | UHF synthesizer                   |

| 18  | Receive RSSI circuit              |

| 17  | Not used                          |

| 16  | Receive Quadrature down-converter |

| 15  | Receive VHF PLL                   |

| 14  | Receive IF input                  |

| 13  | Receive AGC amplifier             |

| 12  | Transmit reconstruction filters   |

| 11  | Transmit RF                       |

| 10  | Transmit UHF LO                   |

| 9   | UHF LO input buffer               |

| 8   | Transmit IF                       |

| 7   | Transmit quadrature modulator     |

| 6   | Transmit VHF PLL                  |

| 5   | Transmit VHF VCO                  |

| 4   | Transmit up-converter IF input    |

Note 1: If a bit is set to logic 1 then that circuit section is powered on.

Note 2: UHF LO input (bit 9) must be enabled for Transmit UHF LO (bit 10), UHF synthesizer (bit 19) and UHF LO Buffer (bit 21) to be active.

The 4 registers address 0 to 3 are assigned as follows:

| Register<br>Address | Register<br>Name         | Description                                                                                                                                                                                                                                                                                             |

|---------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                   | Receive                  | All circuit blocks required in receive mode should be set to 1. This register will be selected when TX RXB is low. No circuits will be actually powered up if ENABLE1 and ENABLE 2 are both low.                                                                                                        |

| 1                   | Transmit                 | Transmit register All circuit blocks required in transmit mode should be set to 1. In duplex modes e.g. AMPS then both receive and transmit circuits must be selected. This register will be selected when TX RXB is high. No circuits will be actually powered up if ENABLE1 and ENABLE 2 are both low |

| 2                   | ENABLE1<br>Configuration | This register determines which circuit sections are powered up when ENABLE1 is high. The contents of this register are logical ANDed with the contents of the Receive or Transmit register as selected by TX RXB input.                                                                                 |

| 3                   | ENABLE2<br>Configuration | This register determines which circuit sections are powered up when ENABLE2 is high. The contents of this register are logical ANDed with the contents of the Receive or Transmit register as selected by TX RXB input.                                                                                 |

A feature of this programming approach is that once a phone operating mode has been selected and set up via the serial bus, all power control can then be via the TX RXB, ENABLE1 and ENABLE2 control pins. Alternatively full power control is possible via the 3 wire serial bus without the use of any external control pins.

If ENABLE1 and ENABLE2 are both low then the device is in Sleep mode. No circuits will be enabled unless either ENABLE1 or ENABLE2 are high regardless of the contents of the receive and transmit registers.

An example of how these control bits can be used, is that the oscillators and PLL circuits can be powered up and allowed to settle prior to powering up the complete transmit or receive path. In the case of the receive path the UHF synthesizer, UHF LO input buffer, UHF LO Buffer and Receive VHF VCO, Receive VHF PLL bits would be set in the ENABLE1 Configuration register. The ENABLE2 Configuration register would contain these bits plus the remainder of the receive path bits, Receive IF input, Receive AGC amplifier, Receive quadrature down-converter and receive baseband section.

This is demonstrated in the following examples.

## 2.1.1 Power Control Modes - TDMA (GSM and IS136)

In a TDMA system the transceiver will either operate in receive only, or transmit only mode. It is assumed that an interim power on state will be used during which the oscillators and PLLs will be set up, and allowed to settle prior to activating the full signal path. The suggested programming for the power control registers (0 - 3) is shown in the table below.

| Bit | Circuit<br>Section                | Receive<br>Addr 0 | Transmit<br>Addr 1 | Enable 1<br>Config.<br>Addr 2 | Enable 2<br>Config.<br>Addr 3 | Comments |

|-----|-----------------------------------|-------------------|--------------------|-------------------------------|-------------------------------|----------|

| 23  | Not used                          | 0                 | 0                  | 0                             | 0                             |          |

| 22  | Receive Baseband section          | 1                 | 0                  | 0                             | 1                             |          |

| 21  | UHF LO Buffer                     | 0                 | 0                  | 0                             | 0                             | Note 1   |

| 20  | Receive VHF VCO                   | 1                 | 0                  | 1                             | 1                             |          |

| 19  | UHF synthesizer                   | 1                 | 1                  | 1                             | 1                             |          |

| 18  | Receive RSSI circuit              | 0                 | 0                  | 0                             | 0                             | Note 2   |

| 17  | Not used                          | 0                 | 0                  | 0                             | 0                             |          |

| 16  | Receive Quadrature down-converter | 1                 | 0                  | 0                             | 1                             |          |

| 15  | Receive VHF PLL                   | 1                 | 0                  | 1                             | 1                             |          |

| 14  | Receive IF input                  | 1                 | 0                  | 0                             | 1                             |          |

| 13  | Receive AGC amplifier             | 1                 | 0                  | 0                             | 1                             |          |

| 12  | Transmit reconstruction filters   | 0                 | 1                  | 0                             | 1                             |          |

| 11  | Transmit RF                       | 0                 | 1                  | 0                             | 1                             |          |

| 10  | Transmit UHF LO                   | 0                 | 1                  | 0                             | 1                             |          |

| 9   | UHF LO input buffer               | 1                 | 1                  | 1                             | 1                             |          |

| 8   | Transmit IF                       | 0                 | 1                  | 0                             | 1                             |          |

| 7   | Transmit quadrature modulator     | 0                 | 1                  | 0                             | 1                             |          |

| 6   | Transmit VHF PLL                  | 0                 | 1                  | 1                             | 1                             |          |

| Bit | Circuit<br>Section               | Receive<br>Addr 0 | Transmit<br>Addr 1 | Enable 1<br>Config.<br>Addr 2 | Enable 2<br>Config.<br>Addr 3 | Comments |

|-----|----------------------------------|-------------------|--------------------|-------------------------------|-------------------------------|----------|

| 5   | Transmit VHF VCO                 | 0                 | 1                  | 1                             | 1                             |          |

| 4   | 4 Transmit up-converter IF input |                   | 1                  | 0                             | 1                             |          |

Note 1: Not required if driving external receive mixer direct from UHF VCO.

Note 2: Can be used for IS136 if required.

The receive register contains all bits required when in receive mode: the transmit register contains all bits required in transmit mode. The Enable1 configuration register contains all bits required to power up oscillators and synthesizers in both receive and transmit mode. The Enable2 configuration register contains all bits required to power up the complete receive and transmit modes (this register can be set to all '1's if preferred).

The following words should therefore be programmed on the serial bus (Hex format):

Receive register (0) 59E200 Transmit register (1) 081FF1 Enable1 Config. register (2) 188262 Enable2 Config. register (3) 59FFF3

#### 2.1.2 Power Control Modes - AMPS

When operating in AMPS mode the ZL20250 will operate in either Receive only or Duplex. The enable registers should therefore be programmed as shown below.

| Bit | Circuit Section                   | Receive<br>Addr 0 | Transmit<br>Addr 1 | Enable 1<br>Config.<br>Addr 2 | Enable 2<br>Config.<br>Addr 3 | Comments |

|-----|-----------------------------------|-------------------|--------------------|-------------------------------|-------------------------------|----------|

| 23  | Not used                          | 0                 | 0                  | 0                             | 0                             |          |

| 22  | Receive Baseband section          | 1                 | 1                  | 0                             | 1                             |          |

| 21  | UHF LO Buffer                     | 0                 | 0                  | 0                             | 0                             | Note 1   |

| 20  | Receive VHF VCO                   | 1                 | 1                  | 1                             | 1                             |          |

| 19  | UHF synthesizer                   | 1                 | 1                  | 1                             | 1                             |          |

| 18  | Receive RSSI circuit              | 1                 | 1                  | 0                             | 1                             |          |

| 17  | Not used                          | 0                 | 0                  | 0                             | 0                             |          |

| 16  | Receive Quadrature down-converter | 1                 | 1                  | 0                             | 1                             |          |

| 15  | Receive VHF PLL                   | 1                 | 1                  | 1                             | 1                             |          |

| 14  | Receive IF input                  | 1                 | 1                  | 0                             | 1                             |          |

| 13  | Receive AGC amplifier             | 1                 | 1                  | 0                             | 1                             |          |

| 12  | Transmit reconstruction filters   | 0                 | 1                  | 0                             | 1                             |          |

| 11  | Transmit RF                       | 0                 | 1                  | 0                             | 1                             |          |

| 10  | Transmit UHF LO                   | 0                 | 1                  | 0                             | 1                             |          |

| 9   | UHF LO input buffer               | 1                 | 1                  | 1                             | 1                             |          |

| 8   | Transmit IF                       | 0                 | 1                  | 0                             | 1                             |          |

| Bit | Circuit Section                 | Receive<br>Addr 0 | Transmit<br>Addr 1 | Enable 1<br>Config.<br>Addr 2 | Enable 2<br>Config.<br>Addr 3 | Comments |

|-----|---------------------------------|-------------------|--------------------|-------------------------------|-------------------------------|----------|

| 7   | 7 Transmit quadrature modulator |                   | 1                  | 0                             | 1                             |          |

| 6   | 6 Transmit VHF PLL              |                   | 1                  | 1                             | 1                             |          |

| 5   | Transmit VHF VCO                | 0                 | 1                  | 1                             | 1                             |          |

| 4   | Transmit up-converter IF input  | 0                 | 1                  | 0                             | 1                             |          |

Note 1: Not required if driving external receive mixer direct from UHF VCO.

The receive register contains all bits required when in receive mode: the transmit register contains all bits required in duplex mode. The Enable1 configuration register contains all bits required to power up oscillators and synthesizers in both receive and duplex mode. The Enable2 configuration register contains all bits required to power up the complete receive and duplex modes (this register can be set to all '1's if preferred).

The following words should therefore be programmed on the serial bus (Hex format):

Receive register (0) 5DE200

Transmit register (1) 5DFFF1

Enable1 Config. register (2) 188262

Enable2 Config. register (3) 5DFFF3

#### 2.2 Operating Register Address 4

This registers selects internal setups for example IS136 or GSM. The bits are assigned for control of receive and transmit bits as shown below:

| 23 | 22 | 21 | 20     | 19    | 18 | 17 | 16 | 15 | 14              | 13 | 12 | 11 | 10 | 9   | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|--------|-------|----|----|----|----|-----------------|----|----|----|----|-----|------|---|---|---|---|---|---|---|---|

|    |    |    | RX<    | 7:0>  |    |    |    |    | TX <11:0>       |    |    |    |    | 0   | 1    | 0 | 0 |   |   |   |   |   |   |

|    |    | R  | eceive | Set U | р  |    |    |    | Transmit Set Up |    |    |    |    | Add | ress |   |   |   |   |   |   |   |   |

The function of the receive bits is shown below:

| Register<br>Bit No. | Control<br>Bit | Action if '0'                         | Action if '1'                        |

|---------------------|----------------|---------------------------------------|--------------------------------------|

| 23                  | RX<7>          | Receive DLL disabled                  | Receive DLL enabled                  |

| 22                  | RX<6>          | Bandpass Filter BW = +/- 20 kHz       | Bandpass Filter BW = +/- 16 kHz      |

| 21                  | RX<5>          | GSM Filters active                    | Receive GSM filters bypassed         |

| 20                  | RX<4>          | LO output = 900 MHz                   | LO Output = 1900 MHz                 |

| 19                  | RX<3>          | Receive output dc bias (I/Q) = 1.25 V | Receive output dc bias (I/Q) = Vcc/2 |

| 18                  | RX<2>          | IS136 Mode IF1 Input enabled          | GSM Mode IF0 Input enabled           |

| 17                  | RX<1>          | AMPS                                  | IS136                                |

| 16                  | RX<0>          | Not used                              | Not used                             |

Bit 23 RX<7> is only applicable when VCO divide by 2 mode is selected in register 5.

The function of the transmit bits is shown below:

| Register Bit<br>No. | Control<br>Bit | Action if '0'                                                                 | Action if '1'                       |

|---------------------|----------------|-------------------------------------------------------------------------------|-------------------------------------|

| 15                  | TX<11>         | Transmit output stage gain control                                            |                                     |

| 14                  | TX<10>         |                                                                               |                                     |

| 13                  | TX<9>          | Control of RF Transmit output stage c<br>Nominal value for TX<11:4> is 101010 |                                     |

| 12                  | TX<8>          |                                                                               |                                     |

| 11                  | TX<7>          |                                                                               |                                     |

| 10                  | TX<6>          |                                                                               |                                     |

| 9                   | TX<5>          |                                                                               |                                     |

| 8                   | TX<4>          |                                                                               |                                     |

| 7                   | TX<3>          | 900 MHz output                                                                | 1900MHz output                      |

| 6                   | TX<2>          | Internal                                                                      | External transmit IF Filter         |

| 5                   | TX<1>          | IS136 baseband filters                                                        | GSM/EDGE baseband filters           |

| 4                   | TX<0>          | Transmit baseband filters selected                                            | Transmit baseband filters by-passed |

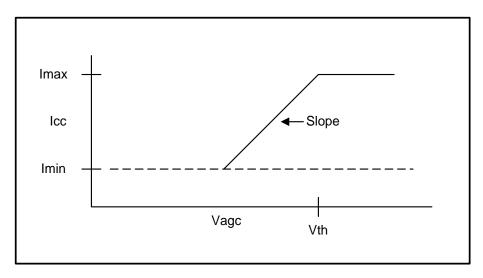

Control bits TX<11:4> allow optimization of the transmit output stage. This allows variation of the decrease in supply current with decreasing agc voltage and also allows optimization depending on output power and linearity requirements. Figure 15 shows the variation of output stage supply current with agc voltage and the programmable characteristics. The maximum current, agc threshold and slope can be programmed. The minimum current is not programmable.

TX<11:10> (bits 15,14) allow the gain of the transmit output stage to be varied in 3 dB steps as shown in the table below:

| TX<11> | TX<10> | Gain (dB) |

|--------|--------|-----------|

| 0      | 0      | -6        |

| 0      | 1      | -3        |

| 1      | 0      | Nominal   |

| 1      | 1      | +3        |

Figure 15 - Transmit Output Stage Current versus Gain Control

TX<9:8> (bits 13:12) control the agc voltage (Vth) at which the output stage current starts reducing. Typical values are shown in the table below:

| TX<9> | TX<8> | Vth (V) |

|-------|-------|---------|

| 0     | 0     | 1.09    |

| 0     | 1     | 1.25    |

| 1     | 0     | 1.48    |

| 1     | 1     | 2.81    |

TX<7:6> (bits 11,10) control the rate of current reduction as shown in Figure 15. Typical vales are shown in the below:

| TX<7> | TX<6> | Slope (mA/V) |

|-------|-------|--------------|

| 0     | 0     | 8.5          |

| 0     | 1     | 10.5         |

| 1     | 0     | 12.0         |

| 1     | 1     | 14.0         |

TX<5:4> (bits 9:8) adjust the maximum current (Imax) of the transmit output stage. The gain of the output stage is not changed. Typical values are shown in the table below:

| TX<5> | TX<4> | Current |

|-------|-------|---------|

| 0     | 0     | 25%     |

| 0     | 1     | 50%     |

| 1     | 0     | Nominal |

| 1     | 1     | 150%    |

Using these controls allows the performance of the output stage to be optimized under various conditions; for example, current cant can be reduced if non-linear operation is required.

The nominal value recommended for TX<11:4> is 10101010.

An example of setting up the control register (address 4) for various systems is shown below:

| Bit | Name   | GSM<br>(850) | GSM<br>(1900) | IS136<br>(900) | IS136<br>(1900) | AMPS | Comments |

|-----|--------|--------------|---------------|----------------|-----------------|------|----------|

| 23  | RX<7>  | 0            | 0             | 0              | 0               | 0    |          |

| 22  | RX<6>  | 0            | 0             | 0              | 0               | 1    |          |

| 21  | RX<5>  | 0            | 0             | 0              | 0               | 0    |          |

| 20  | RX<4>  | 0            | 1             | 0              | 1               | 0    |          |

| 19  | RX<3>  | 0            | 0             | 0              | 0               | 0    | Note 1   |

| 18  | RX<2>  | 1            | 1             | 0              | 0               | 0    |          |

| 17  | RX<1>  | 0            | 0             | 1              | 1               | 0    |          |

| 16  | RX<0>  | 0            | 0             | 1              | 1               | 1    |          |

| 15  | TX<11> | 1            | 1             | 1              | 1               | 1    |          |

| 14  | TX<10> | 0            | 0             | 0              | 0               | 0    |          |

| 13  | TX<9>  | 1            | 1             | 1              | 1               | 1    |          |

| 12  | TX<8>  | 0            | 0             | 0              | 0               | 0    |          |

| 11  | TX<7>  | 1            | 1             | 1              | 1               | 1    |          |

| 10  | TX<6>  | 0            | 0             | 0              | 0               | 0    |          |

| 9   | TX<5>  | 1            | 1             | 1              | 1               | 1    |          |

| 8   | TX<4>  | 0            | 0             | 0              | 0               | 0    |          |

| 7   | TX<3>  | 0            | 1             | 0              | 1               | 0    |          |

| 6   | TX<2>  | 0            | 1             | 0              | 1               | 0    | Note 2   |

| Bit | Name  | GSM<br>(850) | GSM<br>(1900) | IS136<br>(900) | IS136<br>(1900) | AMPS | Comments |

|-----|-------|--------------|---------------|----------------|-----------------|------|----------|

| 5   | TX<1> | 1            | 1             | 0              | 0               | 0    |          |

| 4   | TX<0> | 0            | 0             | 0              | 0               | 0    |          |

Note 1: The setting for RX<3> is dependent on the optimum common mode input voltage of the analog to digital converter in the baseband.

The following hex words are therefore recommended for the control register (address 4):

| GSM (850)    | 04AA24 |

|--------------|--------|

| GSM (1900)   | 4AAE4  |

| IS136 (900)  | 03AA04 |

| IS136 (1900) | 13AAC4 |

| AMPS         | 41AA04 |

#### 2.3 Synthesizer Register - Address 5

This register sets up LO options for receive and transmit and also UHF synthesizer set up.

| 23 | 22 | 21   | 20     | 19    | 18 | 17 | 16 | 15 | 14 | 13           | 12 | 11 | 10             | 9 | 8 | 7 | 6 | 5       | 4 | 3 | 2 | 1 | 0 |

|----|----|------|--------|-------|----|----|----|----|----|--------------|----|----|----------------|---|---|---|---|---------|---|---|---|---|---|

|    |    |      |        |       |    |    | 0  |    |    |              |    |    |                |   |   |   |   |         | 0 | 1 | 0 | 1 |   |

| UI |    | RX L | .O2 Se | et Up |    | UC |    | DL | UD | TX LO Set Up |    |    | UHF PLL Set Up |   |   |   |   | Address |   |   |   |   |   |

Bits 23,17,14 are also used for UHF PLL and LO set up.

Bits 16,15 are not used and should be set to zero.

#### 2.3.1 UHF PLL and LO

| Register<br>Bit No. | Action if '0'                              | Action if '1'                      |  |  |  |  |

|---------------------|--------------------------------------------|------------------------------------|--|--|--|--|

| 23                  | UHF PLL input = 900 MHz                    | UHF PLL input = 1900 MHz           |  |  |  |  |

| 17                  |                                            | Fractional N Compensation selected |  |  |  |  |

| 14                  |                                            | UHF Doubler Selected               |  |  |  |  |

| 8                   | Fractional N Denominator - see table below |                                    |  |  |  |  |

| 7                   |                                            |                                    |  |  |  |  |

| 6                   | Not Used - Set to 0                        |                                    |  |  |  |  |

| 5                   | UHF PLL Charge Pump Current - see tab      | ple below                          |  |  |  |  |

| 4                   |                                            |                                    |  |  |  |  |

Note 1:

Bit 14 is only effective if 1900 MHz mode has been selected (register 4 Bit 7).

Bit 23 is only effective if 1900 MHz mode has been selected (register 4 Bit 7) and the UHF frequency doubler selected (Register 5 Bit 14). This control allows the use of the doubled frequency to be used as the input to the UHF PLL.

Fractional N Denominator Note 2:

Note 4: Bits 8,7 select the fractional N denominator for the UHF PLL as shown below:

Note 2: Selects external transmit IF filter if used.

Data Sheet

| <8> | <7> | Frac N Denom. |

|-----|-----|---------------|

| 0   | 0   | 5             |

| 0   | 1   | 8             |

| 1   | 0   | 13            |

| 1   | 1   | 20            |

# 2.3.2 UHF PLL Charge Pump Current

Bits 5,4 select the charge pump current for the UHF PLL as shown below:

| <5> | <4> | Current (mA) |

|-----|-----|--------------|

| 0   | 0   | 1.00         |

| 0   | 1   | 0.50         |

| 1   | 0   | 0.25         |

| 1   | 1   | 0.125        |

# 2.3.3 Receive LO Set Up

| Register Bit No. | Action if '0'                                         | Action if '1'                          |  |  |  |  |

|------------------|-------------------------------------------------------|----------------------------------------|--|--|--|--|

| 22               | High side Rx second LO injection                      | Low side Rx second LO injection        |  |  |  |  |

| 21               | Rx second LO = VCO/2                                  | Rx second LO = VCO/4                   |  |  |  |  |

| 20               | Rx LO phase detector polarity normal                  | Rx LO phase detector polarity inverted |  |  |  |  |

| 19               | Receive VHF PLL Charge Pump Current - see table below |                                        |  |  |  |  |

| 18               |                                                       |                                        |  |  |  |  |

Bits 19,18 select the charge pump current for the receive VHF PLL as shown below:

| <19> | <18> | Current (mA) |

|------|------|--------------|

| 0    | 0    | 1.00         |

| 0    | 1    | 0.50         |

| 1    | 0    | 0.25         |

| 1    | 1    | 0.125        |

## 2.3.4 Transmit LO Set Up

| Register<br>Bit No. | Action if '0'                                          | Action if '1'                          |  |  |  |  |

|---------------------|--------------------------------------------------------|----------------------------------------|--|--|--|--|

| 15                  | Transmit DLL disabled                                  | Transmit DLL enabled                   |  |  |  |  |

| 13                  | Low side Tx up-converter LO injection                  | High side Tx up-converter LO injection |  |  |  |  |

| 12                  | Tx second LO = VCO/2                                   | Tx second LO = VCO/4                   |  |  |  |  |

| 11                  | Tx LO phase detector polarity normal                   | Tx LO phase detector polarity inverted |  |  |  |  |

| 10                  | Transmit VHF PLL Charge Pump Current - see table below |                                        |  |  |  |  |

| 9                   |                                                        |                                        |  |  |  |  |

Bits 10,9 select the charge pump current for the receive VHF PLL as shown below:

| <10> | <9> | Current (mA) |

|------|-----|--------------|

| 0    | 0   | 1.00         |

| 0    | 1   | 0.50         |

| 1    | 0   | 0.25         |

| 1    | 1   | 0.125        |

# 2.4 Control Register - Address 6

| 23 | 22           | 21 | 20          | 19 | 18 | 17 | 16 | 15           | 14 | 13 | 12 | 11 | 10 | 9       | 8 | 7 | 6 | 5 | 4       | 3 | 2 | 1 | 0 |

|----|--------------|----|-------------|----|----|----|----|--------------|----|----|----|----|----|---------|---|---|---|---|---------|---|---|---|---|

| 0  |              |    |             |    | 0  |    |    |              |    |    |    |    |    |         |   |   |   |   | 0 1 1 0 |   |   |   |   |

|    | BBG TCXO PDF |    | LPC Tx Gain |    |    |    | R  | Mode Control |    |    |    |    |    | Address |   |   |   |   |         |   |   |   |   |

#### 2.4.1 IS136 Baseband Gain

Bits 22:21 can be used to vary the gain of the baseband output stages in IS136 mode only. The gain of the 60 kHz IF stage preceding the baseband mixer is also varied so that the overall gain of the device can be maintained if required. The nominal gain is 20 dB and the recommended setting is BBG<1:0> = 11 to minimize output dc offsets.

| BBG<1><br>Bit 22 | BBG<0><br>Bit 21 | IF Gain<br>(dB) | Baseband Gain<br>(dB) | Overall Gain<br>(dB) |

|------------------|------------------|-----------------|-----------------------|----------------------|

| 0                | 0                | 14              | 6                     | 20                   |

| 0                | 1                | 17              | 6                     | 23                   |