MARCH 2004 REV. P1.0.0

#### **REGISTER MANUAL**

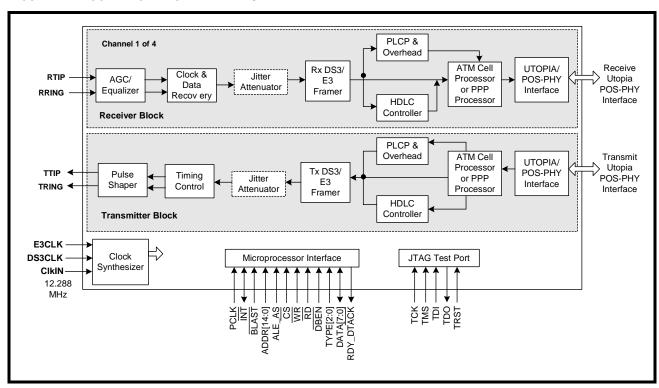

The XRT79L74 is a four channel, ATM UNI/PPP Physical Layer Processor with integrated DS3/E3 framing controllers and Line Interface Units with Jitter Attenuators that are designed to support ATM direct mapping and cell delineation as well as PPP mapping and Frame processing. For ATM UNI applications, this device provides the ATM Physical Layer (Physical Medium Dependent and Transmission Convergence sub-layers) interface for the public and private networks at DS3/E3 rates. For Clear-Channel Framer applications, this device supports the transmission and reception of "user data" via the DS3/E3 payload.

The XRT79L74 includes DS3/E3 Framing, Line Interface Unit with Jitter Attenuator that supports mapping of ATM or HDLC framed data. A flexible parallel microprocessor interface is provided for configuration and control. Industry standard UTOPIA II and POS-PHY interface are also provided.

#### **GENERAL FEATURES:**

- Integrated T3/E3 Line Interface Unit

- Integrated Jitter Attenuator that can be selected either in Receive or Transmit path

- Flexible integrated Clock Multiplier that takes single frequency clock and generates either DS3 or E3 frequency.

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- HDLC Controller that provides the mapping/ extraction of either bit or byte mapped encapsulated packet from DS3/E3 Frame.

- Contains on-chip 16 cell FIFO (configurable in depths of 4, 8, 12 or 16 cells), in both the Transmit (TxFIFO) and Receive Directions (RxFIFO)

- Contains on-chip 54 byte Transmit and Receive OAM Cell Buffer for transmission, reception and processing of OAM Cells

- Supports ATM cell or PPP Packet Mapping

- Supports M13 and C-Bit Parity Framing Formats

- Supports DS3/E3 Clear-Channel Framing.

- Includes PRBS Generator and Receiver

- Supports Line, Cell, and PLCP Loop-backs

- Interfaces to 8 Bit wide Intel, Motorola or PowerPC

- Low power 3.3V, 5V Input Tolerant, CMOS

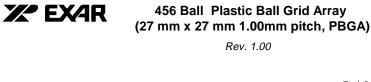

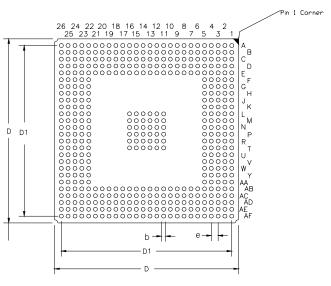

- Available in 456 Lead PBGA Package

- JTAG Interface

#### LINE INTERFACE UNIT

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3 Jitter Tolerance Requirements

- Detects and Clears LOS as per G.775.

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- Compliant with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE,1995 standards

- Meets ETSI TBR 24 and GR-499 Jitter Transfer Requirements

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- On chip advanced crystal-less Jitter Attenuator

- Jitter Attenuator can be selected in Receive or Transmit paths

- 16 or 32 bits selectable FIFO size

- Meets the Jitter and Wander specifications described in T1.105.03b,ETSI TBR-24, Bellcore GR-253 and GR-499 standards

- Jitter Attenuator can be disabled

- Maximum power consumption 3.1W

#### **DS3/E3 FRAMER**

- DS3 framer supports both M13 and C-bit parity.

- DS3 framer meets ANSI T1.107 and T1.404 standards.

- Detects OOF,LOF,AIS,RDI/FERF alarms.

- Generation and Insertion of FEBE on received parity errors supported.

- Automatic insertion of RDI/FERF on alarm status.

- E3 framer meets G.832, G.751 standards.

- Framers can be bypassed.

#### ATM/PPP PROTOCOL PROCESSOR

#### TRANSMIT CELL PROCESSING

- Extracts ATM cells

- Supports ATM cell payload scrambling

- Maps ATM cells into E3 or DS3 frame

- PLCP frame and mapping of ATM cell streams

#### RECEIVE CELL PROCESSING

- Extraction of ATM cells from PLCP frame or directly from E3 or DS3 frame

- Termination of PLCP frame

- Supports payload cell de-scrambling

#### TRANSMIT PACKET PROCESSING

- Inserts PPP packets into data stream

- Maps HDLC data stream directly into DS3 or E3 frame

- Extracts in-band messaging packets

- Supports CRC-16/32, HDLC flag and Idle sequence generation

#### RECEIVE PACKET PROCESSING

- Extracts HDLC data stream from DS3 or E3 frame

- Inserts in-band messaging packets

- Detects and removes HDLC flags

#### **UTOPIA/ SYSTEM INTERFACE**

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- Compliant with ATM Forum UTOPIA II interface

- Programmable FIFO size for both Transmit and Receive direction

- Compliant to POS-PHY Level 2 interface

#### SERIAL INTERFACE

- Serial clock and data interface for accessing DS3/ E3 framer

- Serial clock and data interface for accessing cell/ packet processor

#### **APPLICATIONS**

- Digital Access and Cross Connect Systems

- 3G Base Stations

- DSLAMs

- Digital, ATM, WAN and LAN Switches

#### FIGURE 1. BLOCK DIAGRAM OF THE XRT79L74

#### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE  | OPERATING TEMPERATURE RANGE |

|----------------|---------------|-----------------------------|

| XRT79L74IB     | 456 Lead PBGA | -40°C to +85°C              |

# **X** EXAR

# TABLE OF CONTENTS

| REGISTER MANUAL                                                                                                           | 1           |

|---------------------------------------------------------------------------------------------------------------------------|-------------|

| GENERAL FEATURES:                                                                                                         | 1           |

| Line Interface Unit                                                                                                       | 1           |

| DS3/E3 Framer                                                                                                             |             |

| ATM/PPP PROTOCOL PROCESSOR                                                                                                | 1           |

| Transmit Cell Processing                                                                                                  | 1           |

| Receive Cell Processing                                                                                                   |             |

| Transmit Packet Processing                                                                                                |             |

| Receive Packet Processing                                                                                                 |             |

| Utopia/ System Interface                                                                                                  |             |

| Serial Interface                                                                                                          |             |

| APPLICATIONS                                                                                                              |             |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT79L74                                                                                   |             |

| PRODUCT ORDERING INFORMATION                                                                                              |             |

| TABLE OF CONTENTS                                                                                                         |             |

| REGISTER MAP OF THE XRT79L74                                                                                              | 4           |

| COMMONCONTROL REGISTERS OF THE XRT79L74                                                                                   | 4           |

| CLEAR-CHANNEL FRAMER BLOCK REGISTERS                                                                                      | 5           |

| LIU/JITTER ATTENUATOR CONTROL REGISTERS                                                                                   |             |

| RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS                                                          |             |

| OPERATION BLOCK INTERRUPT REGISTER BIT FORMATS                                                                            |             |

| OPERATION CONTROL REGISTER - BYTE 3 (ADDRESS = 0x0100)                                                                    |             |

| OPERATION CONTROL REGISTER - BYTE 3 (ADDRESS = 0x0100)                                                                    |             |

| OPERATION CONTROL REGISTER - BYTE 2 (ADDRESS = 0X0101)  OPERATION CONTROL - LOOP-BACK CONTROL REGISTER (ADDRESS = 0X0102) |             |

| OPERATION CONTROL - LOOP-BACK CONTROL REGISTER (ADDRESS = 0X0102)  OPERATION CONTROL REGISTER - BYTE 0 (ADDRESS = 0X0103) |             |

|                                                                                                                           |             |

| DEVICE ID REGISTER (ADDRESS = 0x0104)                                                                                     |             |

| REVISION ID REGISTER (ADDRESS = 0x0105)                                                                                   |             |

| OPERATION INTERRUPT STATUS REGISTER - BYTE 1 (ADDRESS = 0x0112)                                                           |             |

| OPERATION INTERRUPT STATUS REGISTER - BYTE 0 (ADDRESS = 0x0113)                                                           |             |

| OPERATION INTERRUPT ENABLE REGISTER - BYTE 1 (ADDRESS = 0x0116)                                                           |             |

| OPERATION INTERRUPT ENABLE REGISTER - BYTE 0 (ADDRESS = 0x0117)                                                           |             |

| CHANNEL INTERRUPT INDICATION REGISTERS                                                                                    |             |

| CHANNEL INTERRUPT INDICATOR - RECEIVE CELL PROCESSOR/PPP PROCESSOR BLOCK (ADDRESS                                         | = 0x0119)25 |

| CHANNEL INTERRUPT INDICATOR - LIU/JITTER ATTENUATOR BLOCK (ADDRESS = 0x011D)                                              | 26          |

| CHANNEL INTERRUPT INDICATOR - TRANSMIT CELL PROCESSOR/PPP PROCESSOR BLOCK (ADDRES 26                                      | S = 0x0121) |

| CHANNEL INTERRUPT INDICATOR - DS3/E3 FRAMER BLOCK (ADDRESS = 0x0127)                                                      | 27          |

| OPERATION GENERAL PURPOSE PIN DATA REGISTER (ADDRESS = 0x0147)                                                            |             |

| OPERATION GENERAL PURPOSE PIN DIRECTION CONTROL REGISTER (ADDRESS = 0x014B)                                               |             |

| RECEIVE UTOPIA INTERFACE BLOCK                                                                                            |             |

| TABLE 1: RECEIVE UTOPIA/POS-PHY INTERFACE BLOCK - REGISTER/ADDRESS MAP                                                    |             |

| RECEIVE UTOPIA/POS-PHY CONTROL REGISTER - BYTE 0 (ADDRESS = 0x0503)                                                       |             |

| RECEIVE UTOPIA PORT ADDRESS REGISTER (ADDRESS = 0x0513)                                                                   |             |

| RECEIVE UTOPIA FORT ADDRESS REGISTER (ADDRESS = 0x0515)                                                                   |             |

|                                                                                                                           |             |

| TRANSMIT UTOPIA INTERFACE BLOCK                                                                                           |             |

| TABLE 2: TRANSMIT UTOPIA INTERFACE BLOCK - REGISTER/ADDRESS MAP                                                           |             |

| ,                                                                                                                         |             |

| TRANSMIT UTOPIA PORT ADDRESS REGISTER (ADDRESS = 0x0593)                                                                  |             |

| TRANSMIT UTOPIA PORT NUMBER REGISTER (ADDRESS = 0x0597)                                                                   |             |

| LIU/JITTER ATTENUATOR CONTROL REGISTER BIT-FORMAT                                                                         |             |

| LIU TRANSMIT APS/REDUNDANCY CONTROL REGISTER (ADDRESS = 0XN300)                                                           |             |

| LIU INTERRUPT ENABLE REGISTER (ADDRESS = 0xn301)                                                                          |             |

| LIU INTERRUPT STATUS REGISTER (ADDRESS = 0xn302)                                                                          | 40          |

| 4 CHAMILE DOGLE AIM CHANT I COMBO IC                       | NEV. 1 1.0.0 |

|------------------------------------------------------------|--------------|

| LIU ALARM STATUS REGISTER (ADDRESS = 0XN303)               | 42           |

| LIU TRANSMIT CONTROL REGISTER (ADDRESS = 0XN304)           |              |

| LIU RECEIVE CONTROL REGISTER (ADDRESS = 0XN305)            | 47           |

| LIU CHANNEL CONTROL REGISTER (ADDRESS = 0XN306)            | 49           |

| JITTER ATTENUATOR CONTROL REGISTER (ADDRESS = 0xn307)      | 50           |

| LIU RECEIVE APS/REDUNDANCY CONTROL REGISTER (ADDRESS = 0XN | 308) 51      |

| ORDERING INFORMATION                                       | 52           |

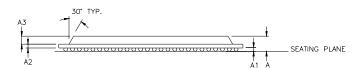

| PACKAGE DIMENSIONS                                         | 52           |

| REVISION HISTORY                                           | 53           |

|                                                            |              |

# **EXAR**

### **REGISTER MAP OF THE XRT79L74**

The register map is divided into two main sections, Common Control Registers and Channel Control Registers. The Channel Control Registers are addressed by the MSB of the address bus A[14:13]. These two bits determine which channel is to be accessed. In this document, n is used in place of the channel number where:

Channel 1 (n = 1)

Channel 2 (n = 2)

Channel 3 (n = 3)

Channel 4 (n = 4)

### COMMONCONTROL REGISTERS OF THE XRT79L74

| Address Location | REGISTER NAME                                                             | Туре | DEFAULT<br>VALUE |

|------------------|---------------------------------------------------------------------------|------|------------------|

|                  | COMMON CONTROL REGISTERS                                                  | •    |                  |

| 0x0100           | Operation Control Register - Byte 3                                       | R/W  | 0x00             |

| 0x0101           | Operation Control Register - Byte 2                                       | R/W  | 0x00             |

| 0x0102           | Operation Control Register - Byte 1                                       | R/W  | 0x00             |

| 0x0103           | Operation Control Register - Byte 0                                       | R/W  | 0x00             |

| 0x0104           | Device ID Register                                                        | R/W  | TBD              |

| 0x0105           | Revision ID Register                                                      | R/W  | 0x01             |

| 0x0106 - 0x0111  | Reserved                                                                  |      |                  |

| 0x0112           | Operation Block Interrupt Status Register - Byte 1                        | RO   | 0x00             |

| 0x0113           | Operation Block Interrupt Status Register - Byte 0                        | RO   | 0x00             |

| 0x0114 - 0x0115  | Reserved                                                                  |      |                  |

| 0x0116           | Operation Block Interrupt Enable Register - Byte 1                        | R/W  | 0x00             |

| 0x0117           | Operation Block Interrupt Enable Register - Byte 0                        | R/W  | 0x00             |

| 0x0118           | Reserved                                                                  |      |                  |

| 0x0119           | Channel Interrupt Indicator - Receive Cell Processor/PPP Processor Block  | R/O  | 0x00             |

| 0x011A - 0x011C  | Reserved                                                                  |      |                  |

| 0x011D           | Channel Interrupt Indicator - LIU/Jitter Attenuator Block                 | R/O  | 0x00             |

| 0x011E - 0x0120  | Reserved                                                                  |      |                  |

| 0x0121           | Channel Interrupt Indicator - Transmit Cell Processor/PPP Processor Block | R/O  | 0x00             |

| 0x0122 - 0x0126  | Reserved                                                                  |      |                  |

| 0x0127           | Channel Interrupt Indicator - DS3/E3 Framer Block - Byte 0                | R/O  | 0x00             |

| 0x0128 - 0x0146  | Reserved                                                                  |      |                  |

| 0x0147           | Operation General Purpose Input/Output Register                           | R/W  | 0x00             |

| 0x0148 - 0x014A  | Reserved                                                                  |      |                  |

# COMMONCONTROL REGISTERS OF THE XRT79L74

| Address Location | REGISTER NAME                                             | Түре | DEFAULT<br>VALUE |

|------------------|-----------------------------------------------------------|------|------------------|

|                  | COMMON CONTROL REGISTERS                                  |      |                  |

| 0x014B           | Operation General Purpose Input/Output Direction Register | R/W  | 0x00             |

| 0x014C - 0x04FF  | Reserved                                                  |      |                  |

| 0x0501           | Receive POS-PHY Control Register - Byte 1                 | R/W  | 0x00             |

| 0x0502           | Receive POS-PHY Control Register - Byte 0                 | R/W  | 0x00             |

| 0x0503           | Receive UTOPIA Control Register                           | R/W  | 0x00             |

| 0x0504 - 0x0512  | Reserved                                                  |      |                  |

| 0x0513           | Receive UTOPIA Port Address Register                      | R/W  | 0x00             |

| 0x0514 - 0x0516  | Reserved                                                  |      |                  |

| 0x0517           | Receive UTOPIA Port Number Register                       | R/W  | 0x00             |

| 0x0518 - 0x0580  | Reserved                                                  |      |                  |

| 0x0581           | Transmit POS-PHY Control Register - Byte 1                | R/W  | 0x00             |

| 0x0582           | Transmit POS-PHY Control Register - Byte 0                | R/W  | 0x00             |

| 0x0583           | Transmit UTOPIA Control Register                          | R/W  | 0x00             |

| 0x0584 - 0x0592  | Reserved                                                  |      |                  |

| 0x0593           | Transmit UTOPIA Port Address Register                     | R/W  | 0x00             |

| 0x0594 - 0x0596  | Reserved                                                  |      |                  |

| 0x0597           | Transmit UTOPIA Port Number Register                      | R/W  | 0x00             |

| Address Location | REGISTER NAME                                  | Түре | DEFAULT<br>VALUE |

|------------------|------------------------------------------------|------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER) |      |                  |

|                  | CLEAR-CHANNEL FRAMER BLOCK REGISTERS           |      |                  |

| 0xn100           | Operating Mode Register                        | R/W  | 0x2B             |

| 0xn101           | I/O Control Register                           | R/W  | 0xA4             |

| 0xn102 - 0xn103  | Reserved                                       |      |                  |

| 0xn104           | Block Interrupt Enable Register                | R/W  | 0x00             |

| 0xn105           | Block Interrupt Status Register                | R/O  | 0x00             |

| 0xn106 - 0xn10B  | Reserved                                       |      |                  |

| 0xn10C           | DS3 Test Register                              | R/W  | 0x00             |

| 0xn10D           | Payload HDLC Control Register                  | R/W  | 0x00             |

| 0xn10E - 0xn10F  | Reserved                                       |      |                  |

**X** EXAR

| Address Location | REGISTER NAME                                                                                     | Түре         | DEFAULT<br>VALUE |

|------------------|---------------------------------------------------------------------------------------------------|--------------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                                                    |              |                  |

|                  | CLEAR-CHANNEL FRAMER BLOCK REGISTERS                                                              |              |                  |

| 0xn110           | RxDS3 Configuration and Status RegisterRxE3 Configuration and Status Register # 1 (G.832 & G.751) | R/O          | 0x12             |

| 0xn111           | RxDS3 Status RegisterRxE3 Configuration and Status Register # 2 (G.832 & G.751)                   | R/O          | 0x00             |

| 0xn112           | RxDS3 Interrupt Enable RegisterRxE3 Interrupt Enable Register 1 (G.832 & G751)                    | R/W          | 0x00             |

| 0xn113           | RxDS3 Interrupt Status RegisterRxE3 Interrupt Enable Register # 2 (G.832 & G.751)                 | RUR          | 0x00             |

| 0xn114           | RxDS3 Sync Detect RegisterRxE3 Interrupt Status Register # 1 (G.832 & G.751)                      | R/W &<br>RUR | 0x00             |

| 0xn115           | RxE3 Interrupt Status Register # 2 (G.832 & G.751)                                                | RUR          | 0x00             |

| 0xn116           | Reserved                                                                                          |              |                  |

| 0xn117           | RxDS3 FEAC Interrupt Enable and Status Register                                                   | R/W &<br>RUR | 0x00             |

| 0xn118           | RxE3 LAPD Control Register                                                                        | R/W &<br>RUR | 0x00             |

| 0xn119           | RxLAPD Status Register                                                                            | R/O          | 0x00             |

| 0xn11A           | RxE3 NR Byte Register (G.832)RxE3 Service Bits Register (G.751)                                   | R/O          | 0x00             |

| 0xn11B           | RxE3 GC Byte Register (G.832)                                                                     | R/O          | 0x00             |

| 0xn11C           | RxE3 TTB Register # 0 (G.832)                                                                     | R/O          | 0x00             |

| 0xn11D           | RxE3 TTB Register # 1 (G.832)                                                                     | R/O          | 0x00             |

| 0xn11E           | RxE3 TTB Register # 2 (G.832)                                                                     | R/O          | 0x00             |

| 0xn11F           | RxE3 TTB Register # 3 (G.832)                                                                     | R/O          | 0x00             |

| 0xn120           | RxE3 TTB Register # 4 (G.832)                                                                     | R/O          | 0x00             |

| 0xn121           | RxE3 TTB Register # 5 (G.832)                                                                     | R/O          | 0x00             |

| 0xn122           | RxE3 TTB Register # 6 (G.832)                                                                     | R/O          | 0x00             |

| 0xn123           | RxE3 TTB Register # 7 (G.832)                                                                     | R/O          | 0x00             |

| 0xn124           | RxE3 TTB Register # 8 (G.832)                                                                     | R/O          | 0x00             |

| 0xn125           | RxE3 TTB Register # 9 (G.832)                                                                     | R/O          | 0x00             |

| 0xn126           | RxE3 TTB Register # 10 (G.832)                                                                    | R/O          | 0x00             |

| 0xn127           | RxE3 TTB Register # 11 (G.832)                                                                    | R/O          | 0x00             |

| 0xn128           | RxE3 TTB Register # 12 (G.832)                                                                    | R/O          | 0x00             |

| 0xn129           | RxE3 TTB Register # 13 (G.832)                                                                    | R/O          | 0x00             |

| Address Location | REGISTER NAME                                                                            | Түре          | DEFAULT<br>VALUE |

|------------------|------------------------------------------------------------------------------------------|---------------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                                           |               |                  |

|                  | CLEAR-CHANNEL FRAMER BLOCK REGISTERS                                                     |               |                  |

| 0xn12A           | RxE3 TTB Register # 14 (G.832)                                                           | R/O           | 0x00             |

| 0xn12B           | RxE3 TTB Register # 15 (G.832)                                                           | R/O           | 0x00             |

| 0xn12C           | RxE3 SSM Register (G.832)                                                                | R/O           | 0x00             |

| 0xn12D - 0xn12F  | Reserved                                                                                 |               |                  |

| 0xn130           | Transmit DS3 Configuration RegisterTransmit E3 Configuration Register                    | R/W           | 0x07             |

| 0xn131           | TxDS3 FEAC Configuration and Status Register                                             | RUR &<br>R/W  | 0x00             |

| 0xn132           | TxDS3 FEAC Register                                                                      | R/W           | 0x7E             |

| 0xn133           | TxLAPD Configuration Register                                                            | R/O & R/<br>W | 0x08             |

| 0xn134           | TxLAPD Status and Interrupt Register                                                     | RUR &<br>R/W  | 0x00             |

| 0xn135           | TxDS3 M-Bit Mask RegisterTxE3 GC Byte Register (G.832)TxE3 Service Bits Register (G.751) | R/W           | 0x00             |

| 0xn136           | TxDS3 F-Bit Mask Register # 1TxE3 MA Byte Register (G.832)                               | R/W           | 0x00             |

| 0xn137           | TxDS3 F-Bit Mask Register # 2TxE3 NR Byte Register (G.832)                               | R/W           | 0x00             |

| 0xn138           | TxDS3 F-Bit Mask Register # 3TxTTB Register # 0 (G.832)                                  | R/W           | 0x00             |

| 0xn139           | TxTTB Register # 1 (G.832)                                                               | R/W           | 0x00             |

| 0xn13A           | TxTTB Register # 2 (G.832)                                                               | R/W           | 0x00             |

| 0xn13B           | TxTTB Register # 3 (G.832)                                                               | R/W           | 0x00             |

| 0xn13C           | TxTTB Register # 4 (G.832)                                                               | R/W           | 0x00             |

| 0xn13D           | TxTTB Register # 5 (G.832)                                                               | R/W           | 0x00             |

| 0xn13E           | TxTTB Register # 6 (G.832)                                                               | R/W           | 0x00             |

| 0xn13F           | TxTTB Register # 7 (G.832)                                                               | R/W           | 0x00             |

| 0xn140           | TxTTB Register # 8 (G.832)                                                               | R/W           | 0x00             |

| 0xn141           | TxTTB Register # 9 (G.832)                                                               | R/W           | 0x00             |

| 0xn142           | TxTTB Register # 10 (G.832)                                                              | R/W           | 0x00             |

| 0xn143           | TxTTB Register # 11 (G.832)                                                              | R/W           | 0x00             |

| 0xn144           | TxTTB Register # 12 (G.832)                                                              | R/W           | 0x00             |

| 0xn145           | TxTTB Register # 13 (G.832)                                                              | R/W           | 0x00             |

| 0xn146           | TxTTB Register # 14 (G.832)                                                              | R/W           | 0x00             |

| 0xn147           | TxTTB Register # 15 (G.832)                                                              | R/W           | 0x00             |

**X** EXAR

| Address Location | REGISTER NAME                                                                | Түре | DEFAULT<br>VALUE |

|------------------|------------------------------------------------------------------------------|------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                               |      |                  |

|                  | CLEAR-CHANNEL FRAMER BLOCK REGISTERS                                         |      |                  |

| 0xn148           | TxE3 FA1 Error Mask Register (G.832)TxE3 FAS Error Mask Register # 1 (G.751) | R/W  | 0x00             |

| 0xn149           | TxE3 FA2 Error Mask Register (G.832)TxE3 FAS Error Mask Register # 2 (G.751) | R/W  | 0x00             |

| 0xn14A           | TxE3 BIP-8 Error Mask Register (G.832)TxE3 BIP-4 Error Mask Register (G.751) | R/W  | 0x00             |

| 0xn14B           | TxE3 SSM Register                                                            | R/W  | 0x00             |

| 0xn14C - 0xn14F  | Reserved                                                                     | R/O  | 0x00             |

| 0xn150           | PMON Line Code Violation Count Register - MSB                                | RUR  | 0x00             |

| 0xn151           | PMON Line Code Violation Count Register - LSB                                | RUR  | 0x00             |

| 0xn152           | PMON Framing Bit/Byte Error Count Register - MSB                             | RUR  | 0x00             |

| 0xn153           | PMON Framing Bit/Byte Error Count Register - LSB                             | RUR  | 0x00             |

| 0xn154           | PMON P-Bit/BIP-8/BIP-4 Error Count Register - MSB                            | RUR  | 0x00             |

| 0xn155           | PMON P-Bit/BIP-8/BIP-4 Error Count Register - LSB                            | RUR  | 0x00             |

| 0xn156           | PMON FEBE Event Count Register - MSB                                         | RUR  | 0x00             |

| 0xn157           | PMON FEBE Event Count Register - LSB                                         | RUR  | 0x00             |

| 0xn158           | PMON CP-Bit Error Count Register - MSB                                       | RUR  | 0x00             |

| 0xn159           | PMON CP-Bit Error Count Register - LSB                                       | RUR  | 0x00             |

| 0xn15A           | PMON PLCP BIP-8 Error Count Register - MSB                                   | RUR  | 0x00             |

| 0xn15B           | PMON PLCP BIP-8 Error Count Register - LSB                                   | RUR  | 0x00             |

| 0xn15C           | PMON PLCP Framing Byte Error Count Register - MSB                            | RUR  | 0x00             |

| 0xn15D           | PMON PLCP Framing Byte Error Count Register - LSB                            | RUR  | 0x00             |

| 0xn15E           | PMON PLCP FEBE Event Count Register - MSB                                    | RUR  | 0x00             |

| 0xn15F           | PMON PLCP FEBE Event Count Register - LSB                                    | RUR  | 0x00             |

| 0xn160 - 0xn167  | Reserved                                                                     |      |                  |

| 0xn168           | PRBS Error Count Register - MSB                                              | RUR  | 0x00             |

| 0xn169           | PRBS Error Count Register - LSB                                              | RUR  | 0x00             |

| 0xn16A - 0xn16C  | Reserved                                                                     |      |                  |

| 0xn16D           | One Second Error Status Register                                             | R/O  | 0x00             |

| 0xn16E           | One Second Accumulator - LCV Count Register - MSB                            | R/O  | 0x00             |

| 0xn16F           | One Second Accumulator - LCV Count Register - LSB                            | R/O  | 0x00             |

#### **CLEAR-CHANNEL FRAMER BLOCK REGISTERS**

| Address Location | REGISTER NAME                                                         | Түре          | DEFAULT<br>VALUE |

|------------------|-----------------------------------------------------------------------|---------------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                        |               |                  |

|                  | CLEAR-CHANNEL FRAMER BLOCK REGISTERS                                  |               |                  |

| 0xn170           | One Second Accumulator - P-Bit/BIP-8/BIP-4 Error Count Register - MSB | R/O           | 0x00             |

| 0xn171           | One Second Accumulator - P-Bit/BIP-8/BIP-4 Error Count Register - LSB | R/O           | 0x00             |

| 0xn172           | One Second Accumulator - CP Bit Error Count Register - MSB            | R/O           | 0x00             |

| 0xn173           | One Second Accumulator - CP Bit Error Count Register - LSB            | R/O           | 0x00             |

| 0xn174 - 0xn17F  | Reserved                                                              |               |                  |

| 0xn180           | Line Interface Drive Register                                         | R/W           | 0x08             |

| 0xn181           | Line Interface Scan Register                                          | R/O           | 0x00             |

| 0xn182           | Reserved                                                              | R/O           | 0x00             |

| 0xn183           | Transmit LAPD Byte Count Register                                     | R/W           | 0x00             |

| 0xn184           | Receive LAPD Byte Count Register                                      | R/W           | 0x00             |

| 0xn185 - 0xn18F  | Reserved                                                              | R/O           | 0x00             |

| 0xn190           | RxPLCP Configuration & Status Register                                | R/O & R/<br>W | 0x06             |

| 0xn191           | RxPLCP Interrupt Enable Register                                      | R/W           | 0x00             |

| 0xn192           | RxPLCP Interrupt Status Register                                      | RUR           | 0x00             |

| 0xn193 - 0xn197  | Reserved                                                              |               |                  |

| 0xn198           | TxPLCP A1 Byte Error Mask Register                                    | R/W           | 0x00             |

| 0xn199           | TxPLCP A2 Byte Error Mask Register                                    | R/W           | 0x00             |

| 0xn19A           | TxPLCP BIP-8 Byte Error Mask Register                                 | R/W           | 0x00             |

| 0xn19B           | TxPLCP G1 Byte Register                                               | R/W           | 0x00             |

| 0xn19C - 0xn2FF  | Reserved                                                              |               |                  |

### LIU/JITTER ATTENUATOR CONTROL REGISTERS

| Address Location | REGISTER NAME                                  | Түре | DEFAULT<br>VALUE |

|------------------|------------------------------------------------|------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER) |      |                  |

|                  | LIU/JITTER ATTENUATOR CONTROL REGISTERS        |      |                  |

| 0xn300           | LIU Transmit APS/Redundancy Control Register   | R/W  | 0x00             |

| 0xn301           | LIU Interrupt Enable Register                  | R/W  | 0x00             |

| 0xn302           | LIU Interrupt Status Register                  | RUR  | 0x00             |

| 0xn303           | LIU Alarm Status Register                      | R/O  | 0x00             |

### LIU/JITTER ATTENUATOR CONTROL REGISTERS

| Address Location | REGISTER NAME                                  | Түре | DEFAULT<br>VALUE |

|------------------|------------------------------------------------|------|------------------|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER) |      |                  |

|                  | LIU/JITTER ATTENUATOR CONTROL REGISTERS        |      |                  |

| 0xn304           | LIU Transmit Control Register                  | R/W  | 0x00             |

| 0xn305           | LIU Receive Control Register                   | R/W  | 0x00             |

| 0xn306           | LIU Channel Control Register                   | R/W  | 0x00             |

| 0xn307           | Jitter Attenuator Control Register             | R/W  | 0x00             |

| 0xn308           | LIU Receive APS/Redundancy Control Register    | R/W  | 0x00             |

| Address Location | REGISTER NAME                                                                                                    | Түре          | DEFAULT<br>VALUE |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|---------------|------------------|--|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                                                                   |               |                  |  |  |  |  |

| RECEI            | RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS                                                 |               |                  |  |  |  |  |

| 0xn700           | Receive ATM Control - Byte 3                                                                                     | R/W           | 0x00             |  |  |  |  |

| 0xn701           | Receive ATM Control - Byte 2                                                                                     | R/W           | 0x00             |  |  |  |  |

| 0xn702           | Receive ATM Control - Byte 1                                                                                     | R/W           | 0x00             |  |  |  |  |

| 0xn703           | Receive ATM Control - Byte 0Receive PPP Control Register                                                         | R/W           | 0x00             |  |  |  |  |

| 0xn704 - 0xn706  | Reserved                                                                                                         |               |                  |  |  |  |  |

| 0xn707           | Receive ATM Status Register                                                                                      | R/O           | 0x00             |  |  |  |  |

| 0xn708 - 0xn709  | Reserved                                                                                                         |               |                  |  |  |  |  |

| 0xn70A           | Receive ATM Interrupt Status Register -Byte 1                                                                    | RUR           | 0x00             |  |  |  |  |

| 0xn70B           | Receive ATM Interrupt Status Register - Byte 0Receive PPP Interrupt Status Register                              | RUR           | 0x00             |  |  |  |  |

| 0xn70C - 0xn70D  | Reserved                                                                                                         |               |                  |  |  |  |  |

| 0xn70E           | Receive ATM Interrupt Enable Register - Byte 1                                                                   |               | 0x00             |  |  |  |  |

| 0xn70F           | Receive ATM Interrupt Enable Register - Byte 0Receive PPP Interrupt Enable Register                              |               | 0x00             |  |  |  |  |

| 0xn710           | Receive PPP Good Packet Count Register - Byte 3                                                                  | RUR           | 0x00             |  |  |  |  |

| 0xn711           | Receive PPP Good Packet Count Register - Byte 2                                                                  |               | 0x00             |  |  |  |  |

| 0xn712           | Receive PPP Good Packet Count Register - Byte 1                                                                  |               | 0x00             |  |  |  |  |

| 0xn713           | Receive ATM Cell Insertion/Extraction Memory Control RegisterReceive PPP Good Packet Count Register - Byte 0     | R/O & R/<br>W | 0x00             |  |  |  |  |

| 0xn714           | Receive ATM Cell Insertion/Extraction Memory Data Register - Byte 3Receive PPP FCS Error Count Register - Byte 3 | R/O & R/<br>W | 0x00             |  |  |  |  |

| Address Location | REGISTER NAME                                                                                                    | Түре          | DEFAULT<br>VALUE |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|---------------|------------------|--|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                                                                   |               |                  |  |  |  |  |

| RECEI            | RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS                                                 |               |                  |  |  |  |  |

| 0xn715           | Receive ATM Cell Insertion/Extraction Memory Data Register - Byte 2Receive PPP FCS Error Count Register - Byte 2 | R/O & R/<br>W | 0x00             |  |  |  |  |

| 0xn716           | Receive ATM Cell Insertion/Extraction Memory Data Register - Byte 1Receive PPP FCS Error Count Register - Byte 1 | R/O & R/<br>W | 0x00             |  |  |  |  |

| 0xn717           | Receive ATM Cell Insertion/Extraction Memory Data Register - Byte 0Receive PPP FCS Error Count Register - Byte 0 | R/O & R/<br>W | 0x00             |  |  |  |  |

| 0xn718           | Receive ATM Cell UDF Data Register - Byte 3Receive PPP Abort Count Register - Byte 3                             | R/W &<br>RUR  | 0x00             |  |  |  |  |

| 0xn719           | Receive ATM Cell UDF Data Register - Byte 2Receive PPP Abort Count Register - Byte 2                             | R/W &<br>RUR  | 0x00             |  |  |  |  |

| 0xn71A           | Receive ATM Cell UDF Data Register - Byte 1Receive PPP Abort Count Register - Byte 1                             | R/W &<br>RUR  | 0x00             |  |  |  |  |

| 0xn71B           | Receive ATM Cell UDF Data Register - Byte 0Receive PPP Abort Count Register - Byte 0                             | R/W &<br>RUR  | 0x00             |  |  |  |  |

| 0xn71C           | Receive PPP Runt Frame Count Register - Byte 3                                                                   | RUR           | 0x00             |  |  |  |  |

| 0xn71D           | Receive PPP Runt Frame Count Register - Byte 2                                                                   | RUR           | 0x00             |  |  |  |  |

| 0xn71E           | Receive PPP Runt Frame Count Register - Byte 1                                                                   | RUR           | 0x00             |  |  |  |  |

| 0xn71F           | Receive PPP Runt Frame Count Register - Byte 0                                                                   | RUR           | 0x00             |  |  |  |  |

| 0xn720           | Receive ATM - Test Cell Header Byte Register - Byte 0                                                            |               | 0x00             |  |  |  |  |

| 0xn721           | Receive ATM - Test Cell Header Byte Register - Byte 1                                                            |               | 0x00             |  |  |  |  |

| 0xn722           | Receive ATM - Test Cell Header Byte Register - Byte 2                                                            |               | 0x00             |  |  |  |  |

| 0xn723           | Receive ATM - Test Cell Header Byte Register - Byte 3                                                            |               | 0x00             |  |  |  |  |

| 0xn724           | Receive ATM - Test Cell Error Count Register - Byte 3                                                            | RUR           | 0x00             |  |  |  |  |

| 0xn725           | Receive ATM - Test Cell Error Count Register - Byte 2                                                            | RUR           | 0x00             |  |  |  |  |

| 0xn726           | Receive ATM - Test Cell Error Count Register - Byte 1                                                            | RUR           | 0x00             |  |  |  |  |

| 0xn727           | Receive ATM - Test Cell Error Count Register - Byte 0                                                            |               | 0x00             |  |  |  |  |

| 0xn728           | Receive ATM Cell Count Register - Byte 3                                                                         |               | 0x00             |  |  |  |  |

| 0xn729           | Receive ATM Cell Count Register - Byte 2                                                                         |               | 0x00             |  |  |  |  |

| 0xn72A           | Receive ATM Cell Count Register - Byte 1                                                                         | RUR           | 0x00             |  |  |  |  |

| 0xn72B           | Receive ATM Cell Count Register - Byte 0                                                                         | RUR           | 0x00             |  |  |  |  |

| 0xn72C           | Receive ATM Cell - Discard Cell Count Register - Byte 3                                                          | RUR           | 0x00             |  |  |  |  |

| 0xn72D           | Receive ATM Cell - Discard Cell Count Register - Byte 2                                                          | RUR           | 0x00             |  |  |  |  |

| 0xn72E           | Receive ATM Cell - Discard Cell Count Register - Byte 1                                                          | RUR           | 0x00             |  |  |  |  |

| Address Location | REGISTER NAME                                                              | Түре | DEFAULT<br>VALUE |  |  |  |

|------------------|----------------------------------------------------------------------------|------|------------------|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                             |      |                  |  |  |  |

| RECEIN           | RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS           |      |                  |  |  |  |

| 0xn72F           | Receive ATM Cell - Discard Cell Count Register - Byte 0                    | RUR  | 0x00             |  |  |  |

| 0xn730           | Receive ATM Correctable HEC Byte Error Count Register - Byte 3             | RUR  | 0x00             |  |  |  |

| 0xn731           | Receive ATM Correctable HEC Byte Error Count Register - Byte 2             | RUR  | 0x00             |  |  |  |

| 0xn732           | Receive ATM Correctable HEC Byte Error Count Register - Byte 1             | RUR  | 0x00             |  |  |  |

| 0xn733           | Receive ATM Correctable HEC Byte Error Count Register - Byte 0             | RUR  | 0x00             |  |  |  |

| 0xn734           | Receive ATM Uncorrectable HEC Byte Error Count Register - Byte 3           | RUR  | 0x00             |  |  |  |

| 0xn735           | Receive ATM Uncorrectable HEC Byte Error Count Register - Byte 2           | RUR  | 0x00             |  |  |  |

| 0xn736           | Receive ATM Uncorrectable HEC Byte Error Count Register - Byte 1           | RUR  | 0x00             |  |  |  |

| 0xn737           | Receive ATM Uncorrectable HEC Byte Error Count Register - Byte 0           | RUR  | 0x00             |  |  |  |

| 0xn738 - 0xn742  | n738 - 0xn742 Reserved                                                     |      |                  |  |  |  |

| 0xn743           | Receive ATM - User Cell Filter # 0 - Filter Control Register               |      | 0x00             |  |  |  |

| 0xn744           | Receive ATM - User Cell Filter # 0 - Header Byte # 1 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xn745           | Receive ATM - User Cell Filter # 0 - Header Byte # 2 Pattern Register      |      | 0x00             |  |  |  |

| 0xn746           | Receive ATM - User Cell Filter # 0 - Header Byte # 3 Pattern Register      |      | 0x00             |  |  |  |

| 0xn747           | Receive ATM - User Cell Filter # 0 - Header Byte # 4 Pattern Register      |      | 0x00             |  |  |  |

| 0xn748           | Receive ATM - User Cell Filter # 0 - Header Byte # 1 Check Register        |      | 0x00             |  |  |  |

| 0xn749           | Receive ATM - User Cell Filter # 0 - Header Byte # 2 Check Register        |      | 0x00             |  |  |  |

| 0xn74A           | Receive ATM - User Cell Filter # 0 - Header Byte # 3 Check Register        |      | 0x00             |  |  |  |

| 0xn74B           | Receive ATM - User Cell Filter # 0 - Header Byte # 4 Check Register        |      | 0x00             |  |  |  |

| 0xn74C           | Receive ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 3 | RUR  | 0x00             |  |  |  |

| 0xn74D           | Receive ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 2 | RUR  | 0x00             |  |  |  |

| 0xn74E           | Receive ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 1 | RUR  | 0x00             |  |  |  |

| 0xn74F           | Receive ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 0 |      | 0x00             |  |  |  |

| 0xn750 - 0xn752  | Reserved                                                                   |      |                  |  |  |  |

| 0xn753           | Receive ATM - User Cell Filter # 1 - Filter Control Register               | R/W  | 0x00             |  |  |  |

| 0xn754           | Receive ATM - User Cell Filter # 1 - Header Byte # 1 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xn755           | Receive ATM - User Cell Filter # 1 - Header Byte # 2 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xn756           | Receive ATM - User Cell Filter # 1 - Header Byte # 3 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xn757           | Receive ATM - User Cell Filter # 1 - Header Byte # 4 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xn758           | Receive ATM - User Cell Filter # 1 - Header Byte # 1 Check Register        | R/W  | 0x00             |  |  |  |

| Address Location | REGISTER NAME                                                              | Түре   | DEFAULT<br>VALUE |  |  |  |

|------------------|----------------------------------------------------------------------------|--------|------------------|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                             |        |                  |  |  |  |

| RECEI            | VE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REG                      | ISTERS |                  |  |  |  |

| 0xn759           | Receive ATM - User Cell Filter # 1 - Header Byte # 2 Check Register        | R/W    | 0x00             |  |  |  |

| 0xn75A           | Receive ATM - User Cell Filter # 1 - Header Byte # 3 Check Register        | R/W    | 0x00             |  |  |  |

| 0xn75B           | Receive ATM - User Cell Filter # 1 - Header Byte # 4 Check Register        | R/W    | 0x00             |  |  |  |

| 0xn75C           | Receive ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 3 | RUR    | 0x00             |  |  |  |

| 0xn75D           | Receive ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 2 | RUR    | 0x00             |  |  |  |

| 0xn75E           | Receive ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 1 | RUR    | 0x00             |  |  |  |

| 0xn75F           | Receive ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 0 | RUR    | 0x00             |  |  |  |

| 0xn760 - 0xn762  | 0xn762 Reserved                                                            |        |                  |  |  |  |

| 0xn763           | Receive ATM - User Cell Filter # 2 - Filter Control Register               | R/W    | 0x00             |  |  |  |

| 0xn764           | Receive ATM - User Cell Filter # 2 - Header Byte # 1 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn765           | Receive ATM - User Cell Filter # 2 - Header Byte # 2 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn766           | Receive ATM - User Cell Filter # 2 - Header Byte # 3 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn767           | Receive ATM - User Cell Filter # 2 - Header Byte # 4 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn768           | Receive ATM - User Cell Filter # 2 - Header Byte # 1 Check Register        | R/W    | 0x00             |  |  |  |

| 0xn769           | Receive ATM - User Cell Filter # 2 - Header Byte # 2 Check Register        |        | 0x00             |  |  |  |

| 0xn76A           | Receive ATM - User Cell Filter # 2 - Header Byte # 3 Check Register        |        | 0x00             |  |  |  |

| 0xn76B           | Receive ATM - User Cell Filter # 2 - Header Byte # 4 Check Register        |        | 0x00             |  |  |  |

| 0xn76C           | Receive ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 3 |        | 0x00             |  |  |  |

| 0xn76D           | Receive ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 2 | RUR    | 0x00             |  |  |  |

| 0xn76E           | Receive ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 1 | RUR    | 0x00             |  |  |  |

| 0xn76F           | Receive ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 0 | RUR    | 0x00             |  |  |  |

| 0xn770 - 0xn772  | Reserved                                                                   |        |                  |  |  |  |

| 0xn773           | Receive ATM - User Cell Filter # 3 - Filter Control Register               | R/W    | 0x00             |  |  |  |

| 0xn774           | Receive ATM - User Cell Filter # 3 - Header Byte # 1 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn775           | Receive ATM - User Cell Filter # 3 - Header Byte # 2 Pattern Register      |        | 0x00             |  |  |  |

| 0xn776           | Receive ATM - User Cell Filter # 3 - Header Byte # 3 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn777           | Receive ATM - User Cell Filter # 3 - Header Byte # 4 Pattern Register      | R/W    | 0x00             |  |  |  |

| 0xn778           | Receive ATM - User Cell Filter # 3 - Header Byte # 1 Check Register        | R/W    | 0x00             |  |  |  |

| 0xn779           | Receive ATM - User Cell Filter # 3 - Header Byte # 2 Check Register        | R/W    | 0x00             |  |  |  |

| 0xn77A           | Receive ATM - User Cell Filter # 3 - Header Byte # 3 Check Register        | R/W    | 0x00             |  |  |  |

| Address Location | REGISTER NAME                                                                                | Түре          | DEFAULT<br>VALUE |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------|---------------|------------------|--|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                                               |               |                  |  |  |  |  |

| RECEIV           | VE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REG                                        | ISTERS        |                  |  |  |  |  |

| 0xn77B           | Receive ATM - User Cell Filter # 3 - Header Byte # 4 Check Register                          | R/W           | 0x00             |  |  |  |  |

| 0xn77C           | Receive ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 3                   | RUR           | 0x00             |  |  |  |  |

| 0xn77D           | Receive ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 2                   | RUR           | 0x00             |  |  |  |  |

| 0xn77E           | Receive ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 1                   | RUR           | 0x00             |  |  |  |  |

| 0xn77F           | Receive ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 0                   | RUR           | 0x00             |  |  |  |  |

| 0xn780 - 0xnEFF  | Reserved                                                                                     |               |                  |  |  |  |  |

| 0xnF00           | Transmit ATM Control Register - Byte 3                                                       | R/W           | 0x00             |  |  |  |  |

| 0xnF01           | Transmit ATM Control Register - Byte 2                                                       | R/W           | 0x00             |  |  |  |  |

| 0xnF02           | Transmit ATM Control Register - Byte 1                                                       | R/W           | 0x00             |  |  |  |  |

| 0xnF03           | Transmit ATM Control Register - Byte 0Transmit PPP Control Register - Byte 2                 | R/W           | 0x00             |  |  |  |  |

| 0xnF04           | Transmit ATM Status Register - Byte 3                                                        | R/O           | 0x00             |  |  |  |  |

| 0xnF05           | Transmit ATM Status Register - Byte 2                                                        | R/O           | 0x00             |  |  |  |  |

| 0xnF06           | Transmit ATM Status Register - Byte 1                                                        | R/O           | 0x00             |  |  |  |  |

| 0xnF07           | Transmit ATM Status Register - Byte 0                                                        |               | 0x00             |  |  |  |  |

| 0xnF08 - 0xnF0A  | Reserved                                                                                     |               |                  |  |  |  |  |

| 0xnF0B           | Transmit ATM Cell Processor Interrupt Status RegisterTransmit PPP Interrupt Status Register  |               | 0x00             |  |  |  |  |

| 0xnF0C - 0xnF0E  | Reserved                                                                                     |               |                  |  |  |  |  |

| 0xnF0F           | Transmit ATM Cell Processor Interrupt Enable Register Transmit PPP Interrupt Enable Register |               | 0x00             |  |  |  |  |

| 0xnF10 - 0xnF12  | Reserved                                                                                     |               |                  |  |  |  |  |

| 0xnF13           | Transmit ATM Cell Insertion/Extraction Memory Control Register                               |               | 0x00             |  |  |  |  |

| 0xnF14           | Transmit ATM Cell Insertion/Extraction Data Register - Byte 3                                |               | 0x00             |  |  |  |  |

| 0xnF15           | Transmit ATM Cell Insertion/Extraction Data Register - Byte 2                                |               | 0x00             |  |  |  |  |

| 0xnF16           | Transmit ATM Cell Insertion/Extraction Data Register - Byte 1                                | R/O & R/<br>W | 0x00             |  |  |  |  |

| 0xnF17           | Transmit ATM Cell Insertion/Extraction Data Register - Byte 0                                | R/O & R/<br>W | 0x00             |  |  |  |  |

| 0xnF18           | Transmit ATM - Idle Cell Header Byte # 1 Register                                            | R/W           | 0x00             |  |  |  |  |

| 0xnF19           | Transmit ATM - Idle Cell Header Byte # 2 Register                                            | R/W           | 0x00             |  |  |  |  |

| Address Location | REGISTER NAME                                                          | Түре | DEFAULT<br>VALUE |  |  |  |  |

|------------------|------------------------------------------------------------------------|------|------------------|--|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                         |      |                  |  |  |  |  |

| RECEI            | RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS       |      |                  |  |  |  |  |

| 0xnF1A           | Transmit ATM - Idle Cell Header Byte # 3 Register                      | R/W  | 0x00             |  |  |  |  |

| 0xnF1B           | Transmit ATM - Idle Cell Header Byte # 4 Register                      | R/W  | 0x00             |  |  |  |  |

| 0xnF1C - 0xnF1E  | Reserved                                                               |      |                  |  |  |  |  |

| 0xnF1F           | Transmit ATM - Idle Cell Payload Byte Register                         | R/W  | 0x00             |  |  |  |  |

| 0xnF20           | Transmit ATM - Test Cell Header Byte # 1 Register                      | R/W  | 0x00             |  |  |  |  |

| 0xnF21           | Transmit ATM - Test Cell Header Byte # 2 Register                      | R/W  | 0x00             |  |  |  |  |

| 0xnF22           | Transmit ATM - Test Cell Header Byte # 3 Register                      | R/W  | 0x00             |  |  |  |  |

| 0xnF23           | Transmit ATM - Test Cell Header Byte # 4 Register                      | R/W  | 0x00             |  |  |  |  |

| 0xnF24 - 0xnF27  | Reserved                                                               |      |                  |  |  |  |  |

| 0xnF28           | Transmit ATM Cell Count Register - Byte 3                              | RUR  | 0x00             |  |  |  |  |

| 0xnF29           | Transmit ATM Cell Count Register - Byte 2                              | RUR  | 0x00             |  |  |  |  |

| 0xnF2A           | Transmit ATM Cell Count Register - Byte 1                              | RUR  | 0x00             |  |  |  |  |

| 0xnF2B           | Transmit ATM Cell Count Register - Byte 0                              | RUR  | 0x00             |  |  |  |  |

| 0xnF2C           | Transmit ATM - Discarded Cell Count Register - Byte 3                  | RUR  | 0x00             |  |  |  |  |

| 0xnF2D           | Transmit ATM - Discarded Cell Count Register - Byte 2                  |      | 0x00             |  |  |  |  |

| 0xnF2E           | Transmit ATM - Discarded Cell Count Register - Byte 1                  |      | 0x00             |  |  |  |  |

| 0xnF2F           | Transmit ATM - Discarded Cell Count Register - Byte 0                  |      | 0x00             |  |  |  |  |

| 0xnF30           | Transmit ATM HEC Byte Error Count Register - Byte 3                    |      | 0x00             |  |  |  |  |

| 0xnF31           | Transmit ATM HEC Byte Error Count Register - Byte 2                    |      | 0x00             |  |  |  |  |

| 0xnF32           | Transmit ATM HEC Byte Error Count Register - Byte 1                    | RUR  | 0x00             |  |  |  |  |

| 0xnF33           | Transmit ATM HEC Byte Error Count Register - Byte 0                    | RUR  | 0x00             |  |  |  |  |

| 0xnF34           | Transmit ATM Cell Processor - Parity Error Count Register - Byte 3     | RUR  | 0x00             |  |  |  |  |

| 0xnF35           | Transmit ATM Cell Processor - Parity Error Count Register - Byte 2     | RUR  | 0x00             |  |  |  |  |

| 0xnF36           | Transmit ATM Cell Processor - Parity Error Count Register - Byte 1     | RUR  | 0x00             |  |  |  |  |

| 0xnF37           | Transmit ATM Cell Processor - Parity Error Count Register - Byte 0     |      | 0x00             |  |  |  |  |

| 0xnF38 - 0xnF42  | Reserved                                                               |      |                  |  |  |  |  |

| 0xnF43           | Transmit ATM - User Cell Filter # 0 - Filter Control Register          | R/W  | 0x00             |  |  |  |  |

| 0xnF44           | Transmit ATM - User Cell Filter # 0 - Header Byte # 1 Pattern Register | R/W  | 0x00             |  |  |  |  |

| 0xnF45           | Transmit ATM - User Cell Filter # 0 - Header Byte # 2 Pattern Register | R/W  | 0x00             |  |  |  |  |

| 0xnF46           | Transmit ATM - User Cell Filter # 0 - Header Byte # 3 Pattern Register | R/W  | 0x00             |  |  |  |  |

| Address Location | REGISTER NAME                                                               | Түре | DEFAULT<br>VALUE |  |  |  |

|------------------|-----------------------------------------------------------------------------|------|------------------|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                              |      |                  |  |  |  |

| RECEI            | RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS            |      |                  |  |  |  |

| 0xnF47           | Transmit ATM - User Cell Filter # 0 - Header Byte # 4 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF48           | Transmit ATM - User Cell Filter # 0 - Header Byte # 1 Check Register        | R/W  | 0x00             |  |  |  |

| 0xnF49           | Transmit ATM - User Cell Filter # 0 - Header Byte # 2 Check Register        | R/W  | 0x00             |  |  |  |

| 0xnF4A           | Transmit ATM - User Cell Filter # 0 - Header Byte # 3 Check Register        | R/W  | 0x00             |  |  |  |

| 0xnF4B           | Transmit ATM - User Cell Filter # 0 - Header Byte # 4 Check Register        | R/W  | 0x00             |  |  |  |

| 0xnF4C           | Transmit ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 3 | RUR  | 0x00             |  |  |  |

| 0xnF4D           | Transmit ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 2 | RUR  | 0x00             |  |  |  |

| 0xnF4E           | Transmit ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 1 | RUR  | 0x00             |  |  |  |

| 0xnF4F           | Transmit ATM - User Cell Filter # 0 - Filtered Cell Count Register - Byte 0 | RUR  | 0x00             |  |  |  |

| 0xnF50 - 0xnF52  | Reserved                                                                    |      |                  |  |  |  |

| 0xnF53           | Transmit ATM - User Cell Filter # 1 - Filter Control Register               | R/W  | 0x00             |  |  |  |

| 0xnF54           | Transmit ATM - User Cell Filter # 1 - Header Byte # 1 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF55           | Transmit ATM - User Cell Filter # 1 - Header Byte # 2 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF56           | Transmit ATM - User Cell Filter # 1 - Header Byte # 3 Pattern Register      |      | 0x00             |  |  |  |

| 0xnF57           | Transmit ATM - User Cell Filter # 1 - Header Byte # 4 Pattern Register      |      | 0x00             |  |  |  |

| 0xnF58           | Transmit ATM - User Cell Filter # 1 - Header Byte # 1 Check Register        |      | 0x00             |  |  |  |

| 0xnF59           | Transmit ATM - User Cell Filter # 1 - Header Byte # 2 Check Register        |      | 0x00             |  |  |  |

| 0xnF5A           | Transmit ATM - User Cell Filter # 1 - Header Byte # 3 Check Register        | R/W  | 0x00             |  |  |  |

| 0xnF5B           | Transmit ATM - User Cell Filter # 1 - Header Byte # 4 Check Register        |      | 0x00             |  |  |  |

| 0xnF5C           | Transmit ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 3 | RUR  | 0x00             |  |  |  |

| 0xnF5D           | Transmit ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 2 | RUR  | 0x00             |  |  |  |

| 0xnF5E           | Transmit ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 1 | RUR  | 0x00             |  |  |  |

| 0xnF5F           | Transmit ATM - User Cell Filter # 1 - Filtered Cell Count Register - Byte 0 | RUR  | 0x00             |  |  |  |

| 0xnF60 - 0xnF62  | Reserved                                                                    |      |                  |  |  |  |

| 0xnF63           | Transmit ATM - User Cell Filter # 2 - Filter Control Register               | R/W  | 0x00             |  |  |  |

| 0xnF64           | Transmit ATM - User Cell Filter # 2 - Header Byte # 1 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF65           | Transmit ATM - User Cell Filter # 2 - Header Byte # 2 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF66           | Transmit ATM - User Cell Filter # 2 - Header Byte # 3 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF67           | Transmit ATM - User Cell Filter # 2 - Header Byte # 4 Pattern Register      | R/W  | 0x00             |  |  |  |

| 0xnF68           | Transmit ATM - User Cell Filter # 2 - Header Byte # 1 Check Register        | R/W  | 0x00             |  |  |  |

| Address Location | REGISTER NAME                                                               | Түре | DEFAULT<br>VALUE |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|------|------------------|--|--|--|--|

|                  | CHANNEL CONTROL REGISTERS (N = CHANNEL NUMBER)                              |      |                  |  |  |  |  |

| RECEIV           | RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS            |      |                  |  |  |  |  |

| 0xnF69           | Transmit ATM - User Cell Filter # 2 - Header Byte # 2 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF6A           | Transmit ATM - User Cell Filter # 2 - Header Byte # 3 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF6B           | Transmit ATM - User Cell Filter # 2 - Header Byte # 4 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF6C           | Transmit ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 3 | RUR  | 0x00             |  |  |  |  |

| 0xnF6D           | Transmit ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 2 | RUR  | 0x00             |  |  |  |  |

| 0xnF6E           | Transmit ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 1 | RUR  | 0x00             |  |  |  |  |

| 0xnF6F           | Transmit ATM - User Cell Filter # 2 - Filtered Cell Count Register - Byte 0 | RUR  | 0x00             |  |  |  |  |

| 0xnF70 - 0xnF72  | Reserved                                                                    |      |                  |  |  |  |  |

| 0xnF73           | Transmit ATM - User Cell Filter # 3 - Filter Control Register               | R/W  | 0x00             |  |  |  |  |

| 0xnF74           | Transmit ATM - User Cell Filter # 3 - Header Byte # 1 Pattern Register      | R/W  | 0x00             |  |  |  |  |

| 0xnF75           | Transmit ATM - User Cell Filter # 3 - Header Byte # 2 Pattern Register      |      | 0x00             |  |  |  |  |

| 0xnF76           | Transmit ATM - User Cell Filter # 3 - Header Byte # 3 Pattern Register      |      | 0x00             |  |  |  |  |

| 0xnF77           | Transmit ATM - User Cell Filter # 3 - Header Byte # 4 Pattern Register      | R/W  | 0x00             |  |  |  |  |

| 0xnF78           | Transmit ATM - User Cell Filter # 3 - Header Byte # 1 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF79           | Transmit ATM - User Cell Filter # 3 - Header Byte # 2 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF7A           | Transmit ATM - User Cell Filter # 3 - Header Byte # 3 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF7B           | Transmit ATM - User Cell Filter # 3 - Header Byte # 4 Check Register        | R/W  | 0x00             |  |  |  |  |

| 0xnF7C           | Transmit ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 3 | RUR  | 0x00             |  |  |  |  |

| 0xnF7D           | Transmit ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 2 | RUR  | 0x00             |  |  |  |  |

| 0xnF7E           | Transmit ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 1 | RUR  | 0x00             |  |  |  |  |

| 0xnF7F           | Transmit ATM - User Cell Filter # 3 - Filtered Cell Count Register - Byte 0 | RUR  | 0x00             |  |  |  |  |

| 0xnF80 - 0xnFFF  | Reserved                                                                    |      |                  |  |  |  |  |

### **OPERATION BLOCK INTERRUPT REGISTER BIT FORMATS**

### OPERATION CONTROL REGISTER - BYTE 3 (ADDRESS = 0X0100)

| Віт 7 | Віт 6 | Віт 5 | Віт 4  | Віт 3 | Віт 2 | Віт 1 | Віт 0                    |

|-------|-------|-------|--------|-------|-------|-------|--------------------------|

|       |       |       | Unused |       |       |       | Configuration<br>Control |

| R/O   | R/O   | R/O   | R/O    | R/O   | R/O   | R/O   | R/O                      |

| 0     | 0     | 0     | 0      | 0     | 0     | 0     | 0                        |

| R/O<br>R/W | Configuration Control: This READ/WRITE bit-field permits the user to configure the XRT79L74 device to support any of the following configuration  • ATM/PPP  • Clear Channel/HDLC The following table presents the relationship between the value. |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R/W        | This READ/WRITE bit-field permits the user to configure the XRT79L74 device to support any of the following configuration  • ATM/PPP  • Clear Channel/HDLC                                                                                         |  |