**XRT79L71** 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

REV. P1.0.3

#### JUNE 2003

### GENERAL DESCRIPTION

The XRT79L71 is a single channel, ATM UNI/PPP Physical Layer Processor with integrated DS3/E3 framing controller and Line Interface Unit with Jitter Attenuator that is designed to support ATM direct mapping and cell delineation as well as PPP mapping and Frame processing. For ATM UNI applications, this device provides the ATM Physical Layer (Physical Medium Dependent and Transmission Convergence sub-layers) interface for the public and private networks at DS3/E3 rates. For Clear-Channel Framer applications, this device supports the transmission and reception of "user data" via the DS3/E3 payload.

The XRT79L71 includes DS3/E3 Framing, Line Interface Unit with Jitter Attenuator that supports mapping of ATM or HDLC framed data. A flexible parallel microprocessor interface is provided for configuration and control. Industry standard UTOPIA II and POS-PHY interface are also provided.

#### **GENERAL FEATURES:**

- Integrated T3/E3 Line Interface Unit

- Integrated Jitter Attenuator that can be selected either in Receive or Transmit path

- Flexible integrated Clock Multiplier that takes single frequency clock and generates either DS3 or E3 frequency.

- 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- HDLC Controller that provides the mapping/ extraction of either bit or byte mapped encapsulated packet from DS3/E3 Frame.

- Contains on-chip 16 cell FIFO (configurable in depths of 4, 8, 12 or 16 cells), in both the Transmit (TxFIFO) and Receive Directions (RxFIFO)

- Contains on-chip 54 byte Transmit and Receive OAM Cell Buffer for transmission, reception and processing of OAM Cells

- Supports ATM cell or PPP Packet Mapping

- Supports M13 and C-Bit Parity Framing Formats

- Supports DS3/E3 Clear-Channel Framing.

- Includes PRBS Generator and Receiver

- Supports Line, Cell, and PLCP Loop-backs

- Interfaces to 8 Bit wide Intel, Motorola, PowerPC, and Mips µPs

- Low power 3.3V, 5V Input Tolerant, CMOS

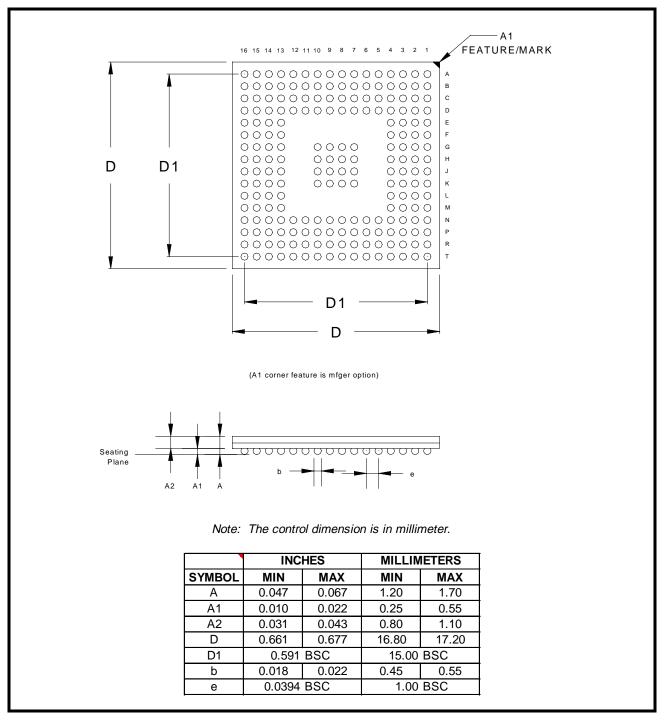

- Available in 208 STBI PBGA Package

JTAG Interface

#### LINE INTERFACE UNIT

- On chip Clock and Data Recovery circuit for high input jitter tolerance

- Meets E3/DS3 Jitter Tolerance Requirements

- Detects and Clears LOS as per G.775.

- Receiver Monitor mode handles up to 20 dB flat loss with 6 dB cable attenuation

- · Compliant with jitter transfer template outlined in ITU G.751, G.752, G.755 and GR-499-CORE, 1995 standards

- Meets ETSI TBR 24 and GR-499 Jitter Transfer Requirements

- On chip B3ZS/HDB3 encoder and decoder that can be either enabled or disabled

- On-chip clock synthesizer provides the appropriate rate clock from a single 12.288 MHz Clock

- On chip advanced crystal-less Jitter Attenuator

- Jitter Attenuator can be selected in Receive or Transmit paths

- 16 or 32 bits selectable FIFO size

- Meets the Jitter and Wander specifications described in T1.105.03b,ETSI TBR-24, Bellcore GR-253 and GR-499 standards

- Jitter Attenuator can be disabled

- Typical power consumption 1.3W

### **DS3/E3 FRAMER**

- DS3 framer supports both M13 and C-bit parity.

- DS3 framer meets ANSI T1.107 and T1.404 standards.

- Detects OOF,LOF,AIS,RDI/FERF alarms.

- Generation and Insertion of FEBE on received parity errors supported.

- Automatic insertion of RDI/FERF on alarm status.

- E3 framer meets G.832,G.751 standards.

- Framers can be bypassed.

#### ATM/PPP PROTOCOL PROCESSOR

#### TRANSMIT CELL PROCESSING

- Extracts ATM cells

- Supports ATM cell payload scrambling

- Maps ATM cells into E3 or DS3 frame

- PLCP frame and mapping of ATM cell streams

## PRELIMINARY

1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

## **RECEIVE CELL PROCESSING**

- Extraction of ATM cells from PLCP frame or directly from E3 or DS3 frame

- Termination of PLCP frame

- Supports payload cell de-scrambling

### TRANSMIT PACKET PROCESSING

- Inserts PPP packets into data stream

- Maps HDLC data stream directly into DS3 or E3 frame

- Extracts in-band messaging packets

- Supports CRC-16/32, HDLC flag and Idle sequence generation

### **RECEIVE PACKET PROCESSING**

- Extracts HDLC data stream from DS3 or E3 frame

- Inserts in-band messaging packets

- Detects and removes HDLC flags

### UTOPIA/ SYSTEM INTERFACE

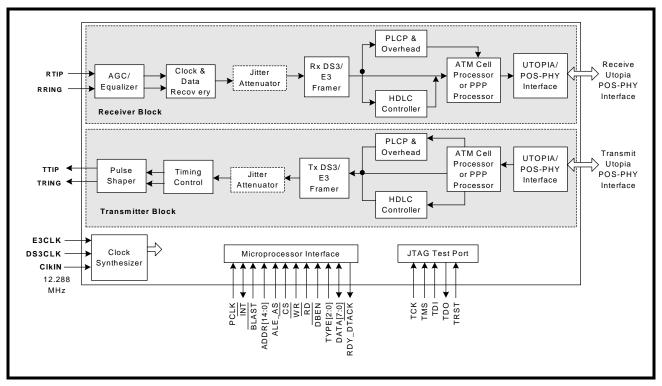

### FIGURE 1. BLOCK DIAGRAM OF THE XRT79L71

# • 8/16 bit UTOPIA Level I and II and PPP Multi-PHY Interface operating at 25, 33 or 50 MHz.

- Compliant with ATM Forum UTOPIA II interface

- Programmable FIFO size for both Transmit and Receive direction

- Compliant to POS-PHY Level 2 interface

#### SERIAL INTERFACE

- Serial clock and data interface for accessing DS3/ E3 framer

- Serial clock and data interface for accessing cell/ packet processor

### APPLICATIONS

- Digital Access and Cross Connect Systems

- 3G Base Stations

- DSLAMs

- Digital, ATM, WAN and LAN Switches

## PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE                                  | OPERATING TEMPERATURE RANGE |

|----------------|-----------------------------------------------|-----------------------------|

| XRT79L71IB     | 17X17 mm 208 Ball Shrink Thin Ball Grid Array | -40°C to +85°C              |

| <b>Z EXAR</b>                    | PRELIMINARY |

|----------------------------------|-------------|

| 1 - CHANNEL DS3/E3 ATM UNI/PPP C | COMBO IC    |

| XRT79L71    |

|-------------|

| REV. P1.0.3 |

|             |

|   | ×                                     |                     | ME         |            |           |            | ~                     | Ψ                 |          | ЧE         | Ш          | Щ          |                                         |          |          |            |

|---|---------------------------------------|---------------------|------------|------------|-----------|------------|-----------------------|-------------------|----------|------------|------------|------------|-----------------------------------------|----------|----------|------------|

| A | RXGFCCLK                              | RXPLOF              | TXPOHFRAME | RXNB_2     | RXSER     | RXCLK      | RXOHCLK               | RXOHFRAME         | TXNIB_0  | TXNIBFRAME | TXFRAMEREF | TXOHENABLE | TXAISEN                                 | PDATA_3  | PDATA_7  | PAS_L      |

| В | RXGFCMSB                              | RXPRED              | ТХРОНСLК   | RXNIB_3    | RXOUTCLK  | RXFRAME    | RXOHENABLE            | TXNOB_3           | DINHOXT  | TXFRAME    | TXOHFRAME  | TXOHCLK    | PDATA_2                                 | PDATA_6  | PBLAST_L | PWR_L      |

| ပ | RXUDATA_13                            | TXGFCCLK            | RXGFC      | RXPOHFRAME | RXNIB_0   | RXOHIND    | RXOH                  | TXNOB_2           | TXSER    | TXINCLK    | тхон       | PDATA_1    | PDATA_5                                 | PRDY_L   | PRD_L    | PADDR_0    |

| D | RXUDATA_9                             | RXUDATA_12          | RXUDATA_15 | RXCP       | RXPOOF    | RXNIB_1    | RXLOS                 | TXNB_1            | TXNIBCLK | TXOHINS    | PDATA      | PDATA_4    | PINT_L                                  | PCS_L    | PADDR_1  | PADDR_2    |

| ш | RXUDATA_5                             | RXUDATA_8           | RXUDATA_11 | RXUDATA_14 |           |            |                       |                   |          |            |            |            | PADDR_6                                 | PADDR_5  | PADDR_4  | PADDR_3    |

| ш | RXUDATA_2                             | RXUDATA_4           | RXUDATA_7  | RXUDATA_10 |           |            |                       |                   |          |            | -          |            | DPADDR_3                                | DPADDR_2 | DPADDR_1 | DPADDR_0   |

| ი | RXUDATA_1                             | RXUDATA_0           | RXUDATA_3  | RXUDATA_6  |           |            | DOV                   | aav               | ααλ      | DDV        |            |            | DPADDR_7                                | DPADDR_6 | DPADDR_5 | DPADDR_4   |

| т | RXUCLAV                               | RXUSOC              | кхирктү    | RXUEN_L    |           |            | GND                   | GND               | GND      | GND        |            |            | DA_SEL                                  | DDV      | GND      | PCLK       |

| ٦ | RXUADDR_4 RXUADDR_0 RXUCLAV RXUDATA_1 | RXUADDR_1           | RXUADDR_2  | RXUADDR_3  |           |            | GND                   | GND               | GND      | GND        |            |            | PDBEN_L                                 | PTYPE_2  | РТҮРЕ_1  | PTYPE_0    |

| х | RXUADDR_4                             | RXUCLKO             | RXPEOP     | RSX_RSOF   |           |            | DOV                   | DDV               | DDV      | DDV        |            |            | GPO_2                                   | GP0_1    | GPO_0    | ССКОЛТ     |

|   | RXMOD                                 | RXPERR              | RXUCLK     | TSX_TSOF   |           |            |                       |                   |          |            |            |            | GPL_2                                   | GPI_1    | GPI_0    | NIBBLEINTF |

| Σ | TXUCLK                                | TXPER               | TXMOD      | TXUEN_L    |           |            |                       |                   |          |            |            |            | OGND                                    | RESET_L  | TESTMODE | E3CLK      |

| z | тхреор                                | RXPDVAL             | TXUCLAV    | TXUDATA_10 | TXUDATA_4 | TXUDATA_8  | TXUDATA_13            | GPI0_1            | TDO      | TXDGND     | ТХРИРР     | TXAGND     | aavo                                    | DDV      | GND      | CLKGND     |

| ٩ | тхисько                               | TXUADDR_4           | TXUSOC     | TXUDATA_1  | TXUDATA_5 | TXUDATA_9  | TXUDATA_15 TXUDATA_14 | GPIO_2            | TDI      | MTIP       | MRING      | REFAGND    | ANAIO1                                  | ANAIO2   | ICTB     | DS3CLK     |

| Ъ | TXUADDR_3                             | TXUADDR_0 TXUADDR_2 | ТХИРКТҮ    | TXUDATA_2  | TXUDATA_6 | TXUDATA_11 | TXUDATA_15            | GPIO_3            | TMS      | TRST       | NC         | REFAVDD    | RRING                                   | RTIP     | TXON     | CLKVDD     |

| F | TXUADDR_1                             | TXUADDR_0           | TXUDATA_0  | TXUDAT_3   | TXUDATA_7 | TXUDATA_12 | GPIO_0                | 0 <sup></sup> ОМД | тск      | TRING      | dITT       | TXAVDD     | DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD | RXAGND   | JAGND    | JAAVDD     |

|   | -                                     | 2                   | с          | 4          | 5         | 9          | 7                     | 8                 | 6        | 10         | 11         | 12         | 13                                      | 14       | 15       | 16         |

## TABLE 1: PIN OUT OF THE XRT79L71 (TOP VIEW)

1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

## TABLE OF CONTENTS

| GENERAL DESCRIPTION                                                                                                                                                                           | 1   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| GENERAL FEATURES:                                                                                                                                                                             | 1   |

| Line Interface Unit                                                                                                                                                                           | 1   |

| DS3/E3 Framer                                                                                                                                                                                 |     |

| ATM/PPP PROTOCOL PROCESSOR                                                                                                                                                                    |     |

| Transmit Cell Processing                                                                                                                                                                      |     |

| Receive Cell Processing                                                                                                                                                                       |     |

| Transmit Packet Processing                                                                                                                                                                    |     |

| Receive Packet Processing                                                                                                                                                                     |     |

| Utopia/ System Interface<br>Serial Interface                                                                                                                                                  |     |

| APPLICATIONS                                                                                                                                                                                  |     |

| FIGURE 1. BLOCK DIAGRAM OF THE XRT79L71                                                                                                                                                       |     |

| PRODUCT ORDERING INFORMATION                                                                                                                                                                  |     |

| TABLE 1: PIN OUT OF THE XRT79L71 (TOP VIEW)                                                                                                                                                   |     |

| TABLE OF CONTENTS                                                                                                                                                                             |     |

| PIN DESCRIPTIONS                                                                                                                                                                              |     |

| MICROPROCESSOR INTERFACE                                                                                                                                                                      |     |

| Test and Diagnostic                                                                                                                                                                           |     |

| General Purpose Input and Output Pins                                                                                                                                                         |     |

| TRANSMIT SYSTEM SIDE INTERFACE PINS                                                                                                                                                           |     |

| Receive System Side Interface Pins                                                                                                                                                            |     |

| TRANSMIT LINE SIDE SIGNALS                                                                                                                                                                    |     |

| Receive Line Side Signals                                                                                                                                                                     |     |

| VDD Pins                                                                                                                                                                                      |     |

| GND Pins                                                                                                                                                                                      |     |

| NOT CONNECTED PINS                                                                                                                                                                            |     |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                                    |     |

|                                                                                                                                                                                               |     |

| AC ELECTRICAL CHARACTERISTIC INFORMATION                                                                                                                                                      |     |

| MICROPROCESSOR INTERFACE TIMING FOR REVISION A SILICON                                                                                                                                        |     |

| MICROPROCESSOR INTERFACE TIMING - ASYNCHRONOUS INTEL MODE                                                                                                                                     |     |

| TABLE 2: DC ELECTRICAL CHARACTERISTICSS                                                                                                                                                       |     |

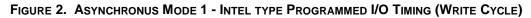

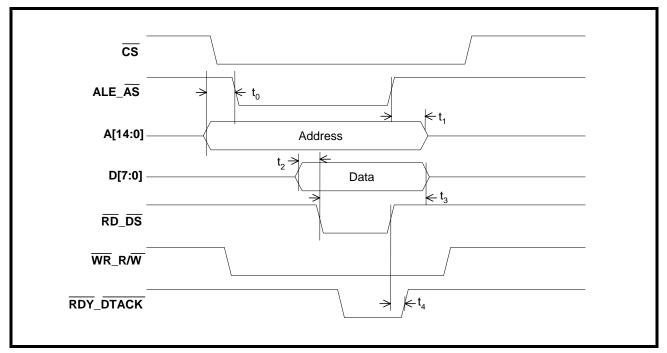

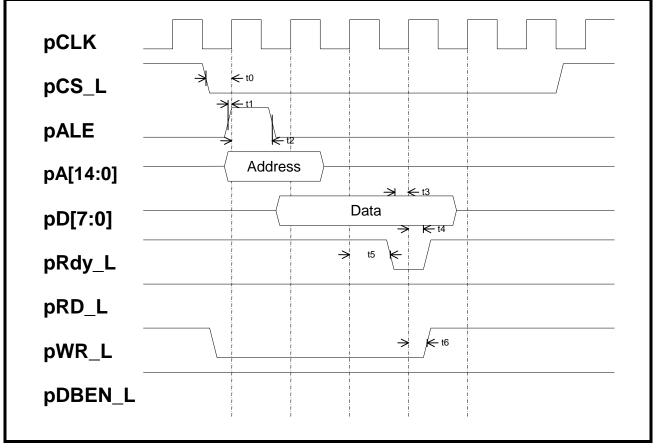

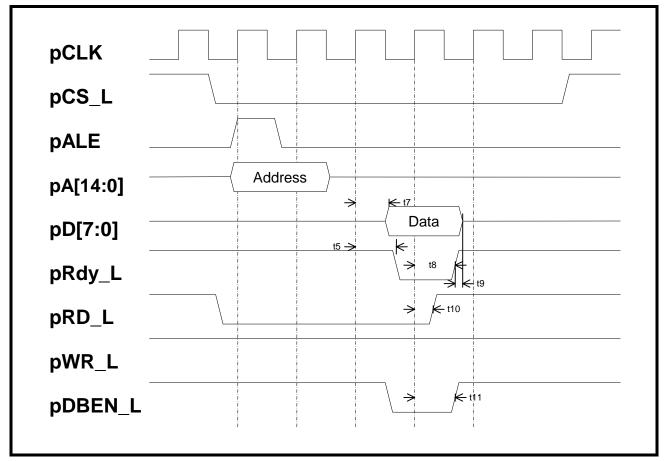

| Applies to all TTL-Level Input and CMOS Level Output pins - Ambient Temperature = 25°C<br>FIGURE 2. ASYNCHRONUS MODE 1 - INTEL TYPE PROGRAMMED I/O TIMING (WRITE CYCLE)                       |     |

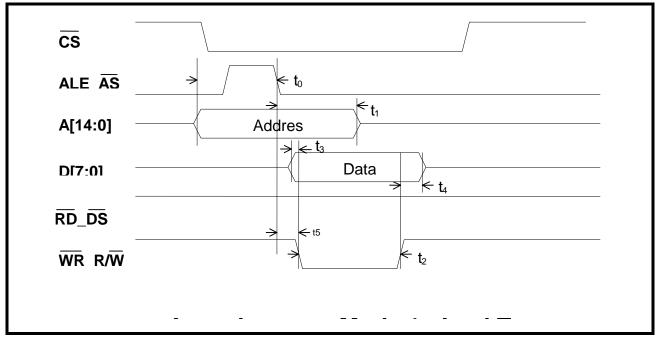

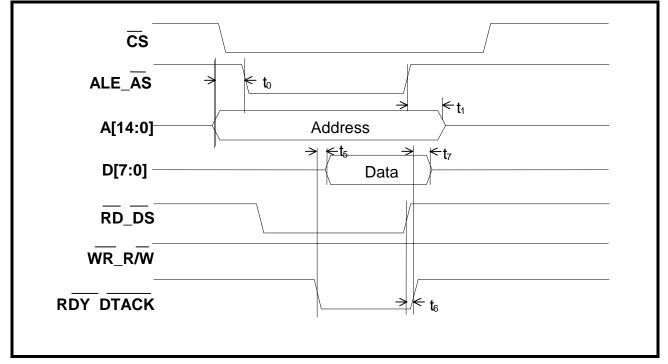

| FIGURE 2. ASYNCHRONUS MODE 1 - INTEL TYPE PROGRAMMED I/O TIMING (WRITE CYCLE)<br>FIGURE 3. ASYNCHRONUS MODE 1 - INTEL TYPE PROGRAMMED I/O TIMING (READ CYCLE)                                 |     |

| TABLE 3: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE, WHEN CONFIGURED TO OPERATE IN THE INTEL ASYNCHRO                                                                                |     |

| Mode                                                                                                                                                                                          |     |

| MICROPROCESSOR INTERFACE TIMING - ASYNCHRONOUS MOTOROLA (68K)                                                                                                                                 |     |

| MODE                                                                                                                                                                                          | 41  |

| Figure 4. Asynchronus Mode 2 - Motorola 68K Programmed I/O Timing (Write Cycle)                                                                                                               | 41  |

| FIGURE 5. ASYNCHRONUS MODE 2 - MOTOROLA 68 PROGRAMMED I/O TIMING (READ CYCLE)                                                                                                                 |     |

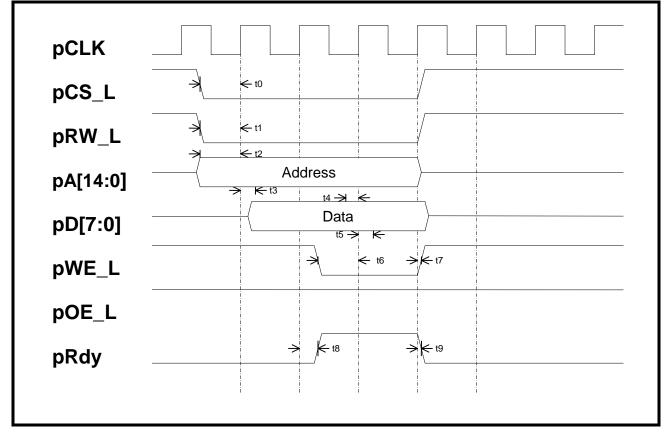

| MICROPROCESSOR INTERFACE TIMING - POWER PC 403 SYNCHRONOUS MOD                                                                                                                                | E42 |

| TABLE 4: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE WHEN CONFIGURED TO OPERATE IN THE MOTOROLA (68K)           CHRONOUS MODE                                                         | 42  |

| FIGURE 6. SYNCHRONOUS MODE 3 - IBM POWERPC 403 INTERFACE TIMING (WRITE CYCLE)                                                                                                                 |     |

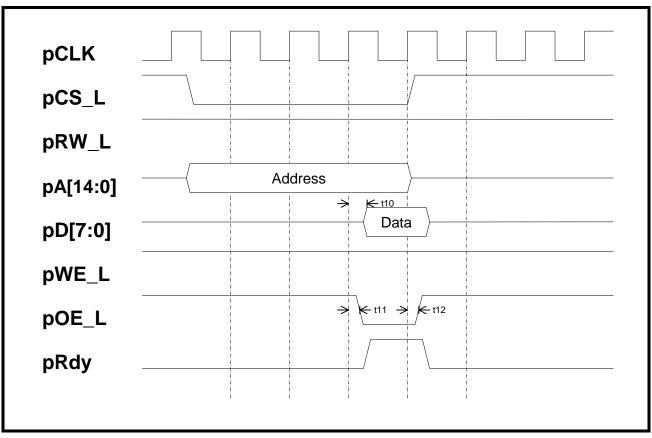

| FIGURE 7. SYNCHRONOUS MODE 3 - IBM POWERPC 403 INTERFACE TIMING (READ CYCLE)<br>TABLE 5: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE, WHEN CONFIGURED TO OPERATE IN THE IBM POWER PC4 | 43  |

| TABLE 5. TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE, WHEN CONFIGURED TO OPERATE IN THE IBM POWER PC4                                                                                 |     |

| MICROPROCESSOR INTERFACE TIMING - IDT3051/52 MODE                                                                                                                                             |     |

| FIGURE 8. SYNCHRONOUS MODE 4 - IDT 3051/52 INTERFACE TIMING (WRITE CYCLE)                                                                                                                     |     |

| FIGURE 9. SYNCHRONOUS MODE 4 - IDT 3051/52 INTERFACE TIMING (READ CYCLE)                                                                                                                      | 45  |

| TABLE 6: TIMING INFORMATION FOR THE MICROPROCESSOR INTERFACE, WHEN CONFIGURED TO OPERATE IN THE IBM POWER PC4                                                                                 | 403 |

| DS3/E3 LIU INTERFACE - LINE SIDE ELECTRICAL CHARACTERISTIC INFORMATI                                                                                                                          |     |

|                                                                                                                                                                                               |     |

| 46                                                                                                                                                                                            |     |

**XP EXAR**

PRELIMINARY

XRT79L71 *REV. P1.0.3*

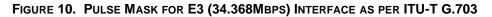

| Fourier 10. Project Masker core E3 (dd. 386Mbere) Interestace as even UT second-antons.       46         DS3 Lines Side PARAMETERS       47         Fourier 11. Biccores GR-990-CORE Proze Thermatic Recoverements or NOS3 Annucations.       47         Fourier 11. Biccores GR-990-CORE Proze Thermatic Recoverements from DS3 Annucations.       48         Thate 8: DS3 Fruste Mark Examples.       49         Fourier 12. Junnel Dangame for the Transmit UTOPIA Interestate Bucoc.       49         Fourier 13. Tamos Disconsen for the Transmit UTOPIA Interestate Bucoc.       49         France 10. Tunnel Interestance Multiput IntERFACE       50         TRANSMIT FAYLOAD DATA INPUT INTERFACE       50         TRANSMIT FAYLOAD DATA INPUT INTERFACE + TIMING REQUIREMENTS.       50         Figure 13. Tamos Diagname Romes.       51         Fourier 11. Tunnel Diagname Romes More Soc.       52         Fourier 11. Tunnel Diagname Romes More Soc.       52         Fourier 13. Tunnel Diagname Romes More Soc.       52         Fourier 14. Tunnel Diagname Romes More Soc.       52         Fourier 13. Tunnel Diagname Romes More Soc.       52         Fourier 13. Tunnel Diagname Romes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E3 Line Side Parameters                                                           | 46 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----|

| DS3 Line Side Parameters       47         Fouse II. BELCOGE GRAGGORE PUISE TEMENTE REQUIREMENTS FOR DS3 APPLICATIONS       47         Trade 8: DS3 Transmitter lines Side Controls       48         TRANSMIT UTOPIA INTERFACE       49         France 1: Tamos Margam Forth TE TRANSMIT UTOPIA INTERFACE BLOCK       49         Trans MIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT FAYLOAD DATA INPUT INTERFACE       50         Figure 1: Tamos Morgam For The TRANSMIT PAYLOAD DATA INPUT INTERFACE BLOCK       50         Figure 1: Tamos Dangam For The TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XFTRD-TI IS CHEATING IN BOTHED TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XFTRD-TI IS CHEATING IN BOTHED TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XFTRD-TI IS CHEATING IN BOTHED TO S0         Figure 1: Tamos Dangam For THE TRANSMIT PAYLOAD DATA INPUT INTERFACE SIGCK       52         Figure 1: Tamos Dangam For THE TRANSMIT PAYLOAD DATA INPUT INTERFACE       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         Tamas Information Ford THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |    |

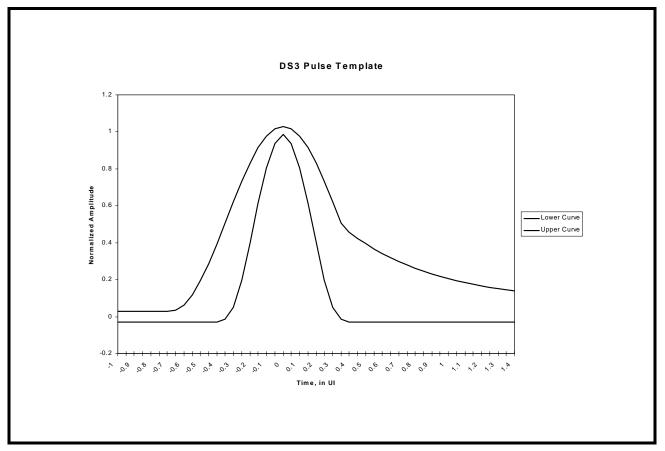

| Picure 11. BELCODE GR-496-CORE PULSE TENERALE REQUEREMENTS FOR DS3 APPLICATIONS.       47         Trale 8: DS3 Transmitte Line Side Culturu and Receiver Line Side Invut Stectications (GR-499)       48         TRANSMIT UTOPIA INTERFACE       49         Fourie 12. Taims Diversant on on the Transmit UTOPIA intersace Block.       49         TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE - TIMING REQUIREMENTS.       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE - TIMING REQUIREMENTS.       50         Trans North Modes       51         PICINE 13. Taims brochame Motes       51         PICINE 14. Taims incomme Motes       51         PICINE 15. Taims brochame Motes       51         PICINE 15. Taims Dagaan For the Transmit PayLoad Data Inveit InterFace With the XRT7RUT is corestating on Both THE D32         Min Looh.Taims Modes       51         PICINE 15. Taims Dagaan For the Transmit PayLoad Data Inveit InterFace With the XRT7RUT is corestating on Both THE D32         Min Looh.Taims Modes       52         FOLME 15. Taims Dagaan For the Transmit PayLoad Data Inveit InterFace With THE XRT7RUT is corestating on Both THE D32         FOLME 15. Taims Dagaan For the Transmit PayLoad Data Neuri InterFace With THE XRT7RUT is corestating on Both THE D32         FOLME 15. Taims Dagaan For the Transmit PayLoad Data Neuri InterFace Steck         FOLME 15. Taims Dagaan For the Tran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |    |

| <ul> <li>TABLE 8: DS3 FURSHINGS LEW STORE CONTRUT AND RECEIVER LINE SIDE UNPUT SPECIFICATIONS (GR-499)</li> <li>48</li> <li>TRANSMIT UTOPIA INTERFACE</li> <li>49</li> <li>FOURD 1: THING DURAN FOR THE TRAVENT UTOPIA INTERFACE BLOCK.</li> <li>49</li> <li>TRANSMIT PAYLOAD DATA INPUT INTERFACE - TMING REQUIREMENTS.</li> <li>50</li> <li>TRANSMIT PAYLOAD DATA INPUT INTERFACE - TMING REQUIREMENTS.</li> <li>50</li> <li>TRANSMIT PAYLOAD DATA INPUT INTERFACE - TMING REQUIREMENTS.</li> <li>50</li> <li>TRANSMIT PAYLOAD DATA INPUT INTERFACE - TMING REQUIREMENTS.</li> <li>50</li> <li>FOURE 11: THING BURGMATION TO THE TRANSMIT PAYLOAD DATA MULT INTERFACE BLOCK.</li> <li>51</li> <li>FOURE 11: THING BURGMATION TO THE TRANSMIT PAYLOAD DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE WHEN THE XETTPL71 is OPERATING IN ANOTHE DATA MULT INTERFACE MULT</li></ul>                            |                                                                                   |    |

| TARANSMIT UTOPIA INTERFACE          PREME 12. TIMMS DAGRAM FOR THE TRANSMIT UTOPIA INTERFACE BLOCK.       49         TRANSMIT PAYLOAD DATA INPUT INTERFACE.       49         TRANSMIT PAYLOAD DATA INPUT INTERFACE.       50         Fourier 13. TIMES BUGGMARTOR TO RUE TRANSMIT PAYLOAD DATA INPUT INTERFACE WIRE METARE ELCOK.       50         Fourier 13. TIMES BUGGMARTOR TO RUE TRANSMIT PAYLOAD DATA INPUT INTERFACE WIRE METART ELCOR.       51         FOURE 14. TIMES BUGGMARTOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WIRE METARTTPL71 IS GEEATING IN BOTH THE D33       52         FOURE 14. TIMES BUGGMARTOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WIRE THE RATTPL71 IS GEEATING IN BOTH THE D35       52         FOURE 15. TIMES BUGGMARTOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WIRE THE RATTPL71 IS GEEATING IN BOTH THE D35       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS.       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS.       54         TABL 21. TIMES BUGGMARTOR THE TRANSMIT OWERHEAD DATA INPUT INTERFACE METHOD 1 ACCESS)       56         FOURE 15. TIMES DAGRAM FOR THE TRANSMIT OWERHEAD DATA INPUT INTERFACE METHOD 1 ACCESS)       54         TABL 21. TIMES BUGGMARTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |    |

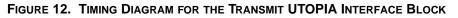

| TRANSMIT UTOPIA INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                   |    |

| Folume 12. Tanko Robinson Por the Transmut TOTPM Interpace BLock.       49         TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE - TIMING REQUIREMENTS.       50         Table 11: Tanko Buckamatorio Portite Transmut TotPation Data Invert Interpace BLOCK.       50         Folume 13: Tanko Dukamatorio Portite Transmut Parkuoad Data Invert Interpace Week the RT79L71 is Operating in Booth the D33       50         Mol Loor-Thanso Modes       51         Folume 14: Tanko Dukama Kon Parking Parkuoad Data Invert Interpace Week the RT79L71 is Operating in Booth the D33       52         Mol Loor-Thanso Modes       52         Folume 15: Tanko Dukama Kon The Transmit Parkuoad Data Invert Interpace Week the RT79L71 is Operating in Booth the D33         Mol Loor-Thanso Modes       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE Week the RT79L71 is Operating in Booth the D33         MBELE-PARLIE AND LOOC-Thanso MOdes       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA OUTPUT INTERFACE       57         Table 13: Tamko Buckama For the Transmit Overhead Data Invert Interpace (Method 1 Access)       56         Folume 14: Tamko Buckama For the Reserve Parkuado Data Output Interpace (Method 1 Access)       57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |    |

| TABLE 10: TAINING INFORMATION FOR THE TRANSMIT UTOPIA INTERFACE       99         TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         Folder 31: TAINING MOREAMER FOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE KRT79L71 IS OPERATING IN THE PASS       50         Folder 31: TAINING MORES       51         Folder 41: TAINING MORES       52         Folder 41: TAINING MORES       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         TABLE 12: TAINING MOREM FOR THE TRANSMET OVERHEAD DATA INPUT INTERFACE MEETING 1 ACCESS)       56         FOLDER 12: TAINING MOREM FOR THE TRANSMET OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       54         TABLE 12: TAINING MOREM FOR THE TRANSMET OVERHEAD DATA INPUT INTERFACE       56         FECELVE PAYLOAD DATA OUTPUT INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                   |    |

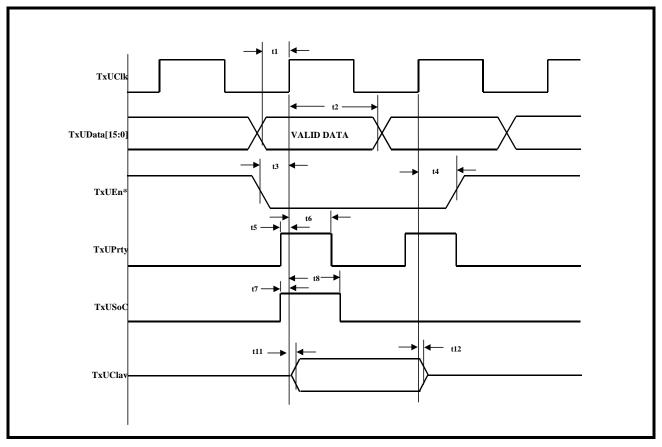

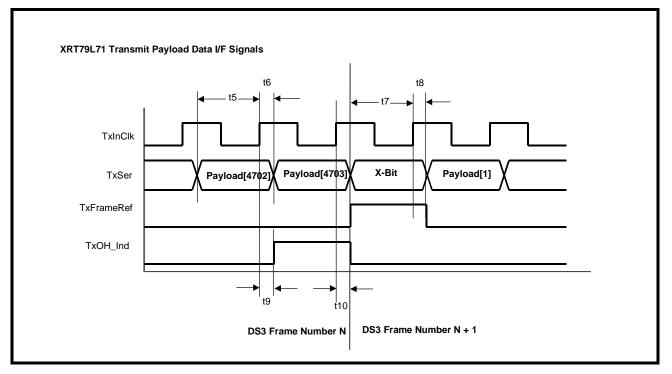

| TRANSMIT PAYLOAD DATA INPUT INTERFACE       50         TRANSMIT PAYLOAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       50         Tallel 11: Tumins information to rist the Transmer Payload Data Invert Interface BLOCK       50         Folume 13: Tumins Duckam root the Transmer Payload Data Invert Interface BLOCK       50         Non LOOP-Times Modes       51         Folume 14: Tumins Duckam root the Transmer Payload Data Invert Interface when the XRT78L71 is operating in BOTH the D33         Non LOC-Times Modes       52         Folume 15: Tuming Duckam root the Transmer Payload Data Invert Interface when the XRT78L71 is operating in BOTH the D33         Nable-Prantile and LOC-Times Modes       52         Folume 15: Tuming Duckam root the Transmer Payload Data Invert Interface when the XRT78L71 is operating in BOTH the D33         Nable-Prantile and LOCA-Times Modes       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         TRANSMIT OVERHEAD DATA OUTPUT INTERFACE       54         TRANSMIT OVERHEAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       56         Folume 17: Tuming Diversition for the Reserve Payload Data Neurly Interface (Merindo 1 Access)       56         Folume 19: Tuming Diversition for the Reserve Payload Data Output Interface (Merindo 2 Access)       56         Folume 19: Tuming Diversition for the Reserve Payload Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |    |

| TRANSMIT PAYLOAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       60         Taule 11: Tuming Parchantone or or the TRANSMET PAYLOAD DATA NEUT INTERFACE ULCK       60         Ficule 12: Tuming Modes       61         Ficule 14: Tuming Modes       61         Ficule 14: Tuming Modes       61         Ficule 14: Tuming Modes       62         Ficule 14: Tuming Modes       62         Ficule 15: Tuming Modes       62         Ficule 15: Tuming Modes       62         Ficule 16: Tuming Modes       63         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         Tabus 11: Tuming Modes       64         Tuming 12: Tuming Modes       64         Tuming 12: Tuming Modes       64         Tuming 12: Tuming Modes       65         Foure 17: Tuming Diagona rop the Transmet Overning Data Neuri Interface (Merrino 1 Access)       66         Foure 17: Tuming Diagona rop the Transmet Overning Data Neuri Interface (Merrino 1 Access)       66         Foure 19: Tuming Diagona rop the Transmet Overning Data Neuri Interface (Merrino 1 Access)       66         Foure 19: Tuming Diagona rop the Tr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |    |

| TABLE 11: TIMING NAMOR THO FOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XRT79L71 IS OPERATING IN BOTH THE DS3<br>AND LOOP. TIMING MODES       56         FIGURE 13. TIMING MODES       56         FIGURE 14. TIMING MODES       52         AND LOCAL TIMING MODES       52         MIREL FARALELE AND LOOP. TIMING MODES       52         MIREL FARALELE AND LOOP. TIMING MODES       52         FIGURE 16. TIMING DIAGRAM FOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XRT79L71 IS OPERATING IN BOTH THE STANSMIT DATA INPUT INTERFACE HOLD TATA INPUT INTERFACE         MIREL FARALELE AND LOCAL TIMING MODES       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         FIGURE 17. TIMING INGGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 1 ACCESS)       56         FIGURE 17. TIMING INGGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE METHOR 2 ACCESS       56         FIGURE 12. TIMING INGGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE STOMMETHOR TO REPORT (METHOR 2 ACCESS)       56         FIGURE 12. TIMING INGGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE       57       57         F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |    |

| <ul> <li>Figure 13. Timms Diagram for the Transmit Parkoan Data Input Interface when the XRT79L71 is operating in Both the SAT AND LOP-Timms Modes.</li> <li>Figure 14. Timms Diagram for the Transmit Parkoan Data Input Interface when the XRT79L71 is operating in Both the DS3 MB Loca-Timms Modes.</li> <li>Figure 15. Timms Diagram for the Transmit Parkoan Data Input Interface when the XRT79L71 is operating in Both the DS3 NBBE.</li> <li>Figure 15. Timms Diagram for the Transmit Parkoan Data Input Interface when the XRT79L71 is operating in Both the DS3 NBBE.</li> <li>Figure 16. Timms Diagram for the Transmit Parkoan Data Input Interface when the XRT79L71 is operating in Both the DS3 NBBE.</li> <li>Figure 16. Timms Diagram for the Transmit Parkoan Data Input Interface when the XRT79L71 is operating in Both the DS3 NBBE.</li> <li>Figure 17. Timms Diagram for the Transmit Overhead Data Input Interface Both Technologies (Stransmither Control of the Transmith Overhead Data Input Interface Both Technologies (Stransmither Technologies)</li> <li>Fecure 18. Timms Diagram for the Transmit Overhead Data Input Interface Both Technologies (Stransmither Technologies)</li> <li>Fecure 18. Timms Diagram for the Transmit Overhead Data Input Interface Both Technologies (Stransmither Stransmither Technologies)</li> <li>Fecure 19. Timms Diagram for the Receive Parkoan Data Outrul Interface Both Technologies (Stransmither Stransmither Stransmither</li></ul> |                                                                                   |    |

| AND LOOP. TIMING MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |    |

| AND LOCAL-TIMINE MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | AND LOOP-TIMING MODES                                                             | 51 |

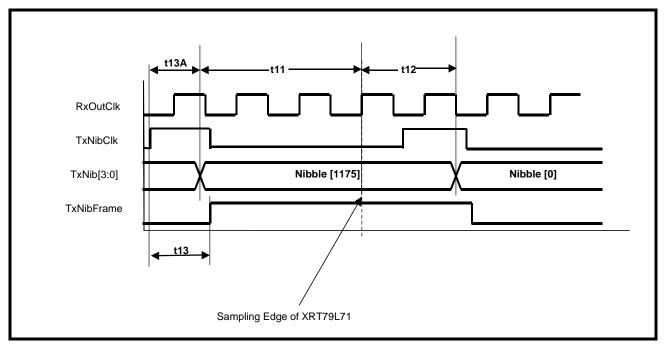

| Figure 15. Tunno Diagram for the TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XRT79L71 IS OPERATING IN BOTH THE DS3/         NIBBLE-PARALLEL AND LOOP-TIMING MODES       52         FIGURE 16. TUNNO DIAGRAM FOR THE TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XRT79L71 IS OPERATING IN BOTH THE DS3/       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRALE 12. TUNNO INFORMATION FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK       54         TABLE 12. TUNNO INFORMATION FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK       56         FIGURE 18. TUNNO DIAGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         TABLE 13. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK       57         FIGURE 13. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK       57         FIGURE 20. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE MENDED       57         FIGURE 21. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE MODE)       57         FIGURE 21. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE MODE)       57         FIGURE 21. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE MODE)       57         FIGURE 21. TUNNO DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                   |    |

| Number PARALLEL AND LOOP-TIMING MODES       52         Figure 16. Thums Dingenam For HTE TRANSMIT PAYLOAD DATA INPUT INTERFACE WHEN THE XRT79L71 IS OPERATING IN BOTH HD S3/<br>NBBLE-PARALLEL AND LOCAL-TIMING MODES       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         TRANSMIT OVERHEAD DATA NUPUT INTERFACE - TIMING REQUIREMENTS       56         Figure 17. TIMING DINGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK.       56         FIGURE 18. TIMING DINGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 1 ACCESS)       56         FIGURE 18. TIMING DINGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE METHOD 2 ACCESS)       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       57         TABLE 13. TIMING DINGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK.       57         FIGURE 19. TIMING DINGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (METHOD 1-USING RACHCEL).       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE.       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1-USING RACHCEL).       60         RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1-USING RACHCEL).       60         RECEIVE OVERHEAD DATA OUTPUT INTERFACE.       59         AC ELECTRICAL CHARACTERISTICS (CONT).       59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                   |    |

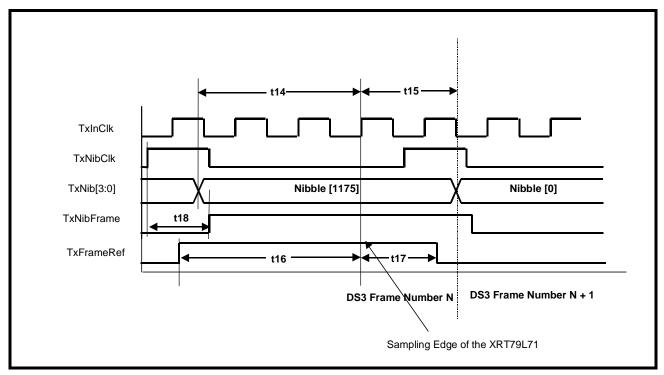

| Figure 16. Timms Diagram for the Transmit Partoab Data Interface when the XRT79L71 is operating in Both the DS3/<br>NBBLE-PracticeLIAND LOCAL-TIMING MODES       53         TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         TRAINE DISCOMMENTOR FOR the TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK       54         Figure 17. TIMING DIAGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 2 ACCESS)       66         PECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         TABLE 13. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (METHOD 2 ACCESS)       57         Figure 13. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         TABLE 13. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK       57         Figure 20. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK       57         Figure 21. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE STALLEL MODE)       58         RECEIVE OVERHEAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         PECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         Figure 21. TIMING DI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                   |    |

| TRANSMIT OVERHEAD DATA INPUT INTERFACE       54         TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS       54         Taket 12: Tuming Diagram for the Transmit Overhead Data Input Interface BLOCK       54         Figure 17. TIMING DIAGRAM for the TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 1 ACCESS)       56         PIGURE 18. TIMING DUAGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 2 ACCESS)       56         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         Taket 13: TIMING DUAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE)       57         Figure 20. TIMING DUAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         AC ELECTRICAL CHARACTERISTICS (CONT.)       59         Figure 21. TIMING DUAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1 - USING RXOHCuk)       60         Figure 23. TIMING DUAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1 - USING RXOHCuk)       60         Figure 23. TIMING DUAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1 - USING RXOHCuk)       60         Figure 24. TIMING DUAGRAM FOR THE RECEIVE OV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                   |    |

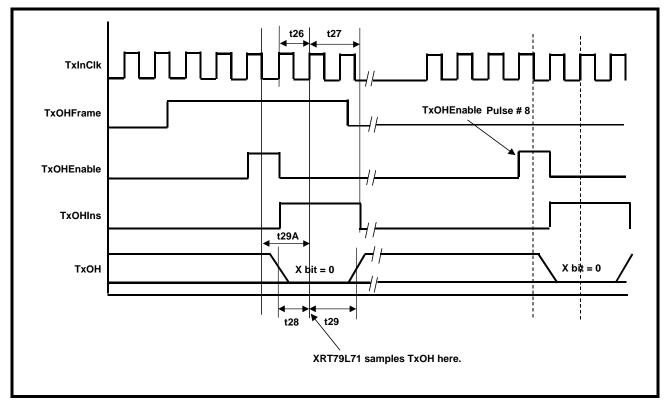

| TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS.       54         TABLE 12: TIMING INFORMATION FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 1 ACCESS)       56         FIGURE 13. TIMING DIAGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 1 ACCESS)       56         FIGURE 13. TIMING DIAGRAM FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE (METHOD 2 ACCESS)       56         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE OYLOAD DATA OUTPUT INTERFACE       57         FIGURE 13. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE)       57         FIGURE 20. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE)       58         RECEIVE OVERHEAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE METHOD 1 - USING RXOHCAK)       60         RECEIVE UTOPIA INTERFACE       59         FIGURE 21. TIMING DIAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1 - USING RXOHEMABLE)       60         RECEIVE UTOPIA INTERFACE       61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NIBBLE-PARALLEL AND LOCAL-TIMING MODES                                            | 53 |

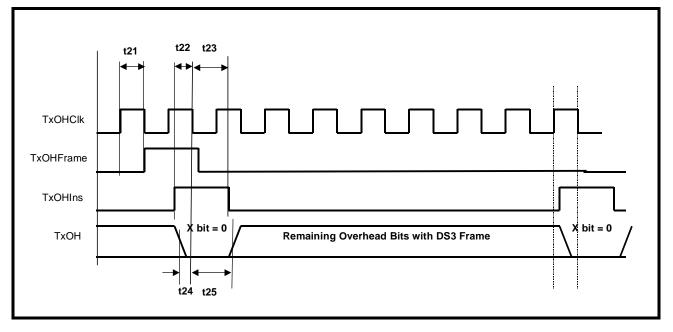

| Table 12: Tuning Information For the Transmit Overhead Data Input Interface (MEthol 1 Access)       54         Figure 17: Tuning Diagram For the Transmit Overhead Data Input Interface (MEthol 2 Access)       56         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         Table 13: Tuning Information For the Receive Payload Data Output Interface Block       57         Table 20: Tuning Diagram For the Receive Payload Data Output Interface Block       57         Figure 19: Tuning Diagram For the Receive Payload Data Output Interface Block       57         Figure 20: Tuning Diagram For the Receive Payload Data Output Interface (Serial Mode)       58         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TRANSMIT OVERHEAD DATA INPUT INTERFACE                                            | 54 |

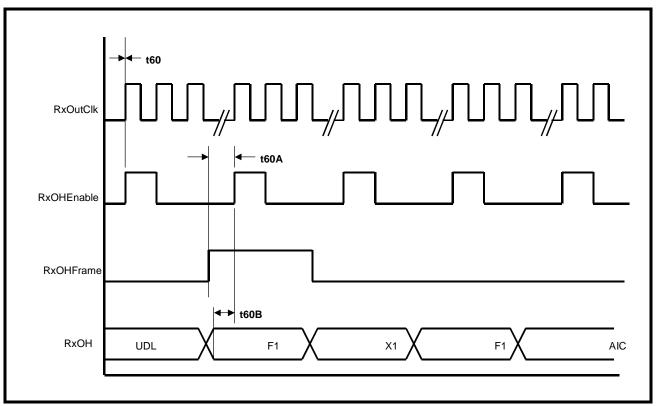

| Figure 17. Tuning Diagram for the Transmit Overhead Data InPUT InterFACE (Method 2 Access)       56 <b>RECEIVE PAYLOAD DATA OUTPUT INTERFACE</b> 57 <i>RECEIVE PAYLOAD DATA OUTPUT INTERFACE</i> 57 <i>RECEIVE PAYLOAD DATA OUTPUT INTERFACE</i> 57 <i>Table</i> 13: Timing Information for the Receive Payload Data Output Interface (Belock       57 <i>Figure</i> 20. Timing Diagram for the Receive Payload Data Output Interface (Senial Mode)       57 <i>Figure</i> 20. Timing Diagram for the Receive Payload Data Output Interface (Senial Mode)       58 <b>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</b> 59 <i>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</i> 60 <i>Figure</i> 21. Timing Diagram for the Receive Overhead Data Output Interface (Method 1 - Using RoHenale)       60 <i>RECEIVE UTOPIA INTERFACE</i> 61 <i>RECEIVE UTOPIA INTERFACE</i> 61 <i>REGEISTER MAP OF THE RECEIVE UTOPIA INTERFACE BLOCK</i> 61 <i>REGEISTER MAP OF THE RECEIVE UTOPIA INTERFACE BLOCK</i> 61 <i>RECEIVE UTOPIA INTERFACE</i> 61 <i>RECEIVE UTOPIA I</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TRANSMIT OVERHEAD DATA INPUT INTERFACE - TIMING REQUIREMENTS                      | 54 |

| Figure 18. Tuming Diagram for The Transmit Overnead Data Input InterFace (Method 2 Access)       56         RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       57         Table 13. Tuming Information for the Receive PayLoad Data Output Interface (Senal Mode)       57         Figure 20. Tuming Diagram for the Receive PayLoad Data Output Interface (Senal Mode)       58         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         AC EleCTRICAL CHARACTERISTICS (CONT.)       59         Figure 21. Tuming Diagram for the Receive Overhead Data Output Interface (Method 1 - Using RxOHCuk)       60         Figure 22. Tuming Diagram for the Receive Overhead Data Output Interface (Method 2 - Using RxOHCuk)       60         Figure 23. Tuming Diagram for the Receive Overhead Data Output Interface (Method 2 - Using RxOHEnable)       60         RECEIVE UTOPIA INTERFACE       61         RECEIVE UTOPIA INTERFACE       61         RECEIVE UTOPIA INTERFACE       63         CommonControl Registers of the XRT79L71       63         Common Control Registers of the XRT79L71       63         CLEAR-CHANNEL FRAMER BLOCK REGISTERS       64         LIU/JJITTER ATTENUATOR CONTROL REGISTER SUDION       77 </td <td>TABLE 12: TIMING INFORMATION FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK</td> <td> 54</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TABLE 12: TIMING INFORMATION FOR THE TRANSMIT OVERHEAD DATA INPUT INTERFACE BLOCK | 54 |

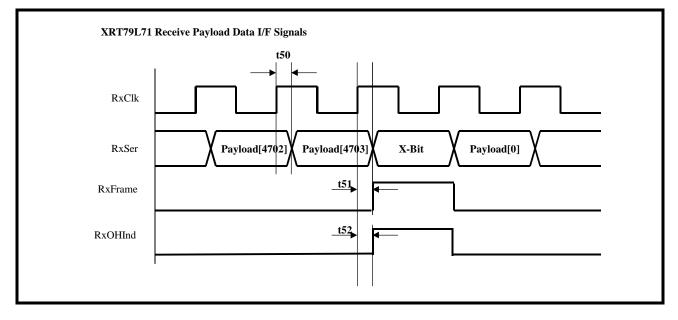

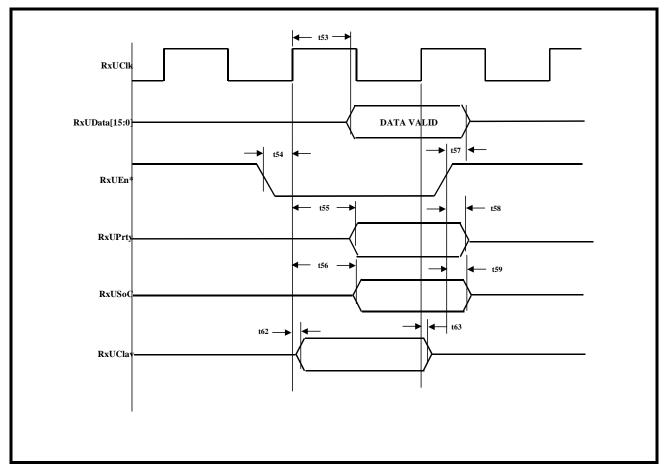

| RECEIVE PAYLOAD DATA OUTPUT INTERFACE       57         RECEIVE PAYLOAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       57         TABLE 13: TIMING INFORMATION FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK.       57         FIGURE 20: TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE).       58         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         AC ELECTRICAL CHARACTERISTICS (CONT.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                   |    |

| RECEIVE PAYLOAD DATA OUTPUT INTERFACE - TIMING REQUIREMENTS       57         TABLE 13: TIMING INFORMATION FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE).       57         FIGURE 19: TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SERIAL MODE).       57         FIGURE 20: TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (NIBBLE-PARALLEL MODE).       58         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         RECEIVE OVERHEAD DATA OUTPUT INTERFACE       59         AC ELECTRICAL CHARACTERISTICS (CONT.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |    |

| Table 13: TIMING INFORMATION FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK.       57         FIGURE 19. TIMING DIAGRAM FOR THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE (SIRAL MODE)       58 <b>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</b> 59 <i>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</i> 59 <i>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</i> - TIMING REQUIREMENTS       59 <i>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</i> 59 <i>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</i> - TIMING REQUIREMENTS       59 <i>FIGURE 21.</i> TIMING DIAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 1 - USING RXOHCIK)       60 <i>FIGURE 22.</i> TIMING DIAGRAM FOR THE RECEIVE OVERHEAD DATA OUTPUT INTERFACE (METHOD 2 - USING RXOHENABLE)       60 <b>RECEIVE UTOPIA INTERFACE</b> 61 <i>RECEIVE UTOPIA INTERFACE</i> 63 <i>COMMONCONTROL REGISTERS</i> 64 <i>LIUJITER ATTENUATOR CONTROL RECEIVE UTOPIA INTERFACE BLOCK</i> 61 <b>REGISTER MAP OF THE X</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |    |

| Figure 19. Timing Diagram for the Receive PayLoad Data Output InterFace (Serial Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                   |    |

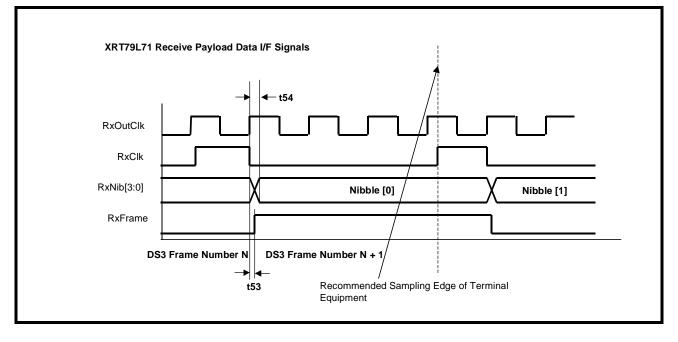

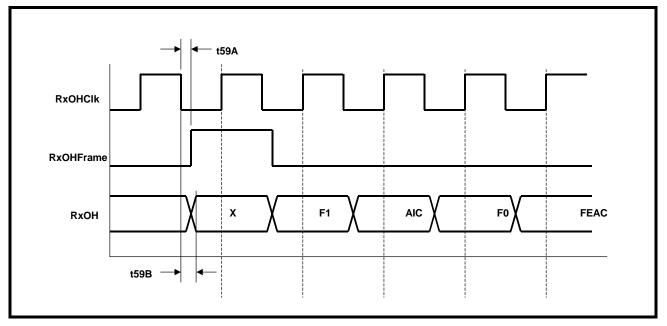

| Figure 20. Timing Diagram for the Receive PayLoad Data OUTPUT INTERFACE (NIBBLE-PARALLEL MODE)       58 <b>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</b> 59 <i>RECEIVE OVERHEAD DATA OUTPUT INTERFACE</i> 59 <i>Figure 21. Timing Diagram for the Receive Overhead Data Output Interface (Method 1 - Using RxOHCLK)</i> 60 <i>Figure 22. Timing Diagram for the Receive Overhead Data Output Interface (Method 2 - Using RxOHEnable)</i> 60 <i>RECEIVE UTOPIA INTERFACE</i> 61 <i>Figure 23. Timing Diagram for the Receive UTOPIA Interface BLOCK</i> 61 <i>REGISTER MAP OF THE XRT79L71</i> 63 <i>COMMONCONTROL REgisters of the XRT79L71</i> 63 <i>CLEAR-CHANNEL FRAMER BLOCK REGISTERS</i> 64 <i>LIUJJITTER ATTENUATOR CONTROL REGISTERS</i> 68 <i>RECEIVE ATM CELL PROCESSOR/PPP PROCESSOR BLOCK CONTROL REGISTERS</i> 69 <b>OPERATION BLOCK INTERRUPT REGISTER BIT FORMATS</b> 77 <i>OPERATION CONTROL REGISTER - BYTE 3 (ADDRESS = 0x0100)</i> 77 <i>OPERATION CONTROL REGISTER - BYTE 1 (ADDRESS = 0x0102)</i> 78 <i></i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                   |    |