# XRK32510

## 3.3V PHASE-LOCK LOOP CLOCK DRIVER WITH 10 CLOCK OUTPUTS

OCTOBER 2005 REV. 1.0.1

## **GENERAL DESCRIPTION**

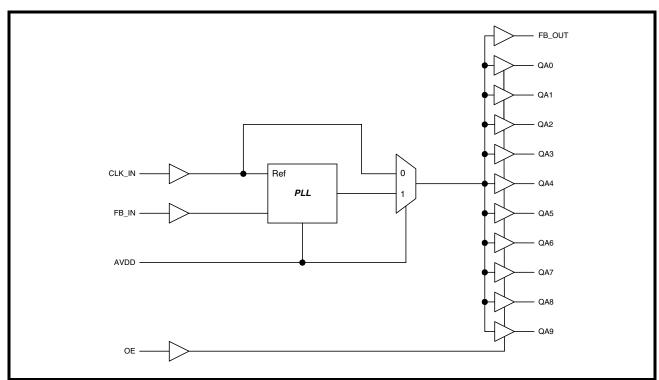

The XRK32510 is a high performance, low jitter, low skew clock driver. The XRK32510 uses phase-lock loop (PLL) tecnology to synthesize the CLK\_IN signal into 10 output signals (QA), synchronized in both phase and frequency. XRK32510 features low skew, low jitter and 50% duty cycle making it a perfect fit in dual in line memory module (DIMM) board clocking, PC133 SDRAM designs and other server applications.

The 10 outputs can be disabled using the Output Enable (OE) pin.

By connecting the Feedback Output (FB\_OUT) signal to the Feedback Input (FB\_IN) signal, the propagation delay from CLK\_IN to the 10 buffered Outputs is nearly zero.

#### **FEATURES**

- Spread Spectrum Clock Compatible

- Operating frequency range: 25MHz to 175MHz

- Low noise

- Low jitter internal PLL

- No external RC filter components required

- Meets or exceeds DPC133 registered DIMM specification 1.1

- Output Enable (OE) pin can be used to disable the CLCK\_OUT pins

- Operating supply of 3.3V VDD

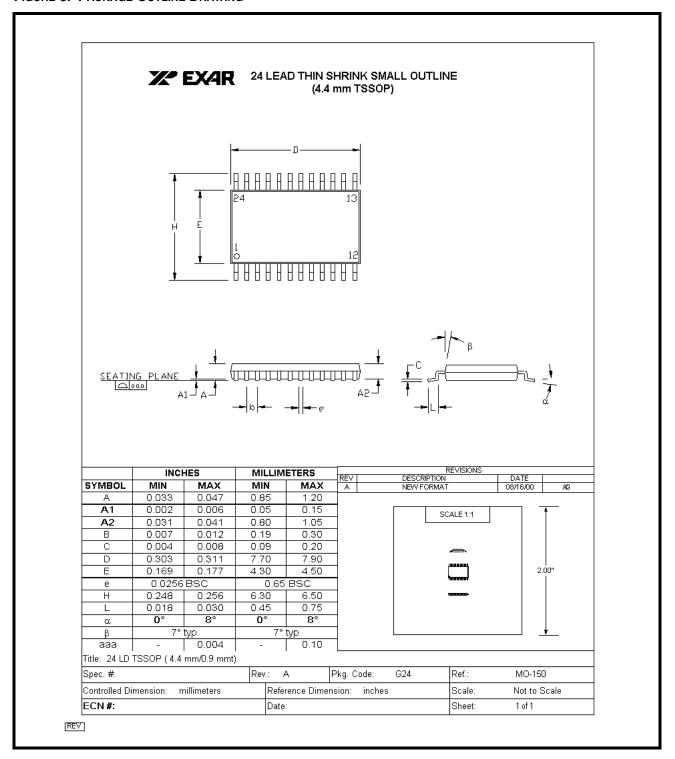

- Plastic 24 Pin TSSOP package

FIGURE 1. BLOCK DIAGRAM OF THE XRK32510

#### PRODUCT ORDERING INFORMATION

| PRODUCT NUMBER | PACKAGE TYPE | OPERATING TEMPERATURE RANGE |  |  |

|----------------|--------------|-----------------------------|--|--|

| XRK32510CG     | 24 Pin TSSOP | 0°C to +70°C                |  |  |

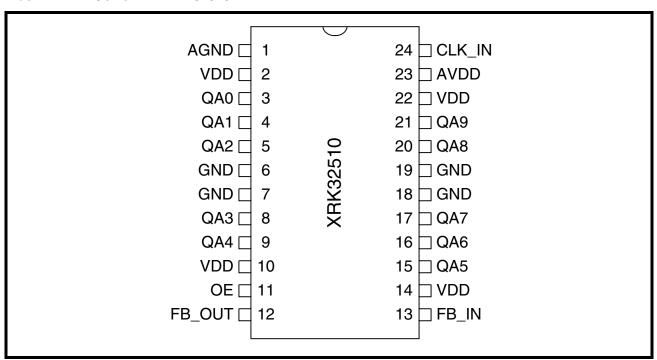

FIGURE 2. PIN OUT OF THE XRK32510

## PIN DESCRIPTIONS

| PIN# | PIN NAME | Түре      | PIN DESCRIPTION                                                                                                                                                        |

|------|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | AGND     | ****      | Analog Ground                                                                                                                                                          |

| 2    | VDD      | ***       | 3.3V Power Supply                                                                                                                                                      |

| 10   | VDD      |           |                                                                                                                                                                        |

| 14   | VDD      |           |                                                                                                                                                                        |

| 11   | OE       | INPUT     | Output Enable:                                                                                                                                                         |

|      |          |           | "High" = Normal operation, Clock outputs (QA[0:9]) enabled                                                                                                             |

|      |          |           | "Low" = Clock outputs (QA[0:9]) disabled                                                                                                                               |

| 12   | FB_OUT   | OUTPUT    | Feedback Output:                                                                                                                                                       |

|      |          |           | When this pin is connected to FB_IN, the propagation delay from                                                                                                        |

|      |          |           | CLK_IN to any of the 10 QA pins will be nearly zero.                                                                                                                   |

| 13   | FB_IN    | INPUT     | Feedback Input                                                                                                                                                         |

| 3    | QA0      | OUTPUT(S) | Buffered Clock Outputs:                                                                                                                                                |

| 4    | QA1      |           | These 10 outputs provide low-skew, low jitter, 50% duty cycle renditions                                                                                               |

| 5    | QA2      |           | of CLK_IN                                                                                                                                                              |

| 8    | QA3      |           |                                                                                                                                                                        |

| 9    | QA4      |           |                                                                                                                                                                        |

| 15   | QA5      |           |                                                                                                                                                                        |

| 16   | QA6      |           |                                                                                                                                                                        |

| 17   | QA7      |           |                                                                                                                                                                        |

| 20   | QA8      |           |                                                                                                                                                                        |

| 21   | QA9      |           |                                                                                                                                                                        |

| 22   | VDD      | ***       | 3.3V Digital Power Supply                                                                                                                                              |

| 23   | AVDD     | ***       | 3.3V Analog Supply:                                                                                                                                                    |

|      |          |           | If this pin is connected to ground, the PLL is disabled and will be bypassed and the CLK_IN signal will be connected directly to the output buffers of the 10 QA pins. |

| 24   | CLK_IN   | INPUT     | Reference Clock Input                                                                                                                                                  |

## **FUNCTIONAL OPERATION**

| INPU | TS   |           | PLL    |        |           |

|------|------|-----------|--------|--------|-----------|

| OE   | AVDD | QA[0:9]   | FB_OUT | SOURCE | CONDITION |

| 0    | 3.3V | 0         | Driven | PLL    | ON        |

| 1    | 3.3V | Driven    | Driven | PLL    | ON        |

|      |      | BUFFER MC | DDE    |        |           |

| 0    | 0    | 0         | Driven | CLK_IN | OFF       |

| 1    | 0    | Driven    | Driven | CLK_IN | OFF       |

#### **ABSOLUTE MAXIMUM RATINGS**

| Analog Supply Voltage (AVDD)        | AVDD < (VDD +0.7V)      |

|-------------------------------------|-------------------------|

| Supply Voltage (VDD)                | 4.3V                    |

| Logic Inputs                        | GND- 0.5V to VDD + 0.5V |

| Ambient Operating Temperature Range | 0°C to +70°C            |

| Storage Temperature Range           | -65°C to +150°C         |

#### **ELECTRICAL CHARACTERISTICS -OUTPUT**

$T_A$  = 0 - 70°C, VDD = AVDD = 3.3V +/- 10%,  $C_L$  = 20 - 30pF,  $R_L$  = 470 $\Omega$ , (unless otherwise stated)

| SYMBOL             | PARAMETER                             | MIN  | TYP  | MAX   | UNITS | Conditions                                            |  |

|--------------------|---------------------------------------|------|------|-------|-------|-------------------------------------------------------|--|

| R <sub>DSP</sub>   | Output Impedance                      |      | 36   |       | Ω     | $V_O = VDD/2$                                         |  |

| R <sub>DSN</sub>   | Output Impedance                      |      | 32   |       | Ω     | V <sub>O</sub> = VDD/2                                |  |

| V <sub>OH</sub>    | Output High Voltage                   | 2.4  | 3.0  |       | V     | I <sub>OH</sub> = -8mA                                |  |

| V <sub>OL</sub>    | Output Low Voltage                    |      | 0.2  |       |       | I <sub>OL</sub> = 8mA                                 |  |

|                    |                                       |      | -33  | -13.6 |       | V <sub>OH</sub> = 2.4V                                |  |

| I <sub>OH</sub>    | Output High Current                   |      | -48  | -22   | mA    | V <sub>OH</sub> = 2.0V                                |  |

|                    | 0                                     | 19   | 28   |       |       | V <sub>OL</sub> = 0.8V                                |  |

| l <sub>OL</sub>    | Output Low Current                    | 13   | 19   |       | mA    | V <sub>OL</sub> =0.55V                                |  |

| T <sub>r</sub>     | Rise Time <sup>1</sup>                | 0.5  | 0.8  | 2.1   | ns    | $V_{OH} = 2.0V, V_{OL} = 0.8V$                        |  |

| T <sub>f</sub>     | Fall Time <sup>1</sup>                | 0.5  | 0.9  | 2.7   | ns    | $V_{OL} = 0.8V, V_{OH} = 2.0V$                        |  |

| D <sub>t</sub>     | Duty Cycle <sup>1</sup>               | 45   | 50   | 55    | %     | VT = 1.5V, C <sub>L</sub> = 30pF                      |  |

| _                  |                                       |      | 28.7 | 100   |       | @66 - 100MHz, loaded outputs                          |  |

| Tcyc-cyc           | Cycle to Cycle Jitter <sup>1</sup>    |      | 25   | 75    | ps    | @133MHz, loaded outputs                               |  |

| T <sub>j</sub> ABS | Absolute Jitter <sup>1</sup>          |      | 57   |       | ps    | 10,000 cycles, C <sub>L</sub> = 30 pF                 |  |

| T <sub>sk</sub>    | Skew <sup>1</sup>                     |      | 29   | 150   | ps    | VT = 1.5V (Window) Output to Output                   |  |

| T <sub>pe</sub>    | Phase Error <sup>1</sup>              | -150 |      | 150   | ps    | V <sub>T</sub> = VDD/2, CLK_IN to FB_IN               |  |

| T <sub>pej</sub>   | Phase Error Jitter <sup>1</sup>       | -50  | 35   | 50    | ps    | V <sub>T</sub> = VDD/2, CLK_IN to FB_IN, Delay Jitter |  |

| D <sub>R1</sub>    | Delay Input to<br>Output <sup>1</sup> |      | 3.5  | 3.7   | ns    | V <sub>T</sub> = 1.5V, PLL Disabled (AVDD = 0)        |  |

#### Note:

1. Guaranteed by design, not 100% tested in production

## REV. 1.0.1

## **ELECTRICAL CHARACTERISTICS - INPUT AND SUPPLY**

$T_A = 0 - 70$ °C, VDD= AVDD = 3.3V +/- 10% (unless otherwise stated)

| SYMBOL          | PARAMETER          | MIN          | TYP | MAX          | UNITS | Conditions                  |

|-----------------|--------------------|--------------|-----|--------------|-------|-----------------------------|

| V <sub>IH</sub> | Input High Voltage | 2            |     | VDD +<br>0.3 | V     |                             |

| V <sub>IL</sub> | Input Low Voltage  | GND -<br>0.3 |     | 0.8          | V     |                             |

| I <sub>IH</sub> | Input High Current |              | 0.1 | 100          | μΑ    | V <sub>IN</sub> = VDD       |

| I <sub>IL</sub> | Input Low Current  |              | 19  | 50           | μΑ    | V <sub>IN</sub> = 0V        |

| I <sub>DD</sub> | Operating Current  |              | 140 | 170          | mA    | $C_L = 0pF, F_{IN} = 66MHz$ |

| C <sub>IN</sub> | Input Capacitance  |              | 4   |              | pF    | Logic Inputs                |

| C <sub>O</sub>  | Output Capacitance |              | 8   |              | pF    | Logic Outputs               |

FIGURE 3. PACKAGE OUTLINE DRAWING

#### REVISIONS

| REV. # | DATE     | DESCRIPTION OF CHANGES                                                         |

|--------|----------|--------------------------------------------------------------------------------|

| 1.0.0  | 9/23/05  | Initial issue.                                                                 |

| 1.0.1  | 10/06/05 | Product ordering information: Remove "F" product numbers and Lead Free column. |

|        |          |                                                                                |

|        |          |                                                                                |

|        |          |                                                                                |

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 2005 EXAR Corporation

Datasheet October 2005.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.