#### 1.0 INTRODUCTION

#### **GENERAL DESCRIPTION** 1.1

This document describes a single chip VLSI Peripheral Cache Manager, SCSI bus controller. and Disk Controller device, the WD61C96A, for target mode of operation. The WD61C96A is a highly integrated CMOS VLSI device which combines the functionality of the WD61C40A Disk Manager and the WD33C96A SCSI Manager. All of the features of the two separate devices are retained, including:

- 8-bit Parallel Disk Data Bus.

- 4M by 16-bit Buffer Memory Interface.

- 16-bit Wide SCSI Interface.

- Fast SCSI timing.

- Internal DMA transfer between devices.

- External DMA port for connecting a second WD61C40A (208-pin device only).

- Single 8-bit, 25 MHz 80186 Microprocessor port.

#### 1.1.1 Features NOT included

The only microprocessor bus type supported is multiplexed direct addressing. The other modes supported by the WD33C96A are not available.

#### 1.1.2 **Deviations**

There are several deviations from the device specifications provided for the WD33C96A and the WD61C40A. These are:

- The I/O Map Test modes are different.

- The DMA (Host) bus is not observable during normal operation on Host Channel A. A test mode is provided to enable the bus to the output. The bus behaves normally for Host Channel B operation, but only for an external WD61C40A slave.

- The WD61C40A portion of the device operates in the burst slave mode and single cycle master mode only and the WD33C96A portion operates in burst and single cycle master mode only.

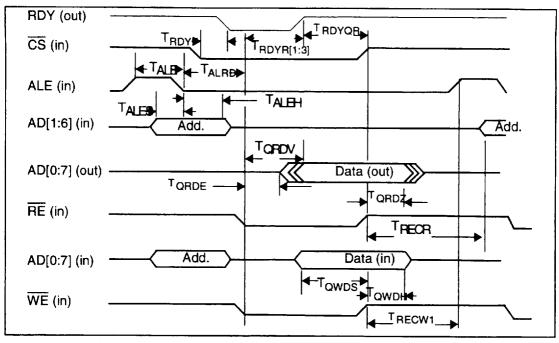

#### Microprocessor Interface 1.1.3

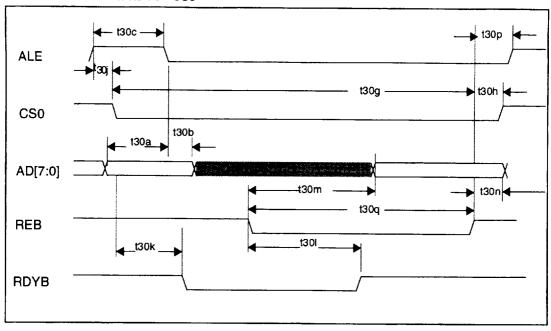

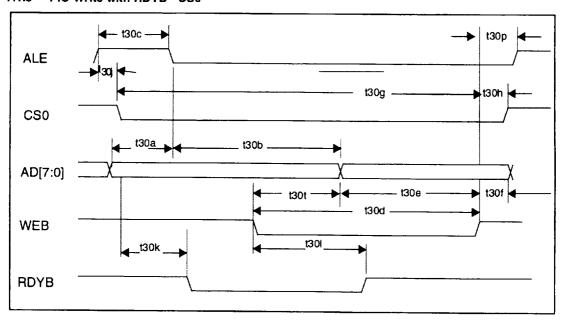

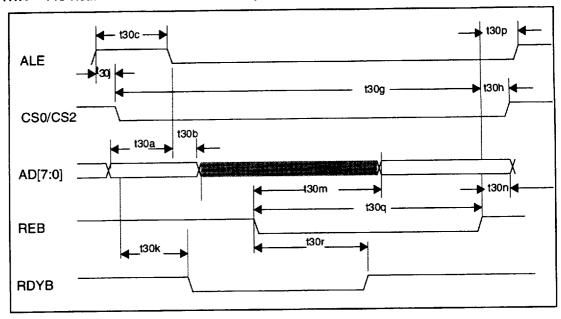

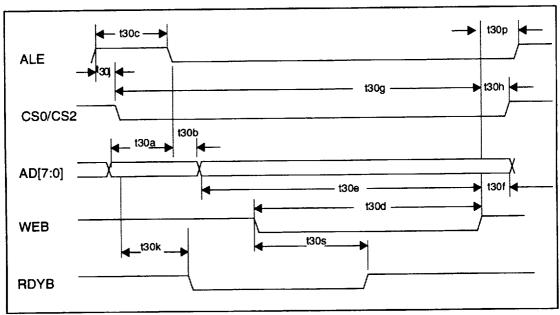

The dedicated microprocessor interface supports 8-bit microprocessors with multiplexed address/ data busses. The microprocessor can access the internal registers and FIFO through this port by using the five following control signals: WEB, REB. ALE, CS0, CS2, and RDYB. The device must be externally mapped into a 384 byte space. A chip select, CS0 or CS2, must be presented to this device for any read or write access. CS0 accesses the registers associated with the WD61C40 functions (256-byte space). CS2 accesses the registers associated with the WD33C96 functions (128-byte space).

The WD61C96A sends a Ready signal, RDYB, to the microprocessor whenever an extended read or write strobe is required. This is done when the microprocessor wishes to access the buffer memory.

#### 1.1.4 **Host Port Interface**

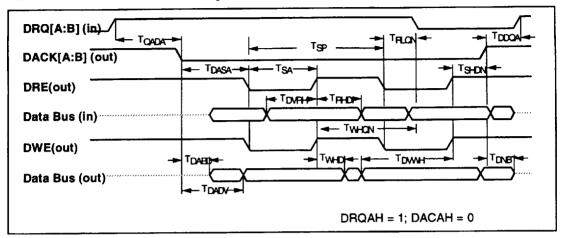

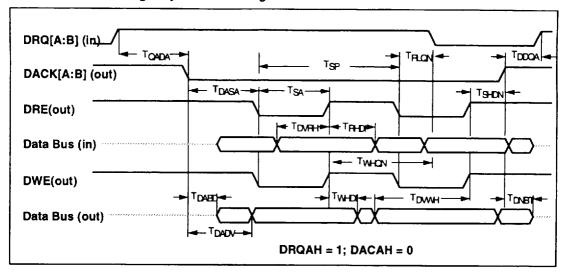

The Host Port is exactly as defined for the WD33C96A: there are two DMA channels available, DREQA/DACKA and DREQB/DACKB. Channel A is dedicated to the internal WD61C40A function which should be programmed as a slave. Channel B is available for use by a second, external WD61C40A device (programmed as a slave), or other generic DMA slave.

Data can be transferred in 8-bit or 16-bit mode. The maximum transfer rate is 10 megatransfers per second.

#### SCSI Interface 1.1.5

The WD61C96A uses a 32-word by 9-bit (8 bits plus parity) Dual Port Register to store special information such as commands, messages, and status. The information is transferred between the SCSI bus and the registers under control of a The writable control store sequence. microprocessor can randomly access these registers.

#### **Buffer Interface** 1.1.6

The buffer port is designed to support 16-bit DRAM configurations up to 4MWords. Memory size and bus timing are all programmable.

The Buffer Manager reduces microprocessor support and provides buffer segmentation hardware assist logic. Skip mask modes reduce microprocessor interrupts.

# 1.1.7 Testability

The WD61C96A includes several features to improve testability of the device:

- All RAM and Register files contain internal BIST logic.

- Full scan test methodology.

- Most microprocessor registers are readable.

- Test modes exist for the large transfer counters, address pointers and major internal logic blocks.

- The I/O pins include the I/O Mapping Test feature for PCB testing.

- The Disk Port contains logic which guarantees data integrity (LRC, CRC, ECC checking).

- The Writable Control Store RAMs are readwritable by the microprocessor.

- A host bus test pin allows the internal DMA bus between the WD61C40A and WD33C96A cores to be observed on the host bus pins.

### 1.2 FEATURES

- High Flexibility

- Programmable SCSI data bus width.

- Programmable synchronous transfer period.

- Programmable DMA data bus width.

- Programmable DMA transfer period.

- Programmable DRQ and DACK polarities.

- Sequencer with a writable control store.

- Capability for direct control of the SCSI signals by the microprocessor.

- Support for specifying transfer lengths in logical and physical blocks.

- High Performance

- High-speed SCSI transfers, up to 10 Mtransfers/s.

- Fast DMA transfer rate, up to 10 Mtransfers/s.

- Dedicated eight-bit port for a high-speed microprocessor.

- Pipelined 24-bit transfer counter.

- Two DMA ports (one internal, one external) to support striping and mirroring.

- Sixteen-word FIFO supports synchronous offsets up to sixteen words or thirty-two bytes.

### Low Overhead

- Minimal SCSI bus overhead and latency.

- Automatic response to selection and reselection.

- Automatic decoding of SCSI command descriptor block lengths.

- Automatic response to DMA requests.

- Efficient interaction with the external and internal WD61C40A Disk Controller to minimize microprocessor overhead.

- Interrupt masking capability.

### Data Integrity

- Longitudinal Redundancy Check (LRC) feature maximizes data transfer integrity.

- Support for data mirroring and striping.

- Parity on all internal data busses and on the FIFO and Dual Port registers.

- Built-in Self Test (BIST) logic for the Writable Control Store, FIFO, and Dual Port registers.

### Other Features

- 48 mA drivers for direct connection to a single-ended SCSI interface.

- Support for external drivers and receivers for single-ended and differential applications (WD33C96A).

- Single +5 V supply.

- Sleep mode minimizes power consumption.

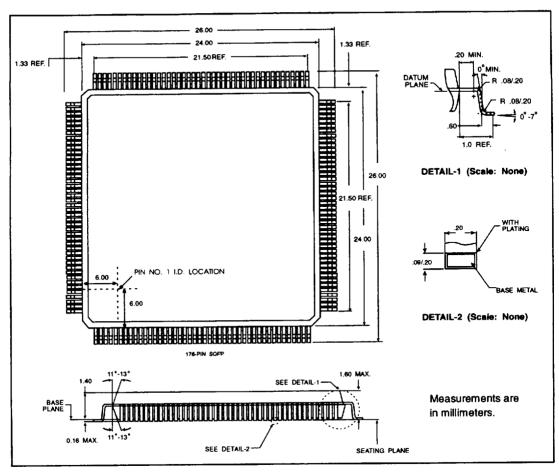

- 176-pin SQFP and PQUAD packages

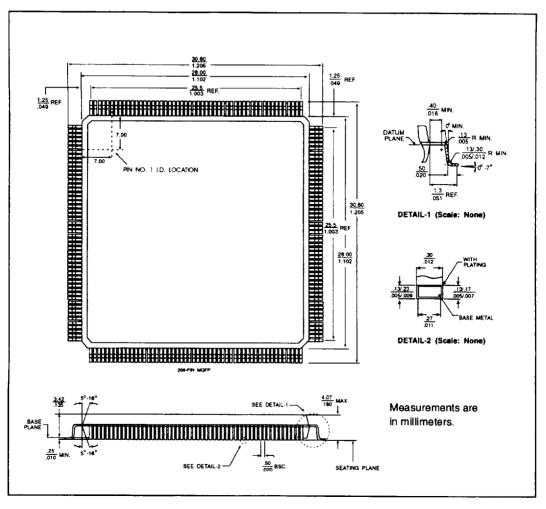

- 208-pin MQFP packages

#### 1.3 ORDERING INFORMATION

The WD61C96A is available in three package options (SW, QW and MZ) with four different bonding options (A, B, C, and D). See Table 3-1, OPTIONAL PACKAGE FEATURES, on page 5 for a description of the packing options. Following are the device order numbers:

| ORDER P/N   | DESCRIPTION                                         |

|-------------|-----------------------------------------------------|

| 61C96ASWA01 | SQFP, 176 pins, bonding<br>Option A                 |

| 61C96ASWC01 | SQFP, 176 pins, bonding<br>Option C                 |

| 61C96AQWA01 | PQUAD, 176 pins, bonding<br>Option A                |

| 61C96AQWC01 | PQUAD, 176 pins, bonding<br>Option C                |

| 61C96AMZB01 | MQFP w/heat spreader,<br>208 pins, bonding Option B |

| 61C96AMZD01 | MQFP w/heat spreader,<br>208 pins, bonding Option D |

#### 1.4 REFERENCE DOCUMENTS

For additional information, please consult the following Western Digital publications:

- WD33C96A SCSI Protocol Chip Specification 96 - 100242.

- WD61C40A High-Performance Disk Manager Engineering Specification 96-106140.

- WD10C01 Disk Controller Specification 96-101474.

#### 1.5 **DOCUMENT SCOPE**

This document provides an architectural signal descriptions, register overview, descriptions, theory of operations, and timing specifications for the WD61C96A. This device is used to control SCSI disks in the target mode of operation. Other topics covered are: Disk/SCSI Control Store, Disk/SCSI LRC operations, error correction, Disk/SCSI interrupts, and test modes.

# 2.0 ARCHITECTURE OVERVIEW

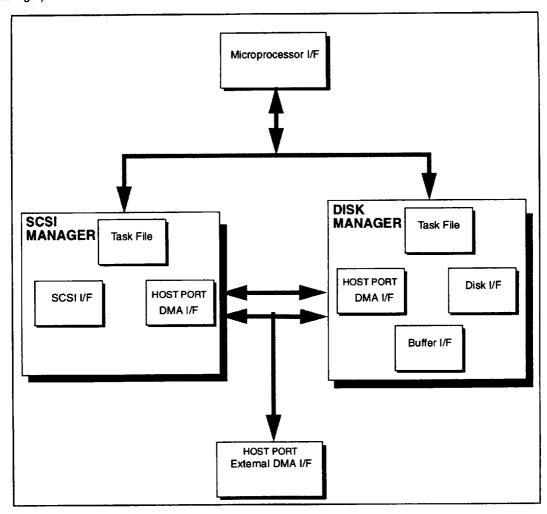

The WD61C96A is a combination of the WD61C40A (Disk Manager) and WD33C96A (SCSI Bus Manager) devices.

FIGURE 2-1 BLOCK DIAGRAM OF WD61C96A

The SCSI Block contains all of the functions of the WD33C96A, including a Task File of microprocessor accessible registers, a 16-bit Wide/Fast SCSI Interface, and a 16-bit DMA Interface.

The Disk Block contains all of the functions of the WD61C40A, including a Task File of microprocessor accessible registers, a 16-bit Buffer Interface, an 8-bit Disk Interface and a 16-bit DMA Interface.

The External DMA Interface is used to connect a second WD61C40A as a DMA slave.

The Microprocessor Interface contains logic which supports a multiplexed data/address bus microprocessor with wait state capabilities. Note that this is the only mode supported. This includes Intel 80196 and 80186 devices.

#### 3.0 SIGNAL DESCRIPTION

The WD61C96A device has four bonding options. These options make trade-offs between:

- Single-ended Only and Single-ended/Differential SCSI support

- 2. Single and Dual LUN support

Quantity of GPX, GPY, POR latch pins, Optional Functional features

Table 3-1 describes the features of each package type. Tables 3-2 through 3-5 list the pin/signals for each option. Refer to Appendix A for more information concerning packaging.

| FEATURES             | OPTION A                                                                     | OPTION B              | OPTION C                                                                                         | OPTION D              |

|----------------------|------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|-----------------------|

| Package Pins         | 176                                                                          | 208                   | 176                                                                                              | 208                   |

| Single Ended<br>SCSI | yes                                                                          | yes                   | yes                                                                                              | yes                   |

| Differential<br>SCSI | no                                                                           | yes                   | no                                                                                               | yes                   |

| Single LUN           | yes                                                                          | yes                   | yes                                                                                              | yes                   |

| Dual LUN             | no                                                                           | yes                   | no                                                                                               | yes                   |

| GPX Pins             | 8<br>(GPX7:0)                                                                | 5<br>(GPX4:0)         | 8<br>(GPX7:0)                                                                                    | 0                     |

| GPY Pins             | 4<br>(GPY3:0)                                                                | 4<br>(GPY3:0)         | 4<br>(GPY3:0)                                                                                    | 4<br>(GPY3:0)         |

| POR Pins             | Total: 12<br>(BD15:11,<br>BDP10:9,<br>BDP4:3, BD2:0)<br>Not bonded:<br>BD8:5 | Total: 16<br>(DB15:0) | Total: 7<br>(BD15:13,<br>BDP10,<br>BDP4:3, BD0)<br>Not bonded:<br>BD8:5, BDP9,<br>BD2:1, BD12:11 | Total: 16<br>(BD15:0) |

**TABLE 3-1 OPTIONAL PACKAGE FEATURES**

All outputs are tristated when the Power on reset, RESETB, is active (low) except:

- RDYB is released open-drain.

- · RSTF is low.

- SDOE[15:0], SDPOE, TGS, and IGS are low.

| PIN - SIGNAL |

|--------------|--------------|--------------|--------------|--------------|

| 1 - DGND     | 37 - CGND    | 73 - SD11    | 109 - RST    | 145 - GPY1   |

| 2 - BF5      | 38 - RDGATE  | 74 - SD10    | 110 - TST2B  | 146 - GPY0   |

| 3 - BF6      | 39 - WRTGATE | 75 - SD9     | 111 - CVDD   | 147 - GPX0   |

| 4 - DGND     | 40 - DATA0   | 76 - DGND    | 112 - CGND   | 148 - A8     |

| 5 - BF7      | 41 - DATA1   | 77 - SD8     | 113 - SCTL   | 149 - DGND   |

| 6 - BFPL     | 42 - DATA 2  | 78 - DVDD    | 114 - WEB    | 150 - A7     |

| 7 - DGND     | 43 - DGND    | 79 - CVDD    | 115 - REB    | 151 - A6     |

| 8 - BF8      | 44 - DATA3   | 80 - CGND    | 116 - CS0    | 152 - A5     |

| 9 - GPX3     | 45 - DATA4   | 81 - SDP1    | 117 - CS2    | 153 - A4     |

| 10 - BF9     | 46 - DVDD    | 82 - SDP     | 118 - ALE    | 154 - BCLK   |

| 11 - DGND    | 47 - DATA5   | 83 - DGND    | 119 - RESETB | 155 - DVDD   |

| 12 - BF10    | 48 - DATA6   | 84 - SD7     | 120 - GPX7   | 156 - CVDD   |

| 13 - BD11    | 49 - DGND    | 85 - SD6     | 121 - AD7    | 157 - CGND   |

| 14 - BF11    | 50 - DATA7   | 86 - SD5     | 122 - DGND   | 158 - A3     |

| 15 - CVDD    | 51 - DATAP   | 87 - DGND    | 123 - AD6    | 159 - A2     |

| 16 - CGND    | 52 - GPX4    | 88 - REQ     | 124 - AD5    | 160 - DGND   |

| 17 - DGND    | 53 - AMDET   | 89 - SD4     | 125 - GPX6   | 161 - A1     |

| 18 - BD12    | 54 - RRCLK   | 90 - SE      | 126 - AD4    | 162 - A0     |

| 19 · BF12    | 55 - GPX5    | 91 - SD3     | 127 - DGND   | 163 - GPX1   |

| 20 - DVDD    | 56 - WRAP    | 92 - DGND    | 128 - AD3    | 164 - BD0    |

| 21 - BD13    | 57 - DRVFLT  | 93 - SD2     | 129 - AD2    | 165 - BF0    |

| 22 - BF13    | 58 - BDP9    | 94 - SD1     | 130 - DVDD   | 166 - DGND   |

| 23 - DGND    | 59 - SMDET   | 95 - CVDD    | 131 - AD1    | 167 - BD1    |

| 24 - BD14    | 60 - BDP4    | 96 - CGND    | 132 - BDP10  | 168 - BF1    |

| 25 - BF14    | 61 - CVDD    | 97 - SD0     | 133 - DGND   | 169 - BD2    |

| 26 - BD15    | 62 - CGND    | 98 - DGND    | 134 - AD0    | 170 - BF2    |

| 27 - BF15    | 63 - IDXDET  | 99 - SEL     | 135 - RSTF   | 171 - DGND   |

| 28 - DGND    | 64 - BDP3    | 100 - DVDD   | 136 - CVDD   | 172 - BF3    |

| 29 - BFPH    | 65 - TST1B   | 101 - IO     | 137 - CGND   | 173 - BF4    |

| 30 - GPX2    | 66 - SCLK    | 102 - ATN    | 138 - INT2   | 174 - CVDD   |

| 31 - MEMW    | 67 - SD15    | 103 - DGND   | 139 - INT1   | 175 - CGND   |

| 32 - CAS     | 68 - DGND    | 104 - BSY    | 140 - INTO   | 176 - DVDD   |

| 33 - RAS     | 69 - SD14    | 105 - ACK    | 141 - RDY    |              |

| 34 - DGND    | 70 - SD13    | 106 - CD     | 142 - DGND   |              |

| 35 - WRTCLK  | 71 - SD12    | 107 - DGND   | 143 - GPY3   |              |

| 36 - CVDD    | 72 - DGND    | 108 - MSG    | 144 - GPY2   |              |

TABLE 3-2 PIN TO SIGNAL (OPTION A - 176-PIN SQFP)

79-890003-000 (REV A)

| PIN - SIGNAL |

|--------------|--------------|--------------|--------------|--------------|--------------|

| 1 - DATA3    | 37 - BF9     | 73 - DGND    | 109 - DGND   | 145 - SDOE1  | 181 - DGND   |

| 2 - DGND     | 38 - BD9     | 74 - A2      | 110 - AD4    | 146 - CGND   | 182 - SD12   |

| 3 - DATA2    | 39 - GPX3    | 75 - DRQB    | 111 =- AD5   | 147 - CVDD   | 183 - SDOE12 |

| 4 - DATA1    | 40 - BF8     | 76 - A3      | 112 - AD6    | 148 - SD1    | 184 - SDOE13 |

| 5 - DATA0    | 41 - BD8     | 77 - DACKB   | 113 - DGND   | 149 - SDOE2  | 185 - SD13   |

| 6 - WRTGATE  | 42 - DGND    | 78 - CGND    | 114 - AD7    | 150 - SD2    | 186 - SDOE14 |

| 7 - RDGATE   | 43 - BFPL    | 79 - CVDD    | 115 - RESETB | 151 - DGND   | 187 - SD14   |

| 8 - CGND     | 44 - BDPL    | 80 - DVDD    | 116 - ALE    | 152 - SD3    | 188 - DGND   |

| 9 - CVDD     | 45 - BF7     | 81 - BCLK    | 117 - CS2    | 153 - SDOE3  | 189 - SD15   |

| 10 - WRTCLK  | 46 - BD7     | 82 - A4      | 118 - CS0    | 154 - SE     | 190 - SDOE15 |

| 11 - DGND    | 47 - DGND    | 83 - A5      | 119 - REB    | 155 - SDOE4  | 191 - SCLK   |

| 12 - RAS     | 48 - BF6     | 84 - A6      | 120 - WEB    | 156 - SD4    | 192 - TST1B  |

| 13 - CAS     | 49 - BD6     | 85 - A7      | 121 - SCTL   | 157 - REQ    | 193 - BDP3   |

| 14 - MEMW    | 50 - BF5     | 86 - DGND    | 122 - CGND   | 158 - DGND   | 194 - IDXDET |

| 15 - GPX2    | 51 - BD5     | 87 - A8      | 123 - CVDD   | 159 - SD5    | 195 - CVDD   |

| 16 - BFPH    | 52 - DGND    | 88 - DWEB    | 124 - TSTB   | 160 - SDOE5  | 196 - SMDET  |

| 17 - BDPH    | 53 - DVDD    | 89 - DREB    | 125 - RSTIN  | 161 - SDOE6  | 197 - DRVFLT |

| 18 - DGND    | 54 - CGND    | 90 - GPX0    | 126 - RST    | 162 - SD6    | 198 - WRAP   |

| 19 - BF15    | 55 - CVDD    | 91 - GPY0    | 127 - MSG    | 163 - SDOE7  | 199 - RRCLK  |

| 20 - BD15    | 56 - BF4     | 92 - GPY1    | 128 - DGND   | 164 - SD7    | 200 - AMDET  |

| 21 - BF14    | 57 - BD4     | 93 - GPY2    | 129 - CD     | 165 - DGND   | 201 - GPX4   |

| 22 - BD14    | 58 - BF3     | 94 - GPY3    | 130 - ACK    | 166 - SDP    | 202 - DATAP  |

| 23 - DGND    | 59 - BD3     | 95 - DGND    | 131 - DSENSE | 167 - SDPOE  | 203 - DATA7  |

| 24 - BF13    | 60 - DGND    | 96 - RDY     | 132 - TGS    | 168 - SDP1   | 204 - DGND   |

| 25 - BD13    | 61 - BF2     | 97 - INTO    | 133 - BSYIN  | 169 - SDOE8  | 205 - DATA6  |

| 26 - DVDD    | 62 - BD2     | 98 - INT1    | 134 - BSY    | 170 - CGND   | 206 - DATA5  |

| 27 - BF12    | 63 - BF1     | 99 - INT2    | 135 - DGND   | 171 - CVDD   | 207 - DVDD   |

| 28 - BD12    | 64 - BD1     | 100 - CGND   | 136 - ATN    | 172 - DVDD   | 208 - DATA4  |

| 29 - DGND    | 65 - DGND    | 101 - CVDD   | 137 - IO     | 173 - SD8    |              |

| 30 - CGND    | 66 - BF0     | 102 - RSTF   | 138 - IGS    | 174 - DGND   |              |

| 31 - CVDD    | 67 - BD0     | 103 - AD0    | 139 - DVDD   | 175 - SD9    |              |

| 32 - BF11    | 68 - GPX1    | 104 - DGND   | 140 - SELIN  | 176 - SDOE9  |              |

| 33 - BD11    | 69 - DRQA    | 105 - AD1    | 141 - SEL    | 177 - SDOE10 |              |

| 34 - BF10    | 70 - A0      | 106 - DVDD   | 142 - DGND   | 178 - SD10   |              |

| 35 - BD10    | 71 - DACKA   | 107 - AD2    | 143 - SD0    | 179 - SDOE11 |              |

| 36 - DGND    | 72 - A1      | 108 - AD3    | 144 - SDOE0  | 180 - SD11   |              |

TABLE 3-3 PIN TO SIGNAL (OPTION B - 208-PIN MQFP)

| PIN - SIGNAL |

|--------------|--------------|--------------|--------------|--------------|

| 1 - DGND     | 37 - CGND    | 73 - SD11    | 109 - RST    | 145 - GPY1   |

| 2 - BF5      | 38 - RDGATE  | 74 - SD10    | 110 - TST2B  | 146 - GPY0   |

| 3 - BF6      | 39 - WRTGATE | 75 - SD9     | 111 - CVDD   | 147 - GPX0   |

| 4 - DGND     | 40 - DATA0   | 76 - DGND    | 112 - CGND   | 148 - A10    |

| 5 - BF7      | 41 - DATA1   | 77 - SD8     | 113 - SCTL   | 149 - A9     |

| 6 - BFPL     | 42 - DATA 2  | 78 - DVDD    | 114 - WEB    | 150 - A8     |

| 7 - DGND     | 43 - DGND    | 79 - CVDD    | 115 - REB    | 151 - DGND   |

| 8 - BF8      | 44 - DATA3   | 80 - CGND    | 116 - CS0    | 152 - A7     |

| 9 - GPX3     | 45 - DATA4   | 81 - SDP1    | 117 - CS2    | 153 - A6     |

| 10 - BF9     | 46 - DVDD    | 82 - SDP     | 118 - ALE    | 154 - A5     |

| 11 - DGND    | 47 - DATA5   | 83 - DGND    | 119 - RESETB | 155 - A4     |

| 12 - BF10    | 48 - DATA6   | 84 - SD7     | 120 - GPX7   | 156 - BCLK   |

| 13 - BF11    | 49 - DGND    | 85 - SD6     | 121 - AD7    | 157 - DVDD   |

| 14 - CVDD    | 50 - DATA7   | 86 - SD5     | 122 - DGND   | 158 - CVDD   |

| 15 - CGND    | 51 - DATAP   | 87 - DGND    | 123 - AD6    | 159 - CGND   |

| 16 - DGND    | 52 - GPX4    | 88 - REQ     | 124 - AD5    | 160 - A3     |

| 17 - BF12    | 53 - AMDET   | 89 - SD4     | 125 - GPX6   | 161 - A2     |

| 18 - DVDD    | 54 - RRCLK   | 90 - SE      | 126 - AD4    | 162 - DGND   |

| 19 - BD13    | 55 - GPX5    | 91 - SD3     | 127 - DGND   | 163 - A1     |

| 20 - BF13    | 56 - WRAP    | 92 - DGND    | 128 - AD3    | 164 -A0      |

| 21 - DGND    | 57 - DRVFLT  | 93 - SD2     | 129 - AD2    | 165 - GPX1   |

| 22 - BD14    | 58 - CMPLT   | 94 - SD1     | 130 - DVDD   | 166 - BD0    |

| 23 - BF14    | 59 - SMDET   | 95 - CVDD    | 131 - AD1    | 167 - BF0    |

| 24 - BD15    | 60 - BDP4    | 96 - CGND    | 132 - BDP10  | 168 - DGND   |

| 25 -BF15     | 61 - CVDD    | 97 - SD0     | 133 - DGND   | 169 - BF1    |

| 26 - DGND    | 62 - CGND    | 98 - DGND    | 134 - AD0    | 170 - BF2    |

| 27 - BFPH    | 63 - IDXDET  | 99 - SEL     | 135 - RSTF   | 171 - DGND   |

| 28 - GPX2    | 64 - BDP3    | 100 - DVDD   | 136 - CVDD   | 172 - BF3    |

| 29 - MEMW    | 65 - TST1B   | 101 - IO     | 137 - CGND   | 173 - BF4    |

| 30 - CAS     | 66 - SCLK    | 102 - ATN    | 138 - INT2   | 174 - CVDD   |

| 31 - RAS     | 67 - SD15    | 103 - DGND   | 139 - INT1   | 175 - CGND   |

| 32 - DGND    | 68 - DGND    | 104 - BSY    | 140 - INTO   | 176 - DVDD   |

| 33 - WRTCLK  | 69 - SD14    | 105 - ACK    | 141 - RDY    |              |

| 34 - AMENA   | 70 - SD13    | 106 - CD     | 142 - DGND   |              |

| 35 - SQOUT   | 71 - SD12    | 107 - DGND   | 143 - GPY3   |              |

| 36 - CVDD    | 72 - DGND    | 108 - MSG    | 144 - GPY2   |              |

|              |              |              |              |              |

TABLE 3-4 PIN TO SIGNAL (OPTION C - 176-PIN SQFP)

| PIN - SIGNAL |

|--------------|--------------|--------------|--------------|--------------|--------------|

| 1 - DATA3    | 37 - DGND    | 73 - A2      | 109 - DGND   | 145 - SDOE1  | 181 - DGND   |

| 2 - DGND     | 38 - BF9     | 74 - DRQB    | 110 - AD4    | 146 - CGND   | 182 - SD12   |

| 3 - DATA2    | 39 - BD9     | 75 - A3      | 111 =- AD5   | 147 - CVDD   | 183 - SDOE12 |

| 4 - DATA1    | 40 - BF8     | 76 - DACKB   | 112 - AD6    | 148 - SD1    | 184 - SDOE13 |

| 5 - DATA0    | 41 - BD8     | 77 - CGND    | 113 - DGND   | 149 - SDOE2  | 185 - SD13   |

| 6 - WRTGATE  | 42 - DGND    | 78 - CVDD    | 114 - AD7    | 150 - SD2    | 186 - SDOE14 |

| 7 - RDGATE   | 43 - BFPL    | 79 - DVDD    | 115 - RESETB | 151 - DGND   | 187 - SD14   |

| 8 - CGND     | 44 - BDPL    | 80 - BCLK    | 116 - ALE    | 152 - SD3    | 188 - DGND   |

| 9 - CVDD     | 45 - BF7     | 81 - A4      | 117 - CS2    | 153 - SDOE3  | 189 - SD15   |

| 10 - SQOUT   | 46 - BD7     | 82 - A5      | 118 - CS0    | 154 - SE     | 190 - SDOE15 |

| 11 - AMENA   | 47 - DGND    | 83 - A6      | 119 - REB    | 155 - SDOE4  | 191 - SCLK   |

| 12 - WRTCLK  | 48 - BF6     | 84 - A7      | 120 - WEB    | 156 - SD4    | 192 - TST1B  |

| 13 - DGND    | 49 - BD6     | 85 - DGND    | 121 - SCTL   | 157 - REQ    | 193 - IDXDET |

| 14 - RAS     | 50 - BF5     | 86 - A8      | 122 - CGND   | 158 - DGND   | 194 - CGND   |

| 15 - CAS     | 51 - BD5     | 87 - A9      | 123 - CVDD   | 159 - SD5    | 195 - CVDD   |

| 16 - MEMW    | 52 - DGND    | 88 - A10     | 124 - TSTB   | 160 - SDOE5  | 196 - SMDET  |

| 17 - BFPH    | 53 - DVDD    | 89 - DWEB    | 125 - RSTIN  | 161 - SDOE6  | 197 - CMPLT  |

| 18 - BDPH    | 54 - CGND    | 90 - DREB    | 126 - RST    | 162 - SD6    | 198 - DRVFLT |

| 19 - DGND    | 55 - CVDD    | 91 - GPY0    | 127 - MSG    | 163 - SDOE7  | 199 - WRAP   |

| 20 - BF15    | 56 - BF4     | 92 - GPY1    | 128 - DGND   | 164 - SD7    | 200 - RRCLK  |

| 21 - BD15    | 57 - BD4     | 93 - GPY2    | 129 - CD     | 165 - DGND   | 201 - AMDET  |

| 22 - BF14    | 58 - BF3     | 94 - GPY3    | 130 - ACK    | 166 - SDP    | 202 - DATAP  |

| 23 - BD14    | 59 - BD3     | 95 - DGND    | 131 - DSENSE | 167 - SDPOE  | 203 - DATA7  |

| 24 - DGND    | 60 - DGND    | 96 - RDY     | 132 - TGS    | 168 - SDP1   | 204 - DGND   |

| 25 - BF13    | 61 - BF2     | 97 - INTO    | 133 - BSYIN  | 169 - SDOE8  | 205 - DATA6  |

| 26 - BD13    | 62 - BD2     | 98 - INT1    | 134 - BSY    | 170 - CGND   | 206 - DATA5  |

| 27 - DVDD    | 63 - BF1     | 99 - INT2    | 135 - DGND   | 171 - CVDD   | 207 - DVDD   |

| 28 - BF12    | 64 - BD1     | 100 - CGND   | 136 - ATN    | 172 - DVDD   | 208 - DATA4  |

| 29 - BD12    | 65 - DGND    | 101 - CVDD   | 137 - IO     | 173 - SD8    |              |

| 30 - DGND    | 66 - BF0     | 102 - RSTF   | 138 - IGS    | 174 - DGND   |              |

| 31 - CGND    | 67 - BD0     | 103 - AD0    | 139 - DVDD   | 175 - SD9    |              |

| 32 - CVDD    | 68 - DRQA    | 104 - DGND   | 140 - SELIN  | 176 - SDOE9  |              |

| 33 - BF11    | 69 - A0      | 105 - AD1    | 141 - SEL    | 177 - SDOE10 |              |

| 34 - BD11    | 70 - DACKA   | 106 - DVDD   | 142 - DGND   | 178 - SD10   |              |

| 35 - BF10    | 71 - A1      | 107 - AD2    | 143 - SD0    | 179 - SDOE11 |              |

| 36 - BD10    | 72 - DGND    | 108 - AD3    | 144 - SDOE0  | 180 - SD11   |              |

|              |              |              |              |              |              |

TABLE 3-5 PIN TO SIGNAL (OPTION D - 208-PIN MQFP)

The following table shows the four different pinout options available for the WD61C96A:

- Option A 176-pin, SQFP

- Option B 208-pin, MQFP

- Option C 176-pin SQFP

- Option D 208-pin, MQFP

| PINS<br>A                                     | PINS<br>B                                            | PINS<br>C                                     | PINS<br>D                                            | MNEMONIC                | vo  | DESCRIPTION                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|-------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                               | MICROPROCESSOR INTERFACE                             |                                               |                                                      |                         |     |                                                                                                                                                                                                                                                    |  |  |  |  |

| 118                                           | 116                                                  | 118                                           | 116                                                  | ALE                     | I   | ADDRESS LATCH ENABLE. This signal is used to load the address of desired register.                                                                                                                                                                 |  |  |  |  |

| 115                                           | 119                                                  | 115                                           | 119                                                  | REB                     | t   | READ ENABLE. This signal is active low and it is used with CS0 or CS2 signal to read the registers.(Active Low)                                                                                                                                    |  |  |  |  |

| 114                                           | 120                                                  | 114                                           | 120                                                  | WEB                     | I   | WRITE ENABLE. This signal is active low and it is used with the CS0 or CS2 signal to write into the registers. (Active Low)                                                                                                                        |  |  |  |  |

| 116                                           | 118                                                  | 116                                           | 118                                                  | CS0                     | I   | CHIP SELECT 0. This signal is active low and is used to qualify REB and WEB signals when the microprocessor is accessing a register. CS0 is used to select DISK Manager functions.                                                                 |  |  |  |  |

| 117                                           | 117                                                  | 117                                           | 117                                                  | CS2                     | 1   | CHIP SELECT 2. This signal is active low and is used to qualify REB and WEB signals when the microprocessor is accessing a register. CS2 is used to select SCSI Manager functions.                                                                 |  |  |  |  |

| 138<br>139<br>140                             | 99<br>98<br>97                                       | 138<br>139<br>140                             | 99<br>98<br>97                                       | INT 2<br>INT 1<br>INT 0 | 0   | INTERRUPT REQUESTS. These output signals are active high. They are asserted to alert the microprocessor indicating a completion or termination of a command. INTO and INT1 are used for Disk Manager interrupts. INT2 is used for SCSI interrupts. |  |  |  |  |

| 121<br>123<br>123<br>126<br>128<br>129<br>131 | 114<br>112<br>111<br>110<br>108<br>107<br>105<br>103 | 121<br>123<br>123<br>126<br>128<br>129<br>131 | 114<br>112<br>111<br>110<br>108<br>107<br>105<br>103 | AD[7:0]                 | 1/0 | MICROPROCESSOR DATA/ADDRESS<br>BUS                                                                                                                                                                                                                 |  |  |  |  |

**TABLE 3-6 SIGNAL DESCRIPTION**

| PINS<br>A | PINS<br>B | PINS<br>C | PINS<br>D | MNEMONIC     | VO     | DESCRIPTION                                                                                                                                                                                                                                                   |

|-----------|-----------|-----------|-----------|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |           | -         | MICRO     | PROCESSOR II | NTERFA | CE (Continued)                                                                                                                                                                                                                                                |

| 141       | 96        | 141       | 96        | RDY          | 0      | READY. This is an open drain output that controls the microprocessor's wait logic. (Active High)                                                                                                                                                              |

|           |           |           |           | HOST (DMA)   | INTERI | FACE                                                                                                                                                                                                                                                          |

| -         | 69        | -         | 68        | DRQA         | I/O    | DMA REQUEST A. The function of this pin is programmable and is defined by the control bits. In normal operation, this pin is tristated since this signal is dedicated to the internal DMA channel. This pin is only driven externally when in a test mode.    |

| -         | 70        | -         | 71        | DACKA        | 1/0    | DMA ACKNOWLEDGE A. The function of this pin is programmable and is defined by the control bits. In normal operation, this pin is tristated since this signal is dedicated to the internal DMA channel. This pin is only driven externally when in a test mode |

| -         | 75        | -         | 74        | DRQB         | 1/0    | DMA REQUEST B. The function of this pin is programmable and is defined by the control bits. This pin is normally driven by an external DMA slave.                                                                                                             |

| -         | 77        | -         | 76        | DACKB        | 1/0    | DMA ACKNOWLEDGE B. The function of this pin is programmable and is defined by the control bits. This pin is normally driven out to an external DMA device                                                                                                     |

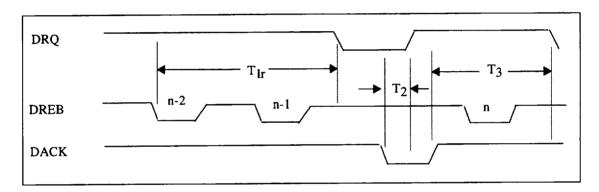

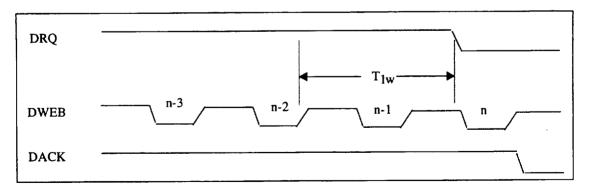

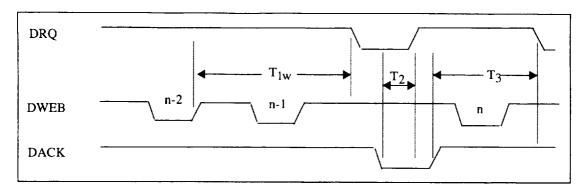

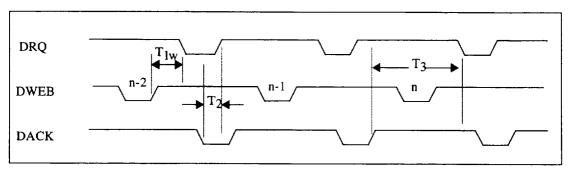

| -         | 88        | -         | 89        | DWEB         |        | DMA WRITE ENABLE, (Active low). This pin is only driven externally when in a test mode, or when an external DMA device is being serviced.                                                                                                                     |

| -         | 89        | -         | 90        | DREB         |        | DMA READ ENABLE, (Active low). This pin is only driven externally when in a test mode, or when an external DMA device is being serviced.                                                                                                                      |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS<br>A | PINS<br>B | PINS<br>C | PINS<br>D | MNEMONIC    | VO  | DESCRIPTION                                                                                                                                                                                     |

|-----------|-----------|-----------|-----------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |           |           | НО        | (Continued) |     |                                                                                                                                                                                                 |

| 26        | 20        | 24        | 21        | BD[15:0]    | 1/0 | HOST DMA BUS. These pins are only                                                                                                                                                               |

| 24        | 22        | 22        | 23        |             | •   | driven externally when in a test mode, or when an external DMA device is being                                                                                                                  |

| 21        | 25        | 19        | 26        |             |     | serviced.                                                                                                                                                                                       |

| 18        | 28        | -         | 29        |             |     |                                                                                                                                                                                                 |

| 13        | 33        | -         | 34        |             |     |                                                                                                                                                                                                 |

| -         | 35        | -         | 36        |             |     |                                                                                                                                                                                                 |

| -         | 38        | -         | 39        |             |     |                                                                                                                                                                                                 |

| •         | 41        | -         | 41        |             |     |                                                                                                                                                                                                 |

| -         | 46        | -         | 46        |             |     |                                                                                                                                                                                                 |

| -         | 49        | -         | 49        |             |     |                                                                                                                                                                                                 |

| -         | 51        | -         | 51        |             |     |                                                                                                                                                                                                 |

| -         | 57        | -         | 57        |             |     |                                                                                                                                                                                                 |

| -         | 59        | •         | 59        |             |     |                                                                                                                                                                                                 |

| 169       | 62        | -         | 62        |             |     |                                                                                                                                                                                                 |

| 167       | 64        | -         | 64        |             |     |                                                                                                                                                                                                 |

| 164       | 67        | 166       | 67        |             |     |                                                                                                                                                                                                 |

| •         | 44        | -         | 44        | BDPL        | 1/0 | PARITY OF THE LOWER DMA BUS. This pin carries the odd parity for the BD7 through BD0. This pin is only driven externally when in a test mode, or when an external DMA device is being serviced. |

| -         | 17        | -         | 18        | BDPH        | 1/0 | PARITY OF THE UPPER DMA BUS. This pin carries the odd parity for the BD15 through BD8. This pin is only driven externally when in a test mode, or when an external DMA device is being serviced |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS<br>A    | PINS<br>B      | PINS<br>C | PINS<br>D | MNEMONIC  | VO  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|--------------|----------------|-----------|-----------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|              | DISK INTERFACE |           |           |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 50           | 203            | 50        | 203       | DATA[7:0] | 1/0 | DISK DRIVE PARALELL DATA BUS                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 48           | 205            | 48        | 205       |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 47           | 206            | 47        | 206       |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 45           | 208            | 45        | 208       |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 44           | 1              | 44        | 1         |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 42           | 3              | 42        | 3         |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 41           | 4              | 41        | 4         |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 40           | 5              | 40        | 5         |           |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 51           | 202            | 51        | 202       | DATAP     | 1/0 | DISK PARALLEL DATA BUS PARITY. Odd or even parity is selectable. See section 4.3.5 on page 32.                                                                                                                                                                                                                                                                                |  |  |  |  |

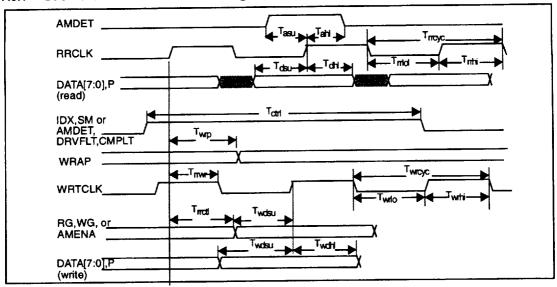

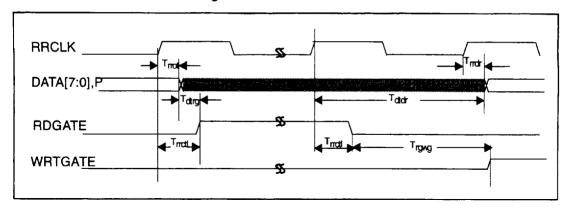

| 54           | 199            | 54        | 200       | RRCLK     | ı   | READ REFERENCE CLOCK. This clock is generated by the Disk Read Channel. All WD61C96A disk control and data pins are synchronized to this clock.                                                                                                                                                                                                                               |  |  |  |  |

| 35           | 10             | 33        | 12        | WRTCLK    | 0   | WRITE CLOCK. This pin is the inversion of the RRCLK.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 38           | 7              | 38        | 7         | RDGATE    | 0   | <b>READ GATE.</b> This signal is controlled by the Control Store.                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 39           | 6              | 39        | 6         | WRTGATE   | 0   | WRITE GATE. This signal is controlled by the Control Store.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 63           | 194            | 63        | 193       | IDXDET    | I   | INDEX DETECT. This signal is generated by the Read/Write logic when an index mark is detected.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 59           | 196            | 59        | 196       | SMDET     | 1   | SECTOR MARK DETECT. This generated by the Read/Write logic when a sector mark is found.                                                                                                                                                                                                                                                                                       |  |  |  |  |

| <del>-</del> | -              | 34        | 11        | AMENA     | 0   | ADDRESS MARK ENABLE. In write mode, this signal indicates to the write channel that an address mark byte is being send on the DATA[0:7] lines. In read mode, this signal flags the read channel on the type of sync bytes is to be detected. When RDGATE and WRTGATE are inactive, this signal indicates a search for an ID Address mark. (Not tristated on reset conditions) |  |  |  |  |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS<br>A    | PINS<br>B                  | PINS<br>C    | PINS<br>D | MNEMONIC | VO  | DESCRIPTION                                                                                                                                                                                                                                                                                           |  |  |  |

|--------------|----------------------------|--------------|-----------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|              | DISK INTERFACE (Continued) |              |           |          |     |                                                                                                                                                                                                                                                                                                       |  |  |  |

| 53           | 200                        | 53           | 201       | AMDET    | 1   | ADDRESS MARK DETECT. The Read Channel generates this signal when an ID address mark (or optional Sync Bytes) are detected.                                                                                                                                                                            |  |  |  |

| -            | -                          | 58           | 197       | CMPLT    | 1   | SEEK COMPLETE. This is a general purpose flag from the drive electronics. This signal is active only when the WCS is in operation. When this signal is active an interrupt can be generated by the WD61C96A.                                                                                          |  |  |  |

| •            | -                          | 35           | 10        | SEQOUT   | 0   | SEQUENCE OUT. This is a general purpose control line that is controlled directly from the Control Store.                                                                                                                                                                                              |  |  |  |

| 57           | 197                        | 57           | 198       | DRVFLT   |     | DRIVE FAULT. This is a general purpose flag from the drive electronics. This is typically an indication of a drive failure. When this signal, is active an interrupt is generated by the WD61C96A. As an option, the Control Store can respond to this error condition and jump to the error routine. |  |  |  |

| 120          | -                          | 120          | -         | GPX[7:0] | 1/0 | GENERAL PURPOSE PORT. These pins                                                                                                                                                                                                                                                                      |  |  |  |

| 125          | -                          | 125          | -         |          |     | can be configured as generic input or output pins.                                                                                                                                                                                                                                                    |  |  |  |

| 55           | -                          | 55           | -         |          |     | Output pins.                                                                                                                                                                                                                                                                                          |  |  |  |

| 52           | 201                        | 52           | -         |          |     |                                                                                                                                                                                                                                                                                                       |  |  |  |

| 9            | 39                         | 9            | -         |          |     |                                                                                                                                                                                                                                                                                                       |  |  |  |

| 30           | 15                         | 28           | -         |          |     |                                                                                                                                                                                                                                                                                                       |  |  |  |

| 163          | 68                         | 165          | _         |          |     |                                                                                                                                                                                                                                                                                                       |  |  |  |

| 147          | 90                         | 147          | -         |          |     |                                                                                                                                                                                                                                                                                                       |  |  |  |

| 143 -<br>146 | 94 - 91                    | 143 -<br>146 | 94 - 91   | GPY[3:0] | 1/0 | GENERAL PURPOSE PORT. These pins can be configured as generic input or output pins.                                                                                                                                                                                                                   |  |  |  |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS        | PINS            | PINS           | PINS     | MUEMONIO | <b>У</b> О | DESCRIPTION                                                              |

|-------------|-----------------|----------------|----------|----------|------------|--------------------------------------------------------------------------|

| <b>A</b> 56 | <b>B</b><br>198 | <b>C</b><br>56 | D<br>199 | WRAP     | I<br>I     | DESCRIPTION WRAP CHECK. In options C and D, this                         |

|             |                 |                |          |          |            | pin is used to verify that the RDGATE,<br>WRTGATE, and AMENA signals are |

|             |                 |                |          |          |            | properly connected to the drive                                          |

|             |                 |                |          |          |            | electronics. In options A and B, this pin is                             |

|             |                 |                |          |          |            | used to verify that RDGATE and WRTGATE are properly connected to the     |

|             |                 |                |          |          |            | drive electronics. An Interrupt is also                                  |

|             |                 |                |          |          |            | generated when an error is detected.                                     |

|             |                 |                |          | SCSI INT | ERFAC      |                                                                          |

| 105         | 130             | 105            | 130      | ACK      | 1/0        | SCSI ACKNOWLEDGE.                                                        |

| 102         | 136             | 102            | 136      | ATN      | 1/0        | SCSI ATTENTION.                                                          |

| 104         | 134             | 104            | 134      | BSY      | I/O        | SCSI BUSY (Single ended) or BUSY OUTPUT (Differential)                   |

| -           | 133             | -              | 133      | BSYIN    | ı          | SCSI BUSY INPUT (Differential mode                                       |

|             |                 |                |          |          |            | only, active low.)                                                       |

| 106         | 129             | 106            | 129      | C/D      | 1/0        | SCSI COMMAND/DATA.                                                       |

| 101         | 137             | 101            | 137      | 1/0      | 1/0        | SCSI INPUT/OUTPUT.                                                       |

| 108         | 127             | 108            | 127      | MSG      | 1/0        | SCSI MESSAGE.                                                            |

| 88          | 157             | 88             | 157      | REQ      | 1/0        | SCSI REQUEST.                                                            |

| 109         | 126             | 109            | 127      | RST      | 1/0        | SCSI RESET I/O (Single ended) or RESET OUTPUT (Differential).            |

| -           | 125             | _              | 125      | RSTIN    | l          | SCSI RESET IN (Differential mode only, active low)                       |

| 99          | 141             | 99             | 141      | SEL      | 1/0        | SCSI SELECT (Single ended) or SELECT OUTPUT (Differential).              |

| -           | 140             | -              | 140      | SELIN    | 1          | SCSI SELECT INPUT (Differential mode only, active low.)                  |

| 84          | 164             | 84             | 164      | SD[7:0]  | 1/0        | SCSI DATA BUS (lower byte).                                              |

| 85          | 162             | 85             | 162      |          |            |                                                                          |

| 86          | 159             | 86             | 159      |          |            |                                                                          |

| 89          | 156             | 89             | 156      |          |            |                                                                          |

| 91          | 152             | 91             | 152      |          |            |                                                                          |

| 93          | 150             | 93             | 150      |          |            |                                                                          |

| 94          | 148             | 94             | 148      |          |            |                                                                          |

| 97          | 143             | 97             | 143      |          |            |                                                                          |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS | PINS<br>B | PINS<br>C | PINS<br>D | MNEMONIC     | I/O | DESCRIPTION                         |

|------|-----------|-----------|-----------|--------------|-----|-------------------------------------|

| A    | В         |           |           | SCSI INTERFA |     |                                     |

| 82   | 166       | 82        | 166       | SDP          | 1/0 | SCSI DATA PARITY (for lower byte).  |

| 67   | 189       | 67        | 189       | SD[15:8]     | 1/0 | SCSI DATA BUS (higher byte).        |

| 69   | 187       | 69        | 187       | 05[:0:0]     |     | (,,                                 |

| 70   | 185       | 70        | 185       |              |     |                                     |

| 71   | 182       | 71        | 182       |              |     |                                     |

| 73   | 180       | 73        | 180       |              |     |                                     |

| 74   | 178       | 74        | 178       |              |     |                                     |

| 75   | 175       | 75        | 175       |              |     |                                     |

| 77   | 173       | 77        | 173       |              |     |                                     |

| 81   | 168       | 81        | 168       | SDP1         | 1/0 | SCSI DATA PARITY (for higher byte). |

|      | 131       | -         | 131       | DSENSE       | 1   | SCSI DIFFERENTIAL SENSE (10K        |

|      |           |           |           |              |     | pullup).                            |

| 90   | 154       | 90        | 154       | SE           | 1   | SINGLE ENDED (10K pullup)           |

| -    | 138       | -         | 138       | IGS          | 0   | INITIATOR GROUP SELECT.             |

| •    | 132       | -         | 132       | TGS          | 0   | TARGET GROUP SELECT.                |

| •    | 190       | -         | 190       | SDOE[15:0]   | 0   | SCSI DATA OUTPUT ENABLES.           |

|      | 186       |           | 186       |              |     |                                     |

|      | 184       | :         | 184       |              |     |                                     |

|      | 183       | ļ         | 183       |              |     |                                     |

|      | 179       |           | 179       |              |     |                                     |

|      | 177       |           | 177       |              |     |                                     |

|      | 176       |           | 176       |              |     |                                     |

|      | 169       |           | 169       |              |     |                                     |

|      | 163       |           | 163       |              |     |                                     |

|      | 161       |           | 161       |              |     |                                     |

|      | 160       |           | 160       |              |     |                                     |

|      | 155       |           | 155       |              |     |                                     |

|      | 153       |           | 153       |              |     |                                     |

|      | 149       |           | 149       |              |     |                                     |

|      | 145       |           | 145       |              |     |                                     |

|      | 144       |           | 144       |              |     |                                     |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS | PINS                       | PINS | PINS |            |          |                                         |  |  |  |  |

|------|----------------------------|------|------|------------|----------|-----------------------------------------|--|--|--|--|

| A    | В                          | С    | D    | MNEMONIC   | VO       | DESCRIPTION                             |  |  |  |  |

|      | SCSI INTERFACE (Continued) |      |      |            |          |                                         |  |  |  |  |

| •    | 167                        | -    | 167  | SDPOE      | 0        | SCSI DATA PARITY OUTPUT ENABLE.         |  |  |  |  |

|      |                            |      |      | BUFFER POF | RT INTER | RFACE                                   |  |  |  |  |

| 5    | 45                         | 5    | 45   | BF[7:0]    | 1/0      | BUFFER DATA BUS (LSB)                   |  |  |  |  |

| 3    | 48                         | 3    | 48   |            |          |                                         |  |  |  |  |

| 2    | 50                         | 2    | 50   |            |          |                                         |  |  |  |  |

| 173  | 56                         | 173  | 56   |            |          |                                         |  |  |  |  |

| 172  | 58                         | 172  | 58   |            |          |                                         |  |  |  |  |

| 170  | 61                         | 170  | 61   |            |          |                                         |  |  |  |  |

| 168  | 63                         | 169  | 63   |            |          |                                         |  |  |  |  |

| 165  | 66                         | 167  | 66   |            |          |                                         |  |  |  |  |

| 27   | 19                         | 25   | 20   | BF[15:8]   | 1/0      | BUFFER DATA BUS (MSB)                   |  |  |  |  |

| 25   | 21                         | 23   | 22   |            |          | , ,                                     |  |  |  |  |

| 22   | 24                         | 20   | 25   |            |          |                                         |  |  |  |  |

| 19   | 27                         | 17   | 28   |            |          |                                         |  |  |  |  |

| 14   | 32                         | 13   | 33   |            |          |                                         |  |  |  |  |

| 12   | 34                         | 12   | 35   |            |          |                                         |  |  |  |  |

| 10   | 37                         | 10   | 38   |            |          |                                         |  |  |  |  |

| 8    | 40                         | 8    | 40   |            |          |                                         |  |  |  |  |

| 6    | 43                         | 6    | 43   | BFPL       | I/O      | BUFFER DATA PARITY BIT LSB. Odd         |  |  |  |  |

| _    |                            | ū    |      |            | "        | parity.                                 |  |  |  |  |

| 29   | 16                         | 27   | 17   | BFPH       | 1/0      | BUFFER DATA PARITY BIT MSB. Odd parity. |  |  |  |  |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS<br>A | PINS<br>B | PINS<br>C | PINS<br>D   | MNEMONIC    | VO    | DESCRIPTION                                                                                                                                            |

|-----------|-----------|-----------|-------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |           |           | BUF         | (Continued) |       |                                                                                                                                                        |

| •         | -         | 148       | 88          | A[10:0]     | 0     | BUFFER ADDRESS.                                                                                                                                        |

| -         | -         | 149       | 87          |             |       |                                                                                                                                                        |

| 148       | 87        | 150       | 86          |             |       |                                                                                                                                                        |

| 150       | 85        | 152       | 84          | <br>        |       |                                                                                                                                                        |

| 151       | 84        | 153       | 83          | ;           |       |                                                                                                                                                        |

| 152       | 83        | 154       | 82          |             |       |                                                                                                                                                        |

| 153       | 82        | 155       | 81          |             |       |                                                                                                                                                        |

| 158       | 76        | 160       | 75          |             |       |                                                                                                                                                        |

| 159       | 74        | 161       | 73          |             |       |                                                                                                                                                        |

| 161       | 72        | 163       | 71          |             |       |                                                                                                                                                        |

| 162       | 70        | 164       | 69          | :           |       |                                                                                                                                                        |

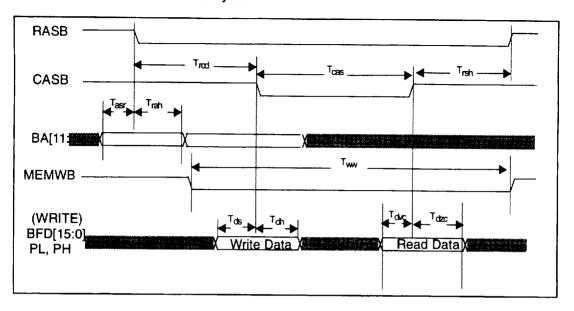

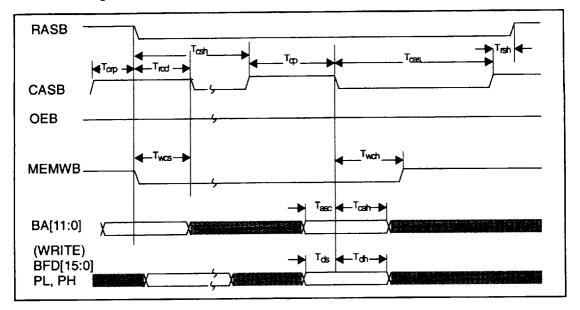

| 31        | 14        | 29        | 16          | MEMW        | 0     | MEMORY WRITE (Active low).                                                                                                                             |

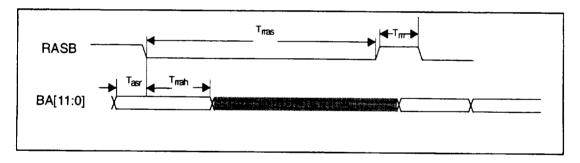

| 32        | 13        | 30        | 15          | RAS         | 0     | ROW ADDRESS STROBE (Active low).                                                                                                                       |

| 33        | 12        | 31        | 14          | CAS         | 0     | PRIMARY COLUMN ADDRESS STROBE (Active low).                                                                                                            |

|           | L.,       |           | <del></del> | MISCELL     | ANEOU | S                                                                                                                                                      |

| 119       | 115       | 119       | 115         | RESETB      | 1     | HARD RESET. This input sets the WD61C96A in power on reset condition. All the drivers are set into inactive state. (Active Low)                        |

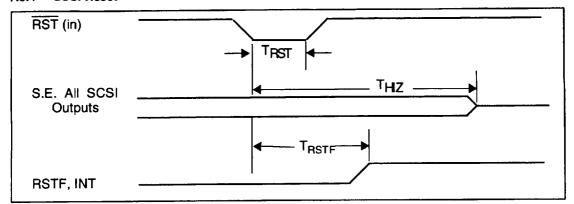

| 135       | 102       | 135       | 102         | RSTF        | 0     | SCSI RESET FOLLOWER. RSTF is a debounced version of the SCSI RST/RSTIN input, and is asserted as long as a valid SCSI reset is detected (active high). |

| 154       | 81        | 156       | 80          | BCLK        | I     | BUFFER CLOCK. Maximum 50 MHz.                                                                                                                          |

| 66        | 191       | 66        | 191         | SCLK        | I     | SCSI CLOCK. Minimum 20 MHz, maximum 40 MHz.                                                                                                            |

| 110       | 124       | 110       | 124         | TST2B       | 1     | VO TEST ENABLES 1 AND 2. When                                                                                                                          |

| 65        | 192       | 65        | 192         | TST1B       |       | active (low) the WD61C96A is placed into special test modes. See Section 5.12.                                                                         |

| 113       | 121       | 113       | 121         | SCTL        | ı     | SCAN SHIFT/LOAD CONTROL                                                                                                                                |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS<br>A | PINS<br>B | PINS<br>C | PINS<br>D | MNEMONIC | VO | DESCRIPTION                                                           |

|-----------|-----------|-----------|-----------|----------|----|-----------------------------------------------------------------------|

| 64        | 193       | 64        | •         | BDP3     | Ī  | POWER ON LATCH INPUTS. The data                                       |

| 60        | -         | 60        | -         | BDP4     |    | on these pins are latched into the WD61C40A power on latch registers. |

| 58        | -         | -         | -         | BDP9     |    | Refer to Table 3-1, OPTIONAL                                          |

| 132       | -         | 132       | -         | BDP10    |    | PACKAGE FEATURES, on page 5.                                          |

| 15        | 31        | 14        | 32        | CVDD     |    | +5 VOLTS                                                              |

| 36        | 9         | 36        | 9         |          |    |                                                                       |

| 61        | 195       | 61        | 195       |          |    |                                                                       |

| 79        | 171       | 79        | 171       |          |    |                                                                       |

| 95        | 147       | 95        | 147       |          |    |                                                                       |

| 111       | 123       | 111       | 123       |          |    |                                                                       |

| 136       | 101       | 136       | 101       |          |    |                                                                       |

| 156       | 79        | 158       | 78        |          |    |                                                                       |

| 174       | 55        | 174       | 55        | ,        |    |                                                                       |

| 16        | 30        | 15        | 31        | CGND     |    | GROUND                                                                |

| 37        | 8         | 37        | 8         |          |    |                                                                       |

| 62        |           | 62        | 194       |          |    |                                                                       |

| 80        | 170       | 80        | 170       |          |    |                                                                       |

| 96        | 146       | 96        | 146       |          |    |                                                                       |

| 112       | 122       | 112       | 122       |          |    |                                                                       |

| 137       | 100       | 137       | 100       |          |    |                                                                       |

| 157       | 78        | 159       | 77        |          |    |                                                                       |

| 175       | 54        | 175       | 54        |          |    |                                                                       |

| 20        | 26        | 18        | 27        | DVDD     |    | +5 VOLTS                                                              |

| 46        | 207       | 46        | 207       |          |    |                                                                       |

| 78        | 172       | 78        | 172       |          |    |                                                                       |

| 100       | 139       | 100       | 139       |          |    |                                                                       |

| 130       | 106       | 130       | 106       |          |    |                                                                       |

| 155       | 80        | 157       | 79        |          |    |                                                                       |

| 176       | 53        | 176       | 53        |          |    |                                                                       |

TABLE 3-6 SIGNAL DESCRIPTION (Continued)

| PINS<br>A | PINS<br>B | PINS<br>C | PINS<br>D | MNEMONIC | VO | DESCRIPTION |

|-----------|-----------|-----------|-----------|----------|----|-------------|

| 1,4,7,    | 52, 47,   | 1,4,7,    | 52, 47,   | DGND     | ·  | GROUND      |

| 11,17,    | 42, 36,   | 11,16,    | 42, 37,   |          |    |             |

| 23, 28,   | 29, 23,   | 21, 26,   | 30, 24,   |          |    |             |

| 34, 43,   | 18, 11,   | 32, 43,   | 19, 13,   |          |    |             |

| 49, 68,   | 2, 204,   | 49, 68,   | 2, 204,   |          |    |             |

| 72, 76,   | 188,      | 72, 76,   | 188,      |          |    |             |

| 83, 87,   | 181       | 83, 87,   | 181       |          |    |             |

| 92, 98,   | 174       | 92, 98,   | 174       |          |    |             |

| 103,      | 165       | 103,      | 165       |          |    |             |

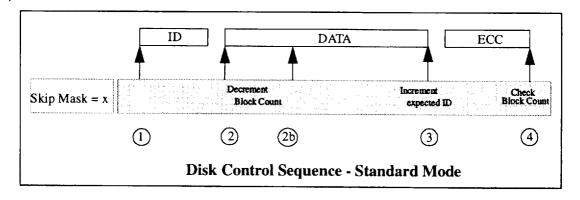

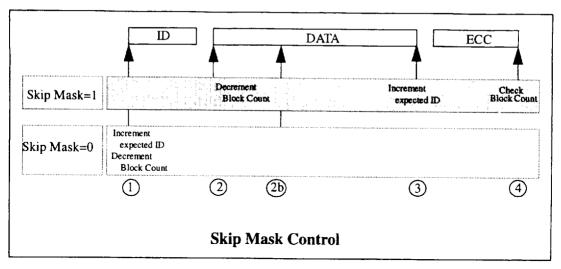

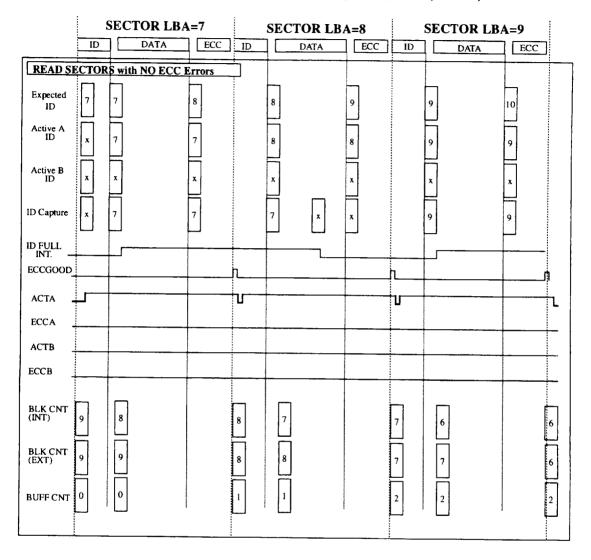

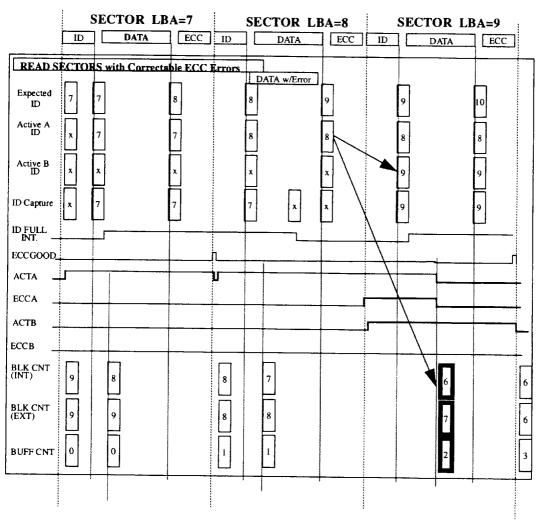

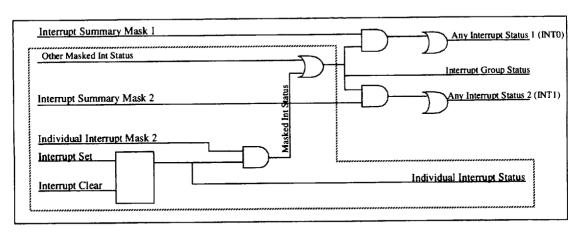

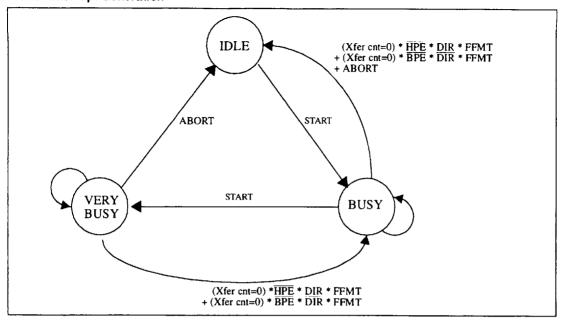

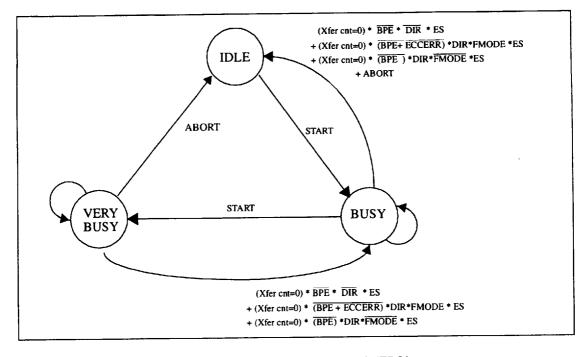

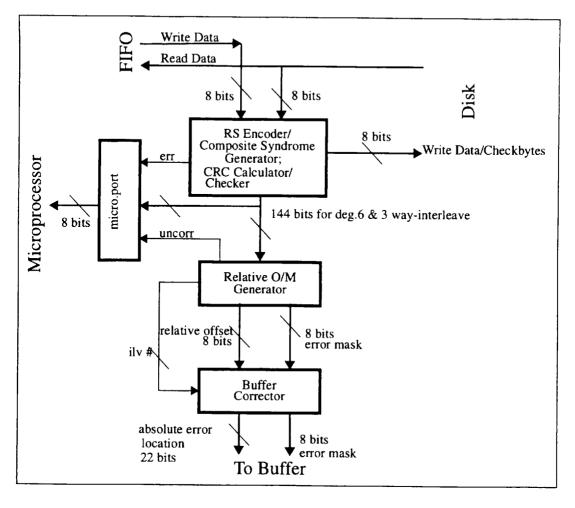

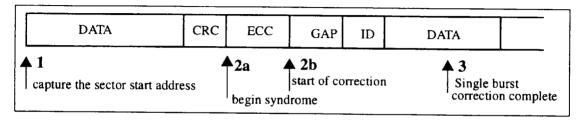

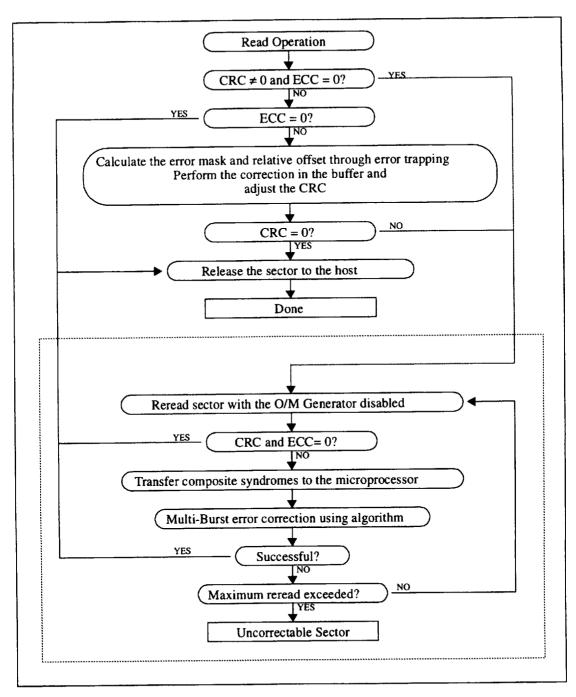

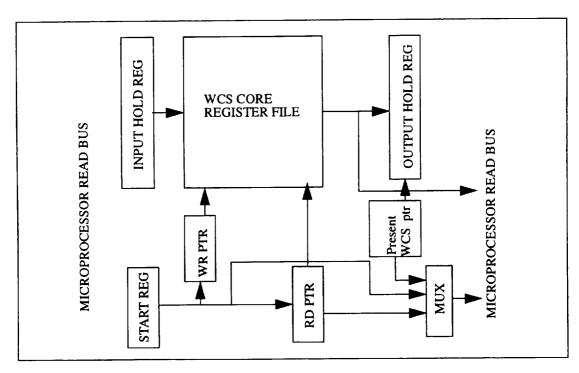

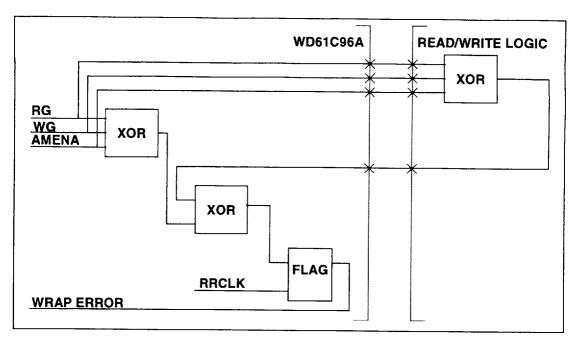

| 107       | 158       | 107       | 158       |          |    |             |