WD10C27

Data

Separator

www.DataSheet4U.com

www.DataSheet4U.com

13

## **TABLE OF CONTENTS**

T-52-38

| Section | Title        |                                                            | Page           |  |  |  |

|---------|--------------|------------------------------------------------------------|----------------|--|--|--|

| 1.0     | INTF         | RODUCTION                                                  | 13-1           |  |  |  |

|         | 1.1          | GENERAL DESCRIPTION                                        | 13-1           |  |  |  |

|         | 1.2          | FEATURES                                                   | 13-1           |  |  |  |

|         |              |                                                            |                |  |  |  |

| 2.0     | MICI         | ROPROCESSOR INTERFACE                                      | 13-8           |  |  |  |

|         | 2.1          | REGISTER DESCRIPTION                                       | 13-8           |  |  |  |

|         |              | 2.1.1 Configuration Registers                              | 13-9           |  |  |  |

|         |              | 2.1.2 Frequency Synthesizer Registers                      | 13-12          |  |  |  |

|         |              | 2.1.3 Window Synthesizer Registers                         | 13-12          |  |  |  |

|         |              | 2.1.4 Skew-Symmetric Precomp.Registers                     | 13-12          |  |  |  |

|         |              | 2.1.5 Channel Control Registers                            | 13-13          |  |  |  |

|         |              | 2.1.6 Registers                                            | 13-13          |  |  |  |

| 3.0     |              | OLIENOV CVAITUEOIZED                                       | ÷              |  |  |  |

| 3.0     | 3.1          | QUENCY SYNTHESIZERPROGRAMMABLE FS CRYSTAL REFERENCE (XTLI) | 13-17          |  |  |  |

|         | 3.2          | ES DIVIDED OBERATION                                       | 13-17          |  |  |  |

|         | 3.3          | FS DIVIDER OPERATION                                       | 13-17          |  |  |  |

|         | 0.0          | PROGRAMMING THE FS DIVIDERS                                | 13-18          |  |  |  |

| 4.0     | READ CHANNEL |                                                            |                |  |  |  |

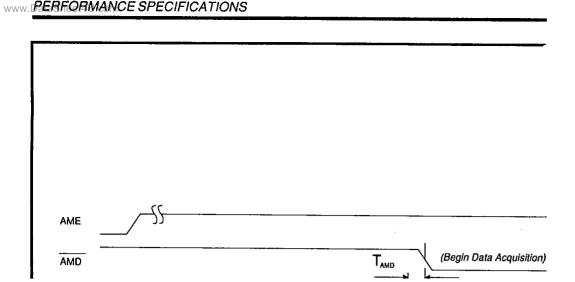

|         | 4.1          | ADDRESS MARK DETECTOR                                      | 13-20          |  |  |  |

|         |              | 4.1.1 Address Mark Detection Rules                         | 13-20          |  |  |  |

|         |              | 4.1.2 Formatting to Reduce False AM Detection              | 13-22          |  |  |  |

|         | 4.2          | ACQUISITION SEQUENCER                                      | 13-22          |  |  |  |

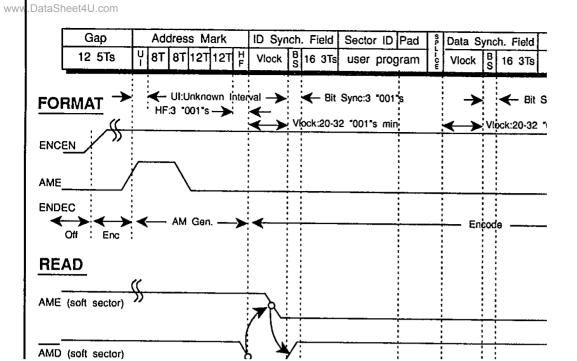

|         |              | 4.2.1 Soft Sector Sequencing                               | 13-22          |  |  |  |

|         |              | 4.2.2 Data Acquisition and Tracking                        | 13-23          |  |  |  |

|         |              | 4.2.3 RCLK Source                                          | 13-24          |  |  |  |

|         | 4.3          | DATA SYNCHRONIZER                                          | 13-26          |  |  |  |

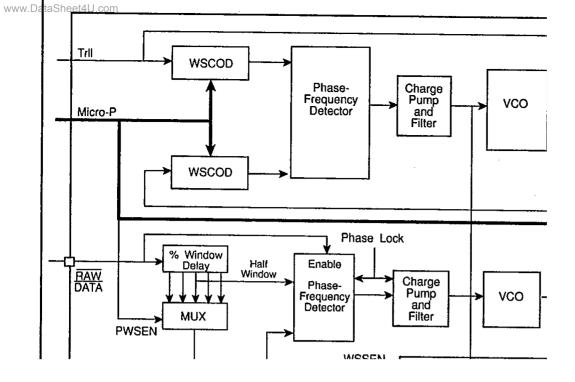

|         |              | 4.3.1 Phase-Locked Loop                                    | 13-26          |  |  |  |

|         |              | 4.3.2 Window Generation                                    | 13-27          |  |  |  |

|         |              | 4.3.3 Window Monitoring                                    | 19-27          |  |  |  |

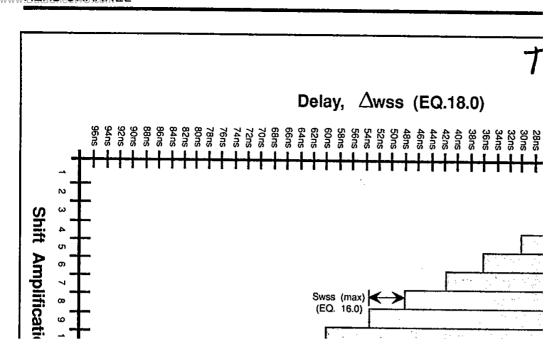

|         |              | 4.3.4 Window Shifting                                      | 19-27          |  |  |  |

|         | 4.4          | DECODER                                                    | 12-21          |  |  |  |

|         | 4.5          | CHANNEL CONTROL DACs                                       | 12-22          |  |  |  |

|         |              | 4.5.1 Frequency Control (FCDAC)                            | 12_2A          |  |  |  |

|         |              | 4.5.2 Boost Control (BCDAC)                                | 40-01<br>40-01 |  |  |  |

|         |              | 4.5.3 Hysteresis Control (FCDAC)                           | 12_0 <i>A</i>  |  |  |  |

|         |              | ·                                                          | 10-04          |  |  |  |

## T-52-38

## **TABLE OF CONTENTS (Continued)**

| <b>Section</b> 5.0                                                     | Title  WRITE CHANNEL  5.1 ENCODER  5.1.1 Framing in Hard Sector Formats  5.1.2 Framing in Soft Sector Formats  5.2 PATTERN DEPENDENT PRECOMPENSATION  POWER ON RESET                                                                                                                                                                                                                                                                                                                                                       | . 13-35<br>. 13-35<br>. 13-36<br>. 13-36                                                                          |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 7.0                                                                    | PERFORMANCE SPECIFICATIONS 7.1 MAXIMUM RATINGS 7.2 DC ELECTRICAL CHARACTERISTICS 7.3 AC ELECTRICAL AND TIMING CHARACTERISTICS  APPENDICES                                                                                                                                                                                                                                                                                                                                                                                  | 13-40<br>13-40                                                                                                    |

| A.0                                                                    | APPLICATION NOTES  A-1 FREQUENCY SYNTHESIZER  A-2 WINDOW SHIFT SYNTHESIZER  LIST OF ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                          | 13-47                                                                                                             |

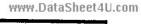

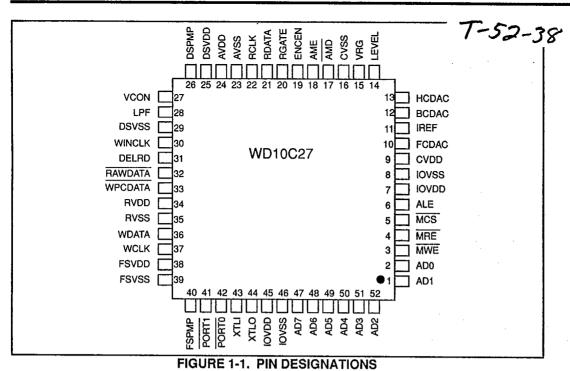

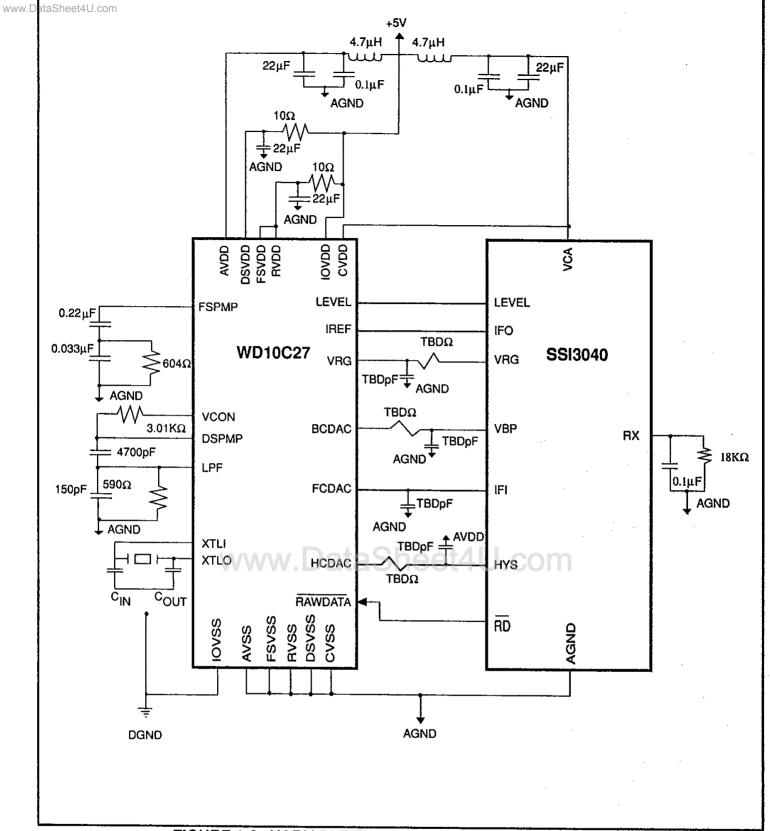

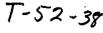

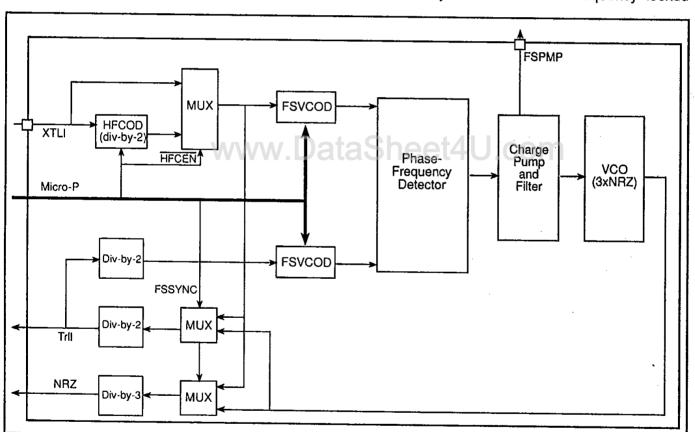

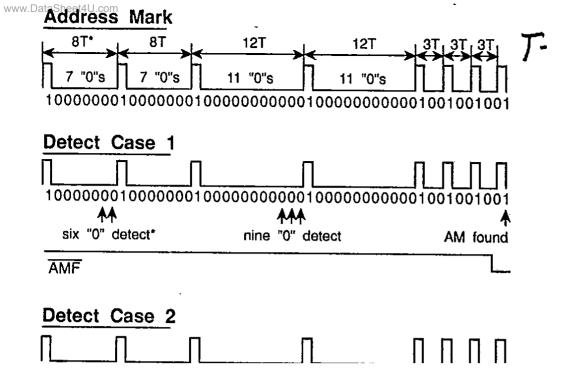

| Figure 1-1 1-2 1-3 3-1 4-1 4-2 4-3 4-4 4-5 7-1 7-2 7-3 7-4 7-5 7-6 7-7 | Title Pin Designations Variable Frequency Channel Schematic WD10C27 Block Diagram Frequency Synthesizer Block Diagram Soft Sector Timing The Acquisition Sequence Data Synchronizer Block Diagram Window Shift Synthesis Code Word to Data Word Relationship Crystal Input Timing Diagram Encoder Timing Diagram Address Mark Generation Timing Diagram Write Precompensation Timing Diagram Read Timing Diagram Microprocessor Read Timing Diagram Microprocessor Read Timing Diagram Microprocessor Write Timing Diagram | .13-6<br>.13-7<br>13-17<br>13-23<br>13-25<br>13-26<br>13-29<br>13-32<br>13-46<br>13-47<br>13-48<br>13-49<br>13-51 |

## LIST OF TABLES

# T-52-38

| lable            | ritte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1-1              | Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13-3             |

| 2-1              | Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13-8             |

| 4-1              | Address Mark Detect Sequences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13-21            |

| 4-2              | Velocity Lock Time Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13-24            |

| 4-3              | Frequency Band Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13-27            |

| 4-4              | PWS Direction and Magnitude Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13-31            |

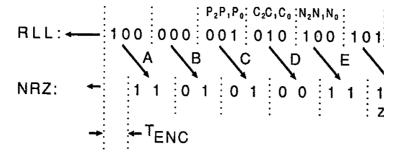

| 4-5              | Expanded 1,7 RLL to NRZ Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13-33            |

| 5-1              | Expanded NRZ to 1,7 RLL Encode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12-25            |

| 5-2              | Skew Symmetric Matrix Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13-36            |

| 5-3              | Precompensation Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19-00            |

| 7-1              | Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12-40            |

| 7-2              | Crystal Oscillator DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12-40            |

| 7-3              | Output Driver DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19.41            |

| 7-4              | Input Receivers DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19-41            |

| 7-5              | Data Synchronizer Internal Filter DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10-42            |

| 7-6              | Data Synchronizer Internal VCO DC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-42            |

| 7-7              | Hysteresis Control DAC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 10-40<br>10 44 |

| 7-8              | Frequency Control DAC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10-44            |

| 7-9              | Boost Control DAC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10-40            |

| 7-10             | Power Supply Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-40            |

| 7-11             | Crystal Oscillator Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10-40            |

| 7-12             | Encoder Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10-40            |

| 7-13             | Address Mark Generation Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10-47            |

| 7-14             | Write Precompensation Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-48            |

| <sup>7</sup> -15 | Phase and Data Detection Window Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13-49            |

| <sup>7</sup> -16 | Read Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13-50            |

| <sup>7</sup> -17 | Window Shift Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13-50            |

| <b>7</b> -18     | Data Synchronizer PLL AC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13-50            |

| <b>7</b> -19     | Frequency Synchronizer PLL AC Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13-52            |

| <b>'-20</b>      | Microprocessor Interface Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13-53            |

|                  | The second of th | 13-54            |

www.DataSheet4U.com

#### 1.0 INTRODUCTION

#### 1.1 GENERAL DESCRIPTION

The WD10C27 Read/Write Channel is a fully integrated LSI device intended for variable frequency applications in conjunction with the WD61C22 Hard Disk Controller/Buffer Manager.

In a typical application, the WD10C27 performs all of the handling of the sensitive read/write signals between a disk controller and data drivers and receivers. Raw read data corresponds to previous write data, with added phase, frequency, and write splice noise. The fundamental purpose of the WD10C27 is to remove these noise components and present a clean digital recovered data and reference clock to the controller.

#### 1.2 Features

- General

- Specifically designed for the WD61C22 Hard Disk Controller/Buffer Manager

- Supports Zone Bit Recording from 7.5-27MBps with no component changes

- 1.25 micron +5 volt only CMOS technology

- Available in 52-pin EIAJ package

- Frequency Synthesizer

- Programmable input reference frequency to 40 MHz

- Multiple dividers for extremely high resolution

- Micro-Processor Interface

- Eight bit Intel compatible multiplexed address/data port

- Programmable test and low power modes

T-52-38

- Write Data Conditioner

- Crystal controlled processing of the write data to eliminate pulse pairing

- Programmable pattern dependent Skew Symmetric Precompensation matrix for precomp. of up to ±25% with 2<sup>-6</sup> resolution

- Encoder/Decoder

- IBM Compatible 1,7 RLL

- Hard/soft sector support and Address Mark Detection

- Data Synchronizer

- Precision internal self adjusting VCO compensates for component, temperature, voltage, and aging variations

- Internal gain/bandwidth modulation linearizes loop gain and increases phase margin across zones

- Dual gain charge pump for faster acquisition and better jitter rejection while tracking

- Dual mode phase/phase-frequency detector eliminating quadrature and harmonic lock

- mP controlled Window Shift Synthesis for window shifting up to ±50% of the window

- Window monitoring capability

- Channel Control

- 5-bit DACs specifically designed for use with the SSI8011 and SSI3040 read channel devices

- Bandwidth, Boost and Hysteresis Control for ZBR

- Two Programmable Micro Processor Ports

www.DataS

www.DataSheet4U.com

13-2

ADVANCE INFORMATION 5/15/91

1/2

ww.INTRODUCTION

| PIN                |           | <del> </del>            | <del>  •                                     </del> | T-52-38                                                                                                                                                          |

|--------------------|-----------|-------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER<br>(IO MAP) | MNEUMONIC | SIGNAL                  | 1/0                                                 |                                                                                                                                                                  |

| 47-52,             | AD7-0     | NAME                    | A/S                                                 | FUNCTIONAL DESCRIPTION                                                                                                                                           |

| 1-2                |           | Address/Data<br>Bus     | 1/0                                                 | ADDRESS inputs used in conjunction with ALE to select the internal register to be transmitted or received on the DATA input/outputs.                             |

| 3                  | MWE       | Write Enable            | 1                                                   | When asserted will transmit data from the AD bus into internal registers.                                                                                        |

| 4                  | MRE       | Read Enable             | 1                                                   | When asserted will transmit data from internal registers onto the AD bus.                                                                                        |