# WESTERN DIGITAL

# WD10C20-05 Self-Adjusting Data Separator

#### **FEATURES**

- PROCESSES ALL SENSITIVE READ/WRITE DATA SIGNALS

- CMOS TECHNOLOGY

- DESIGNED FOR ST506/ST412 AND WD1010/ WD2010 INTERFACE

- HIGHLY STABLE LC TYPE VOLTAGE CONTROLLED OSCILLATOR

- SELF ADJUSTING VCO COMPENSATES FOR COMPONENT, TEMPERATURE, VOLTAGE, AND AGING VARIATIONS

- FREQUENCY DETECTION ON CRYSTAL REFERENCE AND DATA SYNCHRONIZATION FIELD, ELIMINATES 180 DEGREE LOCK DUE TO DRIVE ASYMMETRY, AND ELIMINATES HARMONIC LOCK FROM WP.ITE SPLICES

- ZERO PHASE STARTUP PROVIDES FASTER, MORE PREDICATABLE LOCK ACQUISITION

- LOCKS TO CRYSTAL REFERENCE WHILE IDLE

- DUAL GAIN: HIGH FOR FASTER ACQUISITION LOW FOR MORE JITTER REJECTION WHILE TRACKING

- EXTERNAL PUMP CURRENT CONTROL

- AVAILABLE IN 28-PIN DIP OR QSM PACKAGE

- INTEGRATED CRYSTAL OSCILLATOR

- ACCOMMODATES OTHER DATA RATES THROUGH SELECTION OF EXTERNAL COMPONENTS

#### DESCRIPTION

The WD10C20-05 is an LSI device implemented in 3 micron high-speed CMOS, designed to be compatible with the WD1010 and WD2010 Winchester Disk Controllers and ST506/ST412 disk drives. In a typical application, it handles all sensitive read/write signals between a WD1010/WD2010 and the data drivers/receivers. Read data corresponds to previous write data, with added phase, frequency, and write splice noise. The WD10C20-05 removes these sources of noise and presents a clean, digital read signal to the WD1010/WD2010.

While reading, the WD10C20-05 performs phaselocked loop data synchronization on data read from the drive. An on-board Sync Field detector automatically switches the PLL from the stable crystal reference to the read data. Zero-phase startup results when the VCO is halted and restarted in phase with the data to eliminate initial acquisition in the wrong frequency direction. Frequency-phase detection is used at the beginning of the Sync Field to quickly and reliably acquire lock to the data. Use of this technique eliminates susceptibility to harmonics and asymmetry. The WD10C20-05 then switches to phase-only detection to complete the phase acquisition before the end of the Synch Field and to enable tracking of random MFM read data. When switching to phase detection, the WD10C20-05 reduces the error amplifier gain for better rejection of drive jitter. A precisely aligned detector samples the data at twice the underlying data rate to remove the phase jitter. The regenerated signal, along with a fixed-phase synchronous clock, are output to the WD1010/WD2010 digital circuits.

While writing, the WD10C20-05 conditions the write data to the drive. MFM data from the WD1010WD2010 is precisely clocked, with a signal at twice the data frequency, to minimize digital phase noise. If precompensation is enabled, early, nominal, and late taps on an external delay line are multiplexed through matched delay paths to produce synchronized, precompensated write data, which is sent directly to the drive's write circuits.

The WD10C20-05 is designed to work at the 5 Mbit/sec data rate of the ST506/ST412 interface. Other data rates may be accommodated through the proper selection of external components.

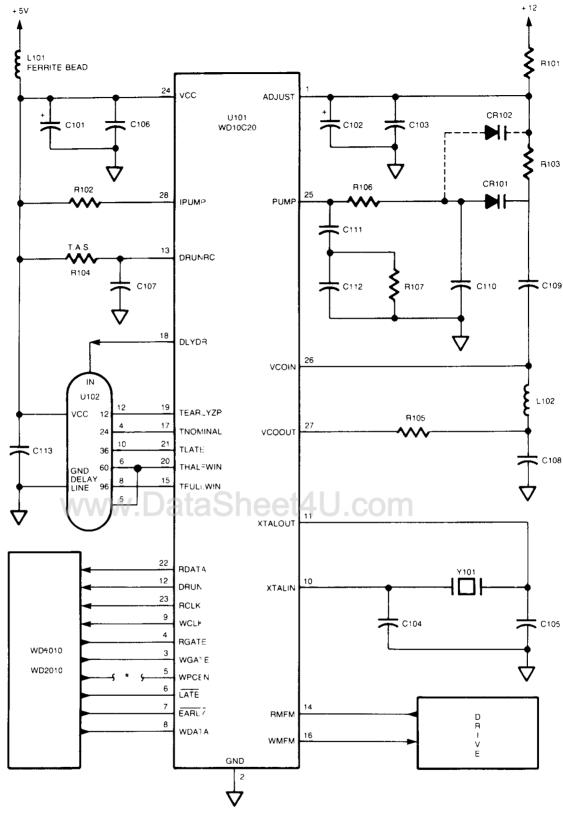

NOTE: To assure reliable operation of the WD10C20-05, it is recommended that the WD10C20-05 KIT, number 77-000014 be used. If the user elects to not use the kit, the external components as shown in Figure 1, must be selected from the parts listed in the WD10C20-05 Application Note. The placement of these components must conform to the layout illustrated in the Application Note. (The Application Note is available through your Western Digital field representative.)

eet4U.com

Winchester Disk Support Devices

\*RWC CONNNECTS TO WPCEN IF REDUCED WRITE CURRENT IS TO START AT THE SAME TIME AS WRITE PRECOMP. THE WD1002S-WX2 USES LS/DIR/WPC.

FIGURE 1. EXTERNAL COMPONENTS

Winchester Disk Support Devices

4–3

FIGURE 2. WD10C20 BLOCK DIAGRAM

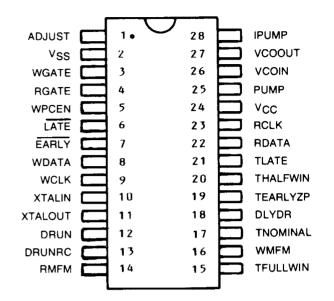

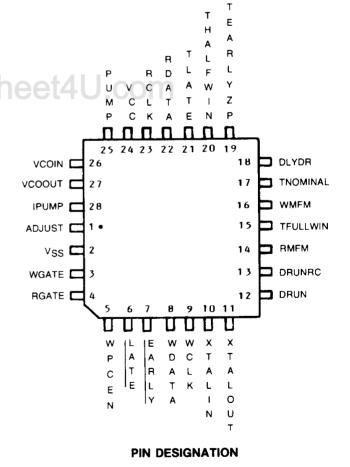

# PIN DESCRIPTION

| PIN<br>NUMBER | MNEMONIC | SIGNAL NAME                | I/O | FUNCTION                                                                                                                                                                                                                                                                                                        |

|---------------|----------|----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | ADJUST   | ADJUST                     | 0   | Provides self calibration of the PLL.                                                                                                                                                                                                                                                                           |

| 2             | vss      | GROUND                     |     |                                                                                                                                                                                                                                                                                                                 |

| 3             | WGATE    | WRITE GATE                 | ı   | WGATE is asserted when the controller writes on the disk.                                                                                                                                                                                                                                                       |

| 4             | RGATE    | READ GATE                  | 1   | RGATE is asserted when the controller intends to read from the disk. RGATE causes the WD10C20-05 to remain locked onto the incoming data stream.                                                                                                                                                                |

| 5             | WPCEN    | WRITE<br>PRECOMP<br>ENABLE | 1   | WPCEN is asserted to enable the EARLY and LATE signals from the controller. WPCEN may be connected to the Reduce Write Current (RWC) available from the WD1010/WD2010 if Write Precomp is to occur at the same time as the Reduced Write Current, or to an independent source if they start at different times. |

| 6             | LATE     | LATE                       | ı   | Asserted by the Controller to delay the writing of a bit to the disk.                                                                                                                                                                                                                                           |

| 7             | EARLY    | EARLY                      | 1   | Asserted by the Controller to advance the writing of a bit to the disk.                                                                                                                                                                                                                                         |

| 8             | WDATA    | WRITE DATA                 | 1   | Non-Synchronized and Non-Precompensated MFM data from the controller to be written on the disk via WMFM.                                                                                                                                                                                                        |

| 9             | WCLK     | WRITE CLOCK                | 0   | WCLK is equal to XTALIN ÷ 2 and is used by the controller to generate the data to be written.                                                                                                                                                                                                                   |

| 10            | XTALIN   | xtalin<br>ww.Data          | Sh  | XTALIN is a crystal controlled oscillator input used by a number of internal control functions. Divided by 2 it develops WCLK. XTALIN may also be driven by an external driver in which case XTALOUT is left open. The input level of this pin is not TTL and must be guaranteed by the clock source.           |

| 11            | XTALOUT  | XTALOUT                    | 0   | XTALOUT is the crystal controlled oscillator output. When an external frequency source is used, this pin is left open.                                                                                                                                                                                          |

| 12            | DRUN     | DATA RUN                   | 0   | DRUN is a signal that discriminates between frequencies on RMFM. It goes low for low frequencies and high for high frequencies. Its nominal threshold is set to 1-3/8 bit times using DRUNRC. DRUN remains asserted for a continuous stream of one's or zero's. ie: Sync Field.                                 |

| 13            | DRUNRC   | DRUNRC                     | 1   | Connected to an external RC circuit for the generation of DRUN.                                                                                                                                                                                                                                                 |

| 14            | RMFM     | READ MFM<br>DATA           | 1   | MFM Data received from the drive. A nominal 4K ohm internal pullup resistor allows tri-state multiplexing of the driver's data receivers.                                                                                                                                                                       |

| 15            | TFULLWIN | TFULLWINDOW                |     | Delay line tap for generating full window RMFM pulses.                                                                                                                                                                                                                                                          |

| 16            | WMFM     | WRITE MFM<br>DATA          | 0   | Preconditioned WDATA ready to be written on the disk. WMFM is held low when WGATE is low.                                                                                                                                                                                                                       |

| 17            | TNOMINAL | TNOMINAL                   | l   | Delay line tap for uncompensated write data.                                                                                                                                                                                                                                                                    |

#### **PIN DESCRIPTION (Continued)**

| PIN    |          |                                            |          |                                                                                                                           |

|--------|----------|--------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------|

| NUMBER | MNEMONIC | SIGNAL NAME                                | 1/0      | FUNCTION                                                                                                                  |

| 18     | DYLDR    | DELAY LINE<br>DRIVER                       | 0        | Drives an external delay line.                                                                                            |

| 19     | TEARLYZP | TEARLY ZERO<br>PHASE TIMING                | 1        | Delay line tap for early precompensated write data and for zero phase startup of the VCO.                                 |

| 20     | THALFWIN | THALFWINDOW                                | ı        | Delay line tap for generating the enable phase delay when in phase detection mode.                                        |

| 21     | TLATE    | TLATE                                      | ı        | Delay line tap for late precompensated write data.                                                                        |

| 22     | RDATA    | READ DATA                                  | 0        | RDATA is RMFM synchronized to RCLK. The clock is removed from the RMFM by the controller.                                 |

| 23     | RCLK     | READ CLOCK                                 | 0        | RCLK is equal to one half of VCO and is synchronized to RDATA during a read operation and to WCLK while in an idle state. |

| 24     | VCC      | POWER SUPPLY                               | 1        | +5V Power Supply.                                                                                                         |

| 25     | PUMP     | PUMP                                       | I/O      | Charge PUMP to the PLL filter. Also a voltage input to the self-adjust sensing circuitry.                                 |

| 26     | VCOIN    | VOLTAGE<br>CONTROL<br>OSCILLATOR<br>INPUT  | I        | Input to the VCO gain stage. VCOIN is clamped low, and then released during zero phase startup.                           |

| 27     | VCOOUT   | VOLTAGE<br>CONTROL<br>OSCILLATOR<br>OUTPUT | 0        | Output from the VCO gain stage.                                                                                           |

| 28     | IPUMP    | IPUMP                                      | l<br>Sha | An external resistor connected to IPUMP establishes the magnitude of the charge pump current and ADJUST current.          |

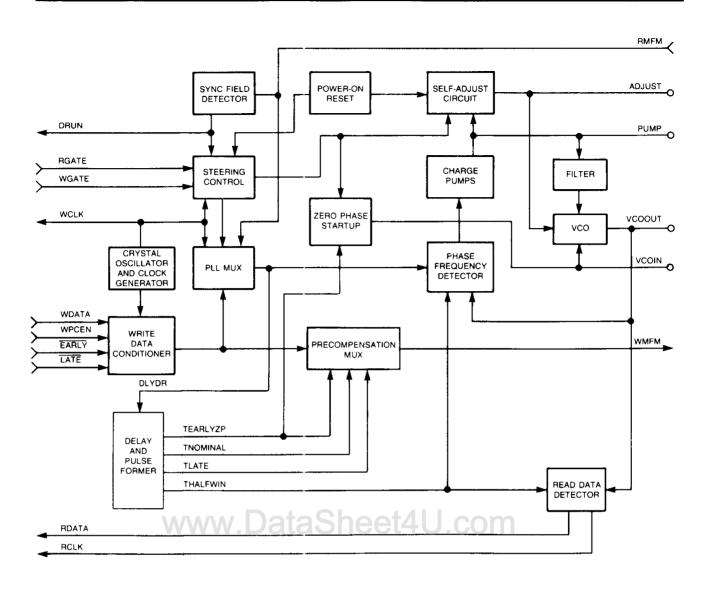

#### **ARCHITECTURE**

The WD10C20-05, with the necessay external components, provides the data interface between the WD1010 or WD2010 and an ST506/ST412 compatible drive. There are eight major functional sections within the WD10C20-05:

- Synchronized Field Detector

- Steering Control

- Phase-locked Loop (PLL)

Phase-frequency Detector

Charge Pumps

Filter

Voltage Controller Oscillator (VCO)

Zero Phase Startup Circuit Self Adjustment Circuit

- Read Data Detector

- Crystal Oscillator

- Write Data Conditioner

- · Delay And Pulse Former

- Power-on Reset

#### SYNCHRONIZATION FIELD DETECTOR

The Synchronization Field Detector discriminates between the 00's of a Synchronization Field and the low

frequency data immediately preceding these fields. The criterion used is pulse period discrimination on the RMFM data. The external resistor and capacitor connected to DRUNRC sets the nominal detection threshold of 1-3/8 bit times. DRUN goes low for long periods and high for short periods.

#### STEERING CONTROL

This logic controls the sequencing of events when the WD10C20-05 is switching between read, write and idle modes. When switching, the Steering Control disables the Phase-Frequency Detector and Charge Pumps, switches the MUX source, invokes zero-phase startup, selects the velocity lock mode of the Phase-Frequency Detector, and high gain on the Charge Pump. After the zero-phase startup is complete, the Phase-Frequency Detector and Charge pumps are enabled. If the device is in read or write mode, after four byte times the Steering Control switches to phase detection, and the charge pumps are set to low gain.

#### PHASE-LOCKED LOOP

# **Phase-Frequency Detector**

The Phase-Frequency Detector operates in one of two modes: velocity lock mode or phase-only detection.

Winchester Disk Support Devices

4-6

Velocity lock mode is used for acquisition when the PLL is switched to read or write data or when the PLL is following the reference crystal oscillator.

The Steering Control logic switches to the Phase-only mode when frequency and phase acquisition is nearly complete. Internal delay paths have been carefully matched to minimize introduction of a phase error due to switching. The phase-only mode must be used to lock to the MFM following the Sync Field, since that contains the three MFM frequencies.

In either mode, the Phase-Frequency detector converts a phase difference between the VCO and the input to a pulse width equal to the phase difference. The polarity of the phase error determines whether a signal is directed to the pump up or pump down circuitry in the Charge Pump section.

#### **Charge Pumps**

The Charge Pump circuit converts the widths received from the Phase-Frequency Detector to proportional amounts of charge, into or out of the filter. The gain of the Charge Pumps is set by the input current of the IPUMP signal. This current is set by an external resistor connected to the VCC.

#### Filter

The Filter converts the current pulses from the Charge Pumps to a voltage ouptut to the VCO. It also peforms the sample-and-hold function necessary for an edge locked PLL, and is also necessary during the zero phase startup period. As shown in Figure 1, one of the filter's capacitors (C110) is also part of the VCO's series resonant oscillator.

The filter must meet the specific requirements of acquisition time, capture range, and jitter ejection, and within the context of its effect on VCO operation. The filter functions to block high frequency signals due to RMFM read data jitter, and passes the low frequency signals of the RMFM.

# **Voltage Controlled Oscillator**

The VCO is a series resonant LC oscillator. The active gain element that provides the energy to sustain oscillation is within the WD10C20-05, between the VCOIN and VCOOUT pins. An inexpensive varactor controls and tunes the VCO. The filter connects to the anode of the varactor and provides the voltage for loop operation of the PLL. Higher voltages at the VCO input correspond to lower frequencies, and lower voltages correspond to higher frequencies. The self-adjustment circuit connects to the cathode of the varactor. The voltage bias at this point determines the location of the VCO's V-F characteristic curve, and is set for a favorable VCO input voltage at the nominal frequency of the VCO.

# Zero Phase Startup Circuit

The VCOIN connects to the Zero Phase Startup Circuit, which contains the logic necessary to turn a clamp on or off. This clamp, in turn, enables or

disables the VCO gain stage. When the WD10C20-05 changes the PLL input signal, the clamp is turned on for a minimum of one input data period. This stops the VCO gain and removes the AC energy from the passive VCO components. The VCO is now in a known state, and the time between the release of the clamp and the time the first edge of the VCO reaches the Phase Frequency Detector can be predicted. This event is made to coincide with the arrival of a data pulse by the delay between TEARLYZP and THALFWIN.

# Self Adjustment Circuit

The Self Adjustment Circuit (SAC) serves to slowly maintain the VCO's input voltage near the sense level. It performs compensation for component variations in much the same way as manual adjustments, as well as dynamic variations such as temperature, voltage and aging. Another advantage of this circuit is the heavy RC filtering of the + 12 volt supply. The SAC tunes the VCO so that its nominal output frequency of twice the data rate corresponds to an input voltage favorable to the Charge Pumps. This voltage is approximately half of the VCC, and centers the capture range. The PUMP signal connects to an internal comparator and senses the VCO input voltage to determine whether it is above or below the threshold voltage (VSENSE).

The comparator is sampled at a low frequency derived from the crystal. The output is used as the up / down control to a six-bit counter. At power-on, this counter is set to half scale. The least significant two bits are for noise immunity only. The most significant four bits connect to a digital-to-analog converter (DAC) that controls the current-sinking ability of the ADJUST signal. To convert the ADJUST signal current to a voltage, it is connected externally through a resistor to the + 12V. To filter the DAC steps and transients, the ADJUST is connected to two capacitors. A resistor from the ADJUST signal to the cathode of the VCO varactor completes the circuit. Refer to Figure 1.

#### **READ DATA DETECTOR**

The Read Data Detector produces RCLK and RDATA. RCLK is a square wave equal to one half of the VCO frequency. During data tracking, RCLK mirrors the slowly varying frequency of the RMFM. RDATA is a regenerated form of the RMFM, with the jitter removed and one-half bit-time pulse widths, and is exactly synchronous with RCLK. RCLK edges occur nominally in the center of RDATA to allow sufficient setup and hold time for the digital circuits in the WD1010 / WD2010 using these signals.

#### **CRYSTAL OSCILLATOR**

The Crystal Oscillator is designed to operate in the parallel resonant mode, with an external crystal and two capacitors. It generates the WCLK signal used externally. Internally, various divisions of it are used by the Write Data Conditioner, PLL, and SAC.

4–7

When an externally generated clock is desired, the crystal and capacitors are omitted. The XTALIN pin is connected to the clock source, and XTALOUT is left disconnected. The input levels of XTALIN are not TTL and must be guaranteed by the clock source.

#### WRITE DATA CONDITIONER

The Write Data Conditioner samples and precisely synchronizes WDATA, EARLY, and LATE on the leading and trailing edges of WCLK. When WGATE is asserted, the DLYDR signal is a direct derivative of WDATA and is connected to the input of the delay line. It returns to the WD10C20-05 via the TEARLYZP, TNOMINAL, and TLATE input signals. When WPCEN is de-asserted, WMFM follows the TNOMINAL signal. When WPCEN is asserted, the EARLY and LATE signals select the TEARLYZP and TLATE inputs, respectively. The differential delay between TEARLYZP and TNOMINAL at the delay line defines the amount of early precompensation, and similarly, the differential delay between TNOMINAL to TLATE defines the amount of late precompensation.

When WGATE is asserted, one of the initial MFM pulses is suppressed to create an interval of two bit times. This ensures that DRUN will go low at the beginning of a Sync Field preceding a data field, so that zero phase startup and velocity lock are executed properly. When WGATE is de-asserted. WMFM is held low.

#### **DELAY AND PULSE FORMER**

The Delay And Pulse Former includes the external delay line as well as logic internal to the WD10C20-05. In response to rising edges, it produces positive pulses slightly longer than one detection window, which is half of one bit time. The taps are also used for write precompensation, zero-phase startup, and defining the enable window for phase detection. Depending on the mode of operation, its input is either RMFM, synchronized WDATA, or WCLK.

#### **POWER-ON RESET**

This integrated function is used to reliably set flipflops to a predictable state during the application of the VCC. It is used by the Steering Control and SAC sections.

# DATA SEPARATOR CIRCUIT PERFORMANCE SPECIFICATIONS

The following specifications apply when the external components are selected as specified and operate within the following ranges:

$V_{CC} = +5V \pm .25V$  with  $\leq$  100 mV ripple, 0 to 30 KHz + 12V = + 12V  $\pm$  1.2V with  $\leq$  200 mV ripple, 0 to 30 KHz

Temperature = 0° to 70°C (32° to 158°F)

# PHASE-LOCKED LOOP:

| • | Acquisition Time   | > ± 2.2% ( ± 1% drive ·                                                              | om DRUN high)<br>±.1% crystal Osc.)                                                                    |

|---|--------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| • | Damping Factor     | min .7 typ. 1 max 1.4 V                                                              | elocity Lock                                                                                           |

| • | KD Error Amplifier | min .5 typ7 max 1.1 F<br>min 2 mA<br>typ 6 mA<br>max 10 mA<br>min 1 mA<br>typ 4.3 mA | Phase Detection Velocity Lock Operating Range VSENSE ± 1060 mv Phase Detection Operating Range         |

| • | Error Amplifier    | max 6.8 mA<br>max 2:1                                                                | VSENSE ± 950 mV<br>Phase Detection<br>Operating Range<br>VSENSE ± 950 mV<br>Phase: ± 5 to<br>± 40 nsec |

| • | Ko VCO Gain        | min 4.5% per volt<br>typ 5% per volt<br>max 7.5% per volt                            | 0                                                                                                      |

# FREQUENCY DETECTOR

DRUN must be high in response to RMFM rising edge to rising edge periods less than 250 nsec. DRUN must be low for periods greater than 300 nsec.

#### **CRYSTAL OSCILLATOR**

The operational frequency must be within  $\pm .1\%$  of 10 MHz.

# PHASE DETECTOR/CHARGE PUMPS

Phase Decision Points

While in the phase detection mode, the phase difference from null (zero pump current) to the decision points must be no less than  $\pm 40$  nsec.

#### VCO GAIN

Over the VCO input voltage range, VSENSE nominal  $\pm$  1060 mV, the VCO gain must be within the range of 4.5% to 7.5% per volt. There must be no interruptions in its characteristic V-F curve over the input voltage range.

4-8

Winchester Disk Support Devices

#### WD10C20-05 ELECTRICAL CHARCTERISTICS

#### MAXIMUM RATINGS

| V <sub>CC</sub> with respect to V <sub>SS</sub>             | + 5.5 Volts                 |

|-------------------------------------------------------------|-----------------------------|

| Max Voltage range on any pin                                |                             |

| (except ADILIST) with respect to Vac                        |                             |

| Max Voltage Range on ADJUST with respect to V <sub>SS</sub> | 0.5V to +13.2V              |

| Operating Temperature                                       | 0°C(32°F) to 70°C(158°F)    |

| Storage Temperature                                         | 65°C(-85°F) to 150°C(302°F) |

#### NOTE

Maximum limits indicate where permanent device damage occurs. Continuous operation at these limits is not intended and should be limited to those conditions specified in the DC Operating Characteristics

# DC OPERATING CHARACTERISTICS

$T_A = 0^{\circ}C (32^{\circ}F) \text{ to } 70^{\circ}C (158^{\circ}F)$

$V_{CC} = +5V \pm .25V$

Input signals:

TEARLYZP, TNOMINAL, TLATE, THALFWIN, TFULLWIN, RGATE, WGATE, WPCEN, WDATA, EARLY, LATE, RMFM

|   | SYMBOL          | CHARACTERISTIC     | MIN | TYP | MAX | UNIT | CONDITION |

|---|-----------------|--------------------|-----|-----|-----|------|-----------|

| r | V <sub>IH</sub> | Voltage Input High | 3.0 |     |     | ٧    |           |

|   | V <sub>IL</sub> | Voltage Input Low  |     |     | .8  | ٧    |           |

# Input signals:

TEARLYZP, TNOMINAL, TLATE, THALFWIN, TFULLWIN, RGATE, WGATE, XTALIN, VCOIN (Clamp off)

| SYMBOL          | CHARACTERISTIC | MIN | TYP  | MAX  | UNIT | CONDITION                         |

|-----------------|----------------|-----|------|------|------|-----------------------------------|

| I <sub>IN</sub> | Input leakage  | aoi | lee! | ± 10 | μA   | $V_{IN} = GND \text{ to } V_{CC}$ |

Input signals: WDATA, EARLY, LATE

| SYMBOL          | CHARACTERISTIC     | MIN | TYP | MAX  | UNIT | CONDITION                |

|-----------------|--------------------|-----|-----|------|------|--------------------------|

| I <sub>IH</sub> | Current Input High |     |     | + 10 | μΑ   | V <sub>IH</sub> = 3.4 V* |

| I <sub>IL</sub> | Current Input Low  |     |     | -4   | mA   | $V_{IL} = .45 V^*$       |

#### Input signal: WPCEN

| SYMBOL          | CHARACTERISTIC     | MIN | TYP | MAX  | UNIT | CONDITION               |

|-----------------|--------------------|-----|-----|------|------|-------------------------|

| 1 <sub>IH</sub> | Current Input High |     |     | + 10 | μA   | $V_{IH} = 3.4 V^*$      |

| I <sub>IL</sub> | Current Input Low  |     |     | -2   | mA   | V <sub>IL</sub> = .4 V* |

<sup>\*</sup>These inputs may or may not have an internal pullup resistor. In either case, if  $I_{\rm IH}$  and  $I_{\rm IL}$  meet these specs, the inputs will be driven correctly.

Winchester Disk Support Devices

4–9

Input signal: RMFM

| SYMBOL          | CHARACTERISTIC                          | MIN | TYP | MAX              | UNIT     | CONDITION                                                                     |

|-----------------|-----------------------------------------|-----|-----|------------------|----------|-------------------------------------------------------------------------------|

| I <sub>IL</sub> | Current Input High<br>Current Input Low |     |     | <b>0</b><br>-2.5 | mA<br>mA | V <sub>IH</sub> = 3.4 V<br>V <sub>IL</sub> = .4 V<br>Internal pullup resistor |

Input signal: XTALIN

| SYMBOL          | CHARACTERISTIC     | MIN | TYP | MAX | UNIT | CONDITION |

|-----------------|--------------------|-----|-----|-----|------|-----------|

| V <sub>IH</sub> | Voltage Input High | 3.6 | _   |     | ٧    |           |

| V <sub>IL</sub> | Voltage Input Low  |     |     | .6  | ٧    |           |

Output signals: WCLK\*\*, WMFM, DLYDR

| SYMBOL            | CHARACTERISTIC        | MIN | TYP | MAX | UNIT | CONDITION                |

|-------------------|-----------------------|-----|-----|-----|------|--------------------------|

| V <sub>OH</sub>   | Voltage Output High   | 2.4 |     |     | ٧    | $I_{OH} = -1 \text{ mA}$ |

| V <sub>OL</sub>   | Voltage Output Low    |     |     | .4  | ٧    | $I_{OL} = 4 \text{ mA}$  |

| T <sub>RISE</sub> | Rise Time .8 to 2.0 V |     |     | 10  | nsec | CL = 30 pf               |

| T <sub>FALL</sub> | Fall Time 2.0 to .8 V |     |     | 10  | nsec | CL = 30 pf               |

| FALL              | Fall Time 2.0 to .8 V |     |     | 10  | nsec | CL = 30 pt               |

Output signal: WCLK\*\*

| SYMBOL            | CHARACTERISTIC        | MIN | TYP  | MAX | UNIT     | CONDITION               |

|-------------------|-----------------------|-----|------|-----|----------|-------------------------|

| V <sub>OH</sub>   | Voltage Output High   | 4.6 |      |     | <b>V</b> | $I_{OH} = -100  \mu A$  |

| V <sub>OL</sub>   | Voltage Output Low    |     |      | .2  | V        | $I_{OL} = 1 \text{ mA}$ |

| T <sub>RISE</sub> | Rise Time .9 to 4.2 V |     |      | 30  | nsec     | CL = 30 pf              |

| T <sub>FALL</sub> | Fall Time 4.2 to .9 V | She | eet4 | 30  | nsec     | CL = 30 pf              |

<sup>\*\*</sup>WCLK has two requirements. It must be able to drive special WD1010 / WD2010 inputs, as well as a buffer at TTL levels. In any application, the total capacitance of the WD1010 / WD2010, buffer, and PC board, must not be more than 30 pf. The total input current of the WD1010 / WD2010 and buffer at the different input voltages must not exceed the above specification.

Output signals: RCLK, RDATA, DRUN

| SYMBOL            | CHARACTERISTIC        | MIN  | TYP | MAX | UNIT | CONDITION                 |

|-------------------|-----------------------|------|-----|-----|------|---------------------------|

| V <sub>OH</sub>   | Voltage Output High   | 4.65 |     |     | ٧    | $I_{OH} = -20 \mu A$      |

| $V_{OL}$          | Voltage Output Low    |      |     | .2  | V    | $I_{OI} = 20 \mu\text{A}$ |

| T <sub>RISE</sub> | Rise Time .9 to 4.2 V |      |     | 30  | nsec | CL = 20 pf                |

| T <sub>FALL</sub> | Fall Time 4.2 to .9 V |      |     | 30  | nsec | CL = 20 pf                |

#### Self Adjust, Pump, and Power

| SYMBOL           | CHARACTERISTIC           | MIN | TYP   | MAX  | UNIT | CONDITION            |

|------------------|--------------------------|-----|-------|------|------|----------------------|

| V <sub>S</sub>   | VSENSE Threshold         |     | 2.4   |      | ٧    |                      |

| I <sub>A</sub>   | ACQUISITION PUMP Current |     | ±6    |      | mΑ   | 3.57K on IPUMP***    |

| I <sub>T</sub>   | TRACKING PUMP Current    |     | ± 4.5 |      | mΑ   | 3.57K on IPUMP***    |

| l <sub>JMX</sub> | ADJUST Max Current       | .4  | .6    | 1.0  | mΑ   | 3.57K on IPUMP***    |

| I <sub>JMN</sub> | ADJUST Min Current       |     |       | ± 10 | μΑ   |                      |

| I <sub>CC</sub>  | Power Supply Current     |     | 40    |      | mA   | 3.57K on IPUMP, 5MHz |

<sup>\*\*\*</sup>Depending upon the application, there are specific requirements upon the pump currents and their relationship to VSENSE. This document is written for 5 Mbit/sec, WD1010/WD2010, ST506/ST412 drive.

# **AC OPERATING CHARACTERISTICS**

Timing on signals RDATA, RCLK, WCLK, and DRUN are measured at the voltage halfway between the WD1010/WD2010's VIH and VIL: 2.55 Volts. All other signals are measured from the I.4 volt transition. All timing is measured with the load capacitance, CL = 50 pf.

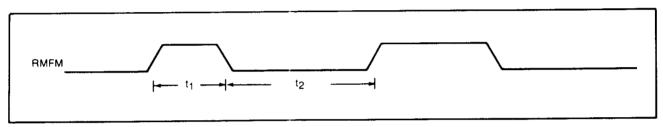

FIGURE 3. DISK DRIVE READ DATA, PULSE FORMING TABLE 1. DISK DRIVE READ DATA, PULSE FORMING

| SYMBOL                        | CHARACTERISTIC                                | MIN      | TYP | MAX | UNIT         | CONDITION |

|-------------------------------|-----------------------------------------------|----------|-----|-----|--------------|-----------|

| t <sub>1</sub> t <sub>2</sub> | RMFM Pulse Width High<br>RMFM Pulse Width Low | 20<br>25 | iee | 150 | nsec<br>nsec | M         |

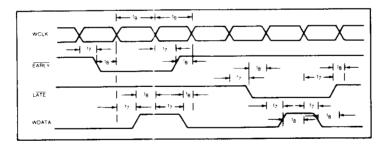

FIGURE 4. WRITE SETUP/OLD TABLE 2. WRITE SETUP/HOLD

| SYMBOL         | CHARACTERISTIC   | MIN | TYP | MAX | UNIT | CONDITION |

|----------------|------------------|-----|-----|-----|------|-----------|

| t <sub>7</sub> | Hold Time        | 5   |     |     | nsec |           |

| t <sub>8</sub> | Setup Time       | 20  |     |     | nsec |           |

| t <sub>9</sub> | WCLK Pulse Width | 95  |     | 105 | nsec |           |

Setup and Hold time is independent of the application of the WD10C20-05.

Winchester Disk Support Devices

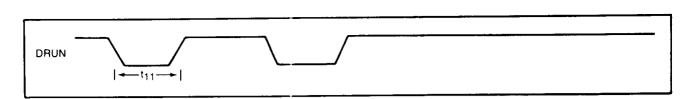

FIGURE 5. DRUN

**TABLE 3. DRUN**

| SYMBOL          | CHARACTERISTIC       | MIN | TYP | MAX | UNIT | CONDITION |

|-----------------|----------------------|-----|-----|-----|------|-----------|

| t <sub>11</sub> | DRUN Low Pulse Width | 30  |     |     | nsec | *         |

\*No requirement on DRUN pulse width high

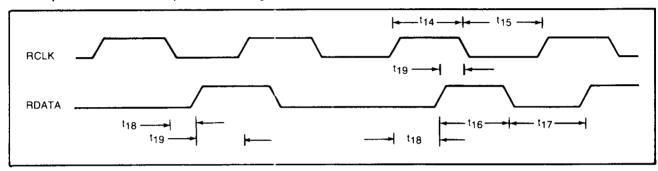

FIGURE 6. RCLK, RDATA TIMING TABLE 4. RCLK, RDATA TIMING

| SYMBOL          | CHARACTERISTIC         | MIN | TYP | MAX | UNIT | CONDITION                              |

|-----------------|------------------------|-----|-----|-----|------|----------------------------------------|

| t <sub>14</sub> | RCLK High Pulse Width  | 93  |     | 108 | nsec |                                        |

| t <sub>15</sub> | RCLK Low Pulse Width   | 93  |     | 108 | nsec |                                        |

| t <sub>16</sub> | RDATA High Pulse Width | 93  |     | 108 | nsec |                                        |

| t <sub>17</sub> | RDATA Low Pulse Width  | 93  |     | 108 | nsec |                                        |

| t <sub>18</sub> | RCLK Edge to RDATA     | 30  |     |     | nsec | Max is implicit in t <sub>19</sub> min |

|                 | Rising Edge            |     |     | !   |      |                                        |

| t <sub>19</sub> | RDATA Rising Edge To   | 30  |     |     | nsec | Max is implicit in t <sub>18</sub> min |

|                 | RCLK Edge              |     |     |     |      |                                        |

$t_{14}$  and  $t_{15}$  each define an MFM detection window. The rising edge of RDATA must occur within the window.  $t_{14} + t_{15} =$  the current bit cell time.

Winchester Disk Support Devices

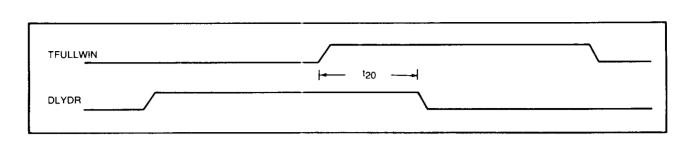

FIGURE 7. DLYDR, TFULLWIN TIMING

# **TABLE 5. DLYDR, TFULLWIN TIMING**

| SYMBOL          | CHARACTERISTIC     | MIN | TYP | MAX | UNIT | CONDITION |

|-----------------|--------------------|-----|-----|-----|------|-----------|

| t <sub>20</sub> | DLYDR Shutoff Time | 12  |     | 36  | nsec |           |

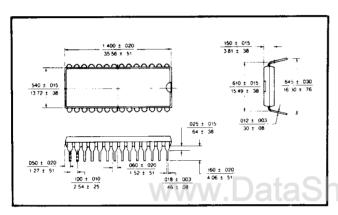

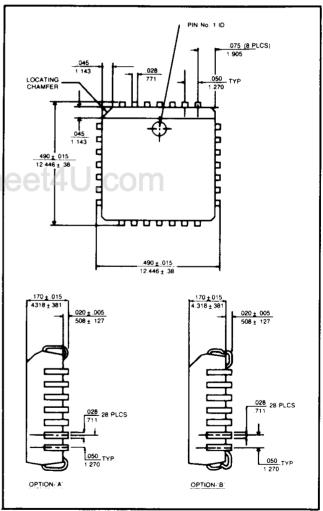

#### **PACKAGE DIAGRAMS**

28 LEAD PLASTIC PH

28 LEAD PLASTIC QUAD JH

Winchester Disk Support Devices

4-13