### 68020 FEATURES

- Selection of Processor Speeds: 16.67, 20, 25 MHz

- Military Temperature Range: -55°C to +125°C

- Packaging

- •114 pin Ceramic PGA (P2)

- •132 lead Ceramic Quad Flatpack, CQFP (Q2)

- Object-code compatible with earlier 68000 Microprocessors

- Addressing mode extensions for enhanced support of high-level languages

- Bit Field Data Type Accelerates Bit-Oriented Applications—i.e., Video Graphics

- Fast On-Chip Instruction Cache Speeds Instructions and Improves Bus Bandwidth

- Coprocessor Interface to Companion 32-Bit Peripherals—the 68881 and 68882 Floating-Point Coprocessors and the 68851 Paged Memory Management Unit

- Pipelined Architecture with High Degree of Internal Parallelism allowing Multiple Instructions to be executed concurrently

- High-Performance Asynchronous Bus Is Nonmultiplexed and Full 32-Bits

- Dynamic Bus Sizing Efficiently Supports 8-/16-/32-Bit Memories and Peripherals

- Full Support of Virtual Memory and Virtual Machine

- 16 32-Bit General-Purpose Data and Address Registers

- Two 32-Bit Supervisor Stack Pointers and Five Special-Purpose Control Registers

- 18 Addressing Modes and 7 Data Types

- 4 GigaByte Direct Addressing Range

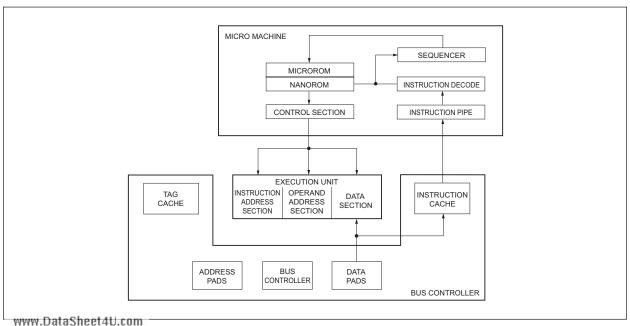

#### DESCRIPTION

The WC32P020 is a 32-bit implementation of the 68000 Family of microprocessors. Using HCMOS technology, the WC32P020 is implemented with 32-bit registers and data paths, 32-bit addresses, a powerful instruction set, and flexible addressing modes.

#### FIGURE 1 – BLOCK DIAGRAM

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

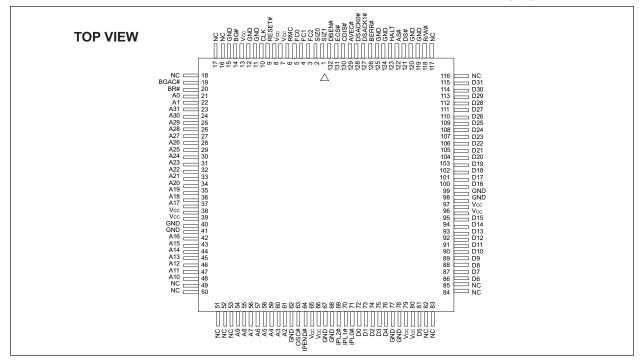

# FIGURE 2 – PIN CONFIGURATION FOR WC32P020-XXM, CQFP (Q2)

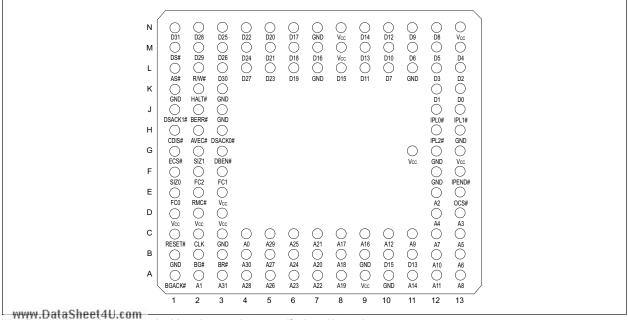

# FIGURE 3 - PIN CONFIGURATION FOR WC32P020-XXM, PGA (P2)

hite Electronic Designs Corp. reserves the right to change products or specifications without notice.

#### **ADDRESSING MODES**

| Addressing                                                | Syntax          |

|-----------------------------------------------------------|-----------------|

| Register Direct                                           |                 |

| Data Register Direct                                      | Dn              |

| Address Register Direct                                   | An              |

| Register Indirect                                         |                 |

| Address Register Indirect                                 | (An)            |

| Address Register Indirect with Postincrement              | (An) +          |

| Address Register Indirect with Predecrement               | - (An)          |

| Address Register Indirect with Displacement               | (d16,An)        |

| Register Indirect with Index                              |                 |

| Address Register Indirect with Index (8-Bit Displacement) | (d8,An,Xn)      |

| Address Register Indirect with Index (Base Displacement)  | (bd,An,Xn)      |

| Memory Indirect                                           |                 |

| Memory Indirect Postindexed                               | ([bd,An],Xn,od) |

| Memory Indirect Preindexed                                | ([bd,An,Xn],od) |

| Program Counter Indirect with Displacement                | (d16,PC)        |

| Program Counter Indirect with Index                       |                 |

| PC Indirect with Index (8-Bit Displacement)               | (d8,PC,Xn)      |

| PC Indirect with Index (Base Displacement)                | (bd,PC,Xn)      |

| Program Counter Memory Indirect                           |                 |

| PC Memory Indirect Postindexed                            | ([bd,PC],Xn,od) |

| PC Memory Indirect Preindexed                             | ([bd,PC,Xn],od) |

| Absolute                                                  | (               |

| Absolute Short                                            | xxx).W          |

| Absolute Long                                             | (xxx).L         |

| Immediate                                                 | #(data)         |

#### NOTES:

- Dn = Data Register, DO-D7

- An = Address Register, AO-A7

- d8, d16 = A twos-complement or sign-extended displacement; added as part of the effective address calculation; size is 8 (d8) or 16 (d16) bits; when omitted, assemblers use a value of zero.

- Xn = Address or data register used as an index register; form is Xn.SIZE\*SCALE, where SIZE is.W or .L (indicates index register size) and SCALE is 1, 2, 4, or 8 (index register is multiplied by SCALE); use of SIZE and/or SCALE is optional.

- bd = A twos-complement base displacement; when present, size can be 16 or 32 hits

- od = 0uter displacement, added as part of effective address calculation after any memory indirection, use is optional with a size of 16 or 32 bits.

- PC = Program Counter

- (data) = Immediate value of 8, 16, or 32 bits

- () = Effective Address

- [] = Use as indirect access to long-word address.

### **INSTRUCTION SET**

| Mnemonic | Description                     |

|----------|---------------------------------|

| ABCD     | Add Decimal with Extend         |

| ADD      | Add                             |

| ADDA     | Add Address                     |

| ADDI     | Add Immediate                   |

| ADDQ     | Add Quick                       |

| ADDX     | Add with Extend                 |

| AND      | Logical AND                     |

| ANDI     | Logical AND Immediate           |

| ASL, ASR | Arithmetic Shift Left and Right |

| Mnemonic    | Description                                     |

|-------------|-------------------------------------------------|

| Bcc         | Branch Conditionally                            |

| BCHG        | Test Bit and Change                             |

| BCLR        | Test Bit and Clear                              |

| BFCHG       | Test Bit Field and Change                       |

| BFCLR       | Test Bit Field and Clear                        |

| BFEXTS      | Signed Bit Field Extract                        |

| BFEXTU      | Unsigned Bit Field Extract                      |

| BFFFO       | Bit Field Find First One                        |

| BFINS       | Bit Field Insert                                |

| BFSET       | Test Bit Field and Set                          |

| BFTST       | Test Bit Field                                  |

| BKPT        | Breakpoint                                      |

| BRA         | Branch                                          |

| BSET        | Test Bit and Set                                |

| BSR         | Branch to Subroutine                            |

| BTST        | Test Bit                                        |

| CALLM       | Call Module                                     |

| CAS         | Compare and Swap Operands                       |

| CAS2        | Compare and Swap Dual Operands                  |

| CHK         | Check Register Against Bound                    |

| CHK2        | Check Register Against Upper and Lower Bounds   |

| CLR         | Clear                                           |

| CMPA        | Compare Compare Address                         |

| CMPI        | Compare Immediate                               |

| CMPM        | Compare Memory to Memory                        |

| CMP2        | Compare Register Against Upper and Lower Bounds |

| DBcc        | Test Condition, Decrement and Branch            |

| DIVS, DIVSL | Signed Divide                                   |

| DIVU, DIVUL | Unsigned Divide                                 |

| EOR         | Logical Exclusive OR                            |

| EORI        | Logical Exclusive OR Immediate                  |

| EXG         | Exchange Registers                              |

| EXT, EXTB   | Sign Extend                                     |

| ILLEGAL     | Take Illegal Instruction Trap                   |

| JMP         | Jump                                            |

| JSR         | Jump to Subroutine                              |

| LEA         | Load Effective Address                          |

| LINK        | Link and Allocate                               |

| LSL, LSR    | Logical Shift Left and Right                    |

| MOVE        | Move                                            |

| MOVEA       | Move Address                                    |

| MOVE CCR    | Move Condition Code Register                    |

| MOVE SR     | Move Status Register                            |

| MOVE USP    | Move User Stack Pointer                         |

| MOVEC       | Move Control Register                           |

| MOVEM       | Move Multiple Registers                         |

| MOVEP       | Move Peripheral                                 |

| MOVEQ       | Move Quick                                      |

| MOVES       | Move Alternate Address Space                    |

| MULS        | Signed Multiply                                 |

| MULU        | Unsigned Multiple                               |

|             |                                                 |

www.DataSheet4U.com

Electronic Designs Corp. reserves the right to change products or specifications without notice.

# **INSTRUCTION SET (cont'd)**

| Mnemonic   | Description                                       |

|------------|---------------------------------------------------|

| NBCD       | Negate Decimal with Extend                        |

| NEG        | Negate Negate                                     |

| NEGX       | Negate with Extend                                |

| NOP        | No Operation                                      |

| NOT        | Logical Complement                                |

| OR         | Logical Inclusive OR                              |

| ORI        | Logical Inclusive OR Immediate                    |

| ORI CCR    | Logical Inclusive OR Immediate to Condition Codes |

| ORI SR     | Logical Inclusive OR Immediate to Status Register |

| PACK       | Pack BCD                                          |

| PEA        | Push Effective Address                            |

| RESET      | Reset External Devices                            |

| ROL, ROR   | Rotate Left and Right                             |

| ROXL, ROXR | Rotate with Extend Left and Right                 |

| RTD        | Return and Deallocate                             |

| RTE        | Return from Exception                             |

| RTM        | Return from Module                                |

| RTR        | Return and Restore Codes                          |

| RTS        | Return from Subroutine                            |

| SBCD       | Subtract Decimal with Extend                      |

| Scc        | Set Conditionally                                 |

| STOP       | Stop                                              |

| SUB        | Subtract                                          |

| SUBA       | Subtract Address                                  |

| SUBI       | Subtract Immediate                                |

| SUBQ       | Subtract Quick                                    |

| SUBX       | Subtract with Extend                              |

| SWAP       | Swap Register Words                               |

| TAS        | Test Operand and Set                              |

| TRAP       | Trap                                              |

| TRAPcc     | Trap Conditionally                                |

| TRAPV      | Trap on Overflow                                  |

| TST        | Test Operand                                      |

| UNLK       | Unlink                                            |

| UNPK       | Unpack BCD                                        |

#### COPROCESSOR INSTRUCTIONS

| Mnemonic | Description                                      |

|----------|--------------------------------------------------|

| срВсс    | Branch Conditionally                             |

| cpDBcc   | Test Coprocessor Condition, Decrement and Branch |

| cpGEN    | Coprocessor General Instruction                  |

| Mnemonic  | Description                           |

|-----------|---------------------------------------|

| cpRESTORE | Restore Internal State of Coprocessor |

| cpSAVE    | Save Internal State of Coprocessor    |

| cpScc     | Set Conditionally                     |

| cpTRAPcc  | Trap Conditionally                    |

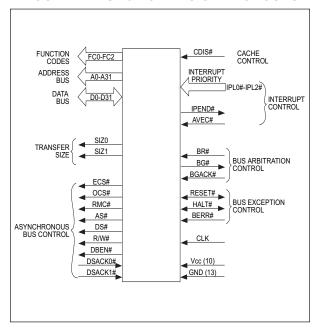

# SIGNAL DESCRIPTION

The V<sub>CC</sub> and GND pins are separated into four groups to provide individual power supply connections for the address bus buffers, data bus buffers, and all other buffers and internal logic. See FIGURE 4.

| Group       | Vcc                  | GND              |

|-------------|----------------------|------------------|

| Address Bus | A9, D3               | A10, B9, C3, F12 |

| Data Bus    | M8, N8, N13          | L7, L11, N7, K3  |

| Logic       | D1, D2, E3, G11, G13 | G12, H13, J3, K1 |

| Clock       | _                    | B1               |

#### FIGURE 4 - FUNCTIONAL SIGNAL GROUPS

www.DataSheet4U.com

tronic Designs Corp. reserves the right to change products or specifications without notice.

### **SIGNAL INDEX**

| Signal Name                           | Mnemonic        | Function                                                                                                                                                                                                                           |

|---------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function Codes                        | FC2-FC0         | 3-bit function code used to identify the address space of each bus cycle.                                                                                                                                                          |

| Address Bus                           | A0-A31          | 32-bit address bus.                                                                                                                                                                                                                |

| Data Bus                              | D0-D31          | 32-bit data bus used to transfer 8, 16, 24, or 32 bits of data per bus cycle.                                                                                                                                                      |

| Size                                  | SIZ0/SIZ1       | Indicates the number of bytes remaining to be transferred for this cycle. These signals, together with A1 and A0, define the active sections of the data bus.                                                                      |

| External Cycle Start                  | ECS#            | Provides an indication that a bus cycle is beginning.                                                                                                                                                                              |

| Operand Cycle Start                   | OCS#            | Identical operation to that of ECS except that OCS is asserted only during the first bus cycle of an operand transfer.                                                                                                             |

| Read,Write                            | R/W#            | Defines the bus transfer as a processor read or write.                                                                                                                                                                             |

| Read-Modify-Write Cycle               | RMC#            | Provides an indicator that the current bus cycle is part of an indivisible read-modify-write operation.                                                                                                                            |

| Address Strobe                        | AS#             | Indicates that a valid address is on the bus.                                                                                                                                                                                      |

| Data Strobe                           | DS#             | Indicates that valid data is to be placed on the data bus by an external device or has been placed on the data bus by the WC32P020-XXM.                                                                                            |

| Data Buffer Enable                    | DBEN#           | Provides an enable signal for external data buffers.                                                                                                                                                                               |

| Data Transfer and Size<br>Acknowledge | DSACK0#/DSACK1# | Bus response signals that indicate the requested data transfer operation has completed. In addition, these two lines indicate the size of the external bus port on a cycle-by-cycle basis and are used for asynchronous transfers. |

| Interrupt Priority Level              | IPL0#-IPL2#     | Provides an encoded interrupt level to the processor.                                                                                                                                                                              |

| Interrupt Pending                     | IPEND#          | Indicates that an interrupt is pending.                                                                                                                                                                                            |

| Autovector                            | AVEC#           | Requests an autovector during an interrupt acknowledge cycle.                                                                                                                                                                      |

| Bus Request                           | BR#             | Indicates that an external device requires bus mastership.                                                                                                                                                                         |

| Bus Grant                             | BG#             | Indicates that an external device may assume bus mastership.                                                                                                                                                                       |

| Bus Grant Acknowledge                 | BGACK#          | Indicates that an external device has assumed bus mastership.                                                                                                                                                                      |

| Reset                                 | RESET#          | System reset.                                                                                                                                                                                                                      |

| Halt                                  | HALT#           | Indicates that the processor should suspend bus activity.                                                                                                                                                                          |

| Bus Error                             | BERR#           | Indicates that an erroneous bus operation is being attempted.                                                                                                                                                                      |

| Cache Disable                         | CDIS#           | Dynamically disables the on-chip cache to assist emulator support                                                                                                                                                                  |

| Clock                                 | CLK             | Clock input to the processor.                                                                                                                                                                                                      |

| Power Supply                          | Vcc             | Power supply.                                                                                                                                                                                                                      |

| Ground                                | GND             | Ground connection.                                                                                                                                                                                                                 |

|                                       |                 |                                                                                                                                                                                                                                    |

#### **MAXIMUM RATINGS**

| Symbol | Parameter                    | Min  | Max  | Unit |

|--------|------------------------------|------|------|------|

| Vcc    | Supply voltage               | -0.3 | +7.0 | V    |

| Vı     | Input voltage                | -0.3 | +7.0 | V    |

| PDMAX  | Max Power dissipation        |      | 2.0  | W    |

| TCASE  | Operating temperature (Mil.) | -55  | +125 | °C   |

| TCASE  | Operating temperature (Ind.) | -40  | +85  | °C   |

| Tstg   | Storage temperature          | -55  | +150 | °C   |

| TJ     | Junction temperature         |      | +160 | °C   |

#### **Thermal Characteristics**

(with no heat sink or airflow)

| Characteristic                                       | Symbol | Value | Rating |

|------------------------------------------------------|--------|-------|--------|

| Thermal Resistance — Junction to Ambient PGA Package | θја    | 26    | °C/W   |

| CQFP Package                                         |        | 46    |        |

| Thermal Resistance — Junction to Case                | θјс    |       | °C/W   |

| PGA Package                                          |        | 3     |        |

| CQFP Package                                         |        | 15    |        |

# POWER CONSIDERATIONS

The average chip junction temperature, TJ, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

where:

T<sub>A</sub> = Ambient Temperature, °C

$q_{JA}$  = Package Thermal Resistance, Junction-to-

Ambient, °C/W

$P_D = PINT+PI/O$

PINT = Icc x Vcc, Watts-Chip Internal Power

Pi/o = Power Dissipation on Input and Output Pins-User Determined

For most applications, P<sub>I/O</sub> < P<sub>INT</sub> and can be neglected.

The following is an approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected ):

$$P_D = K \triangleright (T_J + 273^{\circ}C)$$

(2)

Solving equations (1) and (2) for K gives:

$$K = P_D \cdot (T_A + 273^{\circ}C) + q_{JA} \cdot P_{D^2}$$

(3)

where K is a constant pertaining to the particular part. K can be determined from equation (3) by measuring  $P_D$  (at equilibrium) for a known TA. Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

The total thermal resistance of a package ( $\theta_{JA}$ ) can be separated into two components,  $\theta_{JC}$  and  $\theta_{CA}$ , representing the barrier to heat flow from the semiconductor junction to the package (case) surface ( $\theta_{JC}$ ) and from the case to the outside ambient ( $q_{CA}$ ). These terms are related by the equation:

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

(4)

$\theta_{JC}$  is device related and cannot be influenced by the user. However,  $\theta_{CA}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling, and thermal convection. Thus, good thermal management on the part of the user can significantly reduce  $\theta_{CA}$  so that  $\theta_{JA}$  approximately equals  $\theta_{JC}$ . Substitution of  $\theta_{JC}$  for  $\theta_{JA}$  in equation (1) will result in a lower semiconductor junction temperature.

### DC ELECTRICAL CHARACTERISTICS

$V_{CC} = 5.0 \text{ V}_{DC} \pm 5\%$ , GND =  $0 \text{ V}_{DC}$ ,  $-55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$

|                                                                          | Characteristics                                                                   | Symbol | Min      | Max       | Unit |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------|----------|-----------|------|

| Input High Voltage                                                       |                                                                                   | Vih    | 2.0      | Vcc       | V    |

| Input Low Voltage                                                        |                                                                                   | VIL    | GND -0.5 | 0.8       | V    |

| Input Leakage Current<br>GND - V <sub>IN</sub> - V <sub>CC</sub>         | BERR#, BR#, BGACK#, CLK, IPL0-2#, AVEC#,<br>CDIS#, DSACK0#, DSACK1#               | lin    | -4       | 4.0       | μA   |

|                                                                          | HALT#, RESET#                                                                     |        | -20      | 20        |      |

| High-Z (Off State) Leakage Current                                       | A31-0, AS#, DBEN#, DS#, D31-0, FC2-0 R/W#, RM#, SIZ1-0                            | Ітѕі   | -20      | 20        | μA   |

| Output High Voltage                                                      | A31-0, AS#, BG#, D31-0, DBEN#, DS#, ECS#, R/W#, IPEND#, OCS#, RMC#, SIZ1-0, FC2-0 | Voн    | 2.4      | _         | V    |

| Output Low Voltage                                                       |                                                                                   | VoL    |          |           | V    |

| loL = 3.2 mA                                                             | A31-0, FC2-0, SIZ1-0, BG#, D31-0                                                  |        | _        | 0.5       |      |

| $I_{OL} = 5.3 \text{ mA}$                                                | AS#, DS#, R/W#, RMC#, DBEN#, IPEND#                                               |        | _        | 0.5       |      |

| loL = 2.0 mA                                                             | ECS#, OCS#                                                                        |        | -        | 0.5       |      |

| I <sub>OL</sub> = 10.7 mA                                                | HALT#, RESET#                                                                     |        | _        | 0.5       |      |

| Maximum Supply Current                                                   |                                                                                   | Icc    | _        | 333       | mA   |

| Capacitance (1)<br>V <sub>IN</sub> = 0V, T <sub>A</sub> = 25°C, f = 1MHz |                                                                                   | Cin    | _        | 20        | pF   |

| Load Capacitance                                                         | ECS#, OCS#<br>All Other                                                           | CL     | _        | 50<br>130 | pF   |

#### NOTES:

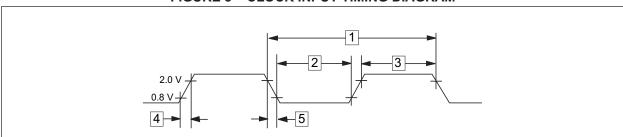

# AC ELECTRICAL SPECIFICATIONS - CLOCK INPUT (see Figure 5)

|                        |               | 16.67 MHz |       | 20 MHz |     | 25MHz |     |      |

|------------------------|---------------|-----------|-------|--------|-----|-------|-----|------|

| Characteristic         | Specification | Min       | Max   | Min    | Max | Min   | Max | Unit |

| Frequency of Operation |               | 8         | 16.67 | 12.5   | 20  | 12.5  | 25  | MHz  |

| Cycle Time             | 1             | 60        | 125   | 50     | 80  | 40    | 80  | ns   |

| Clock Pulse Width      | 2,3           | 24        | 95    | 20     | 54  | 19    | 61  | ns   |

| Rise and Fall Times    | 4,5           | _         | 5     | _      | 5   | _     | 4   | ns   |

### FIGURE 5 - CLOCK INPUT TIMING DIAGRAM

NOTE: Timing measurements are referenced to and from a low 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

www.DataSheet4U.com

Designs Corp. reserves the right to change products or specifications without notice.

<sup>1.</sup> Capacitance is guaranteed by design but not tested.

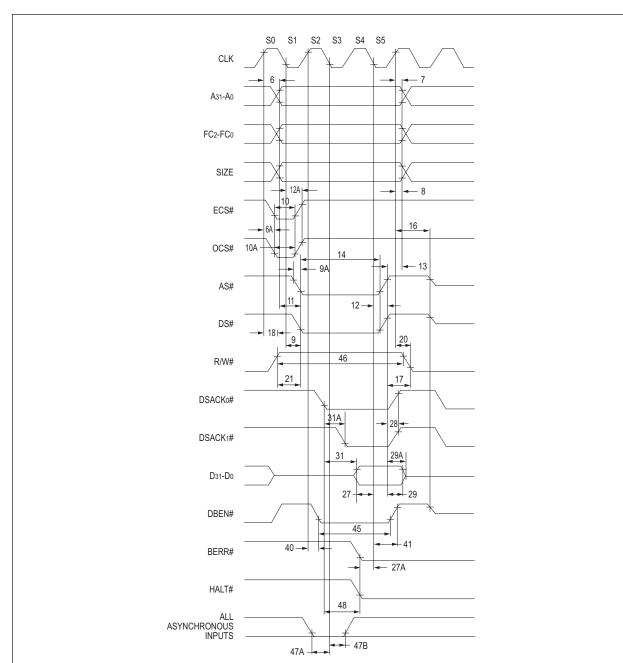

#### AC ELECTRICAL SPECIFICATIONS - READ AND WRITE CYCLES

$V_{CC} = 5.0 \text{ V}_{DC} \pm 5\%$ , GND =  $0 \text{ V}_{DC}$ ,  $-55^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$

|                                                               |               | 16.67 MHz |     | 20 MHz |     | 25 MHz |     |      |

|---------------------------------------------------------------|---------------|-----------|-----|--------|-----|--------|-----|------|

| Characteristic                                                | Specification | Min       | Max | Min    | Max | Min    | Max | Unit |

| Clock high to Address, FC, Size, RMC# Valid                   | 6             | 0         | 30  | 0      | 25  | 0      | 25  | ns   |

| Clock High to ECS#, OCS# Asserted                             | 6A            | 0         | 20  | 0      | 15  | 0      | 12  | ns   |

| Clock High to Address, Data, FC, Size, RMC#, High Impedance   | 7             | 0         | 60  | 0      | 50  | 0      | 40  | ns   |

| Clock high to Address, FC, Size, RMC# Invalid                 | 8             | 0         | _   | 0      | _   | 0      | _   | ns   |

| Clock Low to AS#, DS# Asserted                                | 9             | 1         | 30  | 1      | 25  | 1      | 18  | ns   |

| AS# to DS# Assertion (Read) (Skew)                            | 9A (1)        | -15       | 15  | -10    | 10  | -10    | 10  | ns   |

| AS# Asserted to DS# Asserted (Write)                          | 9B (11)       | 37        | _   | 32     | _   | 27     | _   | ns   |

| ECS# Width Asserted                                           | 10            | 20        | _   | 15     | _   | 15     | _   | ns   |

| OCS# Width Asserted                                           | 10            | 20        | _   | 15     | _   | 15     | _   | ns   |

| ECS#, OCS# width Negated                                      | 10B (7)       | 15        | _   | 10     | _   | 5      | _   | ns   |

| Address, FC, Size, RMC#, Valid to AS# (and DS# Asserted Read) | 11            | 15        | _   | 10     | _   | 6      | _   | ns   |

| Clock Low to AS#, DS# Negated                                 | 12            | 0         | 30  | 0      | 25  | 0      | 15  | ns   |

| Clock Low to ECS#, OCS# Negated                               | 12A           | 0         | 30  | 0      | 25  | 0      | 15  | ns   |

| AS#, DS# Negated to Address, FC, Size, RMC# Invalid           | 13            | 15        | _   | 10     | _   | 10     | _   | ns   |

| AS# (and DS# Read) Width Asserted                             | 14            | 100       | _   | 85     | _   | 70     | _   | ns   |

| DS# Width Asserted Write                                      | 14A           | 40        | _   | 38     | _   | 30     | _   | ns   |

| AS#, DS# Width Negated                                        | 15            | 40        | _   | 38     | _   | 30     | _   | ns   |

| DS# Negated to AS# Asserted                                   | 15A (8)       | 35        | _   | 30     | _   | 25     | _   | ns   |

| Clock High to AS#, DS#, R/W# Invalid, High Impedance          | 16            | _         | 60  | _      | 50  | _      | 40  | ns   |

| AS#, DS# Negated to R/W# Invalid                              | 17            | 15        | _   | 10     | _   | 10     | _   | ns   |

| Clock High to R/W# High                                       | 18            | 0         | 30  | 0      | 25  | 0      | 20  | ns   |

| Clock High to R/W# Low                                        | 20            | 0         | 30  | 0      | 25  | 0      | 20  | ns   |

| R/W# High to AS# Asserted                                     | 21            | 15        | _   | 10     | _   | 5      | _   | ns   |

| R/W# Low to DS# Asserted (Write)                              | 22            | 75        | _   | 60     | _   | 50     | _   | ns   |

| Clock High to Data Out Valid                                  | 23            | _         | 30  | _      | 25  | _      | 25  | ns   |

| DS# Negated to Data Out Invalid                               | 25            | 15        | _   | 10     | _   | 5      | _   | ns   |

| DS# Negated to DBEN# Negated (Write)                          | 25A (9)       | 15        | _   | 10     | _   | 5      | _   | ns   |

| Data Out Valid to DS# Asserted (Write)                        | 26            | 15        | _   | 10     | _   | 5      | _   | ns   |

| Data-In Valid to Clock Low (Data Setup)                       | 27            | 5         | _   | 5      | _   | 5      | _   | ns   |

| Late BERR#/HALT# Asserted to Clock Low Setup Time             | 27A           | 20        | _   | 15     | _   | 10     | _   | ns   |

| AS#, DS# Negated to DSACKx#, BERR#, HALT#, AVEC# Negated      | 28            | 0         | 80  | 0      | 65  | 0      | 50  | ns   |

| DS# Negated to Data-In Invalid (Data-In Hold Time)            | 29            | 0         | _   | 0      | _   | 0      | _   | ns   |

| DS# Negated to Data-In (High Impedance)                       | 29A           | _         | 60  | _      | 50  | _      | 40  | ns   |

| DSACKx# Asserted to Data-In Valid                             | 31 (2)        | _         | 50  | _      | 43  | _      | 32  | ns   |

| DSACKx# Asserted to DSACKx# Valid (DSACK# Asserted Skew)      | 31A (3)       | _         | 15  | _      | 10  | _      | 10  | ns   |

| RESET# Input Transition Time                                  | 32            | _         | 1.5 | _      | 1.5 | _      | 1.5 | Clks |

| Clock Low to BG# Asserted                                     | 33            | 0         | 30  | 0      | 25  | 0      | 20  | ns   |

| Clock Low to BG# Negated                                      | 34            | 0         | 30  | 0      | 25  | 0      | 20  | ns   |

| BR# Asserted to BG# Asserted (RMC# Not Asserted)              | 35            | 1.5       | 3.5 | 1.5    | 3.5 | 1.5    | 3.5 | Clks |

| BGACK# Asserted to BG# Negated                                | 37            | 1.5       | 3.5 | 1.5    | 3.5 | 1.5    | 3.5 | Clks |

www.DataShei

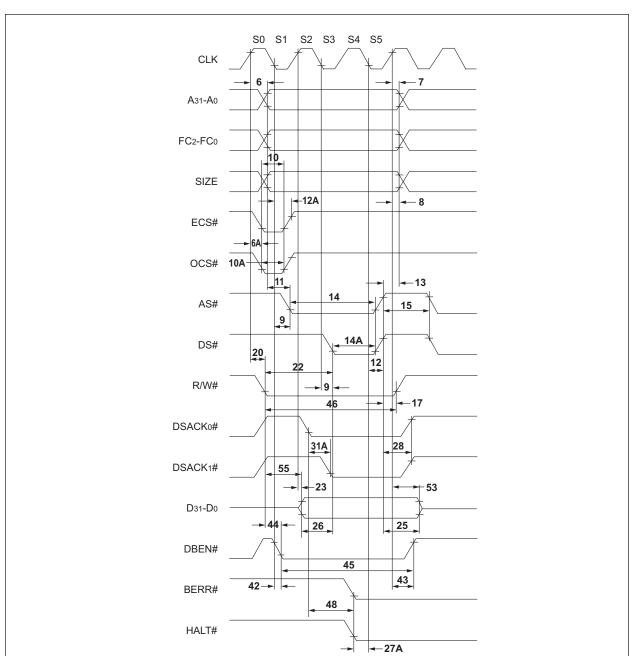

# AC ELECTRICAL SPECIFICATIONS - READ AND WRITE CYCLES (CONT'D)

| Characteristic                            | Specification | 16.67 MHz |     | 20 MHz |     | 25MHz |     | Unit |

|-------------------------------------------|---------------|-----------|-----|--------|-----|-------|-----|------|

|                                           |               | Min       | Max | Min    | Max | Min   | Max |      |

| BGACK# Asserted to BR# Negated            | 37A (6)       | 0         | 1.5 | 0      | 1.5 | 0     | 1.5 | Clks |

| BG Width Negated                          | 39            | 90        | _   | 75     | _   | 60    | _   | ns   |

| BG# Width Asserted                        | 39A           | 90        | _   | 75     | _   | 60    | _   | ns   |

| Clock High to DBEN# Asserted (Read)       | 40            | 0         | 30  | 0      | 25  | 0     | 20  | ns   |

| Clock High to DBEN# Negated (Read)        | 41            | 0         | 30  | 0      | 25  | 0     | 20  | ns   |

| Clock High to DBEN# Asserted (Write)      | 42            | 0         | 30  | 0      | 25  | 0     | 20  | ns   |

| Clock High to DBEN# Negated (Write)       | 43            | 0         | 30  | 0      | 25  | 0     | 20  | ns   |

| R/W# Low to DBEN# Asserted (Write)        | 44            | 15        | _   | 10     | _   | 10    | _   | ns   |

| DBEN# Width Asserted Read                 | 45 (5)        | 60        | _   | 50     | _   | 40    | _   | ns   |

| Write                                     |               | 120       | _   | 100    | _   | 80    | _   |      |

| R/W# Width Valid (Write or Read)          | 46            | 150       | -   | 125    | -   | 100   | -   | ns   |

| Asynchronous Input Setup Time             | 47A           | 5         | -   | 5      | -   | 5     | -   | ns   |

| Asynchronous Input Hold Time              | 47B           | 15        | _   | 15     | _   | 10    | _   | ns   |

| DSACKx# Asserted to BERR#, HALT# Asserted | 48 (4)        | _         | 30  | _      | 20  | _     | 18  | ns   |

| Data Out Hold from Clock High             | 53            | 0         | _   | 0      | _   | 0     | _   | ns   |

| R/W# Valid to Data Bus Impedance Change   | 55            | 30        | _   | 25     | _   | 20    | _   | ns   |

| RESET# Pulse Width (Reset Instruction)    | 56            | 512       | _   | 512    | _   | 512   | _   | Clks |

| BERR# Negated to HALT# Negated (Rerun)    | 57            | 0         | _   | 0      | -   | 0     | -   | ns   |

| BGACK# Negated to Bus Driven              | 58 (10)       | 1         | _   | 1      | -   | 1     | -   | Clks |

| BG# Negated to Bus Driven                 | 59 (10)       | 1         | _   | 1      | _   | 1     | _   | Clks |

#### NOTES:

- 1. This number can be reduced to 5ns if strobes have equal loads.

- If the asynchronous setup time (#47A) requirements are satisfied, the DSACKx#

low data setup time (#31) and DSACKx# low to BERR# low setup time (#48) can be

ignored. The data must only satisfy the data-in to clock low setup time (#27) for the

following clock cycle, and BERR# must only satisfy the late BERR low to clock low

setup time (#27A) for the following clock cycle.

- This parameter specifies the maximum allowable skew between DSACK0# to DSACK1# asserted or DSACK1# to DSACK0# asserted; specification #47A must be met by DSACK0# or DSACK1#.

- This specification applies to the first (DSACK0# or DSACK1#) DSACKx# signal asserted. In the absence of DSACKx#, BERR# is an asynchronous input setup time (347A).

- 5. DBEN# may stay asserted on consecutive write cycles.

- The minimum values must be met to guarantee proper operation. If this maximum value is exceeded, BG may be reasserted.

- This specification indicates the minimum high time for ECS# and OCS# in the event of an internal cache hit followed immediately by a cache miss or operand cycle.

- This specification guarantees operation with the 68881/68882, which specifies a

minimum time for DS# negated to AS# asserted. Without this specification, incorrect

interpretation of specifications #9A and #15 would indicate that the WC32P020-XXM

does not meet the 68881/68882 requirements.

- This specification allows a system designer to guarantee data hold times on the output side of data buffers that have output enable signals generated with DBEN#.

- 10. These specifications allow system designers to guarantee that an alternate bus master has stopped driving the bus when the 68020 regains control of the bus after an arbitration sequence.

- 11. This specification allows system designers to qualify the CS# signal of an 68881/68882 with AS# (allowing 7 ns for a gate delay) and still meet the CS# to DS# setup time requirement.

#### FIGURE 6 - READ CYCLE TIMING DIAGRAM

NOTE: Timing measurements are referenced to and from a low 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

www.DataSheet4U.com

ectronic Designs Corp. reserves the right to change products or specifications without notice.

#### FIGURE 7 - WRITE CYCLE TIMING DIAGRAM

NOTE: Timing measurements are referenced to and from a low 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

www.DataSheet4U.com

ectronic Designs Corp. reserves the right to change products or specifications without notice.

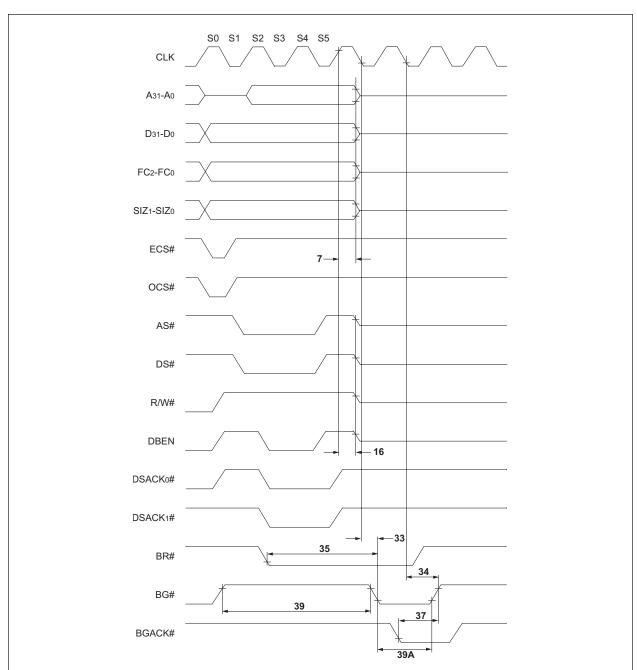

#### FIGURE 8 - BUS ARBITRATION TIMING DIAGRAM

NOTE: Timing measurements are referenced to and from a low 0.8V and a high voltage of 2.0V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be linear between 0.8V and 2.0V.

www.DataSheet4U.com

c Designs Corp. reserves the right to change products or specifications without notice.

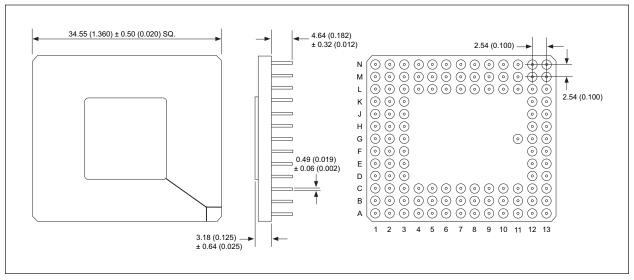

### FIGURE 9 114 PIN GRID ARRAY, PGA (P2)

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

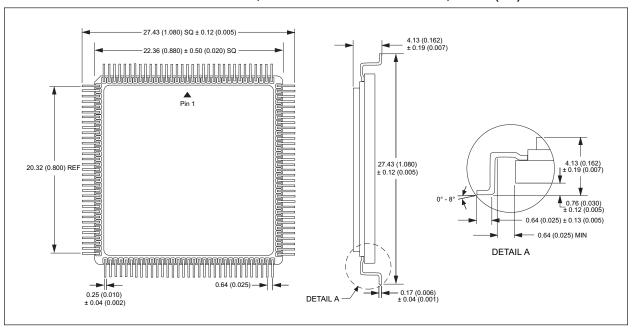

# FIGURE 10 – 132 LEAD, CERAMIC QUAD FLAT PACK, CQFP (Q2)

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

www.DataSheet4U.com

ctronic Designs Corp. reserves the right to change products or specifications without notice.

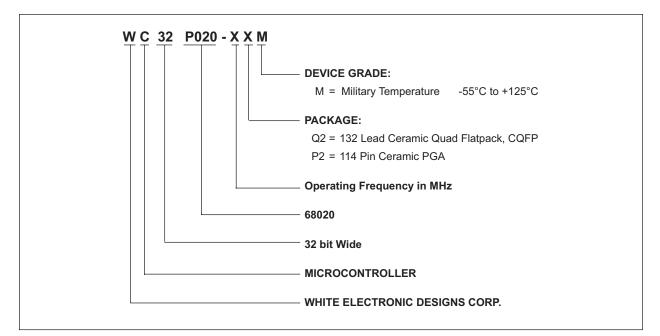

#### ORDERING INFORMATION