3.125Gb/s CML Limiting Amplifier with LOS Detect

#### **Features**

- 3.3V or 5V Power Supply

- Typical Supply Current of 32mA

- Current-Mode Logic Outputs

- Optional Output Squelch

- Loss of Signal Detect

- Output Offset Correction

- Rise/Fall Times Faster than 100ps

- Packages: TSSOP-16, Bare Die

## **Applications**

- SONET/SDH at 622Mb/s, 1.244Gb/s, 2.488Gb/s, and 3.125Gb/s

- Full-Speed Fibre Channel (1.062Gb/s)

- Small Form Factor (SFF) Receivers

- ATM Optical Receivers

### General Description

The VSC7959 is a single supply limiting amplifier with Loss of Signal (LOS) detect for SONET/SDH and Fibre Channel applications up to 3.125Gb/s. The VSC7959 provides a constant output signal swing for a wide range of input voltages and has Current-Mode Logic (CML) outputs. The VSC7961 provides the same functionality as the VSC7959 with positive emitter-coupled logic (PECL) outputs. Key features of the VSC7959 are its RMS power detectors for programmable LOS detection, optional output squelch, adjustable output levels, excellent jitter performance, and fast edge rates. The VSC7959 is available in die form or in a TSSOP-16 package.

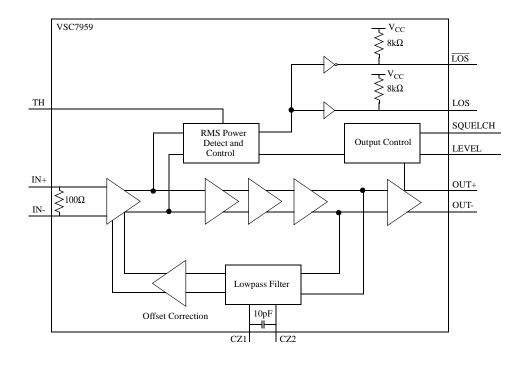

## **Block Diagram**

### 3.125Gb/s CML Limiting Amplifier with LOS Detect

### **Electrical Characteristics**

**Table 1: DC Specifications**

| Symbol            | Parameter                           | Min   | Тур | Max | Units | Conditions      |

|-------------------|-------------------------------------|-------|-----|-----|-------|-----------------|

| V <sub>CC</sub>   | Power Supply Voltage                | 3.135 |     | 5.5 | V     |                 |

| T                 | Power Supply Current <sup>(1)</sup> |       | 31  |     | mA    | $V_{CC} = 3.3V$ |

| $I_{CC}$          | Tower Supply Current                |       | 35  |     | mA    | $V_{CC} = 5V$   |

| I <sub>EE</sub>   | Power Supply Current <sup>(1)</sup> |       | 38  |     | mA    | $V_{CC} = 3.3V$ |

|                   | Tower Supply Current                |       | 43  |     | mA    | $V_{CC} = 5V$   |

| т                 | Power Supply Current when           |       | 21  |     | mA    | $V_{CC} = 3.3V$ |

| $I_{CCSQ}$        | Squelched (1)                       |       | 25  |     | mA    | $V_{CC} = 5V$   |

| т                 | Power Supply Current when           |       | 24  |     | mA    | $V_{CC} = 3.3V$ |

| I <sub>EESQ</sub> | Squelched (1)                       |       | 28  |     | mA    | $V_{CC} = 5V$   |

| $I_{SQ}$          | Squelch Input Current               | 0     |     | 400 | μΑ    |                 |

| PSSR              | Power Supply Rejection Ratio        | 20    | 30  |     | dB    | f < 2MHz        |

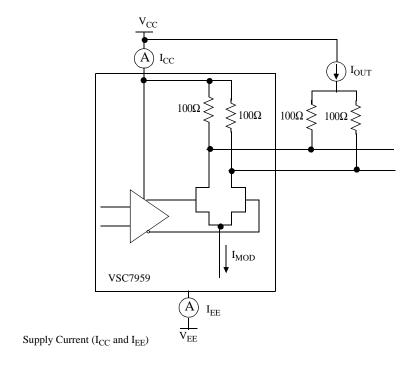

NOTE: (1) See Figure 5 for supply current measurement setup.

#### **Table 2: DC Specifications**

| Symbol            | Parameter                     | Min   | Тур | Max  | Units | Conditions                     |

|-------------------|-------------------------------|-------|-----|------|-------|--------------------------------|

|                   | Data Rate                     | 3.125 |     |      | Gb/s  |                                |

| V <sub>IN</sub>   | Input Voltage Range           | 10    |     | 1200 | mV    | Peak-to-peak                   |

| $J_{\mathrm{D}}$  | Deterministic Jitter          |       |     | 25   | ps    | See Note 1                     |

| $J_R$             | Random Jitter                 |       |     | 8    | ps    | See Note 2, RMS                |

| $t_{R,t_F}$       | Rise and Fall Times           |       | 55  | 100  | ps    | 20% to 80%                     |

| V <sub>N</sub>    | Input Referred Noise          |       |     | 230  | μV    | RMS, IN+ to IN-                |

| R <sub>DIFF</sub> | Differential Input Resistance |       | 100 |      | Ω     | IN+ to IN-                     |

| $f_L$             | Low Frequency Cutoff          |       | 2   |      | MHz   | C <sub>Z</sub> open            |

|                   | Low Frequency Cutoff          |       | 2   |      | kHz   | $C_Z = 0.1 \mu F$              |

| $V_{SQ}$          | Output Signal When Squelched  |       |     | 20   | mV    | Output AC-coupled              |

|                   |                               | 550   |     | 1200 | mV    | Level = open, $R_L = 50\Omega$ |

| $V_{CML}$         | CML Output Voltage            | 1100  |     | 1800 | mV    | Level = GND, $R_L = 75\Omega$  |

|                   |                               |       |     | 20   | mV    | Squelched                      |

| Z <sub>O</sub>    | Output Resistance             |       | 100 |      | Ω     | Single-ended                   |

$NOTES: (1)\ Deterministic\ jitter\ measured\ peak-to-peak\ with\ K28.5\ pattern.\ (2)\ Random\ jitter\ measured\ with\ minimum\ input.$

### 3.125Gb/s CML Limiting Amplifier with LOS Detect

#### **Table 3: Loss of Signal Specifications**

| Symbol            | Parameter                | Min  | Тур   | Max  | Units | Conditions                            |

|-------------------|--------------------------|------|-------|------|-------|---------------------------------------|

| H <sub>LOS</sub>  | LOS Hystersis            | 3.1  | 3.3   | 5.5  | dB    | $H_{LOS} = 20 \log (V_{THD}/V_{THA})$ |

| I <sub>LOS</sub>  | LOS Assert/Deassert Time | 0.22 | 0.25  | 0.28 | μs    |                                       |

|                   |                          |      | 8.2   |      | mV    | $R_{TH} = 2.5k\Omega$                 |

| $V_{THA}$         | LOS Assert Threshold     | 12.8 | 19.8  | 21.8 | mV    | $R_{TH} = 7k\Omega$                   |

|                   |                          |      | 57.2  |      | mV    | $R_{TH} = 20k\Omega$                  |

|                   |                          |      | 11.4  |      | mV    | $R_{TH} = 2.5k\Omega$                 |

| $V_{THD}$         | LOS Deassert Threshold   | 26.2 | 29.0  | 31.6 | mV    | $R_{TH} = 7k\Omega$                   |

|                   |                          |      | 75.2  |      | mV    | $R_{TH} = 20k\Omega$                  |

| V <sub>LOSH</sub> | LOS Output HIGH Voltage  | 3.3  |       |      | V     | $I_{LOS} = -30\mu A$                  |

| V <sub>LOSL</sub> | LOS Output LOW Voltage   |      | 0.168 |      | V     | $I_{LOS} = +1.2\mu A$                 |

#### **Table 4: Loss of Signal Truth Table**

| SQUELCH | LOS  | Output |

|---------|------|--------|

| High    | Low  | Off    |

| Low     | High | On     |

| High    | Low  | On     |

| Low     | Low  | On     |

## Absolute Maximum Ratings(1)

| Power Supply Voltage (V <sub>CC</sub> )     | 0.5V to +6V    |

|---------------------------------------------|----------------|

| Maximum Junction Temperature Range          | TBD            |

| Storage Temperature Range (T <sub>S</sub> ) | 55°C to +150°C |

NOTE: (1) CAUTION: Stresses listed under "Absolute Maximum Ratings" may be applied to devices one at a time without causing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| Positive Voltage Rail (V <sub>CC</sub> )     | 3.3V or 5V     |

|----------------------------------------------|----------------|

| Junction Temperature Range (T <sub>J</sub> ) | 40°C to +100°C |

| Ambient Temperature Range $(T_{\Delta})$     | 40°C to +85°C  |

## 3.125Gb/s CML Limiting Amplifier with LOS Detect

## Package Pin Descriptions

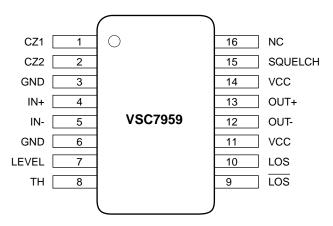

Figure 1: Pin Diagram

Top View TSSOP-16 Package

**Table 5: Pin Identifications**

| Pin Name | Pin No. | Description                                                                                                                                                                                                                     |  |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CZ1      | 1       | Offset Correction Loop Capacitor. Place capacitor between this pin and CZ2 to alter time constant of offset correction loop. See <i>Detailed Description</i> section.                                                           |  |

| CZ2      | 2       | Offset Correction Loop Capacitor. Place capacitor between this pin and CZ1 to alter time constant of offset correction loop. See <i>Detailed Description</i> section.                                                           |  |

| GND      | 3       | Supply Ground                                                                                                                                                                                                                   |  |

| IN+      | 4       | Noninverted Input Signal                                                                                                                                                                                                        |  |

| IN-      | 5       | Inverted Input Signal                                                                                                                                                                                                           |  |

| GND      | 6       | Supply Ground                                                                                                                                                                                                                   |  |

| LEVEL    | 7       | Output Current Level. This pin may either be connected to ground or left unconnected. Connecting to ground causes output current to be 20mA. The output is 16mA when left unconnected. See <i>Detailed Description</i> section. |  |

| TH       | 8       | Loss of Signal (LOS) Threshold. Connect a resistor from this pin to ground to set the input signal level at which LOS outputs will be asserted. See <i>Application Information</i> section.                                     |  |

| LOS      | 9       | Inverted Loss of Signal Output. LOS is HIGH for input signals above the threshold programmed by TH. See <i>Detailed Description</i> section.                                                                                    |  |

| LOS      | 10      | Noninverted Loss of Signal Output. LOS is LOW for input signals above the threshold programmed by TH. See <i>Detailed Description</i> section.                                                                                  |  |

| VCC      | 11      | Power Supply                                                                                                                                                                                                                    |  |

| OUT-     | 12      | Inverted Data Output                                                                                                                                                                                                            |  |

| OUT+     | 13      | Noninverted Data Output                                                                                                                                                                                                         |  |

| VCC      | 14      | Power Supply                                                                                                                                                                                                                    |  |

| SQUELCH  | 15      | Squelch Input. Squelch is disabled if this pin is unconnected or set LOW. When SQUELCH is HIGH, OUT+ and OUT- are forced to static levels.                                                                                      |  |

| NC       | 16      | No Connection                                                                                                                                                                                                                   |  |

3.125Gb/s CML Limiting Amplifier with LOS Detect

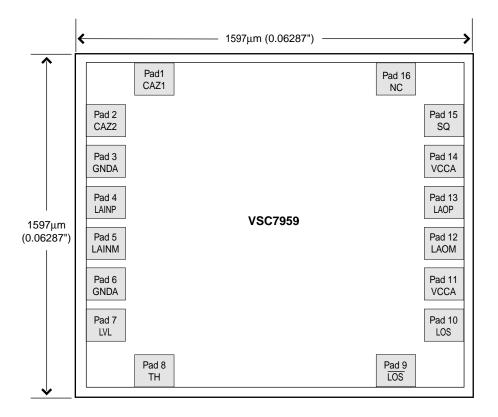

## **Bare Die Descriptions**

Figure 2: Pad Assignments

Die Size:  $1597\mu m\ x\ 1597\mu m\ (0.06287"\ x\ 0.06287")$

Pad Pitch: 180μm (0.00709")

Pad Passivation Opening: 95μm x 95μm (0.00374" x 0.00374")

The back side of the die may either be left floating or connected ot ground.

## 3.125Gb/s CML Limiting Amplifier with LOS Detect

#### **Table 6: Pad Coordinates**

| Pad   | Pin Name | Pad/Pin | Coordinates (µm) |          | Description                                                                                                                                                                                                                     |  |

|-------|----------|---------|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name  | Fin Name | Number  | X                | Y        | - Description                                                                                                                                                                                                                   |  |

| CZ1   | CZ1      | 1       | 270.525          | 1359.05  | Offset Correction Loop Capacitor. Place capacitor between this pin and CZ2 to alter time constant of offset correction loop. See <i>Detailed Description</i> section.                                                           |  |

| CZ2   | CZ2      | 2       | 80.95            | 1170.525 | Offset Correction Loop Capacitor. Place capacitor between this pin and CZ1 to alter time constant of offset correction loop. See <i>Detailed Description</i> section.                                                           |  |

| GNDA  | GND      | 3       | 80.95            | 990.525  | Supply Ground                                                                                                                                                                                                                   |  |

| LAINP | IN+      | 4       | 80.95            | 810.525  | Noninverted Input Signal                                                                                                                                                                                                        |  |

| LAINM | IN-      | 5       | 80.95            | 630.525  | Inverted Input Signal                                                                                                                                                                                                           |  |

| GNDA  | GND      | 6       | 80.95            | 450.525  | Supply Ground                                                                                                                                                                                                                   |  |

| LVL   | LEVEL    | 7       | 80.95            | 270.525  | Output Current Level. This pin may either be connected to ground or left unconnected. Connecting to ground causes output current to be 20mA. The output is 16mA when left unconnected. See <i>Detailed Description</i> section. |  |

| тн    | ТН       | 8       | 270.525          | 80.95    | Loss of Signal (LOS) Threshold. Connect a resistor from this pin to ground to set the input signal level at which LOS outputs will be asserted. See <i>Application Information</i> section.                                     |  |

| LOS   | LOS      | 9       | 1169.475         | 80.95    | Inverted Loss of Signal Output. LOS is HIGH for input signals above the threshold programmed by TH. See <i>Detailed Description</i> section.                                                                                    |  |

| LOS   | LOS      | 10      | 1359.05          | 270.525  | Noninverted Loss of Signal Output. LOS is LOW for input signals above the threshold programmed by TH. See <i>Detailed Description</i> section.                                                                                  |  |

| VCCA  | VCC      | 11      | 1359.05          | 450.525  | Power Supply                                                                                                                                                                                                                    |  |

| LOAM  | OUT-     | 12      | 1359.05          | 630.525  | Inverted Data Output                                                                                                                                                                                                            |  |

| LAOP  | OUT+     | 13      | 1359.05          | 810.525  | Noninverted Data Output                                                                                                                                                                                                         |  |

| VCCA  | VCC      | 14      | 1359.05          | 990.525  | Power Supply                                                                                                                                                                                                                    |  |

| SQ    | SQUELCH  | 15      | 1359.05          | 1170.525 | Squelch Input. Squelch is disabled if this pin is unconnected or set LOW. When SQUELCH is HIGH, OUT+ and OUT- are forced to static levels.                                                                                      |  |

| _     | NC       | —/16    | 1169.475         | 1359.05  | No Connection                                                                                                                                                                                                                   |  |

3.125Gb/s CML Limiting Amplifier with LOS Detect

### **Detailed Description**

The VSC7959 is a high speed limiting amplifier with Loss-of-Signal (LOS) detect. The device is designed to operate with a 3.3V or 5V supply in SDH/SONET and Fibre Channel applications up to 3.125Gb/s. The VSC7959 has current-mode logic (CML) outputs. The VSC7961 provides the same functionality as the VSC7959 with positive emitter-coupled logic (PECL) outputs. The key features of the VSC7959 are Loss-of-Signal (LOS) detect, output offset correction, output squelch, adjustable output levels, low power supply current, and fast rise and fall times.

The inputs of the device provide  $100\Omega$  input impedance between IN+ and IN- and are intended to be DC-coupled. The CML output circuits are designed to tolerate output impedance mismatches and may be AC- or DC-coupled.

#### Loss of Signal (LOS) Detect

This features utilizes an RMS power detector with programmable LOS indicator to provide two outputs, LOS and  $\overline{\text{LOS}}$ . The input TH is used to set the threshold at which the loss of signal detector outputs, LOS and  $\overline{\text{LOS}}$ , change state. See the Loss of Signal Specifications (Table 3) for setting the resistor value between TH and ground. The Loss of Signal Truth Table (Table 4) clarifies how LOS and SQUELCH interact.

#### **Optional Squelch**

Squelch is disabled when SQUELCH is not connected or is set to TTL low level. When SQUELCH is set to TTL high level and LOS is asserted, the data outputs, OUT+ and OUT- are forced to static levels. If LOS is not asserted, the outputs will not be squelched.

#### **Offset Correction**

This feature is provided to ensure that the offsets in the limiting amplifier coupled with its gain do not cause the output buffer to give a false output. Because of the high gain of the amplifier, offset correction using a low-frequency feedback loop reduces input offset. If no component is placed between pins CZ1 and CZ2, the low frequency cut-off is 2MHz. If a  $0.1\mu F$  capacitor is placed between CZ1 and CZ2, the low frequency cut-off is lowered to about 2kHz. For Fibre Channel and Gigabit Ethernet applications, leave pins CZ1 and CZ2 open. For ATM/SONET and other scrambled non-return-to-zero (NRZ) applications, place a  $0.1\mu F$  capacitor between CZ1 and CZ2. This maintains a one-decade separation between the lowest input frequency and the low frequency cut-off. The low frequency cut-off of the offset correction loop is given by the following equation:

$$\begin{split} f_{OC} &= 43 / \left[ 2\pi * 35k \left( C_Z + 100pF \right) \right] \\ &= 196 \bullet 10^{-6} / \left( C_Z + 100pF \right) \\ &= 196 \bullet 10^{-6} / \left( 0.1 \mu F + 100pF \right) \\ &= 1.96 kHz \end{split}$$

### 3.125Gb/s CML Limiting Amplifier with LOS Detect

#### **Output Level Control**

The LEVEL pin adjusts the output levels to 20mA when grounded and to 16mA when left unconnected.

**Figure 3: Supply Current Measurement**

## Applications Information

#### **Wire Bonding**

For best performance, gold ball-bonding techniques are recommended. To minimize inductance, keep wire bond lengths short.

## **PCB Layout Guidelines**

Use high frequency PCB layout techniques with solid ground planes to minimize crosstalk and EMI. Keep high speed traces as short as possible for signal integrity. Short input and output traces will provide best performance.

3.125Gb/s CML Limiting Amplifier with LOS Detect

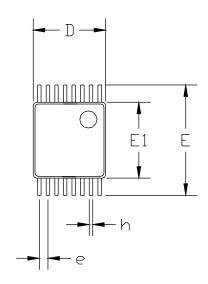

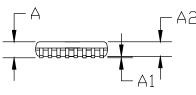

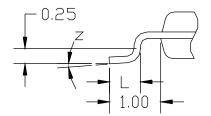

## Package Information

#### TSSOP-16

| ALL DIMENSIONS IN MILLIMETERS |                                  |                                                                                                                     |  |  |  |  |

|-------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TSSOP                         |                                  |                                                                                                                     |  |  |  |  |

| MIN.                          | N□M.                             | MAX.                                                                                                                |  |  |  |  |

| **                            | **                               | 1.10                                                                                                                |  |  |  |  |

| 0.05                          | ×                                | 0.15                                                                                                                |  |  |  |  |

| 0.85 0.90                     |                                  | 0.95                                                                                                                |  |  |  |  |

| 5.00 BSC.                     |                                  |                                                                                                                     |  |  |  |  |

| 6.40 BSC.                     |                                  |                                                                                                                     |  |  |  |  |

| 4.30                          | 4.40                             | 4.50                                                                                                                |  |  |  |  |

| 0.50                          | 0.60                             | 0.70                                                                                                                |  |  |  |  |

| 0.65 BSC.                     |                                  |                                                                                                                     |  |  |  |  |

| 0.19                          | **                               | 0.30                                                                                                                |  |  |  |  |

| 0                             | ×                                | 8                                                                                                                   |  |  |  |  |

|                               | MIN.  0.05 0.85  4.30 0.50  0.19 | TSSUP  MIN. NUM.  → → → → →  0.05 → → →  0.85 0.90  5.00 BSC.  6.40 BSC.  4.30 4.40  0.50 0.60  0.65 BSC.  0.19 → → |  |  |  |  |

- 1. All dimensioning and tolerancing per ASME. Y14.5-1994

- 2. Controlling dimension: millimeter

- 3. This outline conforms to JEDEC Publication 95 Registration MS-026

### 3.125Gb/s CML Limiting Amplifier with LOS Detect

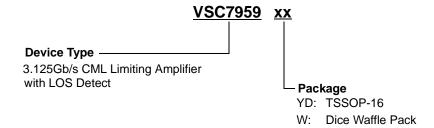

## **Ordering Information**

The order number for this product is formed by a combination of the device type and package type.

#### **Notice**

Vitesse Semiconductor Corporation ("Vitesse") provides this document for informational purposes only. This document contains pre-production information about Vitesse products in their concept, development and/or testing phase. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. Nothing contained in this document shall be construed as extending any warranty or promise, express or implied, that any Vitesse product will be available as described or will be suitable for or will accomplish any particular task.

Vitesse products are not intended for use in life support appliances, devices or systems. Use of a Vitesse product in such applications without written consent is prohibited.