## VS23S010C-L - 1 Megabit SPI SRAM with Serial and Parallel Interfaces and Integrated Video Display Controller

### **Features**

- Flexible 1.5V 3.6V operating voltage

- 131,072 x 8-bit SRAM organization

- Serial Peripheral Interface (SPI) mode 0 compatible

- Byte, Page and Sequential modes

- Supports Single, Dual and Quad I/O read and write

- Fast operation: the whole memory can be filled in 262158 or read in 262159 cycles (Quad-I/O SPI, Quad address mode)

- XHOLD and XWP pins

- 8-bit Parallel Interface (Simplified 8080 and NAND FLASH Type Interface)

- Sequential read and write in 4 byte blocks

- Fast operation, the whole memory can be filled or read in 131077 cycles

- Integrated Video Display Controller with Video DAC

- Supports NTSC and PAL video formats

- Fully configurable by user

- 9-bit Video DAC and 8x Video PLL

- High operating frequencies

- Up to 36 MHz for SPI

- Over 35 MHz for Video Display Controller

- 15 MHz for 8-bit parallel interface

- (TBD) MHz for SRAM writes when Video Display Controller enabled

- Active Low-power

- Read current 200  $\mu$ A at 1 MHz (Single I/O, SO=0, T<sub>A</sub>=+85°C, VDD=3.3V)

- Industrial temperature range

-40°C to + 85°C

- Pb-Free and RoHS compliant

## Description

The VLSI Solution VS23S010C-L is an easyto-use and versatile serial SRAM device. The memory is accessed via an SPI compatible serial bus. The device also contains Video Display Controller, which can be configured to continuously output analog video from the memory array data to implement a video frame buffer.

Alternatively, a 8-bit parallel interface can be used to access the SRAM instead of the SPI.

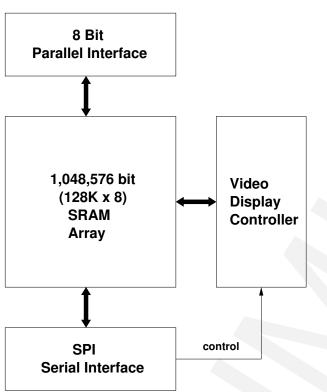

To sum up, there are four separate operating modes in VS23S010C-L:

- SPI Single, Dual, or Quad operation and 4 General Purpose I/O pins

- SPI Single, Dual, or Quad operation and simultaneous Video Display Controller

- 8-bit Parallel Interface operation

- 8-bit Parallel Interface operation and simultaneous Video Display Controller

## Applications

- Microcontroller RAM extension

- VoIP and internet data stream buffer

- Audio data buffer

- Video frame buffer

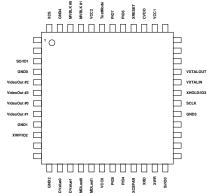

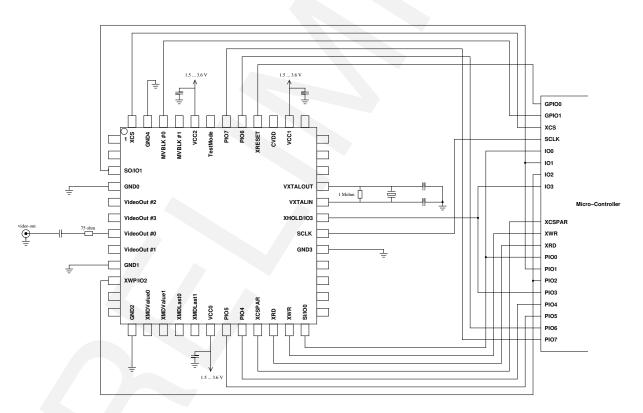

Figure 1: LQFP48 pin out (not to scale)

#### **Operating Modes**

VS23S010C-L operates in one of four modes: SPI, SPI and Video Display Controller, 8-bit parallel mode or 8-bit parallel mode and Video Display Controller.

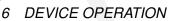

Figure 2: SPI or 8-bit parallel interface and Video Display Controller can be enabled at the same time.

In SPI mode SRAM and control registers can be accessed. Dual-I/O and Quad-I/O modes are used only for SRAM read and write.

When Video Display Controller is enabled SPI can be used simultaneously. There is an additional limit to maximum SPI access rate in this mode.

When 8-bit parallel interface is used to access SRAM, SPI must be inactive. Video Display Controller can be operational simultaneously. However, Video Display Controller can be controlled only by SPI. There is a limit to maximum access rate for 8-bit parallel interface when Video Display Controller is en-

#### abled.

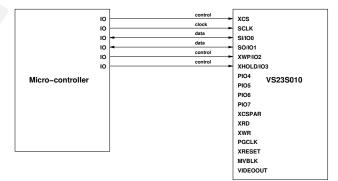

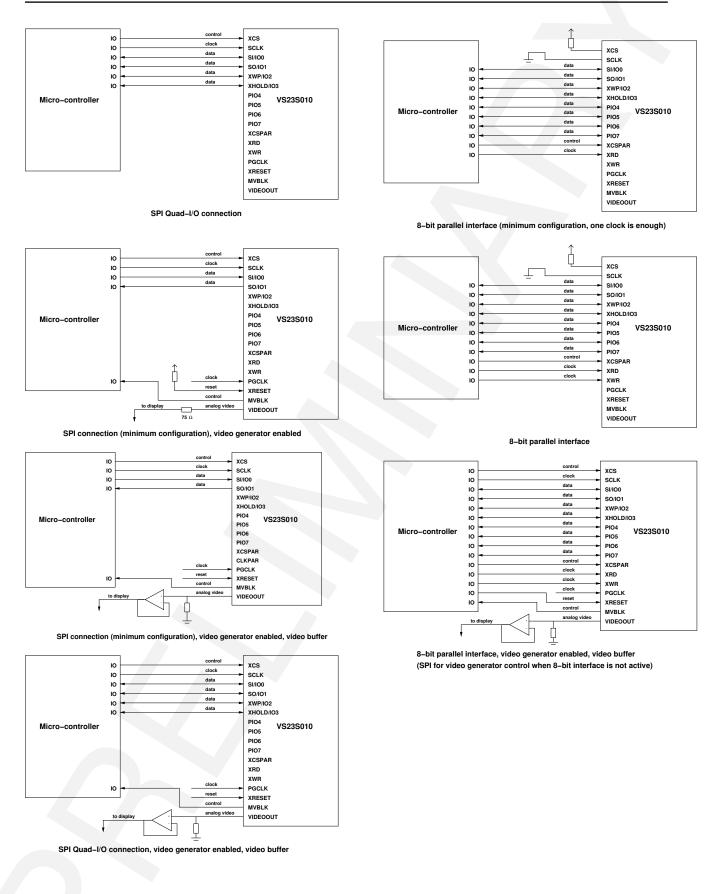

Following are connection examples for different operating modes. Some I/Os of VS23S010C-L are unconnected, because they have internal pull-up or pull-down resistors. Note also, that power and ground connections are not shown in the following examples.

#### SPI connection, basic configuration

SPI Dual-I/O connection

## Contents

| vs  | S23S010C                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Та  | ble of Con                                                                           | ntents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4                                                                                                                                                  |

| Lis | st of Figur                                                                          | res                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6                                                                                                                                                  |

| 1   | Disclaime                                                                            | er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                                                                  |

| 2   | Definitior                                                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8                                                                                                                                                  |

| 3   | 3.1 Abs<br>3.2 DC<br>3.3 AC<br>3<br>3<br>3<br>3.4 Cur<br>3<br>3<br>3.4 Cur<br>3<br>3 | I Characteristics & Specifications         solute Maximum Ratings         Characteristics         Characteristics         3.3.1 General         3.3.2 SPI Mode         3.3.3 Video Display Controller Mode         3.3.4 8-bit Parallel Interface Mode         8.4.1 SPI Mode         3.4.2 Video Display Controller Mode         3.4.3 8-bit Parallel Interface Mode                                                                                                                                                                                                                                                                                                                      | 9          10          10          11          14          15          16          16          17                                                  |

| 4   | 4.1 Nar                                                                              | s and Pin Descriptions<br>rrow SOIC8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                    |

| 5   | Connecti<br>5.1 Cor                                                                  | on Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>22</b><br>22                                                                                                                                    |

| 6   | 6<br>6<br>6.2 Vid<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6<br>6   | peration         1.1       Word, Page and Sequential Operation Modes         5.1.2       Dual-I/O and Quad-I/O Operation         5.1.3       Multi-IC Operation         6.1.3       Multi-IC Operation         6.1.4       Block General Description         6.2.1       Block General Description         6.2.2       Parameters of Video Display Controller         6.2.3       Memory Organization         6.2.4       8x PLL and Clock Switch         6.2.5       Color Modulator         6.2.6       Block Move         6.2.7       Direct DAC Mode         6.2.8       Operating The Video Display Controller         6.2.9       Video Example         8:1       Parallel Interface | 24          26          30          35          35          37          41          43          45          45          47          48          48 |

| 7   | 7.1 SPI                                                                              | mands and Addressing<br>I Read Commands (03h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                    |

|    | 7.2                                                                                                  | 7.2.1<br>7.2.2                                                                                                                                              | Quad-Output Read (6Bh and<br>Commands (02h)<br>Dual-Input Write (A2h and 2<br>Quad-Input Write (32h and 1<br>ellaneous Commands<br>Read Status Register (05h)<br>Write Status Register (01h)<br>Read Manufacturer and Dev<br>Read GPIO Control Register<br>Write GPIO Control Register<br>Read GPIO State Register (<br>Read Multi-IC Control Register<br>Write Multi-IC Control Register | 22h)    |  | 58<br>60<br>60<br>62                   |

|----|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|----------------------------------------|

| 8  | Video<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9<br>8.10<br>8.11<br>8.12<br>8.13 | Write Pict<br>Write Pict<br>Write Line<br>Write Vid<br>Write Pict<br>Write Vid<br>Write U T<br>Write U T<br>Write Pro<br>Read Cur<br>Write Blo<br>Write Blo | Controller Commands<br>ture Start (28h)<br>ture End (29h)<br>e Length (2Ah)<br>eo Display Controller Control<br>ture Index Start Address (2Ch<br>eo Display Controller Control<br>able (2Eh)<br>able (2Fh)<br>gram (30h)<br>crrent Line and PLL Lock (53h)<br>ck Move Control2 (35h)<br>ck Move (36h)                                                                                     | 1 (2Bh) |  | 72<br>74<br>76<br>77<br>78<br>79<br>80 |

| 9  | <b>8-Bit</b><br>9.1<br>9.2                                                                           | 8-Bit Para                                                                                                                                                  | allel Interface Commands and Ad                                                                                                                                                                                                                                                                                                                                                           |         |  |                                        |

| 10 | 10.1                                                                                                 |                                                                                                                                                             | Up                                                                                                                                                                                                                                                                                                                                                                                        |         |  | <b>88</b><br>88<br>88                  |

| 11 | Docu                                                                                                 | ment Vers                                                                                                                                                   | sion Changes                                                                                                                                                                                                                                                                                                                                                                              |         |  | 89                                     |

| 12 | Conta                                                                                                | act Inform                                                                                                                                                  | ation                                                                                                                                                                                                                                                                                                                                                                                     |         |  | 91                                     |

## List of Figures

| 1<br>2            | LQFP48 pin out (not to scale)                                                                 | 1  |

|-------------------|-----------------------------------------------------------------------------------------------|----|

| 2                 | SPI or 8-bit parallel interface and Video Display Controller can be enabled at the same time. | 2  |

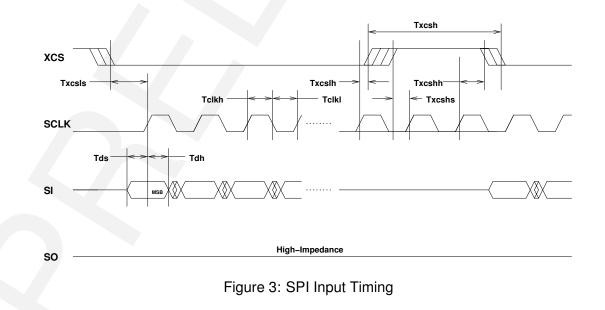

| 3                 | SPI Input Timing                                                                              |    |

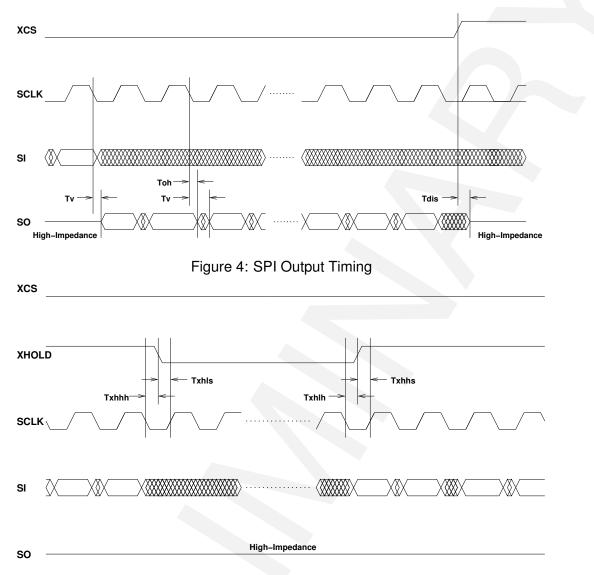

| 4                 | SPI Output Timing                                                                             |    |

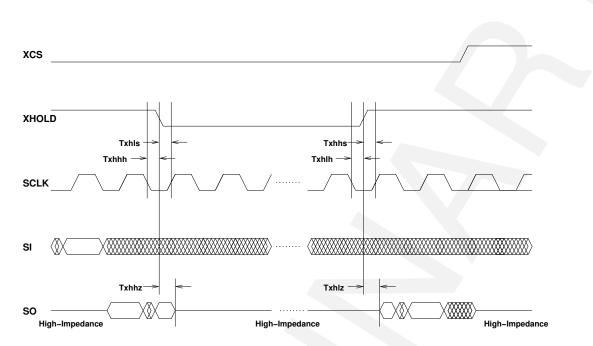

| <del>4</del><br>5 | XHOLD Timing, SPI and Dual-I/O Input Modes. Notice that internal address                      | 12 |

| 5                 | counter does not increment, when XHOLD is low.                                                | 12 |

| 6                 | XHOLD Timing, SPI and Dual-I/O Output Modes. Notice that internal address                     | 12 |

| 0                 | counter does not increment, when XHOLD is low.                                                | 13 |

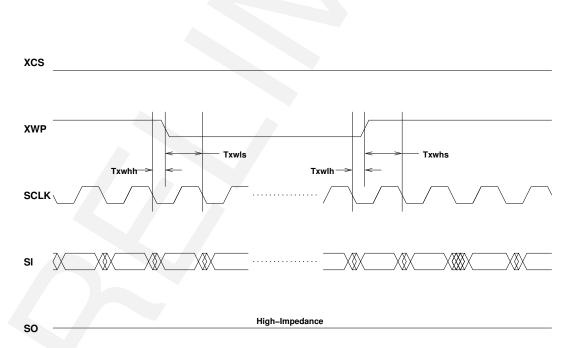

| 7                 | XWP Timing, SPI and Dual-I/O Modes. Notice that internal address counter                      | 15 |

| 1                 | increments, when XWP is low.                                                                  | 13 |

| 8                 | XRESET Timing                                                                                 |    |

| 9                 | 8-bit Parallel Interface Timing                                                               |    |

| 10                | SOIC8 narrow package, compatible with standard pin out (not to scale).                        |    |

| 11                | LQFP48 pin out (not to scale)                                                                 |    |

| 12                | Connection example                                                                            |    |

| 13                | Device Organization                                                                           |    |

| 14                | SPI Mode 0                                                                                    |    |

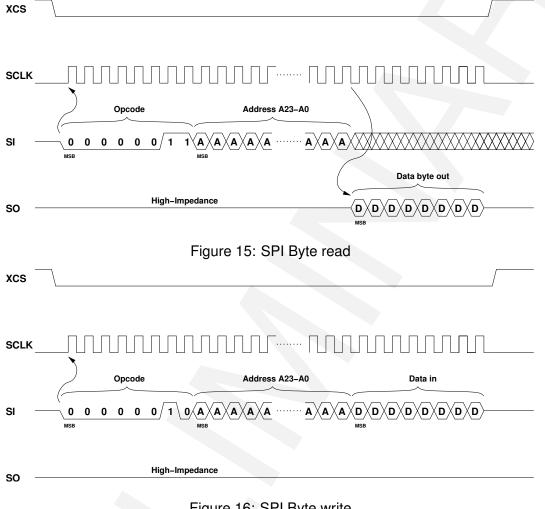

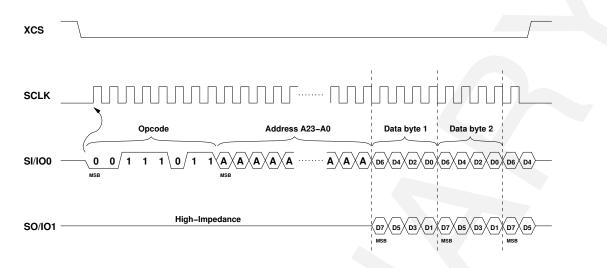

| 15                | SPI Byte read                                                                                 |    |

| 16                | SPI Byte write                                                                                |    |

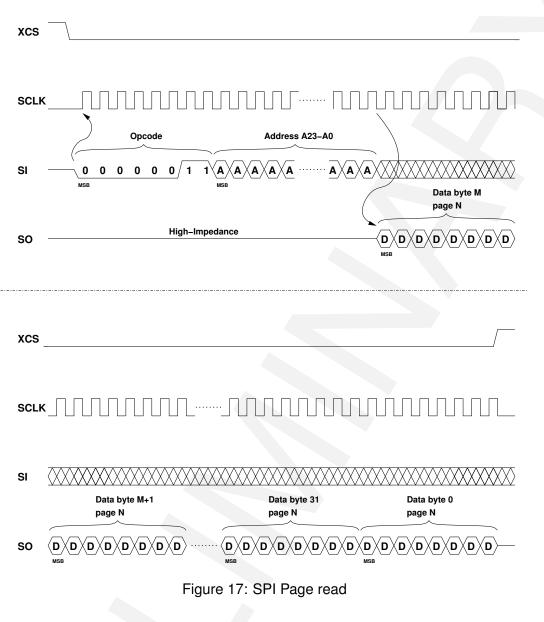

| 17                | SPI Page read                                                                                 |    |

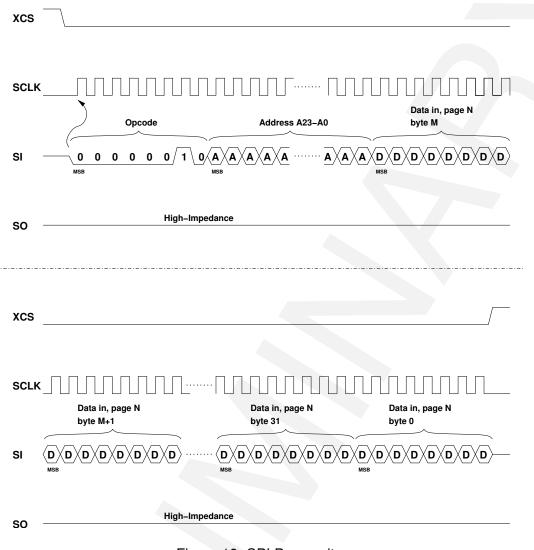

| 18                | SPI Page write                                                                                |    |

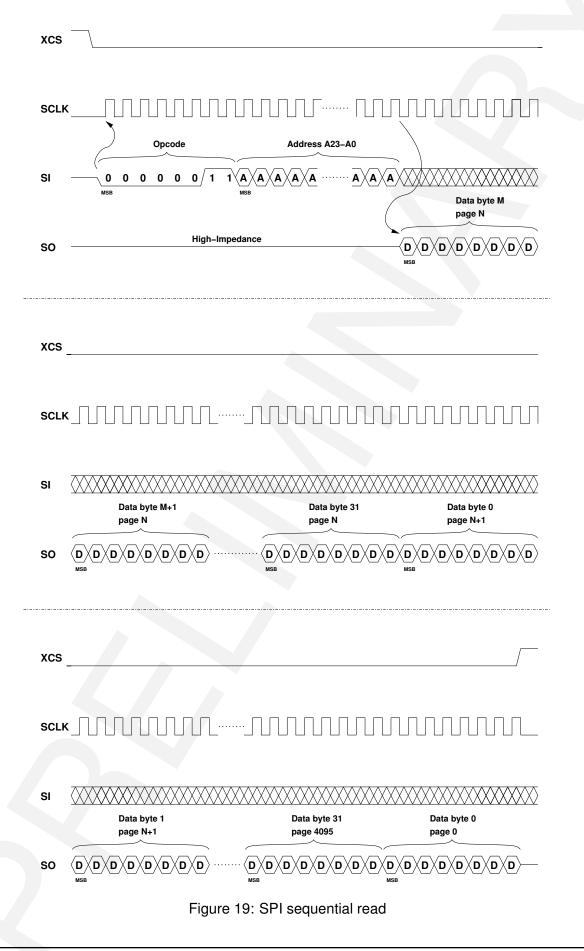

| 19                | SPI sequential read                                                                           |    |

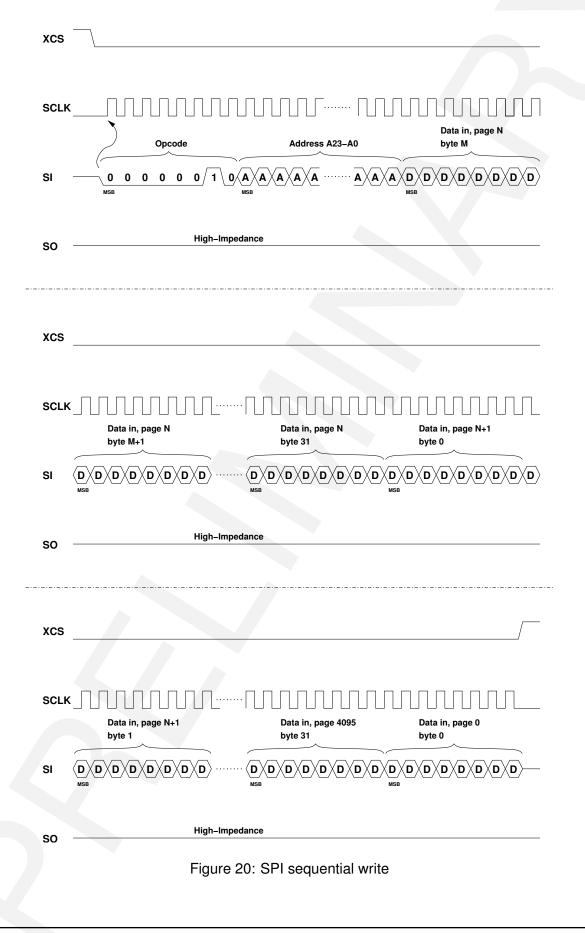

| 20                | SPI sequential write                                                                          |    |

| 21                | One VS23S010 operation                                                                        |    |

| 22                | Two VS23S010s operation                                                                       |    |

| 23                | Three VS23S010s operation                                                                     |    |

| 24                | Four VS23S010s operation                                                                      |    |

| 25                | SPI read in Multi-IC system consisting of four VS23S010C-Ls                                   |    |

| 26                | Video Display Controller block diagram                                                        |    |

| 27                | Video picture parameters                                                                      |    |

| 28                | Switchable low-pass Y filter                                                                  |    |

| 29                | Video mode SRAM organization                                                                  | 41 |

| 30                | Index address organization                                                                    | 42 |

| 31                | Protoline data organization, when whole line is protoline                                     | 43 |

| 32                | Protoline data organization for a picture line (Note that the starting address is             |    |

|                   | formed differently than in previous picture)                                                  | 43 |

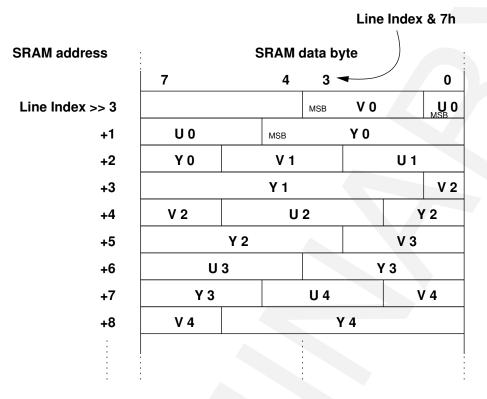

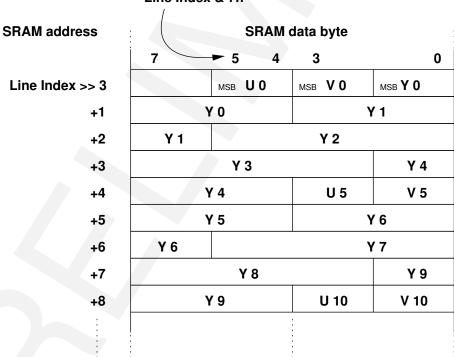

| 33                | Normal line data organization example                                                         | 44 |

| 34                | Normal line data organization example, UVSkip value 4                                         | 44 |

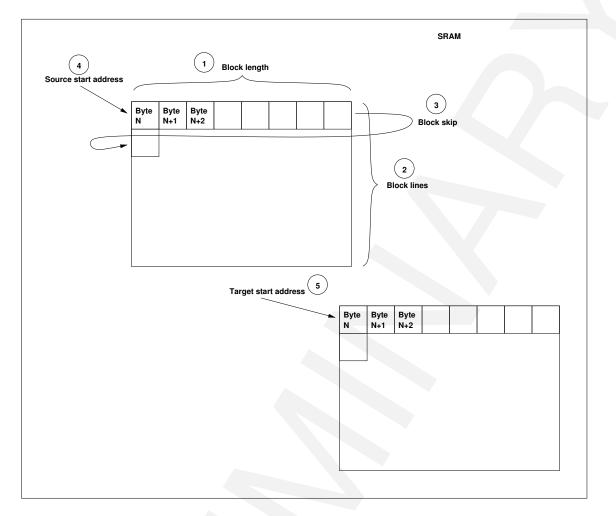

| 35                | Block move parameters                                                                         | 46 |

| 36                | Direct DAC data organization                                                                  | 47 |

| 37                | Timing of on-chip reset signal                                                                | 48 |

| 38                | Interlaced PAL video frame timing                                                             | 49 |

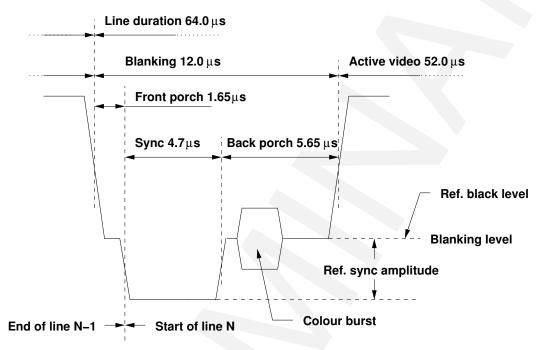

| 39                | PAL video line timing principle (timing tolerances not shown)                                 | 50 |

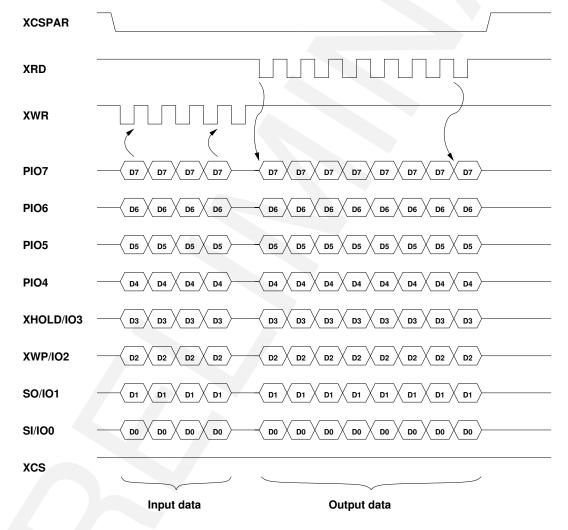

| 40                | Example of 8-Bit Parallel Interface Signals                                                   | 53 |

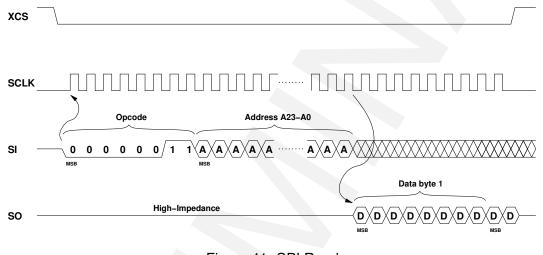

| 41                | SPI Read                                                                                      | 56 |

| 42                | SPI Dual-Output Read                                                                          |    |

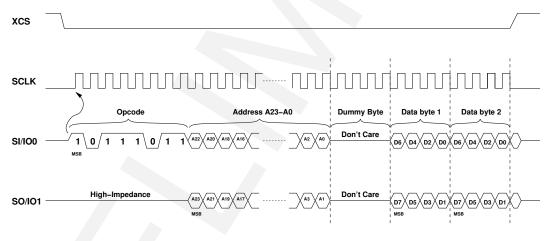

| 43                | SPI Dual-Output Read, Dual Address                                                            | 57 |

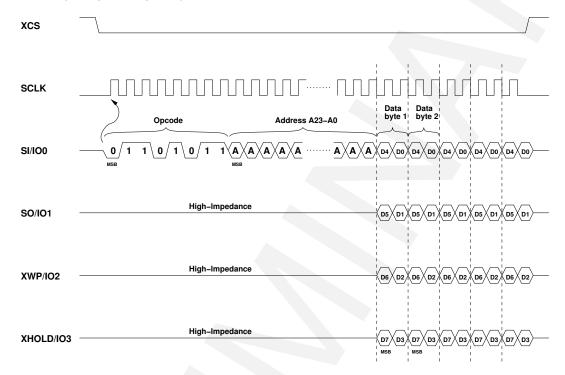

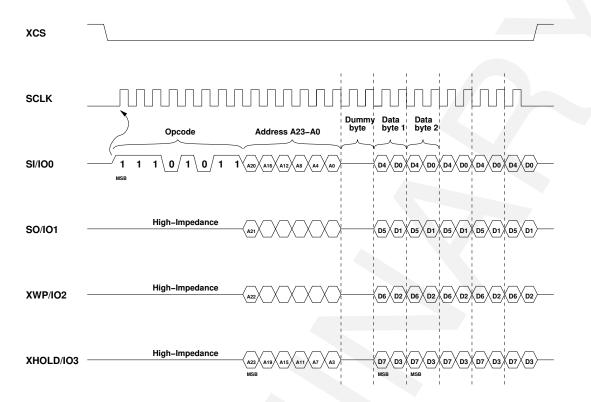

| 44<br>45<br>46<br>47 | SPI Quad-Output Read58SPI Quad-Output Read, Quad Address59SPI Write59SPI Dual-Input Write60 |

|----------------------|---------------------------------------------------------------------------------------------|

| 48                   | SPI Dual-Input, Dual Address Write                                                          |

| 49                   | SPI Quad-Input Write                                                                        |

| 50                   | SPI Quad-Input, Quad Address Write                                                          |

| 51                   | SPI Read Status Register                                                                    |

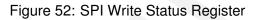

| 52                   | SPI Write Status Register                                                                   |

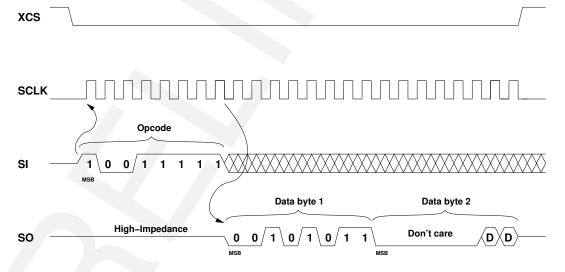

| 53                   | SPI Read Manufacturer and Device ID                                                         |

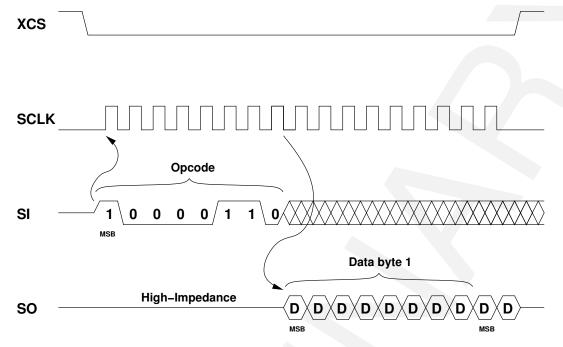

| 54                   | SPI Read GPIO Control                                                                       |

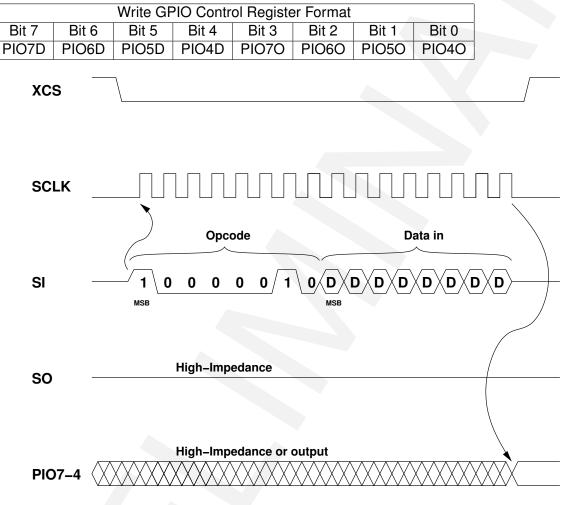

| 55                   | SPI Write GPIO Control                                                                      |

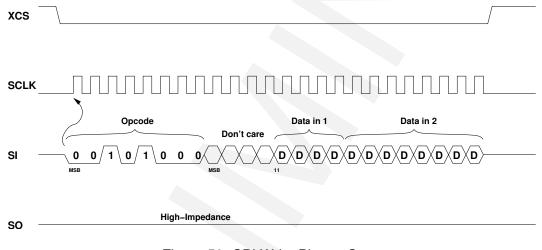

| 56                   | SPI Read GPIO State                                                                         |

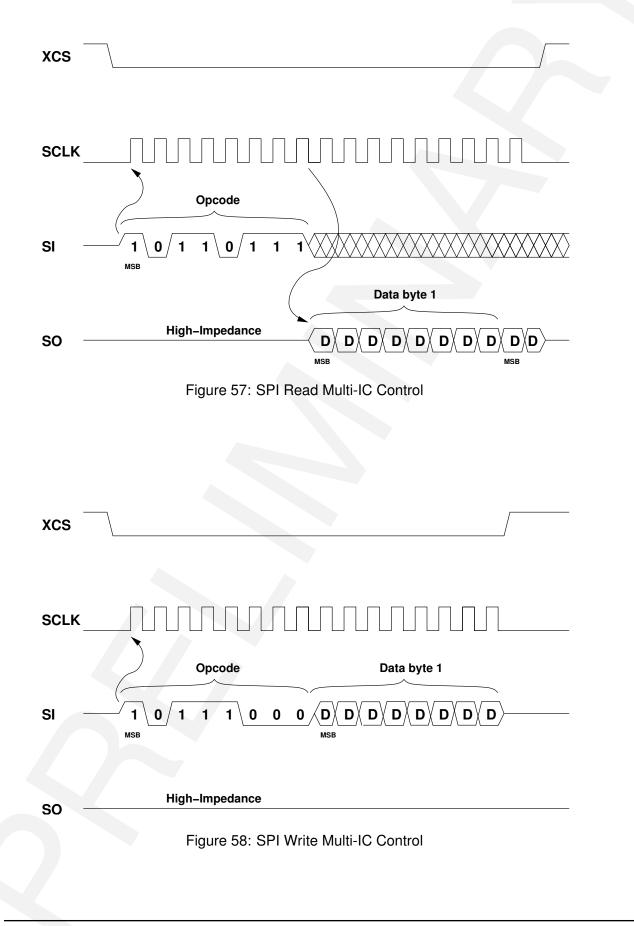

| 57                   | SPI Read Multi-IC Control                                                                   |

| 58                   | SPI Write Multi-IC Control                                                                  |

| 59                   | SPI Write Picture Start                                                                     |

| 60                   | SPI Write Picture End                                                                       |

| 61                   | SPI Write Line Length                                                                       |

| 62                   | SPI Write Video Display Controller Control1                                                 |

| 63                   | SPI Write Picture Index Start Address                                                       |

| 64                   | SPI Write Video Display Controller Control2                                                 |

| 65                   | SPI Write U Table                                                                           |

| 66                   | SPI Write V Table                                                                           |

| 67                   | SPI Write Program                                                                           |

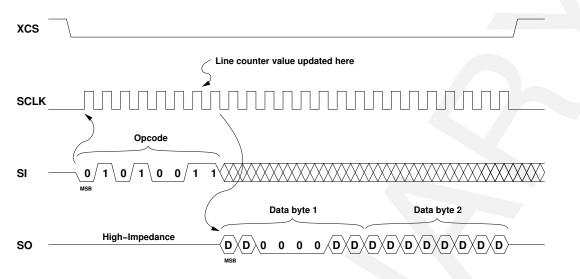

| 68                   | SPI Read Current Line and PLL Lock 80                                                       |

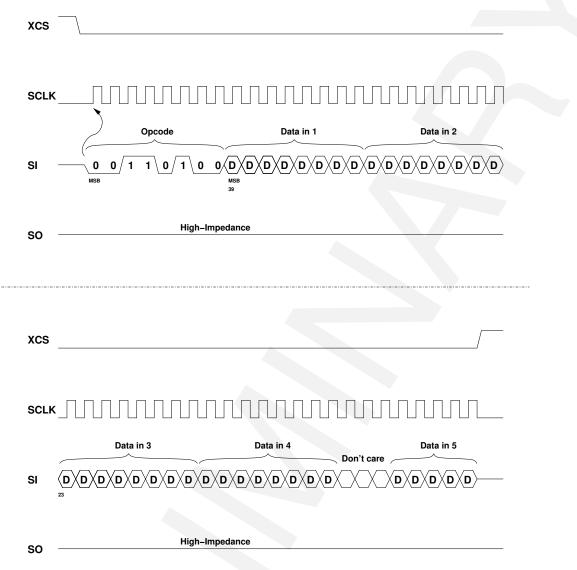

| 69                   | SPI Write Block Move Control1                                                               |

| 70                   | SPI Write Block Move Control2                                                               |

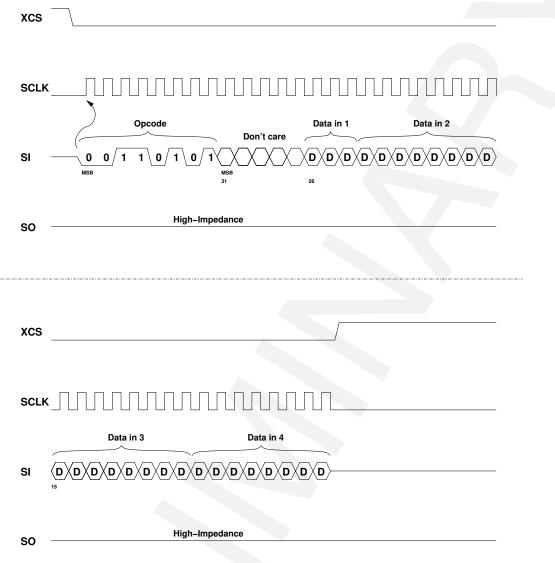

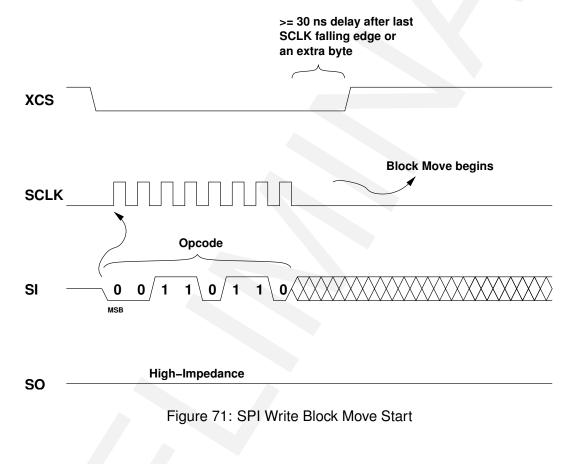

| 71                   | SPI Write Block Move Start                                                                  |

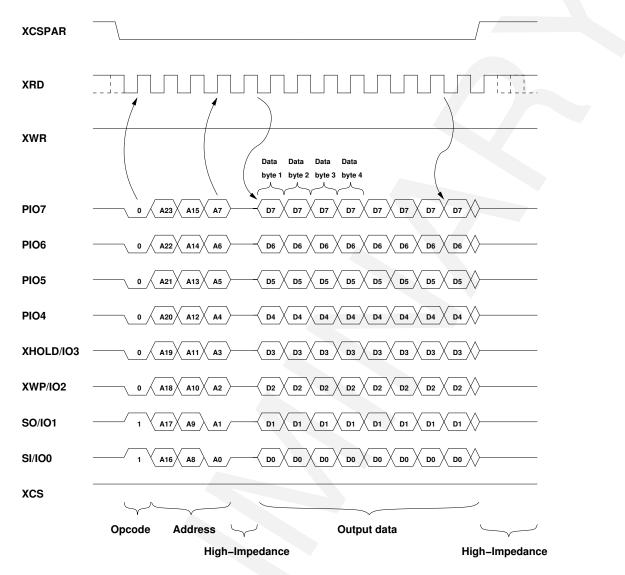

| 72                   | 8-Bit Parallel Interface Read                                                               |

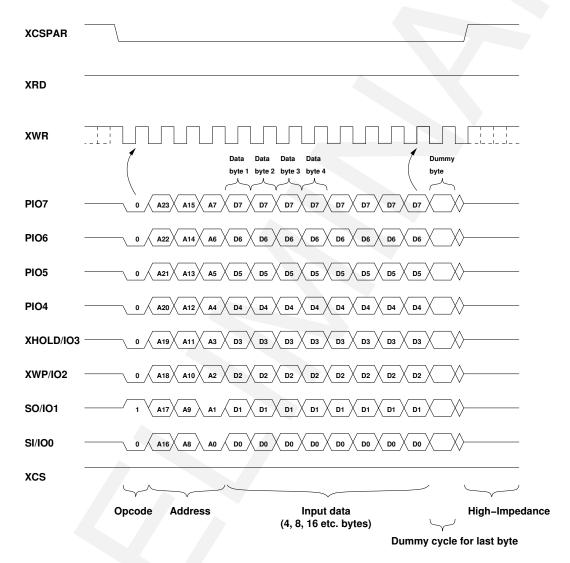

| 73                   | 8-Bit Parallel Interface Write                                                              |

## 1 Disclaimer

This is a *preliminary* data sheet. All properties and figures are subject to change.

## 2 Definitions

B Byte, 8 bits

**b** Bit

CSCIk Clock, which frequency is Colour Subcarrier Frequency of a video format.

- **GPIO** General Purpose I/O

- LSB Least Significant Bit

- MSB Most Significant Bit

- **NTSC** National Television System Committee video format, colour subcarrier frequency is 3.579545 MHz.

- **PAL** Phase Alternating Line video format, colour subcarrier frequency is 4.43361875 MHz.

- **POR** Power On Reset

- SPI Serial Peripheral Interface

- **SRAM** Static Random Access Memory

- **TBD** To Be Defined

- U, V Chrominance components (colour information) of video signal

- **VCIk** Video Display Controller clock of the VS23S010C-L. It can come directly from VXTAL oscillator or can be generated on-chip by 8x PLL from VXTAL pins. VClk frequency has to be 8 times the colour subcarrier frequency of the selected analog video format.  $F_{VClk} = 8 \times F_{CSClk}$

- Y Luna component (the brightness) of video signal

## 3 Electrical Characteristics & Specifications

#### 3.1 Absolute Maximum Ratings

| Parameter                              | Symbol | Min  | Max                  | Unit |

|----------------------------------------|--------|------|----------------------|------|

| Positive Supply                        | VDD    | -0.3 | 3.6                  | V    |

| Core Supply                            | CVDD   | -0.3 | 1.98                 | V    |

| Current at any non-power pin $^1$      |        |      | ±50                  | mA   |

| Voltage at any digital input           |        | -0.3 | VDD+0.3 <sup>2</sup> | V    |

| Operating temperature                  |        | -40  | +85                  | °C   |

| Storage temperature                    |        | -65  | +150                 | °C   |

| ESD protection on any pin <sup>3</sup> |        | 2.0  |                      | kV   |

$^{\rm 1}$  Higher current can cause latch-up.

<sup>2</sup> Must not exceed 3.6 V

<sup>3</sup> Human Body Model (HBM) MIL-STD-883E Method 3015.7

#### 3.2 DC Characteristics

T<sub>A</sub> = -40 ... +85 °C

| Parameter                                 | Min                     | Тур   | Max                      | Unit | Test Conditions                          |

|-------------------------------------------|-------------------------|-------|--------------------------|------|------------------------------------------|

| Positive supply voltage                   | 1.5                     |       | 3.6                      | V    |                                          |

| High-level input voltage                  | $0.7 \times \text{VDD}$ |       | VDD+0.3 <sup>1</sup>     | V    |                                          |

| Low-level input voltage                   | -0.2                    |       | $0.3 \times VDD$         | V    |                                          |

| Low-level input voltage                   | -0.2                    |       | $0.25 \times \text{VDD}$ | V    | Any Schmitt-trigger pin                  |

| High-level output voltage                 | $0.7 \times VDD$        |       |                          | V    | I <sub>O</sub> = -1.0 mA                 |

| Low-level output voltage                  |                         |       | $0.3 \times VDD$         | V    | I <sub>O</sub> = 1.0 mA                  |

| I/O leakage current <sup>2</sup>          | -1.0                    |       | 1.0                      | μA   | Pin as input or High-Z                   |

| Pull-up current                           | -5.0                    |       | -1.1                     | μA   | Any pull-up pin                          |

| Pull-down current                         | 1.1                     |       | 5.0                      | μA   | Any pull-down pin                        |

| I/O capacitance <sup>4</sup>              |                         |       | (TBD)                    | pF   | VDD=0V, f=0.5MHz, T <sub>A</sub> =+25 °C |

| RAM data retention voltage <sup>3,4</sup> |                         | 0.6   | 1.0                      | V    |                                          |

| Start-up time after power-up 5            |                         | (TBD) | (TBD) 4                  | ms   |                                          |

| DAC low level                             |                         |       | 0.1                      | mV   | 150 $\Omega$ load                        |

| DAC middle level                          |                         | 1.21  |                          | V    | 150 $\Omega$ load                        |

| DAC high level                            | 2.18                    |       |                          | V    | 150 $\Omega$ load                        |

<sup>1</sup> Must not exceed 3.6V

<sup>2</sup> Excluding the pins with pull-up or pull-down resistors

- <sup>3</sup> This is the limit to which VDD can be lowered without losing RAM data.

- <sup>4</sup> This parameter is periodically sampled and is not 100% tested.

- <sup>5</sup> Refer to Chapter 10.1 for additional information.

#### 3.3 AC Characteristics

#### 3.3.1 General

VDD = 3.3 V, T\_A = -40 ... +85  $^\circ\text{C}$

| Parameter                    | Symbol | Min              | Max | Unit    |

|------------------------------|--------|------------------|-----|---------|

| Clock high time <sup>1</sup> | Tclkh  | $0.45 * T_{MAX}$ |     | ns      |

| Clock low time <sup>1</sup>  | Tclkl  | $0.45 * T_{MAX}$ |     | ns      |

| Clock rise time <sup>2</sup> | Tclkr  |                  | 1.5 | $\mu$ S |

| Clock fall time <sup>2</sup> | Tclkf  |                  | 1.5 | $\mu$ S |

| Data in setup time           | Tds    | 5                |     | ns      |

| Data in hold time            | Tdh    | 3                |     | ns      |

| Output disable time          | Tdis   |                  | 12  | ns      |

| Output valid time            | Tv     |                  | 14  | ns      |

| Output valid time of PIO4-7  | Tvpio  |                  | 11  | ns      |

| Output hold time             | Toh    | 0                |     | ns      |

$^1$  T\_{MAX} is the minimum clock cycle time in each mode.  $^2$  This parameter is periodically sampled and is not 100% tested.

#### 3.3.2 SPI Mode

VDD = 3.3 V, T\_A = -40 ... +85  $^\circ\text{C}$

| Parameter                                | Symbol     | Min                  | Max | Unit | Test Conditions |

|------------------------------------------|------------|----------------------|-----|------|-----------------|

| SPI clock frequency (read) 1             | $F_{SCLK}$ |                      | 12  | MHz  | VDD = 1.5 V     |

|                                          |            |                      | 18  | MHz  | VDD = 1.8 V     |

|                                          |            |                      | 33  | MHz  | VDD = 3.0 V     |

|                                          |            |                      | 36  | MHz  |                 |

| SPI clock frequency (write) <sup>1</sup> | $F_{SCLK}$ |                      | 27  | MHz  | VDD = 1.5 V     |

|                                          |            |                      | 27  | MHz  | VDD = 1.8 V     |

|                                          |            |                      | 48  | MHz  | VDD = 3.0 V     |

|                                          |            |                      | 48  | MHz  |                 |

| XCS high time                            | Txcsh      | 14                   |     | ns   |                 |

| XCS low setup time                       | Txcsls     | 6                    |     | ns   |                 |

| XCS low hold time                        | Txcslh     | 5                    |     | ns   |                 |

| XCS high setup time                      | Txcshs     | 8                    |     | ns   |                 |

| XCS high hold time                       | Txcshh     | $0.5 * T_{SCLK} + 5$ |     | ns   |                 |

| XHOLD low setup time                     | Txhls      | 5                    |     | ns   |                 |

| XHOLD low hold time                      | Txhlh      | 3                    |     | ns   |                 |

| XHOLD high setup time                    | Txhhs      | 5                    |     | ns   |                 |

| XHOLD high hold time                     | Txhhh      | 3                    |     | ns   |                 |

| XHOLD low to output High-Z               | Txhlz      | 6                    | 7   | ns   |                 |

| XHOLD high to output valid               | Txhhz      |                      | 6   | ns   |                 |

| XWP low setup time                       | Txwls      | 5                    |     | ns   |                 |

| XWP low hold time                        | Txwlh      | 3                    |     | ns   |                 |

| XWP high setup time                      | Txwhs      | 5                    |     | ns   |                 |

| XWP high hold time                       | Txwhh      | 3                    |     | ns   |                 |

<sup>1</sup> When used with an external micro-controller the maximum SPI frequency is based on the total of VS23S010C-L and micro-controller I/O-delays and routing delays of the card.

Figure 5: XHOLD Timing, SPI and Dual-I/O Input Modes. Notice that internal address counter does not increment, when XHOLD is low.

Figure 6: XHOLD Timing, SPI and Dual-I/O Output Modes. Notice that internal address counter does not increment, when XHOLD is low.

Figure 7: XWP Timing, SPI and Dual-I/O Modes. Notice that internal address counter increments, when XWP is low.

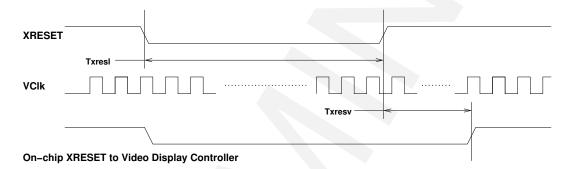

#### 3.3.3 Video Display Controller Mode

VDD = 3.3 V,  $T_A$  = -40 ... +85 °C

| Parameter                        | Symbol        | Min | Max                 | Unit    | <b>Test Conditions</b> |

|----------------------------------|---------------|-----|---------------------|---------|------------------------|

| Video Display Controller crystal | $F_{VXTALP}$  |     | 4.5                 | MHz     |                        |

| frequency when PLL used          |               |     |                     |         |                        |

| Video Display Controller crystal | $F_{VXTALXP}$ |     | 35.5                | MHz     |                        |

| frequency when PLL not used      |               |     |                     |         |                        |

| XRESET active time               | Txresl        | 0.5 |                     | $\mu$ S |                        |

| XRESET inactive to ready         | Txresv        |     | $4 * T_{VClk} + 10$ | ns      |                        |

| DAC output risetime              | Tdacor        |     | 5                   | ns      | 150 $\Omega$ load      |

Figure 8: XRESET Timing

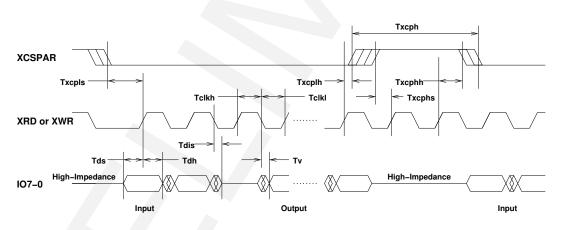

#### 3.3.4 8-bit Parallel Interface Mode

VDD = 3.3 V,  $T_A$  = -40 ... +85 °C

| Parameter              | Symbol         | Min                      | Max | Unit | Test Conditions |

|------------------------|----------------|--------------------------|-----|------|-----------------|

| Clock frequency        | $F_{XRD\_XWR}$ |                          | 6   | MHz  | VDD = 1.5 V     |

| (read) $^1$            |                |                          | 9   | MHz  | VDD = 1.8 V     |

|                        |                |                          | 15  | MHz  | VDD = 3.0 V     |

|                        |                |                          | 15  | MHz  |                 |

| Clock frequency        | $F_{XRD\_XWR}$ |                          | 24  | MHz  | VDD = 1.5 V     |

| (write) <sup>1</sup>   | _              |                          | 24  | MHz  | VDD = 1.8 V     |

|                        |                |                          | 30  | MHz  | VDD = 3.0 V     |

|                        |                |                          | 30  | MHz  |                 |

| XCSPAR high time       | Txcph          | 20                       |     | ns   |                 |

| XCSPAR low setup time  | Txcpls         | 5                        |     | ns   |                 |

| XCSPAR low hold time   | Txcplh         | $0.5 * T_{XRD\_XWR} + 2$ |     | ns   |                 |

| XCSPAR high setup time | Txcphs         | 5                        |     | ns   |                 |

| XCSPAR high hold time  | Txcphh         | $0.5 * T_{XRD} XWR + 2$  |     | ns   |                 |

<sup>1</sup> When used with an external micro-controller the maximum 8-bit Parallel Interface frequency is based on the total of VS23S010C-L and micro-controller I/O-delays and routing delays of the card.

Figure 9: 8-bit Parallel Interface Timing

**AC Test Conditions**

| AC Waveform:          |                                                    |  |  |  |  |  |

|-----------------------|----------------------------------------------------|--|--|--|--|--|

| Input pulse level     | $0.1 \times \text{VDD}$ to $0.9 \times \text{VDD}$ |  |  |  |  |  |

| Input rise/fall time  | (TBD) ns                                           |  |  |  |  |  |

| Operating temperature | -40 °C to +85 °C                                   |  |  |  |  |  |

| $C_L = (TBD) pF$      |                                                    |  |  |  |  |  |

| Timing Measurement I  | Reference Level:                                   |  |  |  |  |  |

| Input                 | 0.5 	imes VDD                                      |  |  |  |  |  |

| Output                | 0.5 	imes VDD                                      |  |  |  |  |  |

#### 3.4 Current Consumption

$T_A = +25$  °C, XCS=VDD, SI=SO=SCLK=GND, other inputs connected to VDD or GND by onchip pull-up or pull-down resistors of the pins.

| Parameter                       | Min | Тур | Max | Unit    | Test Conditions      |

|---------------------------------|-----|-----|-----|---------|----------------------|

| Stand-by current <sup>1,2</sup> |     | 85  | 300 | $\mu A$ | VDD = 1.95 V - 3.6 V |

<sup>1</sup> This parameter is periodically sampled and is not 100% tested.

<sup>2</sup> The stand-by current can be lowered below Max by following methods:

A set clock to VXTALIN by enabling the crystal oscillator

B If VXTALIN is not used as a clock, make a couple of SPI writes when VS23S010C-L is in operation:

- First set Video Display Controller Control1 register to 1000h

- Then set it to 0000h

- Do this e.g. five times between other operations

The workaround for lowering stand-by current is described in Chapter 10.2

#### 3.4.1 SPI Mode

VDD = 3.3 V,  $T_A$  = +85 °C, these parameters are periodically sampled and are not 100% tested.

| Parameter                           | Min | Тур     | Max  | Unit    | Test Conditions                            |

|-------------------------------------|-----|---------|------|---------|--------------------------------------------|

| VDD current, SPI single output read |     |         | 200  | $\mu A$ | $F_{SCLK} = 1 \text{ MHz}, \text{ SO} = 0$ |

|                                     |     |         | 650  | $\mu A$ | $F_{SCLK}$ = 10 MHz, SO = 0                |

|                                     |     |         | 1.05 | mA      | $F_{SCLK}$ = 24 MHz, SO = 0                |

| VDD current, SPI single port write  |     | 0.1-1.3 |      | mA      | $F_{SCLK}$ = 1 MHz, $T_A$ = +25 °C         |

| & read, two patterns <sup>1</sup>   |     | 1.0-2.7 |      | mA      | $F_{SCLK}$ = 10 MHz, $T_A$ = +25 °C        |

<sup>1</sup> Current is heavily data-dependent.

#### 3.4.2 Video Display Controller Mode

VDD = 3.3 V,  $T_A$  = +25 °C, these parameters are periodically sampled and are not 100% tested.

| Parameter                                | Min | Тур        | Max | Unit | <b>Test Conditions</b> |

|------------------------------------------|-----|------------|-----|------|------------------------|

| VDD current, Video Display Controller on |     | 3.8 - 18.4 |     | mA   | 150 $\Omega$ load      |

#### 3.4.3 8-bit Parallel Interface Mode

VDD = 3.3 V,  $T_A$  = +85 °C, these parameters are periodically sampled and are not 100% tested.

| Parameter                             | Min | Тур | Max | Unit    | Test Conditions                                  |

|---------------------------------------|-----|-----|-----|---------|--------------------------------------------------|

| VDD current, parallel read            |     |     | 450 | $\mu A$ | $F_{XRD XWR} = 1$ MHz, data out = 00h            |

|                                       |     |     | 1.0 | mA      | $F_{XRD} XWR = 10$ MHz, data out = 00h           |

|                                       |     |     | 1.5 | mA      | $F_{XRD}_{XWR}$ = 20 MHz, data out = 00h         |

| VDD current, parallel read            |     | 0.8 |     | mA      | $F_{XRD}$ <sub>XWR</sub> = 1 MHz, $T_A$ = +25 °C |

| & write, increasing data <sup>1</sup> |     | 2.2 |     | mA      | $F_{XRD}_{XWR}$ = 10MHz, $T_A$ = +25 °C          |

|                                       |     | 3.0 |     | mA      | $F_{XRD}XWR} = 15MHz, T_A = +25 \text{ °C}$      |

<sup>1</sup> Current is heavily data-dependent.

## 4 Packages and Pin Descriptions

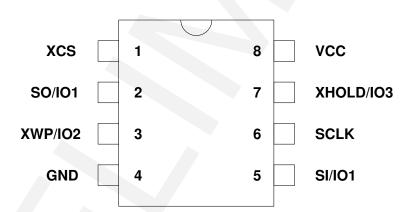

#### 4.1 Narrow SOIC8

Narrow SOIC8 is a lead (Pb) free and also RoHS compliant package. RoHS is a short name of Directive 2002/95/EC on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

Narrow SOIC8 package dimensions can be found at http://www.vlsi.fi/fileadmin/quality/soic8.pdf.

| Pin Name  | SOIC8 | Pin    | Function                                            |

|-----------|-------|--------|-----------------------------------------------------|

|           | Pin   | Туре   |                                                     |

| XCS       | 1     | DIS    | Active low chip select for SPI                      |

| SO/IO1    | 2     | DIO    | SO for SPI / IO1 for Dual-I/O and Quad-I/O SPI      |

| XWP/IO2   | 3     | DIOSPU | Active low write protect for SPI and Dual-I/O SPI / |

|           |       |        | IO2 for Quad-I/O SPI                                |

| GND       | 4     | GND    | Ground                                              |

| SI/IO0    | 5     | DIO    | SI for SPI / IO0 for Dual-I/O and Quad-I/O SPI      |

| SCLK      | 6     | DIS    | SCLK for SPI                                        |

| XHOLD/IO3 | 7     | DIOSPU | Active low Hold for SPI and Dual-I/O SPI /          |

|           |       |        | IO3 for Quad-I/O SPI                                |

| VCC       | 8     | PWR    | Power supply                                        |

The VS23S010C-S has the following pin out:

Figure 10: SOIC8 narrow package, compatible with standard pin out (not to scale).

Pin types:

| Туре   | Description                                                 |

|--------|-------------------------------------------------------------|

| DIS    | Digital input, Schmitt-trigger                              |

| DIO    | Digital input/output                                        |

| DIOSPU | Digital input/output with Pull-Up resistor, Schmitt-trigger |

| GND    | Ground pin                                                  |

| PWR    | Power supply pin                                            |

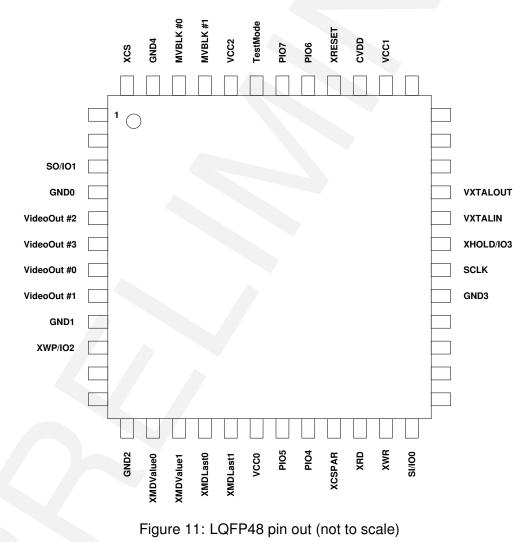

#### 4.2 LQFP48

LQFP48 is a lead (Pb) free and also RoHS compliant package. RoHS is a short name of Directive 2002/95/EC on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

LQFP48 package dimensions can be found at http://www.vlsi.fi/fileadmin/quality/lqfp48.pdf.

The VS23S010C-L has the following pin out:

Pin Name LQFP48 Pin Function Pin Туре 1-2 R DIO SO for SPI / SO/I01 3 IO1 for Dual-I/O and Quad-I/O SPI and 8-bit parallel interface GND0 GND Ground 4 VideoOut #2<sup>1</sup> 5 AO Analog video output VideoOut #3<sup>1</sup> AO Analog video output 6 VideoOut #0 7 AO Analog video output VideoOut #1<sup>1</sup> 8 AO Analog video output GND1 9 GND Ground XWP/IO2 DIOSPU Active low write protect for SPI and Dual-I/O SPI / 10 IO2 for Quad-I/O SPI and 8-bit parallel interface 11-12 R GND GND2 13 Ground XMDValue0 14 DIPU Multi-IC IC Id bit 0, active low DIPU XMDValue1 15 Multi-IC IC Id bit 1, active low DIPU Multi-IC Last IC bit 0, active low XMDLast0 16 XMDLast1 17 DIPU Multi-IC Last IC bit 1, active low PWR Power supply VCC0 18 PIO5 19 DIOPD IO5 for 8-bit parallel interface / GPIO1 / VGP1 for Video Display Controller PIO4 DIOPD IO4 for 8-bit parallel interface / GPIO0 20 VGP0 for Video Display Controller Active low chip select of 8-bit parallel interface XCSPAR 21 DISPU XRD 22 DISPU Clock of 8-bit parallel interface XWR 23 DISPU Clock of 8-bit parallel interface SI for SPI / SI/IO0 24 DIO IO0 for Dual-I/O and Quad-I/O SPI and 8-bit parallel interface 25-28 R GND3 29 GND Ground SCLK 30 DIS SCLK for SPI XHOLD/IO3 31 DIOSPU Active low Hold for SPI and Dual-I/O SPI / IO3 for Quad-I/O SPI and 8-bit parallel interface VXTALIN 32 DIC Clock for Video Display Controller VXTALOUT 33 DOC Clock for Video Display Controller 34-36 R 37 R VCC1 PWR 38 Power supply 39 CPWR CVDD Digital core power, do not connect DISPD Active low reset for Video Display Controller XRESET 40 IO6 for 8-bit parallel interface / GPIO2 / PIO6 41 DIOPD VGP2 for Video Display Controller PIO7 42 DIOPD IO7 for 8-bit parallel interface / GPIO3 / VGP3 for Video Display Controller TestMode 43 DISPD Active high testmode select VCC2 44 PWR Power supply **MVBLK #1**<sup>1</sup> 45 DO Video Display Controller block move active Video Display Controller block move active DO MVBLK #0 46 GND4 47 GND Ground XCS 48 DIS Active low chip select for SPI

<sup>1</sup> Not connected in first prototypes, reserved for use in future Multi-IC VS23S010C-Ls.

VS23S010C Datasheet 4 PACKAGES AND PIN DESCRIPTIONS

#### Pin types:

| Туре   | Description                                                 |

|--------|-------------------------------------------------------------|

| AO     | Analog output                                               |

| CPWR   | Core power pin                                              |

| DIO    | Digital input/output                                        |

| DIOPD  | Digital input/output with Pull-Down resistor                |

| DIOSPU | Digital input/output with Pull-Up resistor, Schmitt-trigger |

| DIPU   | Digital input with Pull-Up resistor                         |

| DIS    | Digital input, Schmitt-trigger                              |

| DISPD  | Digital input with Pull-Down resistor, Schmitt-trigger      |

| DISPU  | Digital input with Pull-Up resistor, Schmitt-trigger        |

| DIC    | Digital input, clock oscillator                             |

| DOC    | Digital output, clock oscillator                            |

| DO     | Digital output                                              |

| GND    | Ground pin                                                  |

| PWR    | Power supply pin                                            |

| R      | Reserved for future use                                     |

## 5 Connection Guidelines

VXTALIN and VXTALOUT are crystal oscillator pins for Video Display Controller.

CVDD pin can be used to supply digital core voltage. Usually there is no need for that because of the on-chip regulator.

Interface signals may require small series resistors if there is too much overshoot or undershoot in these signals.

#### 5.1 Connecting to Video Display

VideoOut can be connected to a display via 75  $\Omega$  series resistor or by using an op-amp buffer.

Figure 12: Connection example

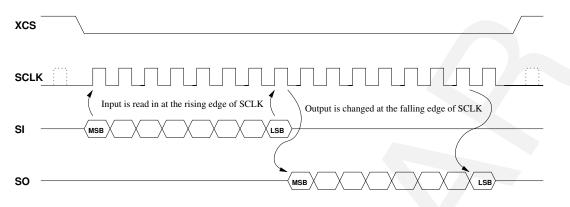

## 6 Device Operation

The device consists of following main blocks: SPI , Video Display Controller, 8-bit Parallel Interface and SRAM. SPI and Video Display Controller can be enabled simultaneously and also 8-bit Parallel Interface and Video Display Controller can be enabled at the same time. However, SPI and 8-bit Parallel Interface have to be used separately because they share I/O. The SRAM can be written and read by all other blocks of VS23S010C-L.

Figure 13: Device Organization

#### 6.1 SPI

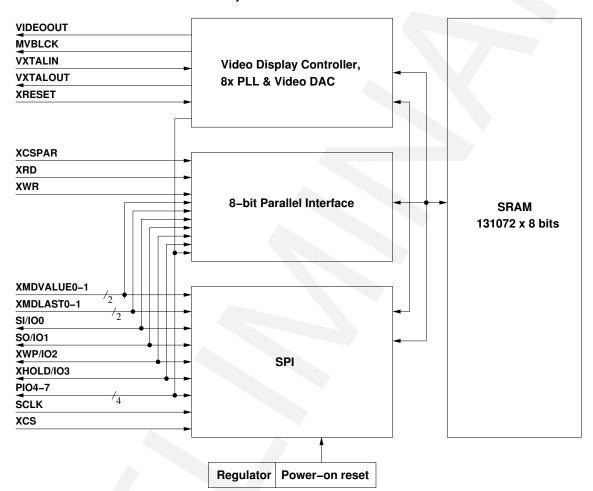

The VS23S010C-L is controlled by a set instructions that are sent from a host controller, commonly referred as SPI Master. The SPI Master communicates with the VS23S010C-L via the SPI bus which is comprised of four signal groups: Chip Select (XCS), Serial Clock (SCLK), Serial Input (SI, also SO in Dual-I/O mode and XWP and XHOLD in Quad-I/O mode) and Serial Output (SO, also SI in Dual-I/O mode and XWP and XHOLD in Quad-I/O mode).

The VS23S010C-L supports SPI protocol operation mode 0, which is very commonly used. Data is always latched in on the rising edge of the SCLK and always output on the falling edge

6

of the SCLK. SPI mode 0 is used in Single, Dual-I/O and Quad-I/O modes.

Figure 14: SPI Mode 0

SPI block does not have a separate Reset pin. There is an on-chip power-up delay logic, which is used to reset the selected SPI registers. SPI block logic is clocked by the SCLK pin. Following is a table describing the registers of the VS23S010C-L.

| Register                   | Symbol    | R/W | Default Value | Initialization                  |

|----------------------------|-----------|-----|---------------|---------------------------------|

| General                    |           |     |               |                                 |

| Status                     | STATUS    | RW  | 00h           | Power-Up                        |

| Manufacturer and Device ID | ID        | R   | ABh           | Power-Up                        |

| GPIO Control               | GPIOCTRL  | RW  | 00h           | Power-Up                        |

| GPIO State                 | GPIOSTATE | R   | 0Ch           | Pull-down and pull-up resistors |

| Multi-IC Access Control    | MDACC     | RW  | 00h           | Power-Up                        |

| Video Display Controller   |           |     |               |                                 |

| Line Start                 | PGLPXST   | W   | 000h          | Power-Up                        |

| Line End                   | PGLPXEND  | W   | 000h          | Power-Up                        |

| Line Length                | PGLPXLEN  | W   | 000h          | Power-Up                        |

| Index Start                | PGIDXST   | W   | 0000h         | Power-Up                        |

| Control1                   | PGCTRL1   | W   | 0000h         | Power-Up                        |

| Control2                   | PGCTRL2   | W   | 0000h         | Power-Up                        |

| U Table                    | PGUTBL    | W   | 0000h         | Power-Up                        |

| V Table                    | PGVTBL    | W   | 0000h         | Power-Up                        |

| Program                    | PGPRGM    | W   | 0000 0000h    | Power-Up                        |

| Line Value                 | PGCURRL   | R   | 0000h         | Power-Up                        |

| Block Move Control1        | PGBMCTRL1 | W   | 0 0000 0000h  | Power-Up                        |

| Block Move Control2        | PGBMCTRL2 | W   | 0000 0000h    | Power-Up                        |

#### 6.1.1 Word, Page and Sequential Operation Modes

Bits 7 to 6 of the Status register select these three SPI Operation Modes. These modes affect SPI Single, Dual and Quad I/O SRAM operations.

6

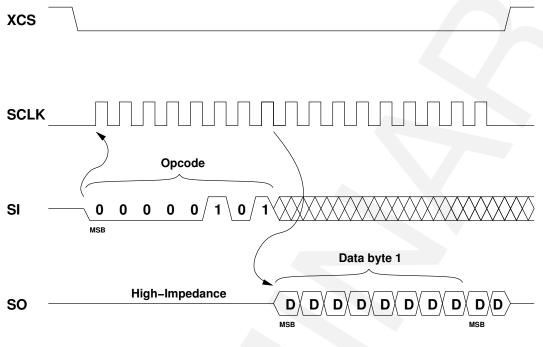

**Byte Operation** This mode is selected when Mode bits are "00". Read and write operations are limited to one byte in this mode i.e. address does not increment after each written or read byte. After command and 24-bit address byte data is read from or written to given SRAM address every time after subsequent 8 (Single), 4 (Dual-I/O) or 2 (Quad-I/O) SCLK cycles.

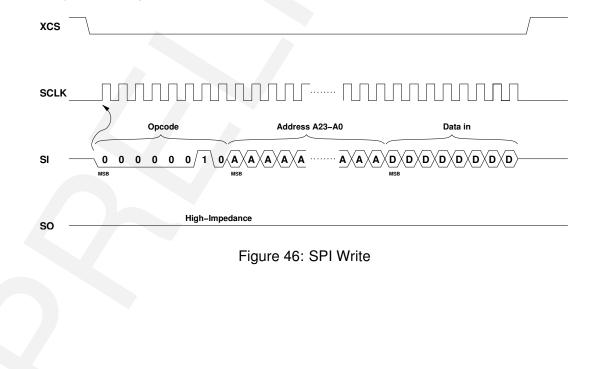

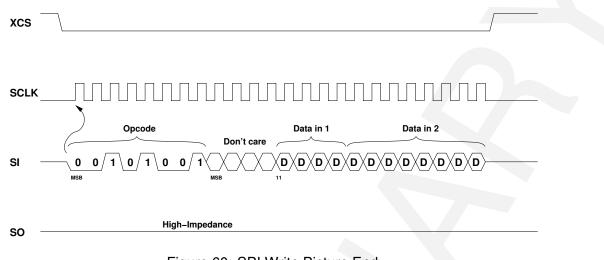

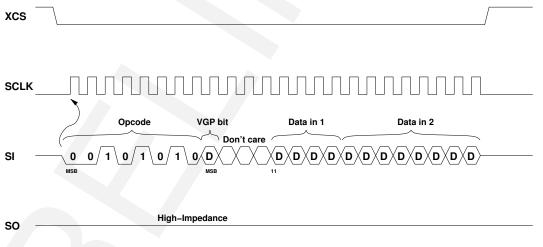

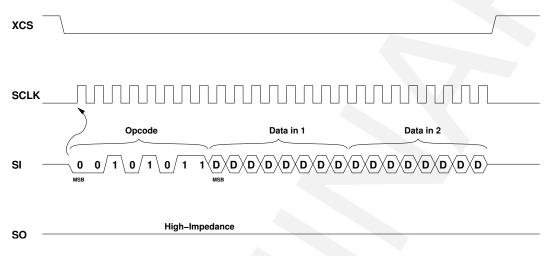

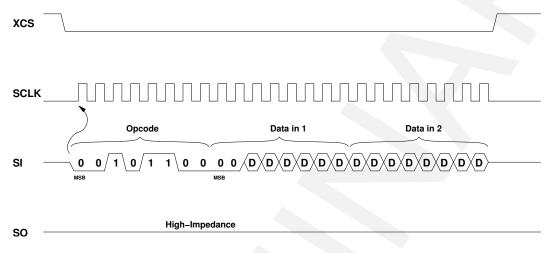

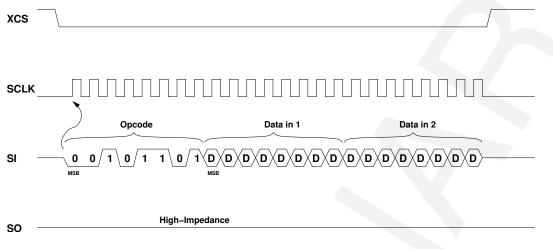

Figure 16: SPI Byte write

**Page Operation** This mode is selected when Mode bits are "10". VS23S010C-L has 4096 pages of 32 bytes. In page mode reads and writes are limited to the page selected by the given address. After each written or read byte the SRAM address is increased automatically. When the last address of page is reached the accessing will continue from the first address of the page.

**Sequential Operation** This mode is selected when Mode bits are "01". In this mode the entire SRAM array can be accessed in one operation. The address counter is increased automatically and when the last address 1FFFFh of the SRAM is reached the address counter returns to value 00000h.

If several VS23S010C-Ls are connected to SPI or 8-bit parallel bus in Multi-IC configuration, in the case of address wrapping around the addressing continues from the address 00000h of the

next VS23S010C-L in system.

#### 6.1.2 Dual-I/O and Quad-I/O Operation

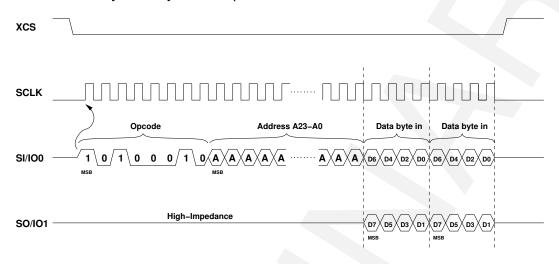

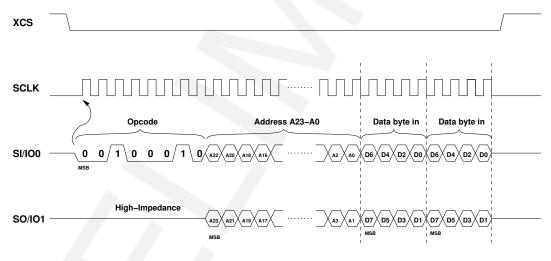

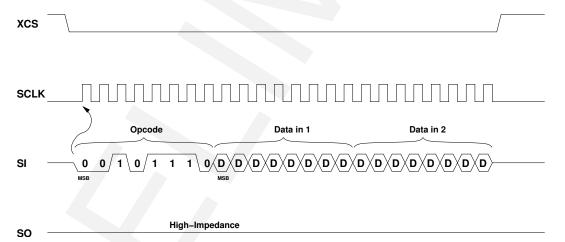

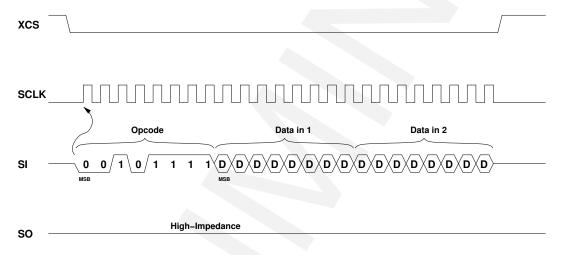

In Dual-I/O SPI mode two data bits are read or written during one SCLK cycle. SI/IO0 pin is the lower bit and SO/IO1 pin is the higher bit in Dual-I/O mode. Both pins are inputs during the write and outputs during the read.

In Quad-I/O SPI mode four data bits are read or written during one SCLK cycle. SI/IO0 pin is the lowest bit, SO/IO1 pin is the second bit, XWP/IO2 is the third bit and finally XHOLD/IO3 is the fourth bit in Quad-I/O mode. The pins are inputs during the write and outputs during the read.

In these modes the SPI command is still given in one-bit SPI mode. The address can be given

DEVICE OPERATION

Figure 18: SPI Page write

either in one-bit SPI mode or multi-bit SPI mode depending on the given command.

6 DEVICE OPERATION

DEVICE OPERATION

6

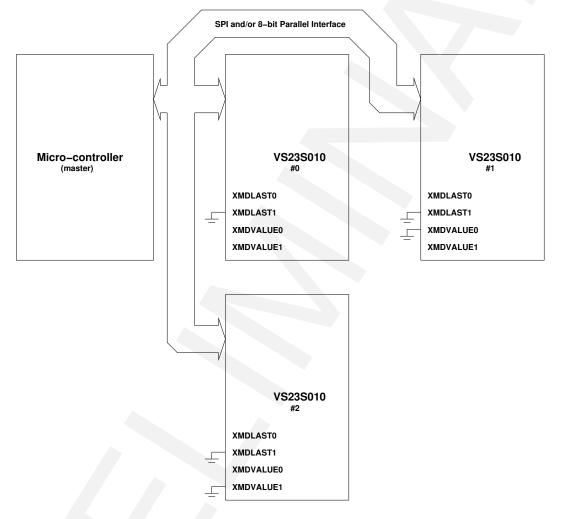

#### 6.1.3 Multi-IC Operation

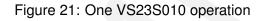

VS23S010C-L has support for multi-die or multi-IC use of SPI and 8-bit parallel interface. In this mode SRAMs are connected in series after each other to form one large SRAM entity.

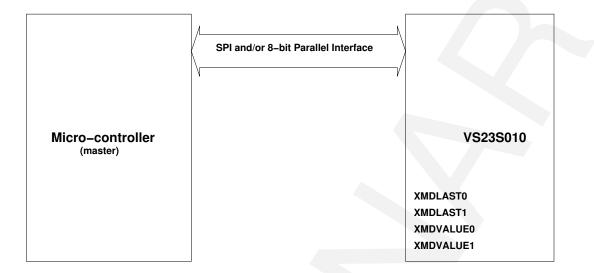

With Multi-IC controls it is possible to connect up to four VS23S010C-Ls acting as one larger VS23S010C-L. XMDLAST0 and XMDLAST1 are active low signals, which are used for informing the number of VS23S010C-L connected to single SPI and/or 8-bit parallel interface bus. XMDVALUE0 and XMDVALUE1 are also active low signals that define the position of each VS23S010C-L in the system.

When one VS23S010C-L is used, the SRAM address is formed using address bits A16-A0. In Multi-IC system additional address bits A18-A17 are used to define, which VS23S010C-L IC is accessed. Value "00" of A18-A17 selects VS23S010C-L #0 as SRAM access target, "01" selects VS23S010C-L #1, "10" selects VS23S010C-L #2 and finally "11" selects VS23S010C-L #3. The following table summarizes how address bits affect the starting address of SRAM operation in different VS23S010C-L Multi-IC configurations.

|            | SRAM Operation Start Point |                |             |            |                   |  |  |  |

|------------|----------------------------|----------------|-------------|------------|-------------------|--|--|--|

| A23-A19    | A18-A17                    | A16-A0         | XMDVALUE1-0 | XMDLAST1-0 | # of VS23S010C-Ls |  |  |  |

| Don't care | Don't care                 | VS23S010C-L #0 | "11"        | "11"       | 1                 |  |  |  |

|            | "00" or "10"               | VS23S010C-L #0 | "11"        | "11"       | 2                 |  |  |  |

|            | "01" or "11"               | VS23S010C-L #1 | "10"        |            |                   |  |  |  |

|            | "00" or "11"               | VS23S010C-L #0 | "11"        | "01"       | 3                 |  |  |  |

|            | "01"                       | VS23S010C-L #1 | "10"        |            |                   |  |  |  |

|            | "10"                       | VS23S010C-L #2 | "01"        |            |                   |  |  |  |

|            | "00"                       | VS23S010C-L #0 | "11"        | "00"       | 4                 |  |  |  |

|            | "01"                       | VS23S010C-L #1 | "10"        |            |                   |  |  |  |

|            | "10"                       | VS23S010C-L #2 | "01"        |            |                   |  |  |  |

|            | "11"                       | VS23S010C-L #3 | "00"        |            |                   |  |  |  |

It is possible to limit SPI register access to selected VS23S010C-Ls in Multi-IC mode by setting bits in Multi-IC Access Control register. This allows user to write a control command to a selected VS23S010C-L or read a register value from a selected VS23S010C-L. SRAM reads and writes are not affected by this control, because SRAM is handled as one large SRAM entity in Multi-IC mode. Also Multi-IC Access Control writes affect all VS23S010C-Ls in the Multi-IC system.

Single VS23S010, XMD\* pins have internal pull-up resistors

Two VS23S010s, XMD\* pins have internal pull-up resistors

Figure 22: Two VS23S010s operation

DEVICE OPERATION

Three VS23S010s, XMD\* pins have internal pull-up resistors

Figure 23: Three VS23S010s operation

DEVICE OPERATION

Four VS23S010s, XMD\* pins have internal pull-up resistors

Figure 24: Four VS23S010s operation

6 DEVICE OPERATION

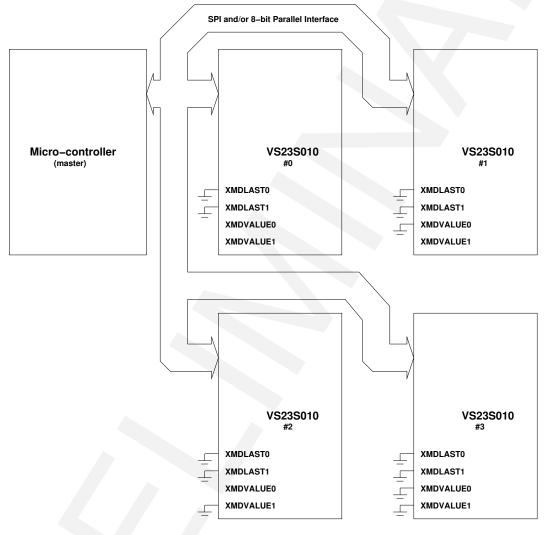

Figure 25: SPI read in Multi-IC system consisting of four VS23S010C-Ls

6

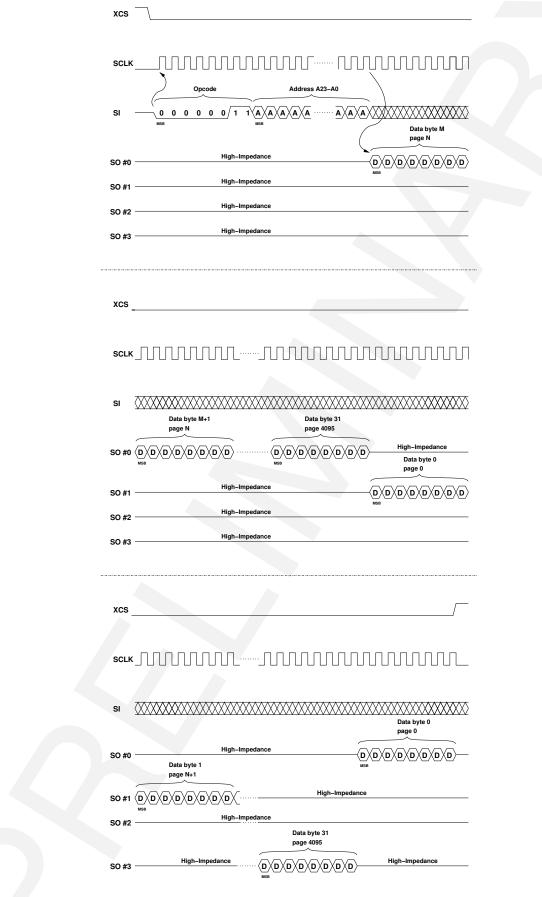

#### 6.2 Video Display Controller

The data in SRAM can be converted to analog video by Video Display Controller block. The Video Display Controller is fully configurable by user. Refer to Chapter 8 for details of required SPI commands.

#### 6.2.1 Block General Description

Video Display Controller is very versatile analog video generation device. The contents of the SRAM can be converted to analog video output using several SPI commands. Video clock crystal oscillator (pins VXTALIN and VXTALOUT) is used for generating the clock (VClk) for Video Display Controller. Video clock crystal oscillator output can be used as VClk or its frequency can be multiplied by 8 in the 8x PLL. The frequency of the VClk is eight times the colour subcarrier frequency (CSClk frequency) of desired video format, for PAL 4.433618 MHz and for NTSC 3.579545 MHz. Following table summarizes general properties of the Video Display Controller block.

| Summary of Video Display Controller Properties |                                               |  |  |  |  |

|------------------------------------------------|-----------------------------------------------|--|--|--|--|

| Versatile organization of SRAM                 |                                               |  |  |  |  |

| Configurable SRAM block move                   |                                               |  |  |  |  |

| 9-bit video DAC                                |                                               |  |  |  |  |

| 8×PLL for VXTAL                                | user selectable                               |  |  |  |  |

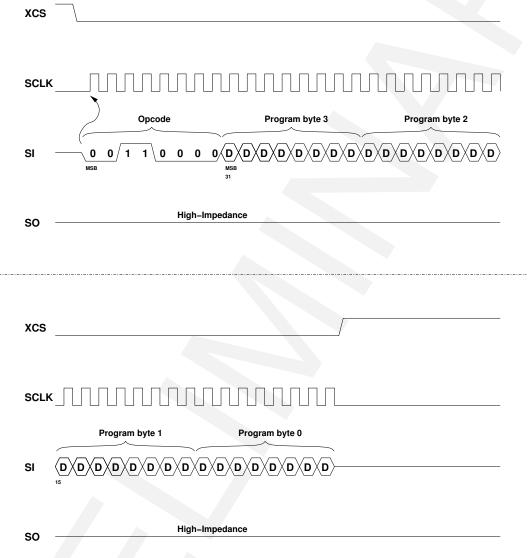

| Microcode programmable                         | 4 byte program                                |  |  |  |  |

| Supported formats                              | PAL, NTSC, direct DAC mode                    |  |  |  |  |

| Video SRAM capacity                            | 1048576 bits                                  |  |  |  |  |

| Colour subcarrier frequency for PAL            | 4.433618 MHz                                  |  |  |  |  |

| Colour subcarrier frequency for NTSC           | 3.579545 MHz                                  |  |  |  |  |

| Pixels per line                                | up to 2048 (theoretical)                      |  |  |  |  |

| Lines per picture                              | up to 1023 (theoretical)                      |  |  |  |  |

| Line types                                     | Protoline and Normal line                     |  |  |  |  |

| Y word length                                  | 1 to 8 bits, unsigned                         |  |  |  |  |

| U word length                                  | 0 to 6 bits, signed                           |  |  |  |  |

| V word length                                  | 0 to 6 bits, signed                           |  |  |  |  |

| U presets                                      | four 4 bit values                             |  |  |  |  |

| V presets                                      | four 4 bit values                             |  |  |  |  |

| Digital output                                 | 4-bit, programmable for video synchronization |  |  |  |  |

SPI or 8-bit parallel interface can be operated when Video Display Controller is enabled. The initialization and enabling of the Video Display Controller are made by SPI so during that period 8-bit parallel interface can't be used. Theoretical maximum operating frequencies of SPI or 8-bit parallel interface when Video Display Controller is enabled are shown on the following table. The Status register StFastWV bit can be used to accelerate SPI write operations when Video Display Controller is on. There are some restrictions in its use, see Chapter 7.3.1 for more information. Also the given datarates are theoretical maximum values and in reality they are more of guidelines.

6 DEVICE OPERATION

Figure 26: Video Display Controller block diagram

| Max. in          | Max. interface speeds when Video Display Controller is enabled (theoretical) |              |                                                |                  |  |  |  |

|------------------|------------------------------------------------------------------------------|--------------|------------------------------------------------|------------------|--|--|--|

| Mode             | Read/Write                                                                   | StFastWV bit | Max. interface clk freq. ( $\times F_{VClk}$ ) | VClk cycles/Byte |  |  |  |

| SPI Single       | R                                                                            | don't care   | 1                                              | 8                |  |  |  |

| SPI Single       | W                                                                            | "0"          | 1                                              | 8                |  |  |  |

| SPI Single       | W                                                                            | "1"          | 15                                             | 8/15             |  |  |  |

| SPI Dual         | R                                                                            | don't care   | 1                                              | 4                |  |  |  |

| SPI Dual         | W                                                                            | "0"          | 1                                              | 4                |  |  |  |

| SPI Dual         | W                                                                            | "1"          | 7                                              | 4/7              |  |  |  |

| SPI Quad         | R                                                                            | don't care   | 1                                              | 2                |  |  |  |

| SPI Quad         | W                                                                            | "0"          | 1                                              | 2                |  |  |  |

| SPI Quad         | W                                                                            | "1"          | 3                                              | 2/3              |  |  |  |

| SPI register op. | don't care                                                                   | don't care   | SPI max. speed                                 | does not affect  |  |  |  |

| 8-b Parallel     | R                                                                            | don't care   | 2                                              | 1/2              |  |  |  |

| 8-b Parallel     | W                                                                            | don't care   | 2                                              | 1/2              |  |  |  |

The example of possible picture resolutions are shown in the following table. There is shown maximum amount of colors for each resolution.

| Resolution               | Н   | V   | Pixels | Colors <sup>1</sup> | Bits per pixel | Memory bytes |

|--------------------------|-----|-----|--------|---------------------|----------------|--------------|

| NTSC YUV422 <sup>2</sup> | 352 | 240 | 84480  | 65536               | 8+4            | 126720       |

| MCGA                     | 320 | 200 | 64000  | 65536               | 16             | 128000       |

| CDG                      | 300 | 216 | 64800  | 65536               | 16             | 129600       |

| QVGA                     | 320 | 240 | 76800  | 8192                | 13             | 124800       |

| NTSC VCD                 | 352 | 240 | 84480  | 4096                | 12             | 126720       |

| PAL VCD                  | 352 | 288 | 101376 | 1024                | 10             | 126720       |

| NTSC noninterlaced       | 440 | 243 | 106920 | 512                 | 9              | 120285       |

| PAL noninterlaced        | 520 | 288 | 149760 | 128                 | 7              | 131040       |

| HVGA                     | 480 | 320 | 153600 | 64                  | 6              | 115200       |

| EGA                      | 640 | 350 | 224000 | 16                  | 4              | 112000       |

| VGA letterbox            | 640 | 400 | 256000 | 16                  | 4              | 128000       |

| NTSC Analog              | 440 | 486 | 213840 | 16                  | 4              | 106920       |

| NTSC SVCD                | 480 | 480 | 230400 | 16                  | 4              | 115200       |

| NTSC DVD                 | 720 | 480 | 345600 | 8                   | 3              | 129600       |

| VGA                      | 640 | 480 | 307200 | 8                   | 3              | 115200       |

| PAL Analog               | 520 | 576 | 299520 | 8                   | 3              | 112320       |

| PAL SVCD                 | 480 | 576 | 276480 | 8                   | 3              | 103680       |

| PAL DVD                  | 720 | 576 | 414720 | 4                   | 2              | 103680       |

<sup>1</sup> Theoretical number of colors based on aligned memory consumption (integer bits per pixel). Actual performance can vary due to implementation details.

<sup>2</sup> YUV422, 8 bits luminance per each pixel plus 8 bits chrominance for each pixel pair.

#### 6.2.2 Parameters of Video Display Controller

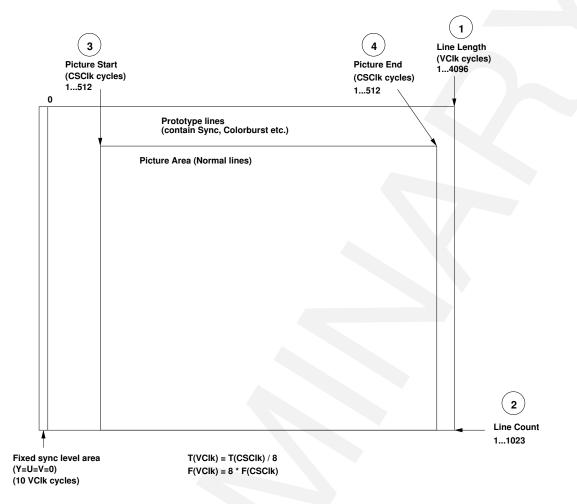

There are several adjustable parameters in the video picture. Figure 27 shows the main parameters of a video frame:

Line length is defined in VClk cycles. This means that increasing the length by 8 increases the duration of line by one CSClk (colour subcarrier) cycle. Line length is a 12 bit value ranging from 1 to 4096. Each line begins with a fixed black level (i.e. zero) signal lasting 10 VClk cycles which is the same as 1.25 CSClk (colour subcarrier) cycles. So the line total length can vary from 11 to 4106 VClk cycles.

Line length is set by Write Line Length command.

2. Line count is the amount of lines per video frame. It is a 10-bit value ranging from 1 to 1023. When the last line is output the system starts again from the first line.

Line count is set by Write Video Display Controller Control1 command.

3. Picture start is given in CSClk (colour subcarrier) cycles (i.e. 8 times VClk cycles). It defines the CSClk cycle where and after video data is fetched from the defined normal line SRAM area. Video data before Picture start cycle is fetched from a defined prototype line area. Prototype and normal lines can have different video formats. Picture start has a 10 bit value and it ranges from 1 to 512.

# 6 DEVICE OPERATION

Figure 27: Video picture parameters

Picture start is set by Write Picture Start value command.

4. Picture end is given in CSClk cycles. It defines the CSClk cycle where and after video data is fetched again from the defined prototype line SRAM area. Video data starting from Picture start cycle to Picture end cycle minus one is fetched from a defined normal line area. Prototype and normal lines can have different video formats. Picture end has a 10 bit value and it ranges from 1 to 512.

Picture end is set by Write Picture End value command.

Microcode program is used for controlling the video generation. The program consists of four bytes. Each program run can last from 2 to 15 VClk cycles. One code line is executed on each VClk cycle. If the run is less than 4 cycles, then only the N first lines of code are executed. If the run is more than 4 cycles, then the rest of the cycles are idle. The program syntax is as follows:

| cycle | pick<br>a b y - | bits<br>18 | shift<br>06 |                          |

|-------|-----------------|------------|-------------|--------------------------|

| 5     |                 |            |             |                          |

| 0     | а               | 4          | 4           | // take $U(4)$ , shift 4 |

| 1     | b               | 4          | 4           | // take $V(4)$ , shift 4 |

| 2     | У               | 8          | 4           | // take $Y(8)$ , shift 4 |

| 3     | -               | x          | 4           | // idle, shift 4         |

Each code line can have one of the four functions:

- Pick a, which takes the amount of bits from the SRAM data and sets them as U data.

- Pick b, which takes the amount of bits from the SRAM data and sets them as V data.

- Pick y, which takes the amount of bits from the SRAM data and sets them as Y data.

- Pick -, which does not take any data. However, this command can be used to shift the SRAM data additionally. Because the maximum SRAM data shift value is 6 and it is possible to take 8 bits for Y, an extra SRAM data shift cycle is needed to keep the SRAM data in synchronization.

As mentioned above, the bits select, how many bits of SRAM data is used for each operation. U and V data can be from 1 to 6 bits, Y data can be from 1 to 8 bits. Shifts are done according to program to keep the SRAM data synchronized. The tables below show how U and V data and Y data are organized depending on bit depth before sending to Color Modulator. Y value is an unsigned integer and U and V are signed integers.

| Bits | Proto/Normal | U & V Data Bit Organization |   |     |     |     |     |

|------|--------------|-----------------------------|---|-----|-----|-----|-----|

|      |              | 5(MSB)                      | 4 | 3   | 2   | 1   | 0   |

| 1    | Normal       | 0                           | 0 | "0" | "0" | "0" | "0" |

| 2    | Normal       | 1                           | 1 | 0   | "0" | "0" | "0" |

| 3    | Normal       | 2                           | 2 | 1   | 0   | "0" | "0" |

| 4    | Proto        | 3                           | 2 | 1   | 0   | "0" | "0" |

| 4    | Normal       | 3                           | 3 | 2   | 1   | 0   | "0" |

| 5    | Normal       | 4                           | 4 | 3   | 2   | 1   | 0   |

| 6    | Normal       | 5                           | 4 | 3   | 2   | 1   | 0   |

6

| Bits | Proto/Normal | Y Data Bit Organization |   |   |   |   |   |   |   |

|------|--------------|-------------------------|---|---|---|---|---|---|---|

|      |              | 7(MSB)                  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1    | Normal       | 0                       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2    | Normal       | 1                       | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3    | Normal       | 2                       | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4    | Normal       | 3                       | 2 | 1 | 0 | 0 | 0 | 0 | 0 |

| 5    | Normal       | 4                       | 3 | 2 | 1 | 0 | 0 | 0 | 0 |

| 6    | Normal       | 5                       | 4 | 3 | 2 | 1 | 0 | 0 | 0 |

| 7    | Normal       | 6                       | 5 | 4 | 3 | 2 | 1 | 0 | 0 |

| 8    | Proto/Normal | 7                       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

A protoline is a line of fixed YUV type (8 bits Y, 4 bits U and 4 bits V) and therefore it has a hardwired program. The microcode for the protoline is the example on previous page. The program length for protoline is eight VClk cycles.

There are still some other parameters affecting the video picture:

- Program length, this tells after how many VClk cycles the Video Display Controller microcode program is run again. The range is from 2 to 16.

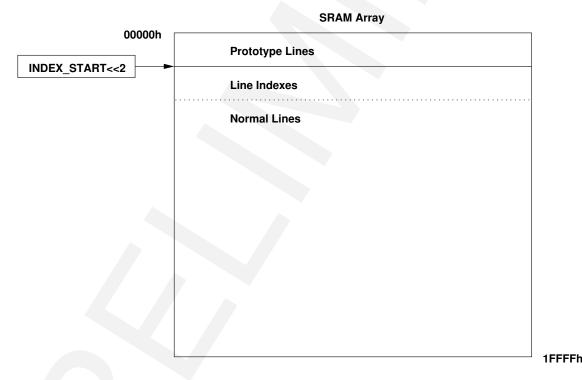

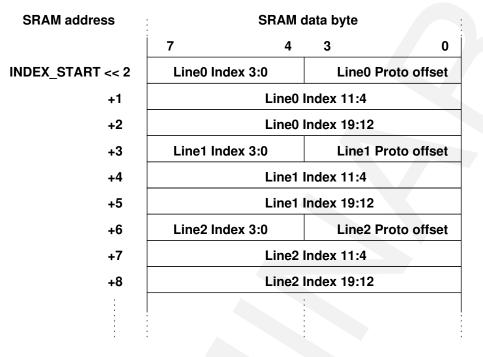

- Index Start parameter is used to define the address where line indexes start in the SRAM.

- Select PAL mode, this control enables the V phase alteration on odd lines in the Color Modulator for the PAL system.

- Translate U and V, this mode enables the use of four element tables for U and V values.

- UV Skip control, this can be used to skip the lines of microcode that pick U and/or V values. The value tells in how many code runs the U and V commands are not executed. The range is from 0 to 7.

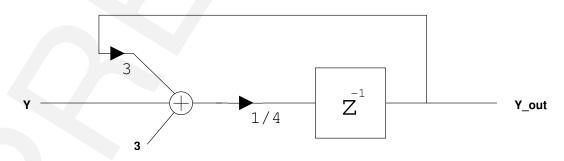

- Y filter enable is for enabling the low-pass Y filter.

- PLL controls are needed to enable the 8x PLL and to select it as a clock source

- DAC control is for selecting the small or large current mode of Video DAC.