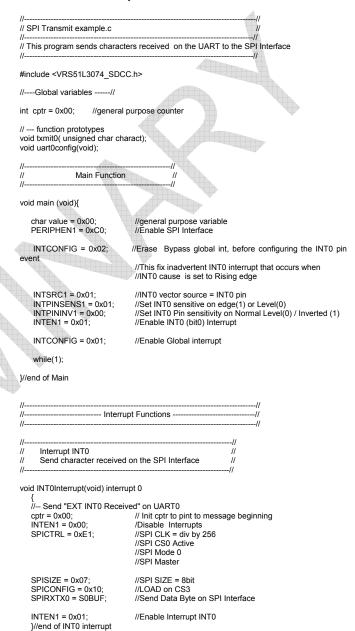

## 9 SPI Interface

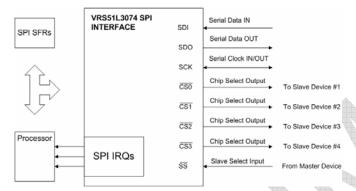

The SPI interface of the VRS51L3074's provides numerous enhancements compared to other vendor offerings. The SPI interface's key features include:

- Supports four standard SPI modes (clock phase/polarity)

- Operates in master and slave modes

- Automatic control of up to four chip select lines

- Configurable transaction size (1 to 32 bits)

- Transaction size of >32 bits is possible

- Double Rx and TX data buffers

- Configurable MSB or LSB first transaction

- Generation frame select/load signals

FIGURE 14: SPI INTERFACE OVERVIEW

Before the SPI can be accessed it must first be enabled by setting the SPIEN bit of the PERIPHEN1 register to 1.

## 9.1 SPI Control Registers

The SPICTRL register controls the operating modes of the SPI interface in master mode.

TABLE 97:SPI CONTROL REGISTER - SPICTRL SFR C1H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

|     | T ==        |                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | SPICLK[2:0] | SPI Communication Speed (Master Mode) 000 = Sys Clk / 2 ( / 8 if SPISLOW = 1) 001 = Sys Clk / 4 ( / 16 if SPISLOW = 1) 010 = Sys Clk / 8 ( / 32 if SPISLOW = 1) 011 = Sys Clk / 16 ( / 64 if SPISLOW = 1) 100 = Sys Clk / 32 ( / 128 if SPISLOW = 1) 101 = Sys Clk / 34 ( / 256 if SPISLOW = 1) 110 = Sys Clk / 128 ( / 512 if SPISLOW = 1) 111 = Sys Clk / 256 ( / 1024 if SPISLOW = 1) |

| 4   | SPICS[1:0]  | SPI Active Chip Select Line (Master Mode) 00 = CS0 is active 01 = CS1 is active 10 = CS2 is active 11 = CS3 is active                                                                                                                                                                                                                                                                    |

| 2   | SPICLKPH    | SPI Clock Phase 0 = SD0 output on rising edge and SDI sampling on falling edge 1= SD0 output on falling edge and SDI sampling on rising edge                                                                                                                                                                                                                                             |

| 1   | SPICLKPOL   | SPI Clock Polarity 0 = SCK stays at 0 when SPI is inactive 1 = SCK stays at 1 when SPI is inactive                                                                                                                                                                                                                                                                                       |

| 0   | SPIMASTER   | SPI Master Mode Enable 0 = SPI operates in slave mode 1 = SPI operate in master mode (default)                                                                                                                                                                                                                                                                                           |

When the SPIMASTER bit is set to 1, the SPI interface operates in master mode. This is the default operating mode of the VRS51L3074 SPI interface after reset.

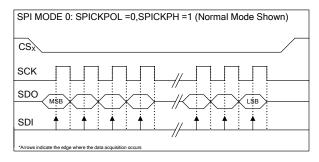

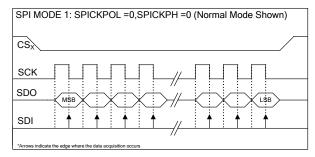

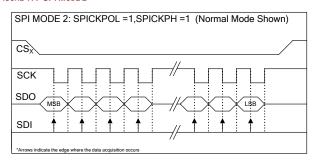

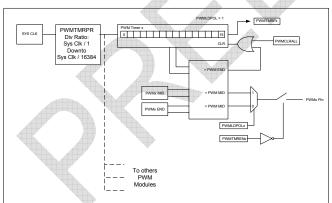

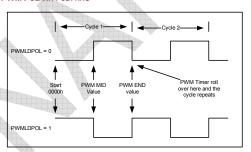

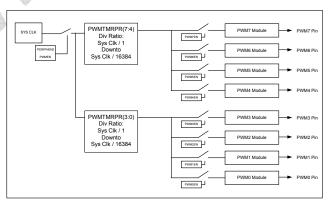

## 9.2 Setting Up Clock Phase and Polarity

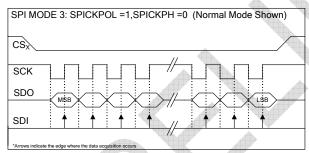

The clock phase and polarity is controlled by the SPICLKPH and SPICLKPOL bits, respectively. The following diagrams show the communication timing associated with the clock phase and polarity.

#### SPI Mode 0:

FIGURE 15: SPI MODE 0

www.ramtron.com page 51 of 105

#### SPI Mode 1:

#### FIGURE 16: SPI MODE 1

#### SPI Mode 2:

#### FIGURE 17: SPI MODE 2

#### SPI Mode 3:

#### FIGURE 18: SPI MODE 3

## 9.3 Defining active chip select line

As previously mentioned, only one chip select line is activated when communicating with an external SPI slave device. The SPICS bits of the SPICTRL register are used to select which CS line will be activated during the transfer.

Note that with the exception of the CS0 line, the SPICSEN bit of the PERIPHEN1 register must be set to 1 in order for the SPI be able to control the SPI CS lines.

## 9.4 Setting the SPI Communication Speed (Master Mode)

In master mode, the SPI interface communication speed is adjustable from "system clock /2" down to "system clock / 1024". Slower communication speeds can be useful for interfacing with slower devices or to adjust the communication speed to specific bus conditions.

The SPICLK SFR register and the SPISLOW bit of the of the SPICONFIG SFR register control the SPI communication speed.

The SPI communication speed in master mode can be calculated using the following formula:

SPI speed =

$$\frac{\text{Sys Clk}}{2^{(\text{SPICLK}[2:0]+1)} \times 4^{\text{SPISLOW}}}$$

#### Where:

- Sys Clk = Processor operating clock

- SPISLOW = can be either 0 or 1

- SPICLK[2:0] = from 0 to 7

The following tables provide example setting for SPI communication speeds with various system clock and SPICLK[2:0] and SPISLOW bit settings.

TABLE 98:SPI COMMUNICATION SPEED EXAMPLE (SPISLOW = 0)

| SPICLK | Com Speed | Com Speed  | Com Speed |

|--------|-----------|------------|-----------|

|        | @ 40MHz   | @ 22.18MHz | @ 4MHz    |

| 000    | 20 MHz    | 11.05 MHz  | 2 MHz     |

| 001    | 10 MHz    | 5.53 MHz   | 1 MHz     |

| 010    | 5 MHz     | 2.76 MHz   | 500 kHz   |

| 011    | 2.5 MHz   | 1.38 MHz   | 250 kHz   |

| 100    | 1.25 MHz  | 691.2 kHz  | 125 kHz   |

| 101    | 625 kHz   | 345.6 kHz  | 62.5 kHz  |

| 110    | 312.5 kHz | 172.8 kHz  | 31.3 kHz  |

| 111    | 156.3 kHz | 86.4 kHz   | 15.6 kHz  |

TABLE 99:SPI COMMUNICATION SPEED EXAMPLE (SPISLOW = 1)

| SPICLK | Com Speed | Com Speed  | Com Speed |

|--------|-----------|------------|-----------|

|        | @ 40MHz   | @ 22.18MHz | @ 4MHz    |

| 000    | 5 MHz     | 2.76 MHz   | 500 kHz   |

| 001    | 2.50 MHz  | 1.38 MHz   | 250 kHz   |

| 010    | 1.25 MHz  | 691.2 kHz  | 125 kHz   |

| 011    | 625 kHz   | 345.6 kHz  | 62.5 kHz  |

| 100    | 312.5 kHz | 172.8 kHz  | 31.3 kHz  |

| 101    | 156.3 kHz | 86.4 kHz   | 15.6 kHz  |

| 110    | 78.1 kHz  | 43.2 kHz   | 7.8 kHz   |

| 111    | 39.1 kHz  | 21.6 kHz   | 3.9 kHz   |

|        |           |            |           |

<u>www.ramtron.com</u> page 52 of 105

## 9.5 SPI Configuration and Status Registers

The SPI configuration and status registers allow the activation and the monitoring of the SPI interface interrupts. They also provide access to the advanced features of the SPI interface such as:

- Frame select/load generation on CS3

- Activating manual control of the chip select lines

- Bit reversed mode (Bitwise Endian Control)

- o Interrupt activation and monitoring

- Monitoring the state of the SS pin

TABLE 100:SPI CONFIGURATION REGISTER - SPICONFIG - C2H

| 7   | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|---|-----|-----|-----|-----|-----|-----|

| R/W | W | R/W | R/W | R/W | R/W | R/W | R/W |

| 0   | 0 | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit | Mnemonic   | Description                                         |

|-----|------------|-----------------------------------------------------|

| 7   |            | SPI Manual CS Mode Enable                           |

| /   | SPIMANCS   |                                                     |

|     |            | 0 = SPI Chip select control is fully automatic      |

|     |            | 1 = SPI Chip select will be brought low by the      |

|     |            | SPI interface, and will stay low until 0 is written |

|     |            | into SPIMANCS bit                                   |

| 6   | SPIUNDERC  | SPI Clear TX Underrun Flag (SPIUNDERF)              |

|     |            | Writing a 1 into this bit will clear the SPIUNDER   |

|     |            | bit of the SPISTATUS register                       |

|     |            | This bit always reads 0                             |

| 5   | FSONCS3    | Frame Select Pulse on CS3                           |

|     |            | 0 = CS3 acts in standard ways                       |

|     |            | 1 = The SPI interface will send an active low       |

|     |            | frame select pulse on CS3                           |

|     |            | Frame select has priority on SPILOAD function       |

| 4   | SPILOADCS3 | Load Pulse on CS3                                   |

|     |            | 0 = CS3 acts in standard way or as frame select     |

|     |            | pulse, if FSONCS3 is set to 1                       |

|     |            | 1 = The SPI interface sends an active low load      |

|     |            | pulse on the CS3 pin, if FSONCS3 is cleared         |

| 3   | SPISLOW    | SPI Slow Speed mode                                 |

|     |            | 0 = SPI transaction occurs at normal speed          |

|     |            | 1 = SPI transaction is 4x slower                    |

| 2   | SPIRXOVEN  | SPI RX Overrun Interrupt Enable                     |

|     |            | 0 = SPI RX overrun interrupt is deactivated         |

|     |            | 1 = SPI RX overrun interrupt is enabled             |

| 1   | SPIRXAVEN  | SPI RX Available Interrupt Enable                   |

|     | A          | 0 = SPI RX available interrupt is deactivated       |

|     |            | 1 = SPI RX available interrupt is enabled           |

| 0   | SPITXEEN   | SPI TX Empty Interrupt Enable                       |

|     |            | 0 = SPI TX empty interrupt is deactivated           |

|     |            | 1 = SPI TX empty interrupt is enabled               |

The SPISTATUS register's role is mainly for monitoring purposes.

TABLE 101:SPI STATUS REGISTER - SPISTATUS SFR C9H

| 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|---|---|---|---|---|---|---|

| R/W | R | R | R | R | R | R | R |

| 0   | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

|     |   |   |   |   |   |   |   |

| D:4 | Masassa    | Description                                                                                                                                                                                                                                                                                              |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Mnemonic   | Description                                                                                                                                                                                                                                                                                              |

| 7   | SPIREVERSE | SPI Reverse Mode<br>0 = SPI operates in normal mode (MSB First)                                                                                                                                                                                                                                          |

|     |            | 1 = SPI operates in reverse mode (LSB First)                                                                                                                                                                                                                                                             |

| 6   | -          | Not used                                                                                                                                                                                                                                                                                                 |

| 5   | SPIUNDERF  | SPI TX Underrun Flag 0 = No underrun condition noticed 1 = Indicates that the SPI transmit buffer has not been fed in time. This condition is likely to occur when the Transaction size is > 32 bits This bit is cleared by setting to 1, the SPICLRTXF bit of the SPICTRL bit of the SPICONFIG register |

| 4   | SSPINVAL   | Slave Select Pin Value 0 =SS pin is low 1 = SS pin is high                                                                                                                                                                                                                                               |

| 3   | SPINOCS    | SPI No Chip Select 0 = At least on chip select line is active 1 = Indicates that all the chip select lines are inactive (high)                                                                                                                                                                           |

| 2   | SPIRXOVF   | SPI RX Overrun InterruptFlag<br>0 = No SPI RX Overrun condition detected<br>1 = SPI Data collision occurred                                                                                                                                                                                              |

| 1   | SPIRXAVF   | SPI RX Available Interrupt Flag<br>0 = SPI receive buffer is empty<br>1 = Data is present in the SPI RX buffer                                                                                                                                                                                           |

| 0   | SPITXEMPF  | SPI TX Empty Interrupt Flag 0 = SPI transmit buffer is full 1 = SPI transmit buffer is ready to receive new data                                                                                                                                                                                         |

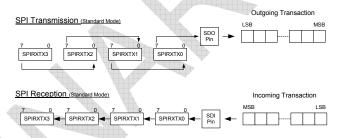

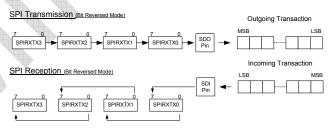

#### 9.6 SPI Transaction Directions

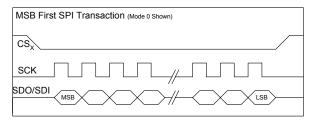

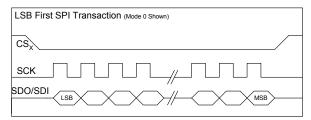

The SPI interface can perform transactions in the standard SPI format (MSB first) as well as in the reverse format (LSB first). In applications where data must be transmitted (or received) in LSB first format, the user would normally need to perform bit reversal manually at the processor level and then send the data through the SPI interface. The SPI interface can automatically handle the bit reversal operations, unloading the processor for other tasks.

When the SPIREVERSE bit of the SPISTATUS register is set to 0, the SPI transactions will take place in MSB first format.

<u>www.ramtron.com</u> page 53 of 105

The following examples show the timing related to these transaction directions:

FIGURE 19: SPI MSB FIRST TRANSACTION

When the SPIREVERSE is set to 1, the SPI transactions are done in LSB first format, as shown in the next figure.

FIGURE 20: SPI LSB FIRST TRANSACTION

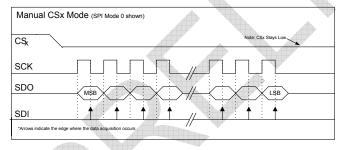

## 9.7 Manual Chip Select Control

When the SPIMANCS bit of the SPICONFIG register is set to 1, the active chip select line will stay at a logic low after the SPI master mode transaction is completed, as shown in the following figure.

FIGURE 21: SPI MANUAL CHIP SELECT

The chip select will remain at logic 0 until the SPIMANCS bit is cleared by the software.

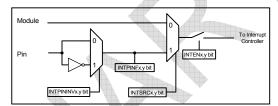

### 9.8 SPI Interrupts

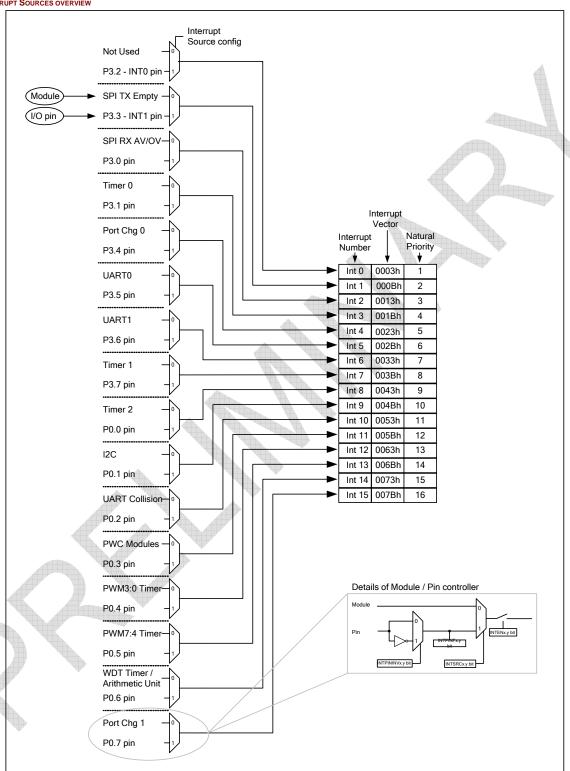

The SPI can trigger three interrupt sources that are handled by two interrupt vectors, as shown in the following table:

**TABLE 102: SPI INTERRUPT SOURCES**

| Interrupt        | Interrupt<br>Number | Interrupt<br>Vector |

|------------------|---------------------|---------------------|

| SPI TX Empty     | Int_1               | 000Bh               |

| SPI RX Available | Int 2               | 0013h               |

| SPI RX Overrun   | 1111_2              | 001311              |

The TX empty interrupt is set when the SPI transmit buffer is ready to receive more data. A double buffer is used in the SPI transmitter. Once transmission begins (after a write to the SPIRXTX0 register), the data is transferred to the final transmission buffer. This frees up the SPIRXTX SFR register, raises the SPITXEMPF flag of the status register and triggers an SPI TX empty interrupt if enabled. The SPI TX empty interrupt is enabled by setting the SPITXEEN bit of the SPICONFIG register to 1.

The priority of the SPI TX empty interrupt is set high in order to avoid buffer overrun in 32-bit SPI transfers.

The SPI RX available interrupt is activated when receive data has been transferred from the SPI RX buffer to the SPIRXTX register. The SPIRXTX register must be read by the processor before the next SPI bus data sequence is completed. The SPI RX available interrupt is enabled by setting the SPIRXAVEN bit of the SPICONFIG register to 1. The SPIRXAVF flag of the SPISTATUS register, when set to 1, indicates that data can be read. The SPIRXAVF flag is automatically reset when the SPIRXTX0 register is read.

The SPI RX overrun interrupt indicates that an overrun condition has taken place. The SPI RX overrun interrupt is enabled by setting the SPIRXOVEN bit of the SPICONFIG register to 1. The SPIRXOVF flag of the SPISTATUS register, when set to 1, indicates that a data collision has occurred.

All the SPI interface interrupt flags are active even if the associated interrupt is not activated and they can be monitored by the user program at any time.

Please consult the Interrupt Section for more details on the SPI interface interrupts and their interaction with other peripherals

<u>www.ramtron.com</u> page 54 of 105

#### 9.9 Alternate CS3 functions

For external SPI devices which require the use of a load or a frame select signal, the VRS51L3074 can be configured to either generate an active low frame select or active high load signal when operating in master mode.

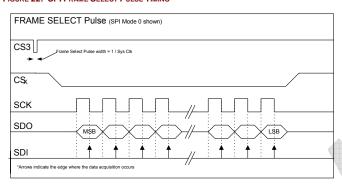

#### 9.9.1 Frame Select signal on CS3

When the FONCS3 bit of the SPICONFIG register is set to 1, the SPI interface will generate an active low frame select pulse on the CS3 pin (see the following timing diagram).

FIGURE 22: SPI FRAME SELECT PULSE TIMING

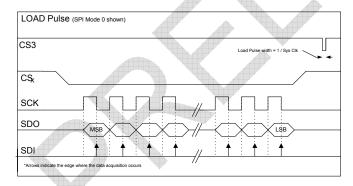

#### 9.9.2 Load Signal on CS3

When the SPILOADCS3 bit of the SPICONFIG register is set to 1 *and* the FSONCS3 bit is cleared, an active low load signal will be generated on the CS3 line of the SPI interface.

FIGURE 23: SPI LOAD PULSE TIMING

Note that the frame select alternate function has priority over the load function. This means that if the FSONCS3 bit is set, the alternate function selected will be the frame select, independent of the value of the SPILOAD bit.

### 9.10 SPI Activity Monitoring

The ability to monitor the state of communication of the SPI interface can be useful in highly modular applications in which the SPI interface is handled by interrupts. The SPISTATUS register contains two flags that can be used to monitor the CS and SS signals of the SPI interface.

The SPINOCS bit of the SPISTATUS register returns the logical AND of all the SPI CS lines of the VRS51L3074. If all the CS lines are inactive (logic high), the SPI interface sets the SPINOCS to 1. The SPINOCS bit is used to verify that the SPI interface is idle before reconfiguring it or starting a new transaction.

The SPINOCS bit of the SPISTATUS register is valid four system clock cycles after the SPI transmission begins. This delay is independent of the SPI transaction speed.

As such, after a write operation to the SPIRXTX0 register, which will trigger a SPI transaction in master mode, a NOP instruction (1 cycle) must be added before the MOV Rn, SPISTATUS instruction (3 cycles).

The SSPINVAL bit of the SPISTATUS register returns the logic level on the SS pin.

### 9.11 SPI TX Underrun Flag

The SPI interface provides an underrun condition flag that can be used to flag whether the software has failed to update transmission buffer in time for the next transfer. This is especially useful when the SPI interface is used to transmit packets greater than 32 bits in length.

If an underrun condition occurs, the SPIUNDERF bit of the SPI status register will be set to 1. This bit can be cleared by writing a 1 to the SPIUNDERC bit of the SPICONFIG register.

Note that SPI underrun monitoring is not linked to any of the SPI interrupts, therefore, this flag can only be v manually by software

www.ramtron.com page 55 of 105

#### 9.12 SPI Transaction Size

The standard SPI protocol is based on 8-bit transactions. However, many devices on the market, specifically A/D and D/A converters, require transactions greater than 8 bits. To communicate with these types of devices using a standard SPI interface, the user has no choice but to send multiple 8-bit streams or to manipulate the I/Os via software to emulate the timing control signals.

The VRS51L3074 SPI interface supports 8-bit transactions and can also be configured to support transactions that measure 1 to 32 bits in both transmit and receive directions. The value written into the SPISIZE register controls the transaction size. Upon reset, the SPI interface is configured for 8-bit transactions.

TABLE 103:SPI TRANSACTION SIZE - SPISIZE SFR C3H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1   |

| Bit | Mnemonic     | Description                                     |

|-----|--------------|-------------------------------------------------|

| 7:0 | SPISIZE[7:0] | SPI transaction Size                            |

|     |              | If < 32 : Transaction Size = SPISIZE + 1        |

|     |              | If >= 32: Transaction Size = (SPISIZE *8) - 216 |

|     |              | Default Transaction Size = 8 bits               |

Four formulas control the SPI transaction size:

#### For Transactions Size <= 32 bits

Transaction Size = SPISIZE[7:0] +1

Or

SPISIZE[7:0] = Transaction Size - 1

For Transactions Size > 32 bits

Transaction Size = [ (SPISIZE[7:0] \* 8) -216]

Or it can be expressed by:

SPISIZE[7:0] = [Transaction Size + 216]

8

The following table provides examples:

TABLE 104: TRANSACTION SIZE VS. SPISIZE[7:0]

| SPISIZE[7:0] | Transaction Size |

|--------------|------------------|

| 0x07         | 8-bit            |

| 0x0B         | 12-bit           |

| 0x0D         | 14-bit           |

| 0x10         | 17-bit           |

| 0x17         | 24-bit           |

| 0x1F         | 32-bit           |

| 0x20         | 40-bit           |

| 0x21         | 48-bit           |

| 0x23         | 64-bit           |

The transaction size must also be configured when the operating the SPI interface in slave mode.

### 9.13 SPI RX/TX Data Registers

Four SFR registers provide access to the SPI interface's receive and transmit data buffer. Performing a write operation to the SPI RX/TX buffer transfers the data to the transmit portion of the SPI interface, while a read operation reads the contents of the receive data buffer. The SPI 32-bit receive and transmit data buffers are double buffered to minimize the risk of data collision and to achieve optimal performance.

The SPI RXTX0 register contains bits 7:0 of the SPI interface RX/TX register.

TABLE 105: SPIRXTX0 REGISTER CONTENT FOR NORMAL AND REVERSED TRANSACTIONS

| (         | Operation | SPI Mode  | SPIRXTXx Data is |  |  |

|-----------|-----------|-----------|------------------|--|--|

| <b></b> F | Read      | MSB First | Right Justified  |  |  |

| d br      |           | LSB First | Left Justified   |  |  |

| ١         | Vrite     | MSB First | Left Justified   |  |  |

|           |           | LSB First | Right Justified  |  |  |

When the SPI is configured in master mode, writing to the SPIRXTX0 will trigger a data transmission. For this reason, when the transaction size is larger than 8 bits, the SPIRXTX0 register must be written last.

TABLE 106:SPI RX / TX0 DATA REGISTER - SPIRXTX0 SFR C4H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit | Mnemonic      | Description                                                                                                                                              |

|-----|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SPIRXTX0[7:0] | Read: SPI RXData[7:0] Right justified in normal mode, left justified in bit reversed mode Reading this register, clears the SPIAVF and SPIRXOVF flags    |

|     |               | Write: SPI TXData[7:0] Left justified in normal mode, right justified in bit reversed mode In master mode, writing to SPIRXTX0 triggers the transmission |

<u>www.ramtron.com</u> page 56 of 105

#### TABLE 107:SPI RX / TX1 DATA REGISTER - SPIRXTX1 SFR C5H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit | Mnemonic      | Description                                           |  |  |  |  |  |

|-----|---------------|-------------------------------------------------------|--|--|--|--|--|

| 7:0 | SPIRXTX1[7:0] | Read: SPI RXData[15:8]                                |  |  |  |  |  |

|     |               | Right justified in normal mode, left justified in bit |  |  |  |  |  |

|     |               | reverse mode                                          |  |  |  |  |  |

|     |               | Write: SPI TXData[15:8]                               |  |  |  |  |  |

|     |               | Left justified in normal mode, right justified in bit |  |  |  |  |  |

|     |               | reverse mode                                          |  |  |  |  |  |

#### TABLE 108: SPI RX / TX2 DATA REGISTER - SPIRXTX2 SFR C6H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit | Mnemonic      | Description                                                                                  |  |  |  |  |  |

|-----|---------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7:0 | SPIRXTX2[7:0] | Read: SPI RXData[23:16] Right justified in normal mode, left justified in bit                |  |  |  |  |  |

|     |               | Right justified in normal mode, left justified in bit reverse mode  Write: SPI TXData[23:16] |  |  |  |  |  |

|     |               | Left justified in normal mode, right justified in bit reverse mode                           |  |  |  |  |  |

#### TABLE 109:SPI RX / TX3 DATA REGISTER - SPIRXTX3 SFR C7H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit | Mnemonic      | Description                                           |

|-----|---------------|-------------------------------------------------------|

| 7:0 | SPIRXTX3[7:0] | Read: SPI RXData[31:24]                               |

|     |               | Right justified in normal mode, left justified in bit |

|     |               | reverse mode                                          |

|     |               | Write: SPI TXData[31:24]                              |

|     |               | Left justified in normal mode, right justified in bit |

|     |               | reverse mode                                          |

### 9.14 SPI Data Input /Output

The VRS51L3074 SPI interface has the ability to perform data transactions in MSB first mode or LSB first. The SPIREVERSE bit of the SPISTATUS register controls whether the data will be transmitted MBS first or LSB first. Upon device reset, the SPIREVERSE bit equals 0 and data is transmitted in MSB first format.

The SPIREVERSE bit state will also affect the data transmission and the data reception buffer structure as shown in the following diagrams.

FIGURE 24: SPI TRANSACTION STANDARD MODE (SPIREVERSE = 0: MSB FIRST)

FIGURE 25: SPI TRANSACTION BIT REVERSE MODE (SPIREVERSE = 1: LSB FIRST)

The next tables gives examples of SPI transmission and reception in different modes if the SPI SDO pin is connected to the SDI pin.

### SPISIZE = 0x0F (16 bit) / SPIREVERSE= 0 (MSB First

| SPIT | SPIRX | ([3:0] |     |    |    |     |     |

|------|-------|--------|-----|----|----|-----|-----|

| XX   | XX    | D3h    | 42h | XX | XX | 42h | D3h |

|      |       |        |     |    |    |     |     |

| XX   | XX    | 54h    | A6h | XX | XX | A6h | 54h |

## SPISIZE = 0x0F (32 bit) / SPIREVERSE= 0 (MSB First

| SPIL | X [3:0] |     |     | SPIRX |     |     |     |

|------|---------|-----|-----|-------|-----|-----|-----|

| 45h  | A3h     | B2h | DF  | DFh   | B2h | A3h | 45h |

|      |         |     |     |       |     |     |     |

| C3h  | 8Ah     | 49h | 24h | 24h   | 49h | 8Ah | C3h |

| SPIS | IZE =   | 0x0F (3 | 32 bit) / | EVERSE= 1 (LSB First |       |       |     |     |

|------|---------|---------|-----------|----------------------|-------|-------|-----|-----|

| SPIT | X [3:0] |         |           |                      | SPIRX | [3:0] |     |     |

| 45h  | A3h     | B2h     | DF        |                      | DFh   | B2h   | A3h | 45h |

|      |         |         |           |                      |       |       |     |     |

| C3h  | 8Ah     | 49h     | 24h       |                      | 24h   | 49h   | 8Ah | C3h |

|      |         |         |           |                      |       |       |     |     |

page 57 of 105 www.ramtron.com

## 9.14.1 Performing Variable-Bit Data Transmission

For a variable-bit data transmission in master mode (when the data is not transmitted in multiples of 8 bits), the most significant bit of the data to be transmitted must first be placed at position 7 of the SPIRXTXO, with the remaining bits positioned as shown in the SPI transaction figures on the previous page.

For example if SPISIZE = 0x0B and SPIREVERSE = 0, the data transaction will measure 12 bits, MSB first. For the transmission to occur in the correct order, the lower 4 data bits must first be placed into bit positions 7:4 of the SPIRXTX1 register, with bits 11:8 written into bit position 7:0 of the SPIRXTX0 register. This will trigger the transmission.

The following is a sequence of steps to transmit 12 bits of data contained in an integer variable called *txmitdata*.

- Clear the SPIRXTX3 and SPIRXTX2 registers (optional)

- 2. Put the lower quartet of the 12-bit data (bits 3:0) into the upper quartet of the SPIRXTX1 register

- 3. Write bit 7:0 of the 12-bit data into the SPIRXTX0 register

- 4. This will trigger a data transmission

#### In C, this is expressed as follows:

```

(...)

SPIRXTX3 = 0x00;

SPIRXTX2 = 0x00;

SPIRXTX1 = (txmitdata << 4)&0xF0;

//Write the lower quartet of data

//into the upper quartet of SPIRXTX1 register

readflag = SPIRXTX0

//-Dummy Read the SPI RX buffer to clear the RXAV Flag

//(Facultative if SPINOCS is monitored)

SPIRXTX0 = dacdata >> 4;

//Writing to SPIRXTX0 will trigger the transmission

```

For example to output 0x3A2 through the SPI interface configured in master mode and MSB first format, write 0x20 into the SPIRXTX1 SFR register and followed by 0xA2 into the SPIRXTX0 register.

The reception of non multiple of 8 data when the SPI interface is configured to MSB first transaction is very straight forward as the data enters into the receiving buffer through the bit 0 of the SPIRXTX0 register and propagates towards the bit 7 of SPIRXTX3 register.

### 9.15 SPI Example Programs

## 9.15.1 UART to SPI Data Transmission Example

<u>www.ramtron.com</u> page 58 of 105

#### 9.16 SPI Interface to 12-Bit ADC and DAC

The following example program shows the initialization and use of the SPI module of the VRS51L3074 as an interface to serial ADC and DAC.

```

.... // VRS51L3074_Generic_SPI_based_ADC_DAC_Interf1.c

// DESCRIPTION

This Program demonstrates the configuration and use of the SPI interface

for interface to typical serial 12 bit A/D and D/A Converters.

The program read the A/D and output the read value out on a D/A converter To perform the conversion the ADC requires 16 clock cycles and

the DAC requires 12 clock cycles

#include <VRS51L3074_SDCC.h>

//---Functions prototypes

void ReadGEN_12BIT_ADC(void);

void WriteGEN_12BIT_DAC(unsigned int );

//GEN_12BIT_ADC Read

//GEN_12_BIT_DAC Write

void V2KDelay1ms(unsigned int);

//Standard Delay function

// Global variables definitions

idata unsigned char cptr = 0x00:

unsigned int at 0x0060 adcdata= 0x00;

MAIN FUNCTION

void main (void) {

ReadGEN_12BIT_ADC();

//Read the A/D Converter

WriteGEN_12BIT_DAC(adcdata);

//write into the D/A Converter

}// End of main

// NAME:

ReadGEN 12BIT ADC

// DESCRIPTION:

Read the GEN_12BIT_ADC A/D

ADC is connected to SPI interface using CS0 Max clk speed is 3.2MHz, Fosc = 40MHz assumed

void ReadGEN 12BIT ADC()

int cptr = 0x00;

char readflag = 0x00;

//SPI Configuration Section

//(Can be moved to Main function if only one device is connected to the SPI Interface)

//Make sure the SPI Interface is activated

PERIPHEN1 |= 0xC0;

//--Wait activity stops on the SPI interface (Monitor SPINOCS) while(!(SPISTATUS &= 0x08));

SPICTRL = 0x65;

//SPICLK = /16 (2.5MHz)

//CS0 Active

//SPI Mode 1 Phase = 1, POL = 0

//SPI Master Mode

SPICONFIG = 0x40;

//Clear SPIUNDEFC Flag

//SPILOAD = 0 -> Manual CS3 behaviour

//No SPI Interrupt used

SPISTATUS = 0x00;

//SPI transactions are in MSB First Format

SPISIZE = 0x0E;

//SPI Transaction Size are 15 bit

//-Dummy Read the SPI RX buffer to clear the RXAV Flag

readflag = SPIRXTX0;

//-Perform the SPI read SPIRXTX0 = 0x00;

//Writing to the SPIRXTX0 will trigger the SPI

while(!(SPISTATUS &= 0x02));

//Wait for the SPI RX AV Flag being set

```

```

// -- It is possible to monitor the SPINOCS Flag instead of the SPIRXAV Flag

//The code piece below shows how to do it. However in that case.

//No that the reading of the SPISTATUS register must be done at

//least 4 System clock cycles after the Write operation to the SPIRXTX0 register

//-Wait for SPINOCS Flag have time to be updated

NOP

endasm

while(!(SPISTATUS &= 0x08));

//Wait activity stops on the SPI interface

//Read SPI data

adcdata= (SPIRXTX1 << 8);

adcdata+= SPIRXTX0;

adcdata&= 0x0FFF

//isolate the 12 lsb of the read value

}//end of ReadGEN_12BIT_ADC

// NAME:

WriteGEN 12BIT DAC

// DESCRIPTION

Write 12bit Data into the GEN 12BIT DAC device

ADC is connected to SPI interface using CS1

Max clk speed is 12.5MHz, Fosc = 40MHz assumed

We will set the SPI prescaler to sysclk / 8

void WriteGEN 12BIT DAC(unsigned int dacdata)

char subdata = 0x00

char readflag = 0x00;

PERIPHEN1 |= 0xC0;

//Make sure the SPI Interface is activated

//--Wait activity stops on the SPI interface (Monitor SPINOCS)

while(!(SPISTATUS &= 0x08));

//SPI Configuration Section

//Can be moved to Main function if only one device is connected to the SPI Interface

SPICTRL = 0x4D:

//SPICLK = /8 (MHz)

//CS1 Active

//SPI Mode 1 Phase = 1, POL = 0

//SPI Master Mode

SPICONFIG = 0x40:

//SPI Chip select is automatic

//Clear SPIUNDEFC Flag

//SPILOAD = 0 -> Manual CS3 behaviour

//No SPI Interrupt used

SPISTATUS = 0x00;

//SPI transactions are in MSB First Format

SPISIZE = 0x0B;

//SPI Transaction Size are 12 bit

//-Format the 12 bit data so data bit 11 is positioned on bit 7 of SPIRXTX0 // and data bit 0 is positioned on bit 4 of SPIRXTX1 and Perform the SPI write operation

dacdata &= 0x0FFF:

//Make sure dacdata is <= 0FFFh (12 bit)

SPIRXTX3 = 0x00;

SPIRXTX2 = 0x00:

SPIRXTX1 = (dacdata << 4)&0xF0;

//-Dummy Read the SPI RX buffer to clear the RXAV Flag

// (Facultative if SPINOCS is monitored)

readflag = SPIRXTX0;

SPIRXTX0 = dacdata >> 4:

//Writing to SPIRXTX0 will trigger the transmission

//--Wait the SPI transaction completes

This section can be omitted if a check of activity on the SPI Interface

is made before each access to it in master mode

//Wait for the SPI RX AV Flag being set

while(!(SPISTATUS &= 0x02));

// -- It is possible to monitor the SPINOCS Flag instead of the SPIRXAV Flag

//The code piece below shows how to do it. However in that case,

//No that the reading of the SPISTATUS register must be done at

//least 4 System clock cycles after the Write operation to the SPIRXTX0 register

//-Wait for SPINOCS Flag have time to be updated

NOP:

_endasm;

//--Wait activity stops on the SPI interface (monitor SPINOCS Flag) while(!(SPISTATUS &= 0x08));

}//end of WriteGEN 12BIT DAC

```

<u>www.ramtron.com</u> page 59 of 105

## 10 I<sup>2</sup>C Interface

The VRS51L3074 includes an I<sup>2</sup>C interface that can operate in master and slave mode. In master mode, the communication speed on the I<sup>2</sup>C is programmable, optimizing communication between I<sup>2</sup>C-based devices. Long or heavily loaded I<sup>2</sup>C bus applications are likely to require slower communication speeds.

#### 10.1 I2C Bus Pull-Up Resistors

By definition, the I<sup>2</sup>C requires that the user include external pull-up resistors on the SCL and SDA lines. The pull-up voltage can be either 3.3 or 5 volts. Note that the VRS51L3074 I/Os are 5V-tolerant making it possible to interface 5V, I<sup>2</sup>C-based devices with the VRS51L3074.

The proper value for the pull-up resistor and the proper communication speed depend on bus characteristics such as length and capacitive load.

Note that the pull-up resistor value should not be below 1.25K ohms if running the I<sup>2</sup>C bus at 5V; and 750 ohms if operating at 3.3V. This is required in order to limit the current to 4mA (maximum current of the I/O port connected to the I<sup>2</sup>C interface).

#### 10.2 I2C Phases

The I<sup>2</sup>C protocol includes five phases:

- 1. IDLE (SCL = 1, SDA = 1)

- 2. Device ID

- 3. Device ID Acknowledge

- 4. Data

- 5. Data Acknowledge

The VRS51L3074 I<sup>2</sup>C interface has provisions to monitor activity on the I<sup>2</sup>C bus, particularly the data acknowledge phase of a I<sup>2</sup>C transaction. There is also a mechanism that enables the detection of communication errors.

## 10.3 I<sup>2</sup>C Control and Status Registers

Four SFR registers are dedicated to the I<sup>2</sup>C interface. The I<sup>2</sup>C configuration register I2CCONFIG enables:

- Selection of master or slave operation

- Forcing a start condition after an acknowledge phase

- Manual control of the SCL line

- Activation of the master arbitration monitoring mechanism

- Interrupt activation

TABLE 110:12C CONFIGURATION REGISTER - 12CCONFIG SFR D1H

|   |     |     |     | Valata | 40000000000 |     | State of the latest and the latest a |     |

|---|-----|-----|-----|--------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 7   | 6   | 5   | 4      | 3           | 2   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   |

|   | R/W | R/W | R/W | R/W    | R/W         | R/W | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W |

| ı | 0   | 0   | 0   | 0      | 0           | 1   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0   |

| Bit | Mnemonic   | Description                                                                                                     |  |  |  |  |

|-----|------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

|     | (CE)       | Description                                                                                                     |  |  |  |  |

| 7   | MASTRARB   | Master Lost Arbitration and Mechanism and                                                                       |  |  |  |  |

|     |            | Interrupt                                                                                                       |  |  |  |  |

|     |            | 0 = Deactivated                                                                                                 |  |  |  |  |

|     |            | 1 = Master lost arbitration monitoring and                                                                      |  |  |  |  |

|     | I2CRXOVEN  | interrupt is enabled                                                                                            |  |  |  |  |

| 6   | IZCRXOVEN  | I <sup>2</sup> C RX Overrun Interrupt Enable                                                                    |  |  |  |  |

|     |            | 0 = I <sup>2</sup> C RX Overrun interrupt is deactivated                                                        |  |  |  |  |

| E   | I2CRXAVEN  | 1 = I <sup>2</sup> C RX Overrun interrupt is enabled I <sup>2</sup> C RX Available Interrupt Enable             |  |  |  |  |

| 5   | IZCRXAVEN  | 0 = I <sup>2</sup> C RX Available interrupt is deactivated                                                      |  |  |  |  |

| 4   |            | 1 = I <sup>2</sup> C RX Available interrupt is deactivated                                                      |  |  |  |  |

| 4   | I2CTXEEN   | I <sup>2</sup> C TX Empty Interrupt Enable                                                                      |  |  |  |  |

| 4   | IZCIAEEN   | 0 = I <sup>2</sup> C TX empty interrupt is deactivated                                                          |  |  |  |  |

|     | w.         | 1 = I <sup>2</sup> C TX empty interrupt is enabled                                                              |  |  |  |  |

| 3   | I2CMASTART | I <sup>2</sup> C Master Create Start                                                                            |  |  |  |  |

|     | 1.20       | 0 = No start condition is created after data                                                                    |  |  |  |  |

|     |            | acknowledge phase                                                                                               |  |  |  |  |

| 37  |            | 1 = Master will create a start condition after the                                                              |  |  |  |  |

|     |            | next data acknowledge phase                                                                                     |  |  |  |  |

|     |            | This bit will be cleared when the I <sup>2</sup> C is idle                                                      |  |  |  |  |

| 2   | 12CSCLLOW  | Keep the I <sup>2</sup> C SCL Low                                                                               |  |  |  |  |

|     |            | Setting this bit to 1 will force the SCL line low.                                                              |  |  |  |  |

|     |            | This bit is read by the I <sup>2</sup> C interface when it                                                      |  |  |  |  |

|     |            | enters in the data I <sup>2</sup> C.                                                                            |  |  |  |  |

|     |            | This bit must not be set during the acknowledge                                                                 |  |  |  |  |

|     |            | phase.                                                                                                          |  |  |  |  |

| 1   | 12CRXSTOP  | I <sup>2</sup> C Reception Stop                                                                                 |  |  |  |  |

|     |            | 0 = The I <sup>2</sup> C received will acknowledge after                                                        |  |  |  |  |

|     |            | receiving a byte                                                                                                |  |  |  |  |

|     |            | 1 = The I <sup>2</sup> C receiver will not acknowledge after                                                    |  |  |  |  |

| 0   | I2CMODE    | the next data byte is received  I2C Mode Enable                                                                 |  |  |  |  |

| U   | IZCIVIODE  |                                                                                                                 |  |  |  |  |

|     |            | 0 = I <sup>2</sup> C interface operates in slave mode<br>1 = I <sup>2</sup> C Interface operates in master mode |  |  |  |  |

| L   | 1          | i – i o interiace operates in master mode                                                                       |  |  |  |  |

The I2CMODE bit of the I2CCONFIG register, when set to 1, will configure the I<sup>2</sup>C interface as a master.

In master mode, the VRS51L3074  $I^2C$  interface controls the  $I^2C$  bus and initiates transmission and reception transactions. In master mode, the  $I^2C$  interface also controls the communication speed.

Clearing the I2CMODE bit of the I2CCONFIG register will configure the I<sup>2</sup>C interface as a slave. Slave mode can be useful for applications in which the

www.ramtron.com page 60 of 105

VRS51L3074 operates as a peripheral in a host-controlled system.

When in master mode, the I<sup>2</sup>C interface can be forced to generate a start condition after the next data acknowledge phase. This is done by setting the I2CMASTART bit to 1.

When the MASTRARB bit is set to 1, communications of the I<sup>2</sup>C will be monitored and an interrupt will be generated if arbitration with slave devices on the bus is lost. The interrupt flag associated with this process is the I2CERROR bit of the I2CSTATUS register.

If the I2CRXSTOP bit is set to 1, the I<sup>2</sup>C interface will not acknowledge after reception of the next byte, but will generate a stop condition instead. This will, in effect, end the transaction with the master device.

When the I<sup>2</sup>C interface is configured as a master and the I2CSCLLOW bit of the I2CCONFIG register is set to 1, the SCL line will be driven low during the next data acknowledge phase. This feature enables the user to add the equivalent of wait states to the transfer in order to support "slow" devices connected to the I<sup>2</sup>C bus.

The I<sup>2</sup>C interface includes support for four interrupt conditions via two interrupt vectors.

- RX Data Available

- RX Overrun

- TX Empty

- Master lost arbitration

The following table summarizes the possible interrupt sources at the I<sup>2</sup>C interface level.

TABLE 111: I<sup>2</sup>C INTERRUPT SOURCES

| I <sup>2</sup> C Interrupt | I2CCONFIG bit<br>(Set to 1 to activate) | Interrupt<br>Vector |

|----------------------------|-----------------------------------------|---------------------|

| RX Data<br>Available       | I2CRXAVEN                               | 4Bh<br>(Int 9)      |

| RX Overrun                 | I2CRXOVEN                               | 0x4B<br>(Int 9)     |

| TX Empty                   | I2CTXEEN                                | 0x4B<br>(Int 9)     |

| Master Lost<br>Arbitration | MASTRARB                                | 0x53<br>(Int 10)    |

To activate the I<sup>2</sup>C interface interrupts, the corresponding enable bit of the I2CCONFIG register must be set to 1. This will allow the I<sup>2</sup>C interrupt to propagate to the VRS51L3074's interrupt controller. In order for the I<sup>2</sup>C interrupt to be recognized by the processor, the corresponding bit of the INTEN2 and INTSRC2 registers must be configured accordingly.

See the VRS51L3074 interrupt section for more details.

### 10.4 I<sup>2</sup>C Timing Control Register

The I2CTIMING register controls the communication speed when the I<sup>2</sup>C interface is configured in master mode. When in slave mode, it defines the values of the setup and hold times.

TABLE 112:12C TIMING REGISTER - I2CTIMING SFR D2H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 0   |

| Bit | Mnemonic       | Description                                                              |

|-----|----------------|--------------------------------------------------------------------------|

| 7:0 | I2CTIMING[7:0] | I <sup>2</sup> C master/slave timing configuration register<br>See Below |

The following formulas demonstrate the impact of the I2CTIMING value on the communication speed and setup/hold times.

#### In master mode:

$$SCL period = \frac{12CCLK}{32*(12CTIMING[7:0] + 1)}$$

The following table provides examples of the I2CTIMING values and the corresponding communication speed:

TABLE 113: I<sup>2</sup>C COMMUNICATION SPEED VS. I2CTIMING REGISTER VALUE (FOSC = 40MHz)

| 12CTIMING   | I2C Com Speed |

|-------------|---------------|

| 00h         | 1.25 MHz      |

| 02h         | 416.77 kHz    |

| 0Ch (Reset) | 96.15 kHz     |

| 7Ch         | 10kHz         |

| FFh         | 4.88kHz       |

#### In Slave Mode:

Set-up/Hold Time = I2CCLKperiod \* I2CTIMING[7:0]

In this case, the precision is: 2 x I2CCLKperiod

TABLE 114: I'C SETUP AND HOLD TIME VS. I2CTIMING REGISTER VALUE (FOSC = 40MHz)

| I2CTIMING | Setup/Hold<br>Time |  |  |  |

|-----------|--------------------|--|--|--|

| 00h       | 0 uS               |  |  |  |

| 0Ch       | 0.3 uS             |  |  |  |

| FFh       | 6.38 uS            |  |  |  |

www.ramtron.com page 61 of 105

## 10.5 I<sup>2</sup>C Slave Device ID and Advanced Configuration

When operating in slave mode, the device ID on the I<sup>2</sup>C interface is configurable. The seven upper bits of the I2CIDCFG register contain the user-selected device ID. Bit 0 of the I2CIDCFG register has two distinct roles.

The I2CAVCFG provides advanced control on I<sup>2</sup>C interface operations.

TABLE 115:I<sup>2</sup>C DEVICE ID CONFIGURATION - I2CIDCFG SFR D3H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Bit | Mnemonic   | Description                                                                                                                                                                                                                  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | I2CID[6:0] | Slave I <sup>2</sup> C device ID as selected by user                                                                                                                                                                         |

| 0   | I2CADVCFG  | Read: Indicates that the I <sup>2</sup> C slave has received ID that is different from the I2CID. This flag is cleared when the received ID corresponds with the I2CID                                                       |

|     |            | Writing: Slave Mode: 1= The I2CRXAV flag is raised when the I²C slave receives a device ID Master Mode: 1 = Enables monitoring of the SCL line in wait state mode in case of mismatch of the SCL line vs. the expected value |

When the I<sup>2</sup>C interface operates in master mode and the I2CADVCFG is cleared, the I<sup>2</sup>C interface module will continuously monitor the SCL line. If the slave device drives the SCL line into an incorrect state, the I<sup>2</sup>C interface will enter wait state mode until the slave device releases the SCL line. This mode can be useful for a I<sup>2</sup>C communication debug.

When the I2CADVCFG bit is set, no monitoring of the SCL line will be executed by the I<sup>2</sup>C module and the transaction will proceed independently of the level of the SCL line.

When the VRS51L3074 I<sup>2</sup>C interface module is configured as a slave, reading the I2CADVCFG bit as 1 indicates that the ID received does not match the current device ID. This bit will be cleared when the correct device ID is received.

In slave mode, writing a 1 into the I2CADVCFG bit of the I2CIDCFG register will make the I2CRXAVF flag of the I2CSTATUS register remain at 0, after the device ID is received. If the I2CADVCFG bit is cleared, the I2CRXAVF flag will be set either when a correct device ID, or when valid data, are received.

### 10.6 I<sup>2</sup>C Status Register

Monitoring of the I<sup>2</sup>C interface can be done via the I2CSTATUS register located at SFR address D4h. The I2CSTATUS register is read only and values written into that location have no effect.

The I2CERROR flag indicates that an error condition occurred on the I<sup>2</sup>C interface. In master mode, the I2CERROR flag will be set by the VRS51L3074 I<sup>2</sup>C interface, if it loses bus arbitration.

In slave mode, if an unexpected stop is received, the I2CERROR flag will be set. The I2CERROR flag will be automatically reset by the I2C interface the next time it exits an idle state.

If the I2CNOACK flag is set to 1, it signifies that the slave device did not acknowledge the last data byte it received.

The I<sup>2</sup>C interface also monitors the synchronization of the SDA line. When synchronization is lost, the I2CSDASYNC bit of the I2CSTATUS register will be set by the I<sup>2</sup>C interface.

The I2CSDASYNC bit of the I2CSTATUS register returns the value of the SDA line the moment a read operation is performed on the I2CSTATUS register.

The I2CACKPH bit when set, indicates that the I<sup>2</sup>C interface is currently in the data acknowledge phase.

Reading of the I2CSDASYNC and I2CCKPH bits can be used to determine whether the slave device has acknowledged. If both bits are set to 1 at a given time, the slave device did not acknowledge.

<u>www.ramtron.com</u> page 62 of 105

#### TABLE 116: I2C STATUS REGISTER - I2CSTATUS SFR D4H

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| R | R | R | R | R | R | R | R |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 |

|     | T          | 1 =                                                                                                                                      |  |  |  |

|-----|------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit | Mnemonic   | Description                                                                                                                              |  |  |  |

| 7   |            | Slave Mode Error Flag:                                                                                                                   |  |  |  |

|     |            | 0 = No Error                                                                                                                             |  |  |  |

|     |            | 1 = Indicates that the I <sup>2</sup> C interface received an                                                                            |  |  |  |

|     |            | unexpected stop                                                                                                                          |  |  |  |

|     |            | This flag is reset the next time the I <sup>2</sup> C interface                                                                          |  |  |  |

|     | I2CERROR   | exits from an idle state (see below)                                                                                                     |  |  |  |

|     |            | Master Mode                                                                                                                              |  |  |  |

|     |            | 0 = No Arbitration Error                                                                                                                 |  |  |  |

|     |            | 1 = I <sup>2</sup> C interface has lost arbitration                                                                                      |  |  |  |

|     |            | This flag is reset the next time the I <sup>2</sup> C interface                                                                          |  |  |  |

| _   | 1001101016 | exits from an idle state (see below)                                                                                                     |  |  |  |

| 6   | I2CNOACK   | I <sup>2</sup> C Acknowledge Error Flag                                                                                                  |  |  |  |

|     |            | 0 = Acknowledge was received normally                                                                                                    |  |  |  |

|     |            | 1 = No acknowledge was received during the                                                                                               |  |  |  |

|     |            | last acknowledge phase This flag is reset the next time the I <sup>2</sup> C interface                                                   |  |  |  |

|     |            | exit from the idle state (see below)                                                                                                     |  |  |  |

| 5   | I2CSDASYNC |                                                                                                                                          |  |  |  |

| 5   | IZCODASTNC | I <sup>2</sup> C SDA Sync Status Flag                                                                                                    |  |  |  |

|     |            | 0 = SDA Pin in not in sync<br>1 = SDA pin is in sync                                                                                     |  |  |  |

| 4   | I2CACKPH   |                                                                                                                                          |  |  |  |

| 4   | IZCACKPH   |                                                                                                                                          |  |  |  |

|     |            | When set, this flag indicates that the I <sup>2</sup> C interface is in 'Data Acknowledge Phase.' 5 phases of I <sup>2</sup> C protocol: |  |  |  |

|     |            | 1 Idle                                                                                                                                   |  |  |  |

|     |            | 2. Device ID                                                                                                                             |  |  |  |

|     |            | Device ID Acknowledge                                                                                                                    |  |  |  |

|     |            | 4. Data                                                                                                                                  |  |  |  |

|     |            | 5. Data Acknowledge                                                                                                                      |  |  |  |

| 3   | I2CIDLEF   | I <sup>2</sup> C is idle                                                                                                                 |  |  |  |

|     |            | 0 = I <sup>2</sup> C interface is communicating                                                                                          |  |  |  |

|     |            | 1 = I <sup>2</sup> C interface is inactive (idle phase) and the                                                                          |  |  |  |

|     |            | SCL and SDA lines are high                                                                                                               |  |  |  |

| 2   | I2CRXOVF   | I <sup>2</sup> C RX Overrun Interrupt Flag                                                                                               |  |  |  |

|     |            | 0 = No I <sup>2</sup> C RX overrun condition detected                                                                                    |  |  |  |

|     |            | 1 = I <sup>2</sup> C data collision occurred                                                                                             |  |  |  |

| 1   | I2CRXAVF   | I <sup>2</sup> C RX Available interrupt Flag                                                                                             |  |  |  |

|     |            | 0 = I <sup>2</sup> C receive buffer is empty                                                                                             |  |  |  |

|     |            | 1 = Data is present in the I2C RX buffer                                                                                                 |  |  |  |

| 0   | I2CTXEMPF  | I <sup>2</sup> C TX Empty interrupt Flag                                                                                                 |  |  |  |

|     |            | 0 = I <sup>2</sup> C transmit buffer is full                                                                                             |  |  |  |

|     |            | 1 = I <sup>2</sup> C transmit buffer is ready to receive new                                                                             |  |  |  |

|     |            | data                                                                                                                                     |  |  |  |

When set, the I2CIDLEF indicates that the I<sup>2</sup>C bus is idle and that a transaction can be initiated. Before initiating an I<sup>2</sup>C data transfer, it is recommended to check the state of the I2CIDLEF bit. This bit indicates whether or not a data transfer is currently in progress.

When new data is received in the I<sup>2</sup>C receive buffer, the I2CRXAVF interrupt flag will be set. Data must be retrieved from the I2CRXTX buffer before the reception of the next data byte is complete.

The I2CRXOVF flag when set, indicates an overrun condition in the I<sup>2</sup>C interface receive buffer and the data is potentially corrupted.

The I2CTXEMPF interrupt flag is set by the I<sup>2</sup>C interface when the transmit data buffer is ready to receive another data byte.

### 10.7 I<sup>2</sup>C Transmit/Receive register

The I<sup>2</sup>C interface transmit and receive buffers are accessed via the I2CRXTX SFR register, which is accessible at SFR address D5h.

TABLE 117:I<sup>2</sup>C DATA RX / TX REGISTER I2CRXTX - SFR D5H

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

|     |     |     |     |     |     |     |     |

| Bit | Mnemonic     | Description                                                                                                 |

|-----|--------------|-------------------------------------------------------------------------------------------------------------|

| 7:0 | I2CRXTX[7:0] | Read: I <sup>2</sup> C Receive Buffer Reading the I2CRXTX register will clear the I2CRXAV and I2CRXOV flags |

|     |              | Write: I <sup>2</sup> C Transmit Buffer  Writing into the I2CRXTX register will trigger the transmission    |

## 10.8 I2C Interface alternate pins

Upon reset, the I<sup>2</sup>C interface signal SCL and SDA are mapped into pins P3.4 and P3.5, respectively. However it is also possible to map these signal into the P1.6 and P1.7 pins.

Bit 5 of the DEVIOMAP register (SFR E1h) is used to configure the mapping of the I<sup>2</sup>C interface at the I/O level, as shown in the following table:

TABLE 118: I2C MODULE MAPPING

| DEVIOMAP.5 Bit Value | SCL<br>Mapping | SDA<br>Mapping |

|----------------------|----------------|----------------|

| 0 (Reset)            | P3.4           | P3.5           |

| 1                    | P1.6           | P1.7           |

www.ramtron.com page 63 of 105

## 10.9 I<sup>2</sup>C Interface Example Programs

The following programs provide example code for I<sup>2</sup>C control of EEPROM devices

```

// VRS2k-I2C _EEPROM.c //

// This example program demonstrate the use of the I2C

// interface to perform basic read and write operations on a

// Standard EEPROM device.

#include <VRS51L3074_SDCC.h>

//----Global variables -----//

//general purpose counter

int cptr = 0x00:

// --- Function prototypes char EERandomRead(char,int);

char EERandomWrite(char, char, int); void WaitTXEMP(void);

void WaitRXAV(void);

void WaitI2CIDLE(void);

void wait();

- MAIN FUNCTION

void main (void){

PERIPHEN1 = 0x20;

//Enable I2C Interface

INTCONFIG = 0x02;

//Erase Bypass global int, before configuring the INT0 pin event

//This fix inadvertent INT0 interrupt that occurs when

//INT0 cause is set to Rising edge

//INT0 vector source = INT0 pin

//Set INT0 sensitive on edge(1) or Level(0)

//Set INT0 Pin sensitivity on Normal Level(0) / Inverted (1)

INTSRC1 = 0x01;

INTPINSENS1 = 0x01;

INTPININV1 = 0x00;

INTEN1 = 0x01:

//Enable INT0 (bit0) Interrupt

INTCONFIG = 0x01;

//Enable Global interrupt

while(1)

}//end of Main

--- Interrupt Functions

-- Interrupt INT0 --

void INT0Interrupt(void) interrupt 0

char x:

//-- Send I2C stuff

// Init cptr to pint to message beginning //Disable Interrupts

cptr = 0x00:

INTEN1 = 0x00;

x = EERandomWrite(0xA0, 0x36, 0x0206);

//Perform Write operation

Delay1ms(100);

x = EERandomRead( 0xA0, 0x0206);

//Perform Read operation

INTEN1 = 0x01

//Enable Interrupt INT0

}//end of INT0 interrupt

- Individual Functions

//--- Function EERandomRead(char eeidw,int address) -----//

char EERandomRead(char eeidw,int address){

I2CTIMING = 0x20; // I2C Clock Sp

// I<sup>2</sup>C Clock Speed = about 100kHz

I2CCONFIG = 0x01;

//Write I2C device ID + W

I2CRXTX = eeidw;

WaitTXEMP();

I2CRXTX = address >> 8: //Write I2C ADRSH

WaitTXEMP();

```

```

I2CRXTX = address;

//Write I2C ADRSL

//--Wait for I2C IDLE (This will generate a STOP)

WaitI2CIDLE();

-Start a Preset ADRS read (This will generate a START)

I2CRXTX = eeidw+1;

//Write I2C device ID + R

WaitTXEMP();

12CCONFIG |= 0x02;

//Force I2C to Not Acknowledge after

//receiving the next data byte

WaitRXAV();

//Wait for RX Available bit, This will trigger I2C Reception

return I2CRXTX:

//Return Data Byte

}//End of EERandomRead

--- Function EERandomWrite(char eeid,char data, int address)

char EERandomWrite(char eeidw, char eedata, int address)

// I<sup>2</sup>C Clock Speed = about 100kHz //I<sup>2</sup>C is Master

I2CTIMING = 0x20:

I2CCONFIG = 0x01;

I2CRXTX = eeidw;

//Write I2C device ID + W

WaitTXEMP();

I2CRXTX = address >> 8; //Write I2C device ID + W

WaitTXEMP();

//Write I2C device ID + W

WaitTXEMP();

I2CRXTX = eedata;

//Write I2C device data

WaitTXEMP():

return I2CRXTX:

//Return Data Byte

}//End of EERandomWrite

--- Function WaitTXEMP() ---

void WaitTXEMP()

wait();

USERFLAGS = I2CSTATUS;

USERFLAGS &= 0x01;

//isolate the I2C TX EMPTY flag

}while( USERFLAGS == 0x00);

//Wait for I2C TX EMPTY

}//end of Void WaitTXEMP()

----- Function WaitRXAV() -

void WaitRXAV()

wait();