# High-Efficiency Full Bridge Buck-Boost DC/DC Controller

### **General Description**

The VP3679 is a high efficiency full-bridge buckboost DC/DC controller designed for use in voltage step-up or step-down converting application. It operates over a wide input range from 4.2V to 55V and is capable of adjusting output voltage to 55V. Current mode control scheme also makes it wide bandwidth and good transient response. The operating frequency can be adjusted simply with an external resistor or any external clock source between 100kHz and 600kHz. Its internal gate driver provides 5A peak current driving capability.

The VP3679 also provides input/output average current sensing and limiting function, optional CCM/DCM operation, optional EMI improvement and power status indication pin. This device features lots of protection such as cycle-by-cycle current limiting, input under-voltage lockout, output over voltage, short, over-temperature and Applications optional hiccup mode in sustained overload conditions. Programmable soft-start circuitry reduces the inrush current at start-up.

#### **Features**

- 4-Switch Step-Up/Step-Down Operation

- Wide Input Voltage from 4.2V to 55V

- Adjustable Output Voltage from 0.8V to 55V

- Adjustable 100kHz~600kHz Clock Frequency

- Optional Frequency Synchorization/Dithering

- 5A Peak Current Limit Using Internal Driver

- Current Mode Operation

- External RC Compensation

- Programmable Soft-Start and Input UVLO

- High Efficiency at Light Loads

- Power Good Indication

- Output Over-Voltage Protection

- **Output Short Voltage Protection**

- Current Limit and Over Temperature Protection

- TSSOP28EP Exposed Pad and QFN32 5x5 Green Package with RoHS Compliant

- USB Power Delivery

- Industrial Power Supplies

- Battery and Super-Capacitor Charging

- LED Lighting

- Automotive Start/Stop Systems

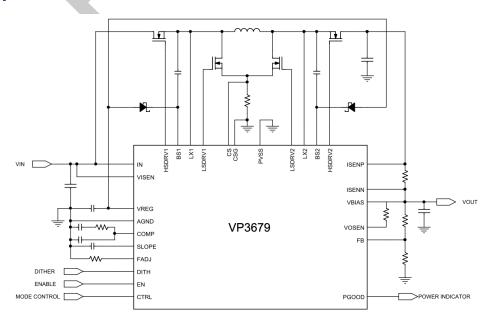

## Typical Application

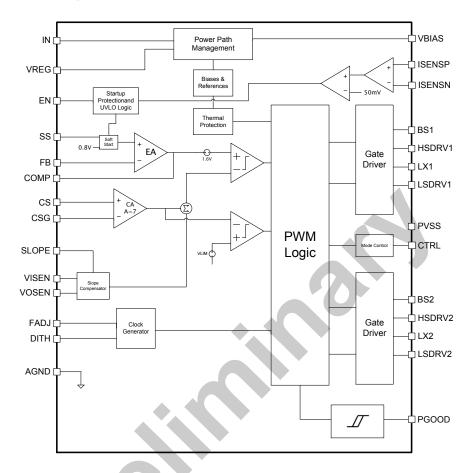

# **Functional Block Diagram**

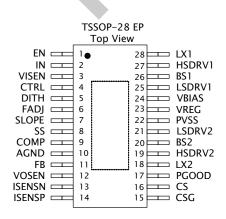

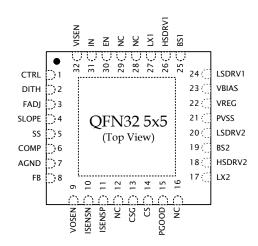

# **Pin Assignments**

# **Pin Descriptions**

| TSSOP | QFN | Pin     | I/O/P | Function Description                                                                                                                                                                                                                  |

|-------|-----|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     |         |       | Chip Enable. For EN<0.73V, the VP3679 enters shutdown mode. For                                                                                                                                                                       |

| 1     | 30  | EN      | 1     | 0.73V <en<1.24v, but="" en="" enabled="" for="" is="" no="" pwm="" switching.="" vreg="">1.24V, PWM</en<1.24v,>                                                                                                                       |

|       |     |         |       | switching is enabled. TTL Logic levels with compliance to $V_{IN}$ .                                                                                                                                                                  |

| 2     | 31  | IN      | Р     | Power Supply Input. Connect this pin to power supply.                                                                                                                                                                                 |

| 3     | 32  | VISEN   | I     | Input Voltage Sense Input. Connect this pin close to input capacitors.                                                                                                                                                                |

| 4     | 1   | CTRL    | ı     | Mode Control. Connect a resistor to ground to configure CCM/DCM operation and hiccup mode. See functional description for setting table.                                                                                              |

| 5     | 2   | DITH    | I     | Frequency Dithering Adjust. Connect a capacitor to ground to make the VP3679 PWM modulation frequency swing in $\pm 5\%$ of the frequency specified by FADJ external resistor. Leave this pin unconnected for disabling this feature. |

| 6     | 3   | FADJ    | I     | Frequency Adjust or Synchronization. A resistor connected from this pin to ground simply sets the oscillator frequency. An external clock signal at this pin will synchronize the controller.                                         |

| 7     | 4   | SLOPE   | ı     | Slope Compensation. Connect a capacitor to ground to perform slope compensation for buck-boost operating stabilization.                                                                                                               |

| 8     | 5   | SS      | I     | Soft-Start Programming. Connect a capacitor to ground to program the soft-start time.                                                                                                                                                 |

| 9     | 6   | COMP    | 0     | Compensation. Use a Type II RC//C network to do proper loop compensation.                                                                                                                                                             |

| 10    | 7   | AGND    | Р     | Analog Ground.                                                                                                                                                                                                                        |

| 11    | 8   | FB      | I     | Output Feedback. Connect the external resistor divider network from output to this pin to sense output voltage.                                                                                                                       |

| 12    | 9   | VOSEN   | I     | Output Voltage Sense Input. Connect this pin close to output capacitors.                                                                                                                                                              |

| 13    | 10  | ISENSN  | I     | Average Current Limit Negative Input.                                                                                                                                                                                                 |

| 14    | 11  | ISENSP  | I     | Average Current Limit Positive Input.                                                                                                                                                                                                 |

| 15    | 13  | CSG     | I     | Negative Current Amplifier Input.                                                                                                                                                                                                     |

| 16    | 14  | CS      | _     | Positive Current Amplifier Input.                                                                                                                                                                                                     |

| 17    | 15  | PGOOD   | OD    | Power Good Indicator (Open Drain). PGOOD is pulled low if FB pin is outside specified $V_{FB}$ regulation.                                                                                                                            |

| 18    | 17  | LX2     |       | 2nd Switching Node. LX2 is the 2nd switching node.                                                                                                                                                                                    |

| 19    | 18  | HSDRV2  | 0     | 2nd High-Side Drive Pin.                                                                                                                                                                                                              |

| 20    | 19  | BS2     | -     | Bootstrap I/O for 2nd High-Side Switch.                                                                                                                                                                                               |

| 21    | 20  | LSDRV2  | 0     | 2nd Low-Side Drive Pin.                                                                                                                                                                                                               |

| 22    | 21  | PVSS    | Р     | Power Ground. The ground connection to all low-side gate drivers.                                                                                                                                                                     |

| 23    | 22  | VREG    | 0     | Internal Regulator. Connect a capacitor to ground.                                                                                                                                                                                    |

| 24    | 23  | VBIAS   | I     | Output Bias Connection. Connect this pin to output to improve efficiency.                                                                                                                                                             |

| 25    | 24  | LSDRV1  | 0     | 1st Low-Side Drive Pin.                                                                                                                                                                                                               |

| 26    | 25  | BS1     | ı     | Bootstrap I/O for 1st High-Side Switch.                                                                                                                                                                                               |

| 27    | 26  | HSDRV1  | 0     | 1st High-Side Drive Pin.                                                                                                                                                                                                              |

| 28    | 27  | LX1     | ı     | 1st Switching Node. LX1 is the 1st switching node.                                                                                                                                                                                    |

| _     | _   | Exposed | Р     | Thermal Ground. The pad should be soldered to the analog ground with low                                                                                                                                                              |

|       |     | Pad     | •     | thermal resistance.                                                                                                                                                                                                                   |

# **Absolutely Maximum Ratings**

Over operating free-air temperature range, unless otherwise specified (\* 1)

| Symbol                                                    | Parameter                                     | Limit                              | Unit |

|-----------------------------------------------------------|-----------------------------------------------|------------------------------------|------|

| V <sub>IN</sub>                                           | Supply voltage range                          | -0.3 to 60                         | V    |

| V <sub>IN(HV)</sub> (EN/VISEN/VOSEN/<br>ISENSP/ISENSN)    | High voltage input range                      | -0.3 to 60                         | V    |

| $V_{IN(HV)}(VBIAS)$                                       | High voltage bias input range                 | -0.3 to 60                         | ٧    |

| V <sub>IN(LV)</sub> (COMP/FB/SS/DITH/<br>FADJ/SLOPE)      | Low voltage input range                       | -0.3 to 3.6                        | V    |

| $V_{REG}(VREG/CTRL/PGOOD)$                                | Internal regulator related pin input          | -0.3 to 6                          | V    |

| LSDRV1,LSDRV2<br>BS1, HSDRV1 to LX1<br>BS2, HSDRV2 to LX2 | Input voltage range                           | -0.3 to 6                          | V    |

| V <sub>sw</sub> (LX1 / LX2)                               | Switch node voltage                           | LX1: -1 to 60<br>LX2: -1 to 60     | V    |

| V <sub>BS</sub> (BS1,BS2)                                 | Bootstrap node voltage                        | BS1: -0.3 to 60<br>BS2: -0.3 to 60 | V    |

| CS, CSG                                                   | Sense pins differential input voltage range   | -0.3 to 0.3                        | V    |

| $T_{J(MAX)}$                                              | Operating junction temperature range          | 150                                | °C   |

| $T_{STG}$                                                 | Storage temperature range                     | -65 to 150                         | °C   |

| Electrostatic discharge                                   | Human body model                              | 2                                  | kV   |

| Electrostatic discharge                                   | Machine model                                 | 200                                | V    |

| $\theta_{\text{JC(TSSOP28)}}$                             | TSSOP28 Thermal resistance (Junction to Case) | 16                                 | °C/W |

| $	heta_{	extsf{JC}(	extsf{QFN32})}$                       | QFN32 Thermal resistance (Junction to Case)   | 13                                 | °C/W |

| $\theta_{JA(TSSOP28)}$                                    | TSSOP28 Thermal resistance (Junction to Air)  | 37                                 | °C/W |

| $\theta_{JA(QFN32)}$                                      | QFN32 Thermal resistance (Junction to Air)    | 34                                 | °C/W |

<sup>(\*1):</sup> Stress beyond those listed at table above may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

### **Recommended Operating Conditions**

| Symbol           | Parameter                            | Specifi | Unit |       |

|------------------|--------------------------------------|---------|------|-------|

| Syllibol         | raiailietei                          | Min     | Max  | Oilit |

| V <sub>IN</sub>  | Supply voltage                       | 4.2     | 55   | V     |

| VBIAS            | Auxiliary supply voltage             | 6       | 36   | V     |

| EN               | Enable pin input voltage             | 0       | 55   | V     |

| ISENSP, ISENSN   | Sense pin input voltage              | 0       | 55   | V     |

| f <sub>osc</sub> | Switching voltage range              | 100     | 600  | kHz   |

| T <sub>A</sub>   | Operating free-air temperature range | -40     | 85   | °C    |

| T <sub>J</sub>   | Operating temperature range          | -40     | 125  | °C    |

### **Electrical Characteristics**

Operating condition  $V_{IN}=24V$ ,  $C_{SS}=0.1\mu F$ ,  $T_J=25^{\circ}C$ , unless otherwise specified (\* 1)

| Cumphed                  | Downwater.                        | Test Condition                               | Sp    | ecificati | ion   | Unit  |

|--------------------------|-----------------------------------|----------------------------------------------|-------|-----------|-------|-------|

| Symbol                   | Parameter                         | Test Condition                               | Min   | Тур.      | Max   | Offic |

| SUPPLY V                 | OLTAGE                            |                                              |       |           |       |       |

| V <sub>IN</sub>          | Input voltage                     |                                              | 4.2   |           | 55    | V     |

| I <sub>SD</sub>          | Shutdown mode supply current      | V <sub>EN</sub> =0V                          |       | 12        | 16    | μΑ    |

| I <sub>STBY</sub>        | Standby mode supply current       | V <sub>EN</sub> =1.1V, non-switching         |       | 0.6       | 2     | mA    |

| I <sub>Q</sub>           | Operating current                 | $V_{EN}=2V$ , $V_{FB}=0.9V$                  |       | 2.72      | 4     | mA    |

| ENABLE/                  | UVLO                              |                                              |       |           |       |       |

| V <sub>EN(STBY)</sub>    | Standby threshold voltage         | V <sub>EN</sub> rising                       | 0.6   | 0.73      | 0.9   | V     |

| I <sub>EN(STBY)</sub>    | Standby mode pin source current   | V <sub>EN</sub> =1.1V                        |       | 1.8       | 3     | μΑ    |

| V <sub>EN(OPER)</sub>    | Operating threshold voltage       | V <sub>EN</sub> rising                       | 1.1   | 1.24      | 1.4   | V     |

| I <sub>HYS(OPER)</sub>   | Operating hysteresis current      | V <sub>EN</sub> =2.4V                        | 1.5   | 3.5       | 5.5   | μΑ    |

| VBIAS                    |                                   |                                              |       |           |       |       |

| $V_{VBIAS(SW)}$          | Internal bias switchover voltage  | $V_{EN}=2V$ , $V_{VBIAS}$ rising             |       | 5.6       |       | V     |

| ERROR A                  | MPLIFIER                          |                                              |       |           | ı     |       |

| V <sub>FB</sub>          | Feedback reference voltage        | V <sub>EN</sub> =2V, FB connect to COMP      | 0.788 | 0.8       | 0.812 | V     |

| I <sub>FB</sub>          | Feedback bias current             | $V_{FB}$ in regulation                       |       |           | 0.1   | μΑ    |

| BW                       | Unity gain bandwidth              |                                              |       | 2         |       | MHz   |

| ,                        | COMP source current               | $V_{EN}=2V$ , $V_{COMP}=V_{FB}=0V$           |       | 323       |       |       |

| I <sub>COMP</sub>        | COMP sink current                 | $V_{EN}=2V$ , $V_{FB}=1.1V$ , $V_{COMP}=3V$  |       | 320       |       | μA    |

| g <sub>M(EA)</sub>       | Error amplifier trans-conductance |                                              |       | 1490      |       | μS    |

| VREG                     |                                   |                                              |       |           |       |       |

| $V_{REG}$                | Internal regulation voltage       | V <sub>EN</sub> =2V, VBIAS, VREG pin open    |       | 5.3       | 5.6   | V     |

| V <sub>UV</sub>          | VREG UVLO threshold               | $V_{IN}=3V$ , $V_{EN}=2V$ , $V_{REG}$ rising | 3.0   | 3.4       | 3.6   | V     |

| R <sub>OUT(VREG)</sub>   | LDO Output impedance              | $I_{OUT} = 0.03A, V_{IN} = 3.5V$             |       | 4.5       |       | Ω     |

|                          | UVLO hysteresis                   |                                              |       | 100       |       | mV    |

| I <sub>OUT(VREG)</sub>   | VREG maximum supply current       | $V_{REG} = 0V$                               |       | 110       |       | mA    |

| PGOOD                    |                                   |                                              |       |           |       |       |

| \/                       | PGOOD trip ratio for FB (Falling) | Ratio to V <sub>FB</sub>                     |       | -9        |       | %     |

| $V_{PGOOD}$              | PGOOD trip ratio for FB (Rising)  | Ratio to $V_{FB}$                            |       | 10        |       | %     |

|                          | Hysteresis                        |                                              |       | 1.6       |       | %     |

| I <sub>LEAK(PGOOD)</sub> | PGOOD leakage current             | $V_{EN}=2V$ , $V_{FB}=0.8V$ , $V_{PGOOD}=5V$ |       | 125       | 200   | nA    |

| I <sub>SINK(PGOOD)</sub> | PGOOD sink current                | $V_{FB}=0V$ , $V_{PGOOD}=0.4V$               |       | 5.4       | 7     | mA    |

<sup>(\*1):</sup> Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

# **Electrical Characteristics (cont.)**

Operating condition  $V_{IN}=24V$ ,  $C_{SS}=0.1\mu F$ ,  $T_J=25^{\circ}C$ , unless otherwise specified (\* 1)

| Symbol                   | Daramatar                        | Test Condition -               |                            | Specification |      |     | Unit |

|--------------------------|----------------------------------|--------------------------------|----------------------------|---------------|------|-----|------|

| Symbol                   | Parameter                        |                                |                            | Min           | Тур. | Max | Unit |

| FREQUEN                  | CY/SYNC/DITHER                   |                                |                            |               |      |     |      |

| PW <sub>SYNC</sub>       | SYNC input pulse width           |                                |                            | 75            |      | 500 | ns   |

| f                        | PWM switching frequency          | V <sub>EN</sub> =2V,           | $R_T=20k\Omega$            | 360           | 370  | 420 | kHz  |

| $f_{sw}$                 | rwin switching frequency         | $V_{FB}=0.6V$                  | $R_T=40k\Omega$            | 180           | 200  | 220 | kHz  |

| V <sub>SYNCH</sub>       | SYNC input high threshold        |                                |                            | 2.4           |      |     | V    |

| $V_{SYNCL}$              | SYNC input low threshold         |                                |                            |               |      | 1.2 | V    |

| V                        | Dither high threshold            |                                |                            |               | 1.23 |     | V    |

| $V_{DITHER}$             | Dither low threshold             |                                |                            |               | 1.15 |     | V    |

| I <sub>DITHER</sub>      | Dither source/sink current       | V <sub>DITHER</sub> =1.1V / 1. | .4V, V <sub>FB</sub> =0.6V |               | 10   |     | μΑ   |

| SOFT STA                 | RT                               |                                |                            |               | •    |     |      |

| I <sub>SS</sub>          | Soft start pull-up current       | V <sub>EN</sub> =2V, V         | $V_{SS}=0V$                | 5             | 6    | 7   | μΑ   |

| $V_{SS(CL)}$             | Soft start clamp voltage         | $V_{EN}=2V$ , $V_{FB}=0$ .     | .6V, SS open               |               | 1.34 |     | V    |

| $\Delta V_{FB} - V_{SS}$ | FB to SS offset voltage          | V <sub>ss</sub> =0             | OV                         |               | -15  |     | mV   |

| GATE DR                  | VER                              |                                |                            |               |      |     |      |

|                          | Gate driver peak source current  | $V_{BS1} - V_{LX1} = 5.3V$     |                            |               | 3.5  |     |      |

| I <sub>HSDRV1,2</sub>    | Gate driver peak sink current    | $V_{BS1}-V_{LX1}$              |                            | 5             |      | - A |      |

| _                        | Gate driver peak source current  | $V_{BS2}-V_{LX2}=5.3V$         |                            |               | 3.5  |     |      |

| L <sub>SDRV1,2</sub>     | Gate driver peak sink current    | $V_{BS2}-V_{LX2}$              |                            | 5             |      |     |      |

| D                        | Gate driver pull-up resistance   | I <sub>HSDRV1,2</sub> =0.1A    |                            |               | 0.5  |     |      |

| R <sub>HSDRV1,2</sub>    | Gate driver pull-down resistance | I <sub>HSDRV1,2</sub> =        | =0.1A                      |               | 0.4  |     | Ω    |

| D                        | Gate driver pull-up resistance   | I <sub>LSDRV1,2</sub> =        | 0.1A                       |               | 0.5  |     |      |

| R <sub>LSDRV1,2</sub>    | Gate driver pull-down resistance | I <sub>LSDRV1,2</sub> =        | :0.1A                      |               | 0.4  |     | Ω    |

| V <sub>UV(BS1,2)</sub>   | BS1,2 to LX1,2 UVLO threshold    | HSDRV1,2                       | shut off                   |               | 2.73 |     | V    |

|                          | BS1,2 to LX1,2 UVLO hysteresis   | HSDRV1,2 beg                   | in switching               |               | 280  |     | mV   |

|                          | BS1,2 to LX1,2 threshold for re- |                                |                            |               | 4.45 |     | V    |

|                          | fresh pulse                      |                                |                            |               | 4.45 |     | V    |

| t <sub>DTH</sub>         | HSDRV1,2 off to LSDRV1,2 on      |                                |                            |               | 45   |     | ns   |

| чин                      | dead time                        |                                |                            |               | '    |     | 113  |

| $t_{DTL}$                | LSDRV1,2 off to HSDRV1,2 on      |                                |                            |               | 45   |     | ns   |

|                          | dead time                        |                                |                            |               |      |     |      |

| OUTPUT                   |                                  |                                |                            |               |      |     |      |

| V <sub>OVP</sub>         | Output overvoltage threshold     | Relative                       | to FB                      |               | 0.86 |     | V    |

|                          | Output overvoltage hysteresis    |                                |                            |               | 21   |     | mV   |

<sup>(\*1):</sup> Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

# **Electrical Characteristics (cont.)**

Operating condition  $V_{IN}=24V$ ,  $C_{SS}=0.1\mu F$ ,  $T_J=25^{\circ}C$ , unless otherwise specified (\* 1)

| Symbol                      | Parameter                                       | Test Condition                                                    | Specification |      |      | Unit  |  |  |

|-----------------------------|-------------------------------------------------|-------------------------------------------------------------------|---------------|------|------|-------|--|--|

| Syllibol                    | raidilletei                                     | rest Condition                                                    | Min           | Тур. | Max  | Offic |  |  |

| CURRENT                     | CURRENT LIMIT                                   |                                                                   |               |      |      |       |  |  |

| V <sub>CS(BUCK)</sub>       | Buck mode current limit threshold (Valley)      | $V_{IN}=V_{VISNS}=24V, V_{VOSNS}=12V,$ $V_{SLOPE}=0V$             | 53.2          | 85   | 98   | mV    |  |  |

| V <sub>CS(BOST)</sub>       | Boost mode current limit thresh-<br>old (Peak)  | $V_{IN}=V_{VISNS}=12V$ , $V_{VOSNS}=18V$ , $V_{SLOPE}=0V$         | 119           | 165  | 221  |       |  |  |

| I <sub>BIAS(CS/CSG)</sub>   | CS/CSG pin bias current                         | $V_{CS} = V_{CSG} = V_{SLOPE} = 0V$                               | 4             | -95  |      | μA    |  |  |

| I <sub>OFFSET(CS/CSG)</sub> | CSG pin offset current                          | $V_{CS} = V_{CSG} = V_{SLOPE} = 0V$                               |               |      | 14   | μΑ    |  |  |

| CONSTAN                     | T CURRENT LOOP                                  |                                                                   |               | •    |      |       |  |  |

| V <sub>SNS</sub>            | Average current loop regulation                 | $V_{ISNSN}$ =24V, sweep ISNSP,<br>Measure $V_{SS}$                | 43            | 50   | 57   | mV    |  |  |

| I <sub>SNS</sub>            | ISNSN/ISNSP pin bias currents                   | $V_{IN}=V_{ISNSP}=V_{ISNSN}=24V$                                  |               | 7    |      | μΑ    |  |  |

| g <sub>M(CS)</sub>          | Current sense amplifier trans-<br>conductance   | $V_{ISNSP}-V_{ISNSN}=55mV$ , $V_{SS}=0.5V$                        |               | 1    |      | mS    |  |  |

| SLOPE CO                    | MPENSATION                                      |                                                                   |               |      |      |       |  |  |

|                             | Buck adaptive slope current                     | $V_{IN}=V_{VISNS}=24V$ , $V_{VOSNS}=12V$ , $V_{SLOPE}=0V$         | 24            | 30   | 35   |       |  |  |

| I <sub>SLOPE</sub>          | Boost adaptive slope current                    | $V_{IN} = V_{VISNS} = 12V$ , $V_{VOSNS} = 18V$ , $V_{SLOPE} = 0V$ | 13            | 17   | 21   | μΑ    |  |  |

| <b>G</b> M(SLOPE)           | Slope compensation amplifier trans -conductance |                                                                   |               | 2    |      | μS    |  |  |

| MODE CO                     | NTROL                                           |                                                                   |               |      |      |       |  |  |

| I <sub>CTRL</sub>           | Source current out of CTRL pin                  | $V_{CTRL} = 0V$                                                   | 17            | 20   | 23   | μΑ    |  |  |

| $V_{DCM\_HIC}$              | DCM with hiccup threshold voltage               |                                                                   | 0.6           | 0.7  | 0.76 |       |  |  |

| V <sub>CCM_HIC</sub>        | CCM with hiccup threshold voltage               |                                                                   | 1.18          | 1.28 | 1.38 | V     |  |  |

| $V_{CCM}$                   | CCM no hiccup threshold voltage                 |                                                                   | 2.22          | 2.4  | 2.6  |       |  |  |

| THERMAL                     | PROTECTION                                      |                                                                   |               |      |      |       |  |  |

| T <sub>SHUTDOWN</sub>       | Thermal shutdown trip point                     |                                                                   |               | 160  |      | ℃     |  |  |

|                             | Thermal shutdown hysteresis                     |                                                                   |               | 15   |      |       |  |  |

<sup>(\*1):</sup> Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

7

### **Functional Descriptions**

also operates in buck-boost mode with excellent and hiccup mode selection. efficiency and low ripple output voltage when VIN close to V<sub>OUT</sub>.

VP3679 integrates two half-bridge N-channel MOSFET gate drivers and is designed to work with 4 external MOSFET switches. When V<sub>IN</sub> is greater then V<sub>OUT</sub>, the VP3679 PWM control works in valley current mode. The inductor current should be monitored for cycle-by-cycle current limit and is sensed through an external sense resistor conand power ground.

When  $V_{IN}$  is lower then  $V_{OUT}$ , the VP3679 PWM control works in peak current mode. For the application cases of lower  $V_{IN}$  (e.g. below than 5.6V) and higher V<sub>OUT</sub>, VP3679 is capable of supporting bias VBIAS terminal with Vout. In this condition, internal regulator source would be switched from V<sub>IN</sub> to V<sub>OUT</sub> for higher gate driver bias so that better switching efficiency would be achieved.

Besides cycle-by-cycle current limiting, VP3679 supports average current sense scheme for either input or output current detection. Softstart is also supported with an external capacitor connected to ground to eliminate inrush current and voltage overshoot during startup.

VP3679 supports continuous conduction mode (CCM) for noise sensitive application such as audio or radio frequency use and discontinuous conduction mode (DCM) for higher light load efficiency such as backup power application. For the output overload condition VP3679 provides optional hiccup mode to reduce the heat and damage during sustained overload case. If the hiccup mode is dis-

The VP3679 is a high efficiency full bridge buck- abled the controller remains in a cycle-by-cycle boost controller with wide input voltage range. In current limit until the overload case is fixed. Use addition to buck mode and boost mode, VP3679 CTRL terminal to configure CCM/DCM operation

> The VP3679 supports over-voltage protection and power good status indication. If the output feedback voltage exceeds then 7.5% or above nominal reference  $V_{REF}(0.8V)$  the high side drivers would be turn off. PGOOD terminal would be externally pulled high when FB pin voltage is regulated within +10% and -9% centered with  $V_{REF}$ .

The VP3679 can operate in shutdown state, nected to the source of low-side MOSFET switches standby state and normal operation state. It can be configured with setting EN terminal with 3 distinct voltage ranges.

### Operation States and UVLO

The VP3679 has chip enable and under-voltage lock out protection. When EN pin voltage is below than standby threshold 0.73V, the controller enters the shutdown state and most of the functional blocks are disabled including V<sub>REG</sub> regulator.

When EN voltage is greater than standby threshold but less than the operating threshold 1.24V, both internal V<sub>REG</sub> regulator and VBIAS bias input are enabled but the controller will still not start up and hence no switching.

The VP3679 standby state will be also latched if the soft start fails or CTRL pin pulled low with hiccup trigger 4 times. While the controller is standby latched, recycling EN pin or power to ground would release the latched state.

When EN voltage is greater than operating threshold, the controller will start switching if the  $V_{REG}$  is also above V<sub>REG</sub> under-voltage threshold (3.4V). If

V<sub>REG</sub> is still under UV threshold, the VP3679 will not switch. Table 1 shows the relation between the state and EN pin threshold voltage range.

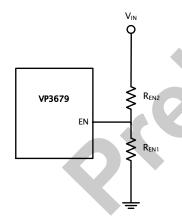

To implement UVLO protection, the simplest way is to use a resistor network from VIN to AGND with the mid-point connect to EN pin. The turn-on threshold can be obtained by equation 1.

$$V_{IN(UVLO)} = 1.24V \times \left\{ 1 + \frac{R_{EN2}}{R_{EN1}} \right\} - R_{EN2} \times 1.5 \mu A$$

(1)

(2)

$$\Delta V_{HYS(UVLO)} = 3.5 \mu A \times R_{EN2}$$

Equation 2 shows the hysteresis between the UVLO turn-on and turn-off threshold and can be obtained with this equation. Beware of the EN pin source current is about 3.5µA when EN pin voltage is above 1.24V.

Figure 1. Programming EN pin

| EN                                                                        | $V_{REG}$        | State                |

|---------------------------------------------------------------------------|------------------|----------------------|

| EN<0.73V                                                                  | N/A              | Shutdown             |

| 0.73V <en<1.24v< td=""><td>N/A</td><td>Standby (latched)</td></en<1.24v<> | N/A              | Standby (latched)    |

| EN>1.24V                                                                  | $V_{REG} < 3.4V$ | Standby              |

| EN>1.24V                                                                  | $V_{REG} > 3.4V$ | Operating, Switching |

Table 1. EN pin threshold voltage

To release the standby latched state, EN pin must function. Dithering function is also disabled when be pulled under 0.73V to ensure the shutdown using external clock input. logic is reset.

### Frequency Adjustment

It is simply to use an external resistor to adjust the PWM clock frequency. Connect a resistor from FADJ terminal to AGND to program switching frequency from 100kHz to 600kHz. Equation 3 shows how to calculate the external resistor:

$$R_T = \frac{(\frac{1}{f_{SW}} - 325ns)}{117pF}$$

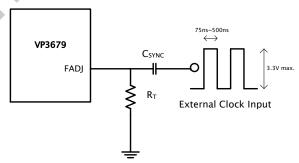

The VP3679 can be synchronized with external clock source. Figure 2 demonstrates the connection to AC clock source. The external clock frequency should be higher than resistor programmed frequency. Beware of the pulse width of the external PWM clock should be in range from 75ns to 500ns and the pulse amplitude must not exceed 3.3V.

Figure 2. External Clock Synchronization

Frequency dithering is an important skill to improve EMI performance. Connect a capacitor from DITH pin to AGND to enable this function. Equation 4 shows the calculation of dithering capacitance:

$$C_{DITH} = \frac{10\mu A}{f_{SW} \times 0.24V}$$

Connect the DITH pin to ground to disable this

#### Soft Start

The VP3679 provides soft start scheme to prevent transient during startup and could be adjusted by (6) a soft start capacitor connected from SS terminal to AGND. During powering up, an internal current **CCM/DCM Operation** source charges the soft start capacitor. When the SS pin voltage below the feedback reference  $V_{REF}$ , soft-start block raises the FB voltage with the same slope as the SS pin. After SS pin voltage exceeds V<sub>REF</sub>, the soft-start period is finished and the output voltage is almost reached to desired output value. If the FB voltage is still under 0.3V after the soft start progress is finished, the VP3679 will enter standby mode and latched. Soft-start time can be calculated by equation 5:

$$t_{ss} = \frac{C_{SS} \times 0.8V}{6 \,\mu A}$$

SS pin will be discharged in the following 3 conditions, EN falling below UVLO voltage and VREG UV threshold, enter hiccup mode and thermal shutdown state. When average current limiting is active, the SS pin would be also discharged by the constant current loop trans-conductance amplifier to limit the current.

#### Average Current Limit

To implement current limit protection of input or output, a constant current trans-conductance amplifier is integrated in the VP3679. An additional current sense resistor connected in series with the ISENSP and ISENSP pins to monitor the voltage drop and compare it with internal 50mV reference. If the voltage drop is greater than 50mV then the constant current loop trans-conductance amplifier gradually discharges the soft-start capacitor to pull low the output voltage to limit the input or output current. Use equation 6 to obtain the current limit value. Short ISENSP and ISENSN to disable this function.

$$I_{CL(AVG)} = \frac{50mV}{R_{SENS}}$$

| CTRL pin         | Mode         | Protection             |

|------------------|--------------|------------------------|

| Direct to VREG   | ССМ          | Cycle-by-cycle limit   |

| Use 91k to AGND  | ССМ          | Hiccup                 |

| Use 47k to AGND  | DCM+CCM      | Hiccup                 |

| Direct to AGND   | DCM+CCM      | Hiccup                 |

| Direct to Adivid | DCIVI FCCIVI | Standby after 4 cycles |

Table 2. CTRL Pin Selections

The VP3679 allows the operation mode change of continuous conduction (CCM) or discontinue conduction (DCM). For noise sensitive application such as audio amplifier, the switching noise needs to be filtered to prevent any hearable noise. CCM operation the inductor current can flow in either direction and the controller switches at a fixed frequency regardless of the load current.

In DCM operation, when the inductor current reaches zero the synchronous rectifier MOSFETs emulates diodes as LSDRV1 or HSDRV2 turn-off for the rest of the PWM cycle at light load to reduce switching losses as possible. DCM operation results in reduced and variable frequency operation which increases light load efficiency of the converter. For the sake of safety, the VP3679 will enter standby latched state after 4 times hiccup trigger if the CTRL pin is connected to ground directly.

Table 2 shows how the CTRL pin configures the operation mode. The mode is latched at startup.

#### Over-current Protection

In buck operation, the sensed valley voltage across

across the R<sub>SENSE</sub> is limited to 165mV. If the peak current in boost switch causes the CS pin to exceed this threshold, the low-side boost switch is  $If V_{IN}$  is lower and working topology is boost, use turned-off for the rest of the clock.

Use proper connection networks defined in Table 2 to configure VP3679 in the appropriate working manner. If the hiccup mode (CCM or DCM) is enabled, the controller shuts down after detecting cycle-by-cycle current for 128 cycles and then the soft-start capacitor is discharged. After 4000 clock cycles the SS pin resumes to charge soft-start capacitor again and the controller starts over again. If the hiccup mode is not enabled, the VP3679 will perform cycle-by-cycle current limit when overload condition occurs.

#### Output Over-voltage Protection

VP3679 will turns off the 2 gate drivers when the feedback voltage is 7.5% greater than the nominal reference voltage V<sub>REF</sub>. Once the feedback value falls in 5% of  $V_{REF}$ , the VP3679 resumes switching.

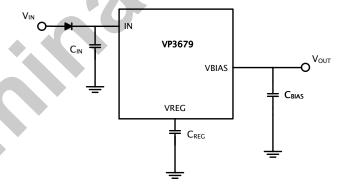

### Internal Regulator and VBIAS Input

Since the VP3679 uses half-bridge gate drivers and high side NMOSFET gate bias should be generated from internal V<sub>REG</sub> with boot-strap circuits. For  $V_{\text{IN}}$  is less than the certain of value, the  $V_{\text{REG}}$ voltage tracks V<sub>IN</sub> with few voltage drop. Otherwise the internal regulator V<sub>REG</sub> voltage will be fixed and regulated. The on/off scheme follows the control mechanism of EN pin as previous described.

When  $V_{OUT}$  is greater then  $V_{REG}$  nominal value plus one more diode drop, the internal regulator will

$R_{SENSE}$  is limited to 85mV. If the sensed value is not use  $V_{OUT}$  to regulate internal  $V_{REG}$  instead of using below this threshold during the buck switch off-  $V_{IN}$ . In buck mode, connect VBIAS pin to  $V_{OUT}$  with time, the high-side buck switch skips a cycle. In  $\,$  V $_{

m OUT}$  value greater then 6V will improve the effiboost operation, the maximum peak voltage ciency. Please be aware that the voltage on VBIAS pin should not exceed then 36V.

> higher output voltage and feed it back to V<sub>OUT</sub> to generate internal  $V_{REG}$  is a good idea. For this case, place a series blocking diode between the input power source and IN terminal to prevent VREG back-feeding into IN pin through internal MOSFET body diode.

Figure 3. VREG and VBIAS

V<sub>REG</sub> grounding capacitor is good to use a 1 µF ceramic capacitor and is better to be placed close to VREG pin.

Since the VP3679 uses internal LDO to generate internal low-voltage power V<sub>REG</sub>, the method of using VBIAS to supply internal power will essentially generate heat. When the VBIAS pin voltage is low (such as 12V), the  $\Delta V^x I_{VREG}$  power loss will not have a great impact on VP3679. However, if VBIAS pin voltage is high (greater than 36V), the power loss will significantly increase the temperature of the IC body and then worse the stability and reliability.

To reduce the heat under this operating condition, there are two options to replace the internal LDO with the external power supply. This external pow-

er supply can use either an external LDO or a buck regulator. One way is to keep using VBIAS pin and connect extra HV regulator and the other one is to connect external power to VREG instead of using VBIAS pin.

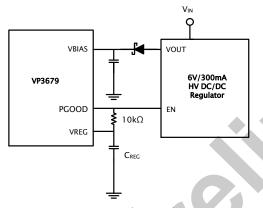

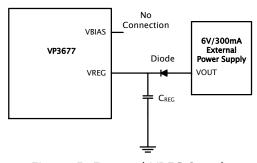

#### Option #1: Using VBIAS:

For higher VBIAS input (>36V) or critical environment, connect external power source to VBIAS pin is a good idea. Since internal VBIAS turn over threshold is about 5.6V, using 6V/300mA external regulator is appropriate. Figure 4 demonstrates the connection diagram.

Figure 4. VBIAS External Regulator Connection

#### Option #2: Using VREG:

If the external MOSFET switches have larger Ciss or multiple MOSFET switches paralleled, it is recommended to connect external power supply to VREG with a blocking diode in series. The concept of such connection is shown in Figure 5.

Figure 5. External VREG Supply

Since the nominal voltage of  $V_{REG}$  is about 5.3V, external power supply voltage should be larger than 5.5V plus diode V-drop 0.6V. According to these, the output voltage should be regulated at 6V.

With these options and good heating dissipating cooper, the surface temperature of VP3677 would be reduced dramatically.

#### **Power Good Indicator**

PGOOD terminal is pulled high when the voltage at the FB pin is within range of  $-9\%\sim+10\%$  of the nominal  $V_{REF}$  voltage. Otherwise the PGOOD is pulled low. Since the PGOOD is open drain output, it is needed to add pull-up resistor and the pull down strength of the internal MOSFET is about 5.4mA. Since the MOSFET is low voltage device, do not connect the pull-up resistor to 5.5V or higher.

#### Slope Compensation

The VP3679 performs a slope compensation based on the current sense signal monitored across the CS and CSG pins with the composition of the  $V_{\text{IN}}$ ,  $V_{\text{OUT}}$  and SLOPE pin signals. The result is compared to the COMP error voltage by PWM modulator.

The current mode controllers require slope compensation for stable current loop operation. In peak current mode the duty is 50% or above and below 50% in valley current mode. Use a capacitor to connect between SLOPE pin and AGND to fine tune optimal slope for various  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  combination.

#### **Loop Compensation**

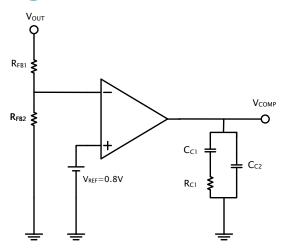

Figure 6. Error Amplifier Compensation Network

Figure 6 shows the internal loop compensation structure. The trans-conductance amplifier output range is from 0.3V to 3V. The COMP pin output range will limit the possible  $V_{IN}$  and output current. Type II PI compensation is formed with  $R_{C1}$ – $C_{C1}$  to AGND in parallel with another pole compensator  $C_{C2}$ .

The VP3679 will operate in buck, boost and buckboost mode and the compensation is separated into two considerations. In buck mode, the bottom value of COMP dominates the maximum possible  $V_{\text{IN}}$  for which the controller can regulate output voltage at no load. Equation 7 shows how to calculate  $V_{\text{COMP}}$  as function of  $V_{\text{IN}}$  at no load in CCM operating.

$$V_{COMP(BUCK)} = 1.6V - A_{CS} \cdot R_{SENSE} \cdot \frac{V_{OUT}}{2 \cdot L1 \cdot F_{SW}} \cdot (1 - D_{BUCK}) - \frac{2\mu S \cdot (V_{IN} - V_{OUT}) + 6\mu A}{C_{SLOPE} \cdot F_{SW}} \cdot (1 - D_{BUCK})$$

Where  $D_{BUCK}$  is given by equation 8.

$$D_{BUCK} = \frac{V_{OUT}}{V_{IN}}$$

To increase the maximum  $V_{IN}$  range of buck operation, try to change appropriate frequency, larger inductor, higher  $C_{SLOPE}$ , smaller sense resistor.

In boost mode, the minimum possible  $V_{IN}$  for which the converter can regulate the output at full load is the top value of  $V_{COMP}$ . Equation 9 shows how to calculate  $V_{COMP}$  as function of  $V_{IN}$  at full load in CCM

operating.

(9)

$$V_{COMP(BOOST)} = 1.6V + A_{CS} \cdot R_{SENSE} \cdot \left(I_{OUT} \cdot \frac{V_{OUT}}{V_N} + \frac{V_N}{2 \cdot L1 \cdot F_{SW}} \cdot D_{BOOST}\right) + \frac{2\mu S \cdot \left(V_{OUT} - V_N\right) + 5\mu A}{C_{SLOPE} \cdot F_{SW}} \cdot D_{BOOST}$$

Where  $D_{BUCK}$  is given by equation 10.

$$D_{BOOST} = 1 - \frac{V_{IN}}{V_{OUT}}$$

From equation 9, a larger  $L_1$ , higher  $C_{SLOPE}$ , smaller  $R_{SENSE}$  and higher frequency could enlarge the  $V_{IN}$  range of boost operation.

#### **Gate Drivers**

The VP3679 is a full bridge controller and it contains 4 NMOSFET gate drivers. The buck half bridge drive pins are HSDRV1 and LSDRV1 as well as the boost half bridge drive pins are HSDRV2 and LSDRV2. Each gate driver is capable of sinking 5A and sourcing 3.75A peak current.

In DCM operation, LSDRV1 and HSDRV2 turn off when the inductor current reaches to zero in buck operation and HSDRV2 turns off when inductor current drops to zero in boost operation. The driver HSDRV2 would not switch unless soft-start progress is finished to prevent possible reverse current from a pre-biased output.

The low side gate drivers LSDRV1 and LSDRV2 are biased from  $V_{REG}$  and the high side gate drivers HSDRV1 and HSDRV2 are driven from boot–strap capacitors. The boot capacitors are charged and boosted through external schottky diodes connected to VREG terminal. Avoids to use the diodes with greater forward conduction voltage  $V_{\rm F}$  because the high–side gate drives bias will be greatly reduced below than 5V.

The gate driving ability of VP3679 is about 5A peak. However, for lower driving capability such as 2A gate driver it may need to add/adjust gate resistors to fine tune slew rate. This would reduce PWM overshoot which would cause worse EMI per-

formance and make it suitable for driving low- $r_{\text{ON}}\ \text{MOSFET}$  which usually has larger input capacitance.

### **Thermal Protection**

The thermal protection circuit monitors the junction temperature and turns off the VP3679 when junction temperature exceeds temperature trip point. When the protection occurs, the soft-start capacitor will be discharged and the gate drivers shut down immediately. The controller will resume switching after soft-start progress when the junction temperature is below then the thermal shutdown hysteresis value.

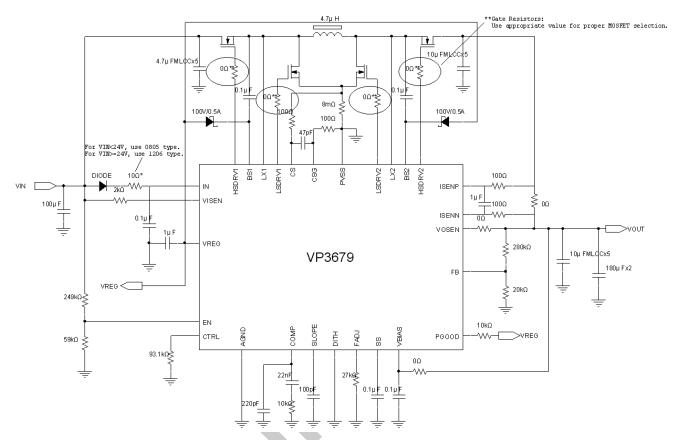

# **Application Information**

Figure 6. VP3679 Typical Application

| SPECIFICATION ITEM  | RATING          |

|---------------------|-----------------|

| Input Voltage Range | 6V~48V          |

| Output              | 12V             |

| Load Current        | 6A maximum      |

| Switching Frequency | 300kHz          |

| Operating Mode      | CCM with Hiccup |

Table 3. VP3679 Typical Application Specification

# **Typical Characteristics**

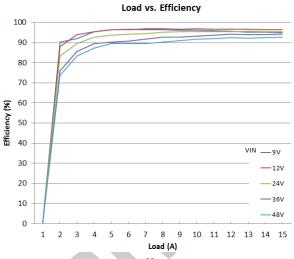

Figure 8. Efficiency (I<sub>OUT</sub>=2A)

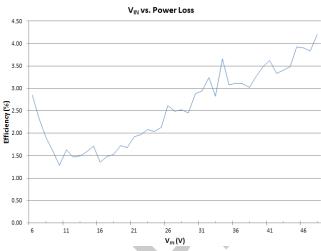

Figure 10. Power Loss (I<sub>OUT</sub>=2A)

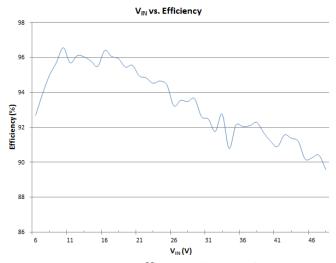

Figure 8. Efficiency (V<sub>IN</sub>)

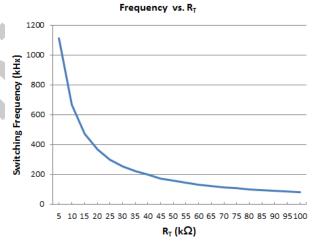

Figure 11. Frequency vs.  $R_T$

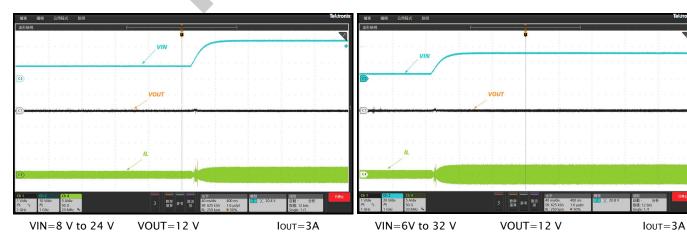

Figure 12. Line Transient

Figure 13. Line Transient

# **Typical Characteristics (cont.)**

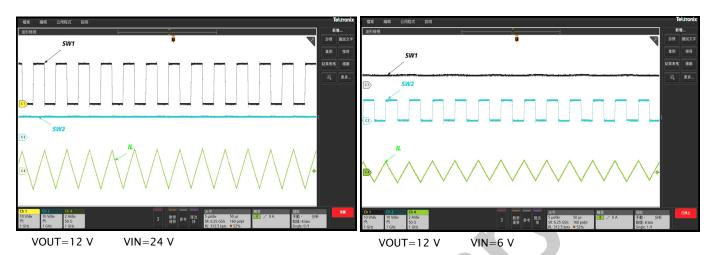

Figure 14. Forced CCM Operation (Buck)

Figure 15. Forced CCM Operation (Boost)

Figure 16. Forced CCM Operation (Buck-Boost)

Figure 17. Load Step (Buck)

Figure 18. Load Step (Boost)

Figure 19. Load Step (Buck-Boost)

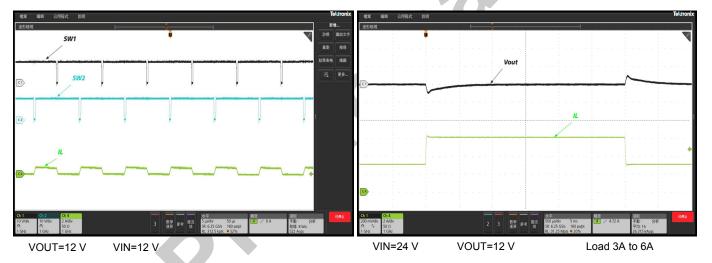

# **Package Information**

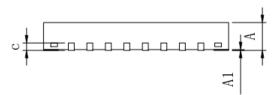

## TSSOP-28EP

| SYMBOL   | Millin | neter |

|----------|--------|-------|

| STIVIBUL | Min.   | Max.  |

| А        |        | 1.20  |

| A1       | 0.05   | 0.15  |

| A2       | 0.80   | 1.05  |

| b        | 0.19   | 0.30  |

| С        | 0.09   | 0.20  |

| D        | 9.60   | 9.80  |

| D1       | 5.70   | 5.90  |

| E        | 6.25   | 6.55  |

| E1       | 4.30   | 4.50  |

| E2       | 2.80   | 3.00  |

| е        | 0.65   | BSC   |

| L        | 0.45   | 0.75  |

| θ        | 0      | 8     |

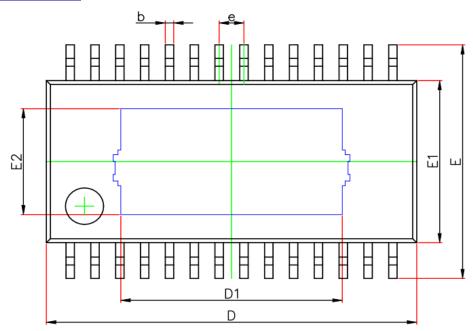

# Package Information (cont.)

### QFN32 5x5

TOP VIEW

BOTTOM VIEW

SIDE VIEW

| ava mor | М     | MILLIMETER |       |   |  |

|---------|-------|------------|-------|---|--|

| SYMBOL  | MIN   | NOM        | MAX   |   |  |

| A       | 0.70  | 0.75       | 0.80  |   |  |

| A1      | _     | 0.02       | 0.05  |   |  |

| b       | 0.18  | 0.25       | 0.30  |   |  |

| b1      |       | 0.16REF    | 7     | Δ |  |

| с       | 0.18  | 0.20       | 0. 25 |   |  |

| D       | 4. 90 | 5. 00      | 5. 10 |   |  |

| D2      | 3. 40 | 3. 50      | 3. 60 |   |  |

| e       | 0     | . 50BSC    |       |   |  |

| Ne      | :     | 3. 50BSC   |       |   |  |

| Е       | 4. 90 | 5. 00      | 5. 10 |   |  |

| E2      | 3. 40 | 3. 50      | 3.60  |   |  |

| L       | 0.35  | 0.40       | 0.45  |   |  |

| h       | 0.30  | 0.35       | 0.40  |   |  |

### **Contact Information**

#### Viva Electronics Incorporated

10F-1, No. 32, Gaotie 2<sup>nd</sup> Rd., Zhubei City, Hsinchu County, Taiwan, R.O.C.

Tel: 886-3-6579508 Fax: 886-3-6579509

WWW: http://www.viva-elec.com.tw

Sales: sales@viva-elec.com.tw

FAE Support: <u>fae@viva-elec.com.tw</u>

#### **IMPORTANT NOTICE**

Viva Electronics Incorporated reserves the right to make changes without further notice to any products or specifications here-in. Viva Electronics Incorporated does not assume any responsibility for use of any its products for any particular purpose, nor does Viva Electronics Incorporated assume any liability arising out of the application or use of any its products or circuits. Viva Electronics Incorporated does not convey any license under its patent rights or other rights nor the rights of others.