VL86C010

## 32-BIT RISC MICROPROCESSOR

## **FEATURES**

- · 32-bit internal architecture

- 32-bit external data bus

- · 64M-byte linear address space

- · Bus timing optimized for standard DRAM usage with page mode operation

- · 40M-byte/second bus bandwidth

- · Simple/powerful instruction set providing an excellent high level language compiler target

- · Hardware support for virtual memory systems

- Low interrupt latency for real-time application requirements

- Full CMOS Implementation results in low power consumption

- Single 5 V ± 5% operation

- 84-pin JEDEC Type-B leadless chip carrier or plastic leaded chip carrier (PLCC)

## DESCRIPTION

The VL86C010 Acorn RISC Machine (ARM) is a full 32-bit general-perpose microprocessor designed using reduced instruction set computer (RISC) methodologies. The processor is targeted for the microcomputer. graphics, industrial and controller markets for use in stand-alone or embedded systems. Applications in which the processor is useful include laser printers, graphics engines, N.C. machines and any other systems requiring fast real-time response to external interrupt sources and high processing throughput.

The VL86C010 features a 32-bit data bus, 27 registers of 32 bits each, a load-store architecture, a partially overlapping register set, 2.6 µs worstcase interrupt latency, conditional instruction execution, a 26-bit linear address space and an average instruction execution rate of from fourto-five million instructions per second (MIPS). Additionally, the processor supports two addressing modes: program counter (PC) and base register relative modes. The ability to do pre- and post-indexing allows

stacks and queues to be easily implemented in software. All instructions are 32 bits long (aligned on word boundaries), with register-to-register operations executing in one cycle. The two data types supported are 8-bit bytes and 32-bit words.

Using a load-store architecture simplifies the execution unit of the processor, since only a few instructions deal directly with memory and the rest operate register-to-register. Load and store multiple register instructions provide enhanced performance, making context switches faster and exploiting sequential memory access modes.

The processsor supports two types of interrupts that differ in priority and register usage. The lowest latency is provided by the fast interrupt request (FIRQ) which is used primarily for I/O to peripheral devices. The other interrupt type (IRQ) is used for interrupt routines that do not demand low-latency service or where the overhead of a full context switch is small compared with the interrupt process execution time.

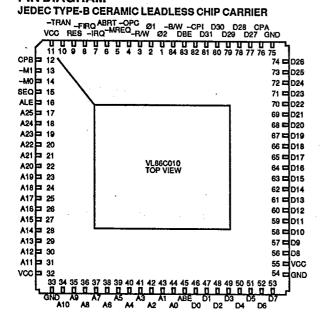

## **PIN DIAGRAM**

| ORDER INFORMATION |                    |                                       |

|-------------------|--------------------|---------------------------------------|

| Part<br>Number    | Clock<br>Frequency | Package                               |

| VL86C010-10QC     | 10 MHz             | Plastic Leaded<br>Chip Carrier (PLCC) |

| VL86C010-10LC     |                    | JEDEC Type-B<br>Ceramic Carrier       |

| VL86C010-12QC     | 12 MHz             | Plastic Leaded<br>Chip Carrier (PLCC) |

| VL86C010-12LC     |                    | JEDEC Type-B<br>Ceramic Carrier       |

Note: Operating temperature range is 0°C to +70°C

PLEASE CONSULT RISC FAMILY DATA MANUAL FOR DETAILED INFORMATION