### UT80C196KD Microcontroller

Datasheet

September 2002

#### **FEATURES**

- 20MHz 16-bit Microcontroller compatible with Industry Standard's MCS-96 ISA

- Register to Register Architecture

- 1000 Byte Register RAM

- ☐ Three 8-bit I/O Ports

- ☐ On-board Interrupt Controller

- ☐ Three Pulse-Width Modulated Outputs

- ☐ High Speed I/O

- ☐ UART Serial Port

- Dedicated Baud Rate Generator

- ☐ Software and Hardware Timers

- 16-Bit Watchdog Timer, Four 16-Bit Software Timers

- Three 16-Bit Counter/Timers

- ☐ Error detection and correction for external memory accesses

- ☐ QML Q compliant part

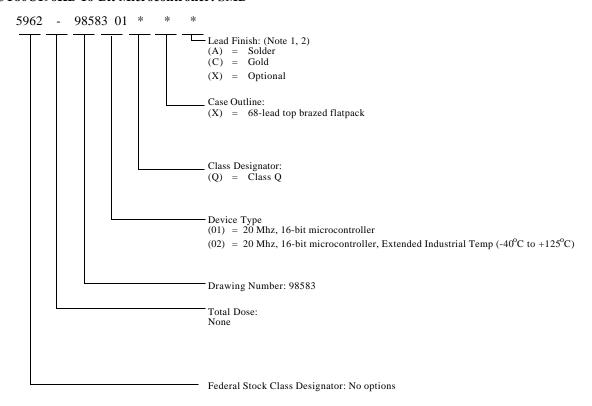

- ☐ Standard Microcircuit Drawing 5962-98583

#### INTRODUCTION

The UT80C196KD is compatible with industry standard's MCS-96 instruction set. The UT80C196KD is supported by commercial hardware and software development tools.

The UT80C196KD accesses instruction code and data via a 16-bit address and data bus. The 16-bit bus allows the microcontroller to access 128K bytes of instruction/data memory. Integrated software and hardware timers, high speed I/O, pulse width modulation circuitry, and UART make the UT80C196KD ideal for control type applications. The CPU's ALU supports byte and word adds and subtracts, 8 and 16 bit multiplies, 32/16 and 16/8 bit divides, as well as increment, decrement, negate, compare, and logical operations. The UT80C196KD's interrupt controller prioritizes and vectors 18 interrupt events. Interrupts include normal interrupts and special interrupts. To reduce power consumption, the microcontroller supports software invoked idle and power down modes.

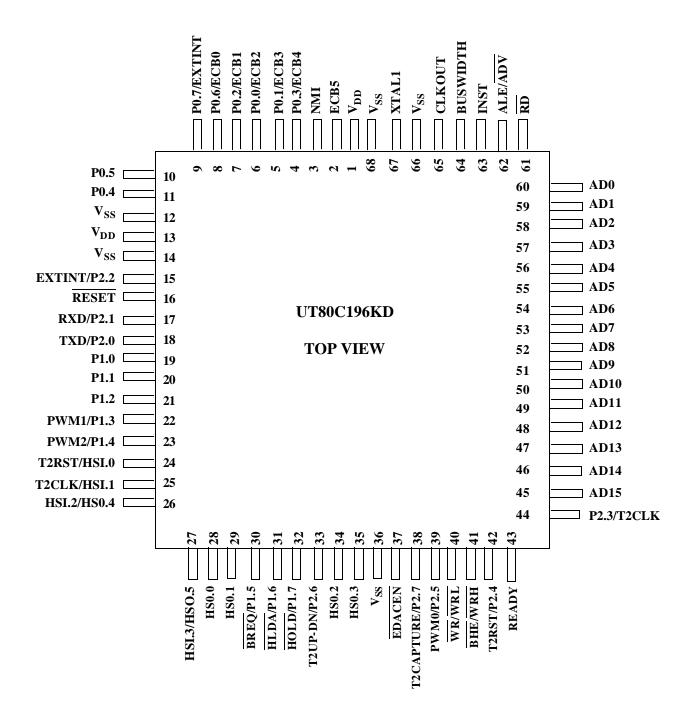

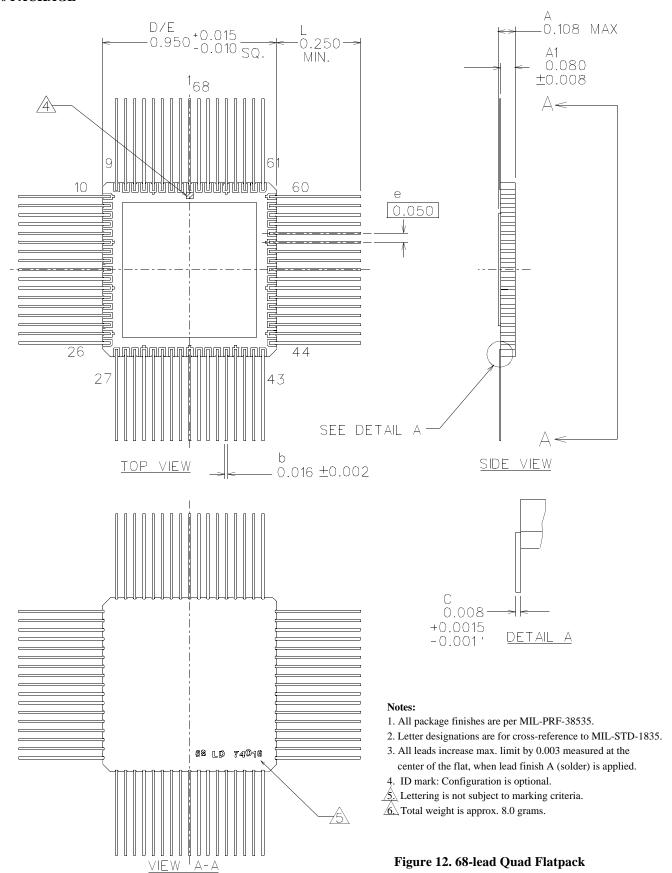

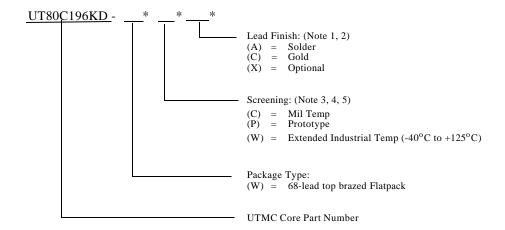

The UT80C196KD is packaged in a 68-lead quad flatpack.

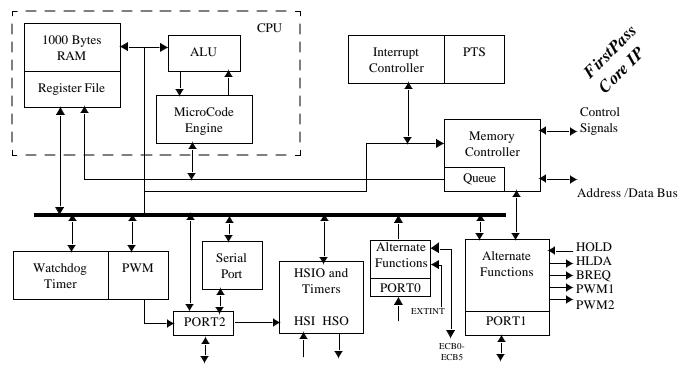

Figure 1. UT80C196KD Microcontroller

#### 1.0 SIGNAL DESCRIPTION

**Port 0 (P0.0 - P0.7):** Port 0 is an 8-bit input only port when used in its default mode. When configured for their alternate function, five of the bits are bi-directional EDAC check bits as shown in Table 1.

**Port 1 (P1.0 - P1.7):** Port 1 is an 8-bit, quasi-bidirectional, I/O port. All pins are quasi-bidirectional unless the alternate function is selected per Table 2. When the pins are configured for their alternate functions, they act as standard I/O, not quasi-bidirectional.

**Port 2 (P2.0 - P2.7):** Port 2 is an 8-bit, multifunctional, I/O port. These pins are shared with timer 2 functions, serial data I/O and PWM0 output, per Table 3.

**AD0-AD7:** The lower 8-bits of the multiplexed address/data bus. The pins on this port are bidirectional during the data phase of the bus cycle.

**AD8-AD15:** The upper 8-bits of the multiplexed address/data bus. The pins on this port are bidirectional during the data phase of the 16-bit bus cycle. When running in 8-bit bus width, these pins are non-multiplexed, dedicated upper address bit outputs.

**HSI:** Inputs to the High Speed Input Unit. Four HSI pins are available: HSI.0, HSI.1, HSI.2, and HSI.3. Two of these pins (HSI.2 and HSI.3) are shared with the HSO Unit. Two of these pins (HSI.0 and HSI.1) have alternate functions for Timer 2.

**HSO:** Outputs from the High Speed Output Unit. Six HSO pins are available: HSO.0, HSO.1, HSO.2, HSO.3, HSO.4, and HSO.5. Pins HSO.4 and HSO.5 are shared with pins HSI.2 and HSI.3 of the HSI Unit respectively.

| Table 1. Port 0 Alternate Functions |                   |                                                                |  |

|-------------------------------------|-------------------|----------------------------------------------------------------|--|

| Port Pin                            | Alternate<br>Name | Alternate Function                                             |  |

| P0.0-P0.3,<br>P0.6                  | ECB0-ECB4         | Error Detection & Correction<br>Check Bits                     |  |

| P0.4<br>P0.5                        |                   | Input Port Pins                                                |  |

| P0.7                                | EXTINT            | Setting IOC1.1=1 will allow P0.7 to be used for EXTINT (INT07) |  |

|             | Table 2. Port 1 Alternate Functions |                                                                                            |  |  |

|-------------|-------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Port<br>Pin | Alternate<br>Name                   | Alternate Function                                                                         |  |  |

| P1.0        | P1.0                                | I/O Pin                                                                                    |  |  |

| P1.1        | P1.1                                | I/O Pin                                                                                    |  |  |

| P1.2        | P1.2                                | I/O Pin                                                                                    |  |  |

| P1.3        | PWM1                                | Setting IOC3.2=1 enables P1.3 as the Pulse Width Modulator (PWM1) output pin.              |  |  |

| P1.4        | PWM2                                | Setting IOC3.3=1 enables P1.4 as the Pulse Width Modulator (PWM2) output pin.              |  |  |

| P1.5        | BREQ                                | Bus Request, output activated when the bus controller has a pending external memory cycle. |  |  |

| P1.6        | HLDA                                | Bus Hold Acknowledge, output indicating the release of the bus.                            |  |  |

| P1.7        | HOLD                                | Bus Hold, input requesting control of the bus.                                             |  |  |

|             | Table 3. Port 2 Alternate Functions |                                                                                                                                                     |  |  |

|-------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Port<br>Pin | Alternate<br>Name                   | Alternate Function                                                                                                                                  |  |  |

| P2.0        | TXD                                 | Transmit Serial Data.                                                                                                                               |  |  |

| P2.1        | RXD                                 | Receive Serial Data.                                                                                                                                |  |  |

| P2.2        | EXTINT                              | External interrupt. Clearing IOC1.1 will allow P2.2 to be used for EXTINT (INT07)                                                                   |  |  |

| P2.3        | T2CLK                               | Timer 2 clock input and Serial port baud rate generator input.                                                                                      |  |  |

| P2.4        | T2RST                               | Timer 2 Reset                                                                                                                                       |  |  |

| P2.5        | PWM0                                | Pulse Width Modulator output 0                                                                                                                      |  |  |

| P2.6        | T2UP-DN                             | Controls the direction of the Timer 2 counter. Logic High equals count down. Logic low equals count up.                                             |  |  |

| P2.7        | T2CAPTURE                           | A rising edge on P2.7 causes<br>the value of Timer 2 to be<br>captured into this register, and<br>generates a Timer 2 Capture<br>interrupt (INT11). |  |  |

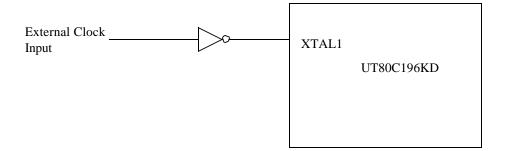

#### 1.1 Hardware Interface

#### 1.1.1 Interfacing with External Memory

The UT80C196KD can interface with a variety of external memory devices. It supports either a fixed 8-bit bus width or a dynamic 8-bit/16-bit bus width, internal READY control for slow external memory devices, a bus-hold protocol that enables external devices to take over the bus, and several bus-control modes. These features provide a great deal of flexibility when interfacing with external memory devices.

#### 1.1.1.1 Chip Configuration Register

The Chip Configuration Register (CCR) is used to initialize the UT80C196KD immediately after reset. The CCR is fetched from external address 2018H (Chip Configuration Byte) after removal of the reset signal. The Chip Configuration Byte (CCB) is read as either an 8-bit or 16-bit word depending on the value of the BUSWIDTH pin. The composition of the bits in the CCR are shown in Table 4.

|     | Table 4. Chip Configuration Register              |

|-----|---------------------------------------------------|

| Bit | Function                                          |

| 7   | N/A                                               |

| 6   | N/A                                               |

| 5   | IRC1 - Internal READY Mode Control                |

| 4   | IRC0 - Internal READY Mode Control                |

| 3   | Address Valid Strobe Select (ALE/ADV)             |

| 2   | Write Strobe Mode Select (WR and BHE/WRL and WRH) |

| 1   | Dynamic Bus Width Enable                          |

| 0   | Enable Power Down Mode                            |

There are 8 configuration bits available in the CCR. However, bits 7 and 6 are not used by the UT80C196KD. Bits 5 and 4 comprise the READY mode control which define internal limits for waitstates generated by the READY pin. Bit 3 controls the definition of the ALE/ADV pin for system memory controls while bit 2 selects between the different write modes. Bit 1 selects whether the UT80C196KD will use a dynamic 16-bit bus or whether it will be locked in as an 8-bit bus. Finally, Bit 0 enables the Power Down mode and allows the user to disable this mode for protection against inadvertent power downs.

#### 1.1.1.2 Bus Width and Memory Configurations

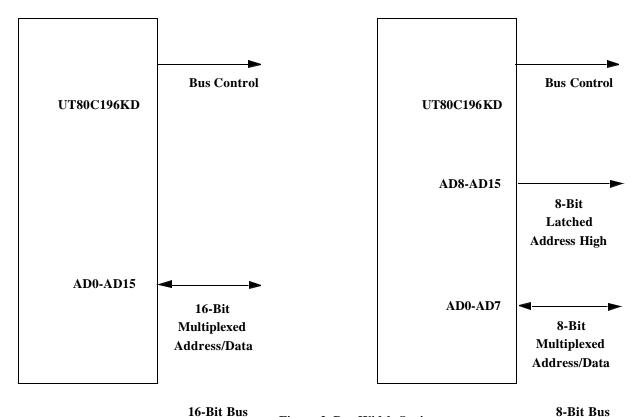

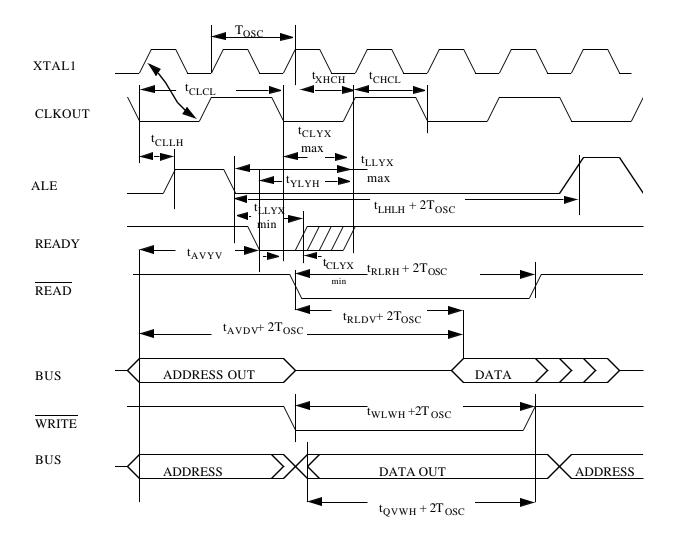

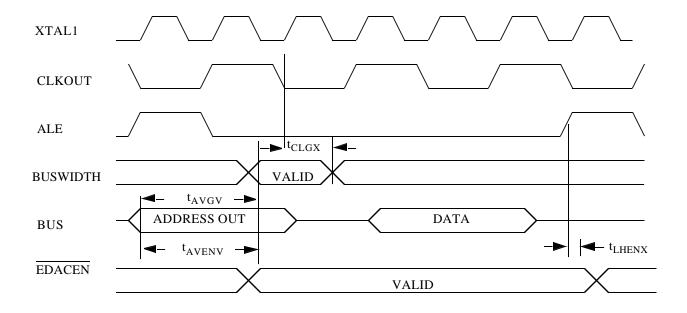

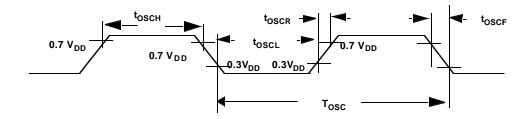

The UT80C196KD external bus can operate as either an 8-bit or 16-bit multiplexed address/data bus (see figure 2). The value of bit 1 in the CCR determines the bus operation. A logic low value on CCR.1 locks the bus controller in 8-bit bus mode. If, however, CCR.1 is a logic high, then the BUSWIDTH signal is used to decide the width of the bus. The bus is 16 bits wide when the BUSWIDTH signal is high, and is 8 bits when the BUSWIDTH signal is low.

#### 1.1.2 Reset

To reset the UT80C196KD, hold the RESET pin low for at least 16 state times after the power supply is within tolerance and the oscillator has stabilized. Resets following the power-up reset may be asserted for at least one state time, and the device will turn on a pull-down transistor for 16 state times. This enables the RESET signal to function as the system reset. The reset state of the external I/O is shown in Table 9, and the register reset values are shown in Table 8.

#### 1.1.3 Instruction Set

The instruction set for the UT80C196KD is compatible with the industry standard MCS-96 instruction set used on the 80C196KD.

| Table 5. Memory Map          |        |        |  |

|------------------------------|--------|--------|--|

| Memory Description           | Begin  | End    |  |

| External Memory <sup>1</sup> | 02080H | 0FFFFH |  |

| Reserved                     | 0205EH | 0207FH |  |

| PTS Vectors                  | 02040H | 0205DH |  |

| Upper Interrupt Vectors      | 02030H | 0203FH |  |

| Reserved                     | 02020H | 0202FH |  |

| Reserved                     | 02019H | 0201FH |  |

| Chip Configuration Byte      | 02018H | 02018H |  |

| Reserved                     | 02014H | 02017H |  |

| Lower Interrupt Vectors      | 02000H | 02013H |  |

| External Memory              | 00400H | 1FFFH  |  |

| Internal Memory (RAM)        | 0001AH | 003FFH |  |

| Special Function Registers   | 00000Н | 00019H |  |

<sup>1.</sup> The first instruction read following reset will be from location 2080h. All other external memory can be used as instruction and/or data memory.

| Table 6. Interrupt Vector Sources, Locations, and Priorities |                              |                                                              |                                 |                           |                                                  |

|--------------------------------------------------------------|------------------------------|--------------------------------------------------------------|---------------------------------|---------------------------|--------------------------------------------------|

| Number                                                       | Interrupt Vector             | Source(s)                                                    | Interrupt<br>Vector<br>Location | PTS<br>Vector<br>Location | Priority <sup>1</sup> (0 is the Lowest Priority) |

| Special                                                      | Unimplemented<br>Opcode      | Unimplemented Opcode                                         | 2012h                           | N/A                       | N/A                                              |

| Special                                                      | Software Trap                | Software Trap                                                | 2010h                           | N/A                       | N/A                                              |

| INT 15                                                       | NMI <sup>2</sup>             | NMI                                                          | 203Eh                           | N/A                       | 15                                               |

| INT 14                                                       | HSI FIFO Full                | HSI FIFO Full                                                | 203Ch                           | 205Ch                     | 14                                               |

| INT 13                                                       | EXTINT 1 <sup>2</sup>        | Port 2.2                                                     | 203Ah                           | 205Ah                     | 13                                               |

| INT 12                                                       | Timer 2 Overflow             | Timer 2 Overflow                                             | 2038h                           | 2058h                     | 12                                               |

| INT 11                                                       | Timer 2 Capture <sup>2</sup> | Timer 2 Capture                                              | 2036h                           | 2056h                     | 11                                               |

| INT 10                                                       | HSI FIFO 4                   | HSI FIFO<br>Fourth Entry                                     | 2034h                           | 2054h                     | 10                                               |

| INT 9                                                        | Receive                      | RI Flag <sup>3</sup>                                         | 2032h                           | 2052h                     | 9                                                |

| INT 8                                                        | Transmit                     | TI Flag <sup>3</sup>                                         | 2030h                           | 2050h                     | 8                                                |

| INT 7                                                        | EXTINT <sup>2</sup>          | Port 2.2 or Port 0.7                                         | 200Eh                           | 204Eh                     | 7                                                |

| INT 6                                                        | Serial Port                  | RI Flag and TI Flag <sup>4</sup>                             | 200Ch                           | 204Ch                     | 6                                                |

| INT 5                                                        | Software Timer               | Software Timer 0-3<br>Timer 2 Reset                          | 200Ah                           | 204Ah                     | 5                                                |

| INT 4                                                        | HSI.0 <sup>2</sup>           | HSI.0 Pin                                                    | 2008h                           | 2048h                     | 4                                                |

| INT 3                                                        | High Speed<br>Outputs        | Events on HSO.0 thru<br>HSO.5 Lines                          | 2006h                           | 2046h                     | 3                                                |

| INT 2                                                        | HSI Data Available           | HSI FIFO Full or<br>HSI Holding Reg.<br>Loaded               | 2004h                           | 2044h                     | 2                                                |

| INT 1                                                        | EDAC Bit Error               | Single Bit Error<br>Single Bit Error OVF<br>Double Bit Error | 2002h                           | 2042h                     | 1                                                |

| INT 0                                                        | Timer Overflow               | Timer 1 or Timer 2                                           | 2000h                           | 2040h                     | 0                                                |

All of the previous maskable interrupts can be assigned to the PTS. Any PTS interrupt has priority over all other maskable interrupts.

- 1. The Unimplemented Opcode and Software Trap interrupts are not prioritized. The Interrupt Controller immediately services these interrupts when they are asserted. NMI has the highest priority of all prioritized interrupts. Any PTS interrupt has priority over lower priority interrupts, and over all other maskable interrupts. The standard maskable interrupts are serviced according to their priority number with INTO has the lowest priority of all interrupts.

- 2. These interrupts can be configured to function as independant, external interrupts.

- 3. If the Serial interrupt is masked and the Receive and Transmit interrupts are enabled, the RI flag and TI flag generate separate Receive and Transmit interrupts.

- 4. If the Receive and Transmit interrupts are masked and the Serial interrupt is enabled, both RI flag and TI flag generate a Serial Port interrupt.

| Table 7. SFR Memory Mapping |                 |                 |                          |                      |

|-----------------------------|-----------------|-----------------|--------------------------|----------------------|

| Address                     | HWin 0 Read     | HWin 0 Write    | HWin 1                   | HWin 15 <sup>1</sup> |

| 019H                        | Stack Pntr (hi) | Stack Pntr (hi) | Stack Pntr (hi)          | Stack Pntr (hi)      |

| 018H                        | Stack Pntr (lo) | Stack Pntr (lo) | Stack Pntr (lo)          | Stack Pntr (lo)      |

| 017H                        | IOS2            | PWM0_CTRL       | PWM2_CTRL                | ***                  |

| 016H                        | IOS1            | IOC1            | PWM1_CTRL                | ***                  |

| 015H                        | IOS0            | IOC0            | EDAC-CS <sup>2</sup>     | ***                  |

| 014H                        | WSR             | WSR             | WSR                      | WSR                  |

| 013H                        | INT_MASK1       | INT_MASK1       | INT_MASK1                | INT_MASK1            |

| 012H                        | INT_PEND1       | INT_PEND1       | INT_PEND1                | INT_PEND1            |

| 011H                        | SP_STAT         | SP_CON          | RESERVED                 | ***                  |

| 010H                        | PORT 2          | PORT 2          | RESERVED                 | PSW <sup>2</sup>     |

| 00FH                        | PORT 1          | PORT 1          | Timer 3(hi) <sup>2</sup> | RESERVED             |

| 00EH                        | PORT 0          | BAUD RATE       | Timer 3(lo) <sup>2</sup> | RESERVED             |

| 00DH                        | Timer 2 (hi)    | Timer 2 (hi)    | WDT-SCALE <sup>2</sup>   | T2CAPTURE (hi)       |

| 00CH                        | Timer 2 (lo)    | Timer 2 (lo)    | IOC3                     | T2CAPTURE (lo)       |

| 00BH                        | Timer 1 (hi)    | IOC2            | INT_PRI(hi) <sup>2</sup> | ***                  |

| 00AH                        | Timer 1 (lo)    | Watchdog        | INT_PRI(lo) <sup>2</sup> | ***                  |

| 009H                        | INT_PEND        | INT_PEND        | INT_PEND                 | INT_PEND             |

| 008H                        | INT_MASK        | INT_MASK        | INT_MASK                 | INT_MASK             |

| 007H                        | SBUF (RX)       | SBUF (TX)       | PTSSRV (hi)              | ***                  |

| 006H                        | HSI_status      | HSO_command     | PTSSRV (lo)              | ***                  |

| 005H                        | HSI_time(hi)    | HSO_time (hi)   | PTSSEL (hi)              | ***                  |

| 004H                        | HSI_time (lo)   | HSO_time (lo)   | PTSSEL (lo)              | ***                  |

| 003H                        | RESERVED        | HSI_mode        | RESERVED                 | ***                  |

| 002H                        | RESERVED        | RESERVED        | RESERVED                 | RESERVED             |

| 001H                        | Zero_reg (hi)   | Zero_reg (hi)   | Zero-reg (hi)            | Zero_reg (hi)        |

| 000H                        | Zero_reg (lo)   | Zero_reg (lo)   | Zero_reg (lo)            | Zero_reg (lo)        |

<sup>1.</sup> For some functions that share a register address in HWindow0, the opposite access type (read/write) is available in HWindow 15 if

indicated by the three asterisks (\*\*\*).

2. These registers are not available in the industry standard 80C196KD. Therefore, industry standard development software will not recognize these mnemonics, and you will only be able to access them via their physical addresses.

| Table 8: Special Function Register Reset Values |                     |                            |  |

|-------------------------------------------------|---------------------|----------------------------|--|

| Internal Register                               | Binary Reset State  | Hexadecimal Reset<br>Value |  |

| Stack Pointer (SP)                              | XXXX XXXX XXXX XXXX | XXXX                       |  |

| I/O Status Register 2 (IOS2)                    | 0000 0000           | 00                         |  |

| I/O Status Register 1 (IOS1)                    | 0000 0000           | 00                         |  |

| I/O Status Register 0 (IOS0)                    | 0000 0000           | 00                         |  |

| Window Select Register (WSR)                    | 0000 0000           | 00                         |  |

| Interrupt Mask Register 1 (INT_MASK1)           | 0000 0000           | 00                         |  |

| Interrupt Pending Register 1<br>(INT_PEND1)     | 0000 0000           | 00                         |  |

| Serial Port Status Register (SP_STAT)           | 0000 1011           | 0B                         |  |

| Port 2 Register (PORT2)                         | 110X XXX1           | XX                         |  |

| Port 1 Register (PORT1)                         | 1111 1111           | FF                         |  |

| Port 0 Register (PORT0)                         | XXXX XXXX           | XX                         |  |

| Timer 2 Value Register (TIMER2)                 | 0000 0000 0000 0000 | 0000                       |  |

| Timer 1 Value Register (TIMER1)                 | 0000 0000 0000 0000 | 0000                       |  |

| Interrupt Pending Register (INT_PEND)           | 0000 0000           | 00                         |  |

| Interrupt Mask Register (INT_MASK)              | 0000 0000           | 00                         |  |

| Receive Serial Port Register (SBUF (RX))        | 0000 0000           | 00                         |  |

| HSI Status Register (HSI_status)                | X0X0 X0X0           | XX                         |  |

| HSI Time Register (HSI_time)                    | XXXX XXXX XXXX XXXX | XXXX                       |  |

| Zero Register (ZERO_REG)                        | 0000 0000 0000 0000 | 0000                       |  |

| PWM0 Control Register (PWM0_CTRL)               | 0000 0000           | 00                         |  |

| I/O Control Register 1 (IOC1)                   | 0010 0001           | 21                         |  |

| I/O Control Register 0 (IOC0)                   | 0000 00X0           | 0X                         |  |

| Serial Port Control Register (SP_CON)           | 0000 1011           | 0B                         |  |

| Baud Rate Register (BAUD_RATE)                  | 0000 0000 0000 0001 | 0001                       |  |

| I/O Control Register 2 (IOC2)                   | X00X X000           | XX                         |  |

| Watch Dog Timer Register (WATCH-DOG)            | 0000 0000           | 00                         |  |

| Table 8: Special Function Register Reset Values |                     |                            |  |

|-------------------------------------------------|---------------------|----------------------------|--|

| Internal Register                               | Binary Reset State  | Hexadecimal Reset<br>Value |  |

| Transmit Serial Port Buffer (SBUF (TX))         | 0000 0000           | 00                         |  |

| HSO Command Register<br>(HSO_command)           | 0000 0000           | 00                         |  |

| HSO Time Register (HSO_time)                    | 0000 0000 0000 0000 | 0000                       |  |

| HSI Mode Register (HSI_mode)                    | 1111 1111           | FF                         |  |

| PWM2 Control Register (PWM2_CTRL)               | 0000 0000           | 00                         |  |

| PWM1 Control Register (PWM1_CTRL)               | 0000 0000           | 00                         |  |

| EDAC Control and Status Register (EDAC_CS)      | 0000 0000           | 00                         |  |

| Timer 3 Value Register (TIMER3)                 | 0000 0000 0000 0000 | 0000                       |  |

| Watchdog Timer Prescaler<br>(WDT_SCALE)         | 0000 0000           | 00                         |  |

| I/O Control Register 3 (IOC3)                   | 1111 0000           | FO                         |  |

| Interrupt Priority Register (INT_PRI)           | 0000 0000           | 00                         |  |

| PTS Service Register (PTSSRV)                   | 0000 0000 0000 0000 | 0000                       |  |

| PTS Select Register (PTSSEL)                    | 0000 0000 0000 0000 | 0000                       |  |

| Timer 2 Capture Register<br>(T2CAPTURE)         | 0000 0000 0000 0000 | 0000                       |  |

| Program Counter (PC)                            | 0010 0000 1000 0000 | 2080                       |  |

| Chip Configuration Register (CCR)               | XX10 1111           | XF                         |  |

| Table 9: External I/O Reset State               |                                |                               |                               |

|-------------------------------------------------|--------------------------------|-------------------------------|-------------------------------|

| External I/O                                    | I/O Function After Reset       | I/O State During<br>Reset     | I/O State After Reset         |

| Address/Data Bus (AD15:0)                       | Address/Data Bus               | Pulled High                   | Driven Output                 |

| ALE<br>ADV                                      | ALE                            | Pulled High                   | Driven Output                 |

| RD                                              | RD                             | Pulled High                   | Driven Output                 |

| WRL WRL                                         | WR                             | Pulled High                   | Driven Output                 |

| Port 0 (P0.0-P0.3; P0.6)<br>ECB(4:0)            | [P0.0-P0.3; P0.6] and ECB(4:0) | Undefined Inputs <sup>1</sup> | Undefined I/O <sup>1, 2</sup> |

| Port 0 (P0.4 and P0.5)                          | P0.4 and P0.5                  | Undefined Inputs <sup>1</sup> | Undefined Inputs <sup>1</sup> |

| Port 0 (P0.7)<br>EXTINT                         | P0.7                           | Undefined Input <sup>1</sup>  | Undefined Input <sup>1</sup>  |

| NMI                                             | NMI                            | Pulled Down                   | Pulled Down                   |

| HSI.0<br>T2RST                                  | HSI.0                          | Disabled Input <sup>1</sup>   | Disabled Input <sup>1</sup>   |

| HSI.1<br>T2CLK                                  | HSI.1                          | Disabled Input <sup>1</sup>   | Disabled Input <sup>1</sup>   |

| HSI.2/HSO.4                                     | Undefined                      | Disabled I/O <sup>1</sup>     | Disabled I/O <sup>1</sup>     |

| HSI.3/HSO.5                                     | Undefined                      | Disabled I/O <sup>1</sup>     | Disabled I/O <sup>1</sup>     |

| HSO.0 through HSO.3                             | HSO.0-HSO.3                    | Pulled Down                   | Driven Low<br>Outputs         |

| Port 1 (P1.0-P1.7) PWM1; PWM2; BREQ; HLDA; HOLD | P1.0-P1.7                      | Pulled Up                     | Pulled Up                     |

| Port 2 (P2.0)<br>TXD                            | TXD                            | Pulled Up                     | Driven High<br>Output         |

| Port 2 (P2.1)<br>RXD                            | RXD                            | Undefined Input <sup>1</sup>  | Undefined Input <sup>1</sup>  |

| Port 2 (P2.2)<br>EXTINT                         | P2.2 and EXTINT                | Undefined Input <sup>1</sup>  | Undefined Input <sup>1</sup>  |

| Port 2 (P2.3)<br>T2CLK                          | P2.3 and T2CLK                 | Undefined Input <sup>1</sup>  | Undefined Input <sup>1</sup>  |

| Port 2 (P2.4)<br>T2RST                          | P2.4                           | Undefined Input <sup>1</sup>  | Undefined Input <sup>1</sup>  |

| Table 9: External I/O Reset State |                          |                              |                              |

|-----------------------------------|--------------------------|------------------------------|------------------------------|

| External I/O                      | I/O Function After Reset | I/O State During<br>Reset    | I/O State After Reset        |

| Port 2 (P2.5)<br>PWM0             | PWM0                     | Pulled Down                  | Driven Low Output            |

| Port 2 (P2.6)<br>T2UP-DN          | P2.6                     | Pulled Up                    | Pulled Up                    |

| Port 2 (P2.7)<br>T2CAPTURE        | P2.7 and T2CAPTURE       | Pulled Up                    | Pulled Up                    |

| EDACEN                            | EDACEN                   | Undefined Input <sup>1</sup> | Undefined Input <sup>1</sup> |

| ECB5                              | ECB5                     | Undefined I/O <sup>1</sup>   | Undefined I/O <sup>1,2</sup> |

| READY                             | READY                    | Undefined Input <sup>1</sup> | Undefined Input <sup>1</sup> |

| BUSWIDTH                          | BUSWIDTH                 | Undefined Input <sup>1</sup> | Undefined Input <sup>1</sup> |

| BHE<br>WRH                        | BHE                      | Pulled Up                    | Driven Output                |

| CLKOUT                            | CLKOUT                   | Driven Output                | Driven Output                |

| INST                              | INST                     | Pulled Down                  | Driven Output                |

| RESET                             | RESET                    | Pulled Low by<br>System      | Pulled Up                    |

These pins must not be left floating. Input voltages must not exceed V<sub>DD</sub> during power-up.

Do not directly tie these pins to V<sub>DD</sub> or GND; if EDACEN goes low, they may be driven by the UT80C196KD and bus contention may occur.

16-Bit Bus Figure 2. Bus Width Options

Figure 3. 68-pin Quad Flatpack Package

Legend for I/O fields: TDI = TTL compatible input (internally pulled low) = TTL compatible bidirectional TO = TTL compatible output TB ΤI = TTL compatible input = TTL compatible quasi-bidirectional TUQ = CMOS only input (internally pulled high) CI TUO = TTL compatible output TUB = TTL compatible bidirectional (internally pulled high) (internally pulled high) TDO = TTL compatible output **TUBS** = TTL compatible bidirectional Schmitt Trigger (internally pulled high) (internally pulled low) = TTL compatible input PWR  $= +5V (V_{DD})$ TUI (internally pulled high)  $= OV (V_{SS})$ **GND**

| Table 10: 68-lead Flat Pack Pin Descriptions |     |                         |                                                                                                                                                               |                                                                                                                                                                                                          |

|----------------------------------------------|-----|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP Pin#                                     | I/O | Name Active Description |                                                                                                                                                               | Description                                                                                                                                                                                              |

| 1                                            | PWR | V <sub>DD</sub>         |                                                                                                                                                               | Digital supply voltage (+5V). There are 2 $V_{DD}$ pins, both of which must be connected.                                                                                                                |

| 2                                            | ТВ  | ECB5 <sup>1</sup>       | EDAC Check Bit 5. Asserting the EDACEN pin will cause the error detection and correction engine to pass the EDAC Check Bit 5 through pin 2 of the UT80C196KD. |                                                                                                                                                                                                          |

| 3                                            | TDI | NMI                     | High                                                                                                                                                          | Non-Maskable Interrupt. A positive transition causes a vector through the NMI interrupt at location 203Eh. Assert NMI for at least 1 state time to guarantee acknowledgment by the interrupt controller. |

| 4                                            | TI  | P0.3                    |                                                                                                                                                               | Port 0 Pin 3. An input only port pin that is read at location 0Eh in HWindow 0.                                                                                                                          |

|                                              | ТВ  | ECB4 <sup>1</sup>       |                                                                                                                                                               | EDAC Check Bit 4. Asserting the EDACEN pin will cause the error detection and correction engine to pass the EDAC Check Bit 4 through pin 4 of the UT80C196KD.                                            |

| 5                                            | TI  | P0.1                    | Port 0 Pin 1. An input only port pin that is read at location in HWindow 0.                                                                                   |                                                                                                                                                                                                          |

|                                              | ТВ  | ECB3 <sup>1</sup>       |                                                                                                                                                               | EDAC Check Bit 3. Asserting the EDACEN pin will cause the error detection and correction engine to pass the EDAC Check Bit 3 through pin 5 of the UT80C196KD.                                            |

| 6                                            | TI  | P0.0                    | Port 0 Pin 0. An input only port pin that is read at location 0 in HWindow 0.                                                                                 |                                                                                                                                                                                                          |

|                                              | ТВ  | ECB2 <sup>1</sup>       |                                                                                                                                                               | EDAC Check Bit 2. Asserting the EDACEN pin will cause the error detection and correction engine to pass the EDAC Check Bit 2 through pin 6 of the UT80C196KD.                                            |

|          |     | Tab               | le 10: 68-le | ad Flat Pack Pin Descriptions                                                                                                                                                                                                                                       |

|----------|-----|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFP Pin# | I/O | Name              | Active       | Description                                                                                                                                                                                                                                                         |

| 7        | TI  | P0.2              |              | Port 0 Pin 2. An input only port pin that is read at location 0Eh in HWindow 0.                                                                                                                                                                                     |

|          | ТВ  | ECB1 <sup>1</sup> |              | EDAC Check Bit 1. Asserting the EDACEN pin will cause the error detection and correction engine to pass the EDAC Check Bit 1 through pin 7 of the UT80C196KD.                                                                                                       |

| 8        | TI  | P0.6              |              | Port 0 Pin 6. An input only port pin that is read at location 0Eh in HWindow 0.                                                                                                                                                                                     |

|          | ТВ  | ECB0 <sup>1</sup> |              | EDAC Check Bit 0. Asserting the EDACEN pin will cause the error detection and correction engine to pass the EDAC Check Bit 0 through pin 8 of the UT80C196KD.                                                                                                       |

| 9        | TI  | P0.7              |              | Port 0 Pin 7. An input only port pin that is read at location 0Eh in HWindow 0.                                                                                                                                                                                     |

|          | TI  | EXTINT            | High         | External Interrupt. Setting IOC1.1 = 1 enables pin 9 as the source for the external interrupt EXTINT. A rising edge on this pin will generate EXTINT (INT07, 200Eh). Assert EXTINT for at least 2 state times to ensure acknowledgment by the interrupt controller. |

|          |     |                   |              | During Power Down mode, asserting EXTINT places the chip back into normal operation, even if EXTINT is masked.                                                                                                                                                      |

| 10       | TI  | P0.5              |              | Port 0 Pin 5. An input only port pin that is read at location 0Eh in HWindow 0.                                                                                                                                                                                     |

| 11       | TI  | P0.4              |              | Port 0 Pin 4. An input only port pin that is read at location 0Eh in HWindow 0.                                                                                                                                                                                     |

| 12       | GND | $V_{SS}$          |              | Digital circuit ground (0V). There are 4 $V_{SS}$ pins, all of which must be connected and one additional recommeded $V_{SS}$ connection.                                                                                                                           |

| 13       | PWR | $V_{\mathrm{DD}}$ |              | Digital supply voltage (+5V). There are 2 V <sub>DD</sub> pins, both of which must be connected.                                                                                                                                                                    |

| 14       | GND | $ m V_{SS}$       |              | Digital circuit ground (0V). There are 4 $V_{SS}$ pins, all of which must be connected and one additional recommeded $V_{SS}$ connection.                                                                                                                           |

|                 |      | Tab    | le 10: 68-le | ad Flat Pack Pin Descriptions                                                                                                                                                                                                                                                                                                                                             |  |

|-----------------|------|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP Pin#        | I/O  | Name   | Active       | Description                                                                                                                                                                                                                                                                                                                                                               |  |

| 15              | TI   | P2.2   |              | Port 2 Pin 2. An input only port pin that is written at location 10h of HWindow 0. P2.2 will always generate EXTINT1 (INT13, 203Ah) unless masked by the INT_MASK1 register. Assert EXTINT1 for at least 2 state times to guarantee acknowledgment by the interrupt controller.                                                                                           |  |

|                 | TI   | EXTINT | High         | External Interrupt. Setting IOC1.1 = 0 enables pin 15 as the source for the external interrupt EXTINT. A rising edge on this pin will generate EXTINT (INT07, 200Eh). Assert EXTINT for at least 2 state times to ensure acknowledgment by the interrupt controller.                                                                                                      |  |

|                 |      |        |              | During Power Down mode, asserting EXTINT places the chip back into normal operation, even if EXTINT is masked.                                                                                                                                                                                                                                                            |  |

| 16              | TUBS | RESET  | Low          | Master Reset. The first external reset signal supplied to the UT80C196KD must be active for at least 16 state times. All subsequent RESET assertions need only be active for 1 state time because the UT80C196KD will continue driving the RESET signal for an additional 16 state times. See section 1.1.2 for more information on the RESET function of the UT80C196KD. |  |

| 17              | TI   | P2.1   |              | Port 2 Pin 1. An input only port pin that is read at location 10h of HWindow 0.                                                                                                                                                                                                                                                                                           |  |

|                 |      |        |              | Setting SPCON.3 = 0 enables the P2.1 function of pin 17.                                                                                                                                                                                                                                                                                                                  |  |

|                 | ТВ   | RXD    |              | RXD is a bidirectional serial data port. When operating in Serial Modes 1, 2, and 3, RXD receives serial data. When using Serial Mode 0, RXD operates as an input and an open-drain output for data.                                                                                                                                                                      |  |

|                 |      |        |              | Setting SPCON.3 = 1 enables the RXD function of pin 17.                                                                                                                                                                                                                                                                                                                   |  |

| 18 <sup>2</sup> | TUO  | P2.0   |              | Port 2 Pin 0. An output only port pin that is written at location 10h of HWindow 0.                                                                                                                                                                                                                                                                                       |  |

|                 |      |        |              | Setting IOC1.5 = 0 enables the P2.0 function of pin 18.                                                                                                                                                                                                                                                                                                                   |  |

|                 | TUO  | TXD    |              | Transmit Serial Data (TXD). When set to Serial Mode 1, 2, or 3 TXD transmits serial port data. When using Serial Mode 0, TXD is used as the Serial Clock output.                                                                                                                                                                                                          |  |

|                 |      |        |              | Setting IOC1.5 = 1 enables the TXD function of pin 18.                                                                                                                                                                                                                                                                                                                    |  |

|                 | TUI  | ĪCT    | Low          | In-Circuit Test. The UT80C196KD will enter the In-Circuit Test mode if this pin is held low during the rising edge of RESET.                                                                                                                                                                                                                                              |  |

|          |     | Tab   | le 10: 68-le | ad Flat Pack Pin Descriptions                                                                                                                                                                                                                |  |

|----------|-----|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP Pin# | I/O | Name  | Active       | Description                                                                                                                                                                                                                                  |  |

| 19       | TUQ | P1.0  |              | Port 1 Pin 0. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                                                                                                          |  |

| 20       | TUQ | P1.1  |              | Port 1 Pin 1. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                                                                                                          |  |

| 21       | TUQ | P1.2  |              | Port 1 Pin 2. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                                                                                                          |  |

| 22       | TUQ | P1.3  |              | Port 1 Pin 3. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.  Setting IOC3.2 = 0 enables the P1.3 function of pin 22.                                                                                 |  |

|          |     |       |              | Setting IOC3.2 = 0 enables the P1.3 function of pin 22.                                                                                                                                                                                      |  |

|          | TUO | PWM1  |              | Pulse Width Modulator (PWM) Output 1. The output signal will be a waveform whose duty cycle is programmed by the PWM1_CONTROL register, and the frequency is selected by IOC2.2.                                                             |  |

|          |     |       |              | Setting IOC3.2 = 1 enables the PWM1 function of pin 22.                                                                                                                                                                                      |  |

| 23       | TUQ | P1.4  |              | Port 1 Pin 4. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                                                                                                          |  |

|          |     |       |              | Setting IOC3.3 = 0 enables the P1.4 function of pin 23.                                                                                                                                                                                      |  |

|          | TUO | PWM2  |              | Pulse Width Modulator (PWM) Output 2. The output signal will be a waveform whose duty cycle is programmed by the PWM2_CONTROL register, and the frequency is selected by IOC2.2.                                                             |  |

|          |     |       |              | Setting IOC3.3 = 1 enables the PWM2 function of pin 23.                                                                                                                                                                                      |  |

| 24       | TI  | HSI.0 |              | High Speed Input Module, input pin 0. Unless masked, a rising edge on this input will generate the HSI.0 Pin interrupt (INT04, 2008h). Assert the HSI.0 pin for at least 2 state times to ensure acknowledgment by the interrupt controller. |  |

|          |     |       |              | Setting IOC0.0 = 1 enables pin 24 as an HSI input, and allows events on this pin to be loaded into the HSI FIFO.                                                                                                                             |  |

|          | TI  | T2RST | High         | Timer 2 Reset. A rising edge on the T2RST pin resets Timer 2.                                                                                                                                                                                |  |

|          |     |       |              | To enable the T2RST function of pin 24, set IOC0.3 = 1 and IOC0.5 = 1.                                                                                                                                                                       |  |

|          |     | Tabl  | le 10: 68-le | ad Flat Pack Pin Descriptions                                                                                                                                                     |  |

|----------|-----|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP Pin# | I/O | Name  | Active       | Description                                                                                                                                                                       |  |

| 25       | TI  | HSI.1 |              | High Speed Input Module, input pin 1.                                                                                                                                             |  |

|          |     |       |              | Setting IOC0.2 = 1 enables pin 25 as an HSI input, and allows events on this pin to be loaded into the HSI FIFO.                                                                  |  |

|          | TI  | T2CLK |              | Timer 2 Clock.                                                                                                                                                                    |  |

|          |     |       |              | Setting IOC0.7 = 1 and IOC3.0 = 0 enables pin 25 to function as the Timer 2 clock source.                                                                                         |  |

| 26       | ТО  | HSO.4 |              | High Speed Output Module, output pin 4. This pin can simultaneously operate in the HSI and HSO modes of operation. As a result, this pin acts as an output that the HSI monitors. |  |

|          |     |       |              | Setting IOC1.4 = 1 enables the HSO.4 function of pin 26.  High Speed Input Module, input pin 2. This pin can simulta-                                                             |  |

|          | TI  | HSI.2 |              | High Speed Input Module, input pin 2. This pin can simultaneously operate in the HSI and HSO modes of operation. As a result, this pin can monitor events on the HSO.             |  |

|          |     |       |              | Setting IOC0.4 = 1 enables pin 26 as an HSI input pin, and allows events on this pin to be loaded into the HSI FIFO.                                                              |  |

| 27       | ТО  | HSO.5 |              | High Speed Output Module, output pin 5. This pin can simultaneously operate in the HSI and HSO modes of operation. As a result, this pin acts as an output that the HSI monitors. |  |

|          |     |       |              | Setting IOC1.6 = 1 enables the HSO.5 function of pin 27.                                                                                                                          |  |

|          | TI  | HSI.3 |              | High Speed Input Module, input pin 3. This pin can simultaneously operate in the HSI and HSO modes of operation. As a result, this pin can monitor events on the HSO.             |  |

|          |     |       |              | Setting IOC0.6 = 1 enables pin 27 as an HSI input pin, and allows events on this pin to be loaded into the HSI FIFO.                                                              |  |

| 28       | TDO | HSO.0 |              | High Speed Output Module, output pin 0. The HSO.0 pin is a dedicated output for the HSO module.                                                                                   |  |

| 29       | TDO | HSO.1 |              | High Speed Output Module, output pin 1. The HSO.1 pin is a dedicated output for the HSO module.                                                                                   |  |

|                 |     | Tabl    | e 10: 68-le | ad Flat Pack Pin Descriptions                                                                                                                                                                               |  |  |

|-----------------|-----|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP Pin#        | I/O | Name    | Active      | Description                                                                                                                                                                                                 |  |  |

| 30              | TUQ | P1.5    |             | Port 1 Pin 5. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                                                                         |  |  |

|                 |     |         |             | Setting WSR.7 = 0 enables the P1.5 function of pin 30.                                                                                                                                                      |  |  |

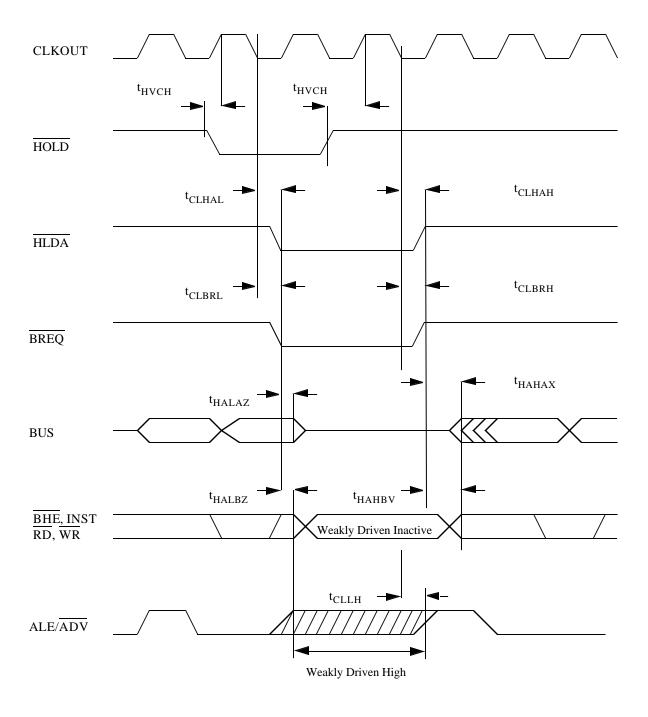

|                 | TUO | BREQ    | Low         | Bus Request. The BREQ output signal asserts during a HOLD cycle when the internal bus controller has a pending external memory cycle.                                                                       |  |  |

|                 |     |         |             | During a HOLD cycle, BREQ will not be asserted until the HLDA signal is asserted. Once asserted, BREQ does not deassert until the HOLD signal is released.                                                  |  |  |

|                 |     |         |             | Setting WSR.7 = 1 enables the $\overline{BREQ}$ function of pin 30.                                                                                                                                         |  |  |

| 31 <sup>2</sup> | TUQ | P1.6    |             | Port 1 Pin 6. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                                                                         |  |  |

|                 |     |         |             | Setting WSR.7 = 0 enables the P1.6 function of pin 31.                                                                                                                                                      |  |  |

|                 | TUO | HLDA    | Low         | Bus Hold Acknowledge. The UT80C196KD asserts the HLDA signal as a result of another device activating the HOLD signal. By asserting this signal, the UT80C196KD is indicating that it has released the bus. |  |  |

|                 |     |         |             | Setting WSR.7 = 1 enables the $\overline{\text{HLDA}}$ function of pin 31.                                                                                                                                  |  |  |

| 32              | TUQ | P1.7    |             | Setting WSR.7 = 1 enables the HLDA function of pin 31.  Port 1 Pin 7. A quasi-bidirectional port pin that is read and written at location 0Fh of HWindow 0.                                                 |  |  |

|                 |     |         |             | Setting WSR.7 = 0 enables the P1.7 function of pin 32.                                                                                                                                                      |  |  |

|                 | TUI | HOLD    | Low         | Bus Hold. The HOLD signal is used to request control of the bus by another DMA device.                                                                                                                      |  |  |

|                 |     |         |             | Setting WSR.7 = 1 enables the $\overline{HOLD}$ function of pin 32.                                                                                                                                         |  |  |

| 33              | TUQ | P2.6    |             | Port 2 Pin 6. A quasi-bidirectional port pin that is read and written at location 10h of HWindow 0.                                                                                                         |  |  |

|                 |     |         |             | Setting IOC2.1 = 0 enables the P2.6 function of pin 33.                                                                                                                                                     |  |  |

|                 | TUI | T2UP-DN |             | Timer 2 Up or Down. The T2UP-DN pin will dynamically change the direction that Timer 2 counts.                                                                                                              |  |  |

|                 |     |         |             | T2UP-DN = 1 then Timer 2 counts down. T2UP-DN = 0 then Timer 2 counts up.                                                                                                                                   |  |  |

|                 |     |         |             | Setting IOC2.1 = 1 enables the T2UP-DN function of pin 33.<br>When IOC2.1 = 0, Timer 2 will only count up.                                                                                                  |  |  |

|                 | Table 10: 68-lead Flat Pack Pin Descriptions |                 |        |                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------|----------------------------------------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| QFP Pin#        | I/O                                          | Name            | Active | Description                                                                                                                                                                                                                                                                                                                                               |  |  |

| 34              | TDO                                          | HSO.2           |        | High Speed Output Module, output pin 2. The HSO.2 pin is a dedicated output for the HSO module.                                                                                                                                                                                                                                                           |  |  |

| 35              | TDO                                          | HSO.3           |        | High Speed Output Module, output pin 3. The HSO.3 pin is a dedicated output for the HSO module.                                                                                                                                                                                                                                                           |  |  |

| 36              | GND                                          | V <sub>SS</sub> |        | Digital circuit ground (0V). There are 4 $V_{SS}$ pins, all of which must be connected and one additional recommeded $V_{SS}$ connection.                                                                                                                                                                                                                 |  |  |

| 37              | TI                                           | EDACEN          | Low    | EDAC Enable. Asserting the EDACEN signal activates the error detection and correction engine. This causes the UT80C196KD to include ECB(5:0) as the EDAC check bit pins in all external memory cycles.                                                                                                                                                    |  |  |

| 38              | TUQ                                          | P2.7            |        | Port 2 Pin 7. A quasi-bidirectional port pin that is read and written at location 10h of HWindow 0.                                                                                                                                                                                                                                                       |  |  |

|                 | TUQ                                          | T2CAPTURE       | High   | Timer 2 Capture. A rising edge on this pin loads the value of Timer 2 into the T2CAPTURE register, and generates a Timer 2 Capture interrupt (INT11, 2036h). Assert the T2CAPTURE signal for at least 2 state times to guarantee acknowledgment by the interrupt controller. Using INT_Mask1.3 controls whether or not a rising edge causes an interrupt. |  |  |

| 39              | TDO                                          | P2.5            |        | Port 2 Pin 5. An output only port pin that is written at location 10h of HWindow 0.                                                                                                                                                                                                                                                                       |  |  |

|                 |                                              |                 |        | Setting IOC1.0 = 0 enables the P2.5 function of pin 39.                                                                                                                                                                                                                                                                                                   |  |  |

|                 | TDO                                          | PWM0            |        | Pulse Width Modulator (PWM) Output 0. The output signal will be a waveform whose duty cycle is programmed by the PWM0_CONTROL register, and the frequency is selected by IOC2.2.                                                                                                                                                                          |  |  |

| 2               | <b>TV</b> 10                                 |                 | _      | Setting IOC1.0 = 1 enables the PWM0 function of pin 39.                                                                                                                                                                                                                                                                                                   |  |  |

| 40 <sup>2</sup> | TUO                                          | WR              | Low    | Write. The WR signal indicates that an external write is occurring. Activation of this signal only occurs during external memory writes.                                                                                                                                                                                                                  |  |  |

|                 |                                              |                 |        | Setting CCR.2 = 1 enables the $\overline{WR}$ function of pin 40.                                                                                                                                                                                                                                                                                         |  |  |

|                 | TUO                                          | WRL             | Low    | Write Low. The WRL signal is activated when writing the low byte of a 16-bit wide word, and is always asserted for 8-bit wide memory writes.                                                                                                                                                                                                              |  |  |

|                 |                                              |                 |        | Setting CCR.2 = 0 enables the $\overline{WRL}$ function of pin 40.                                                                                                                                                                                                                                                                                        |  |  |

|          |     | Tab   | le 10: 68-le | ead Flat Pack Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|----------|-----|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QFP Pin# | I/O | Name  | Active       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 41       | TUO | внЕ   | Low          | Byte High Enable. The assertion of the BHE signal will occur for all 16-bit word writes, and high byte writes in both 8- and 16-bit wide bus cycles.  Setting CCR.2 = 1 enables the BHE function of pin 41.                                                                                                                                                                                                                                                                                                                                                                  |  |

|          |     |       | _            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|          | TUO | WRH   | Low          | Write High. The WRH signal is asserted for high byte writes, and word writes for 16-bit wide bus cycles. Additionally, WRH is asserted for all write operations when using an 8-bit wide bus cycle.                                                                                                                                                                                                                                                                                                                                                                          |  |

|          |     |       |              | Setting CCR.2 = 0 enables the $\overline{WRH}$ function of pin 41.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 42       | TI  | P2.4  |              | Port 2 Pin 4. An input only port pin that is read at location 10h of HWindow 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |