### US5S108 1.8V, 2.5V, 3.3V LVCMOS Clock Buffer

## Description

The US5S104, US5S106, US5S108, US5S110, US5S112 is a modular high-performance, low-skew, generalpurpose clock fanout buffer family. These clock buffers are designed with a modular approach in mind.

Five different fan-out variations, 1:4 to 1:12, are available. All of the devices are pin-compatible to each other for easy handling.

All family members share the same high performing characteristics such as low additive jitter, low skew, and wide operating temperature range.

All family members support an asynchronous output enable control (1G) which switches the outputs into a low state when 1G is low.

Operates in a 1.8-V, 2.5-V and 3.3-V environment and are characterized for operation from  $-40^{\circ}$ C to  $125^{\circ}$ C.

### Features

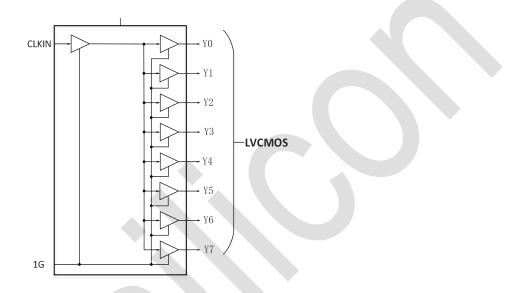

- High-Performance 1:8 LVCMOS Clock Buffer

- Extremely low additive jitter < 25-fs nominal

- Output Skew < 55 ps (Typical)

- Very low propagation delay < 3 ns

- Synchronous Output Enable Is Available

- Outputs Operate up to 250 MHz for 3.3V

- Outputs Operate up to 200 MHz for 2.5V and 1.8V

- Supply voltage: 3.3V, 2.5V or 1.8V

- Industrial Temperature Range: -40°C to 125°C

- Available in 16-Pin TSSOP Package

### Applications

General-Purpose Communication, Industrial, and Consumer Applications

### **Device Information**

| Part Number | Package  | Body Size(NOM)  |

|-------------|----------|-----------------|

| US5S108     | TSSOP-16 | 5.00mm x 4.40mm |

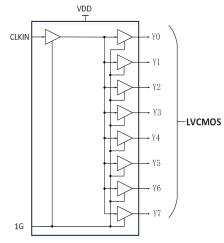

# **Block Diagram**

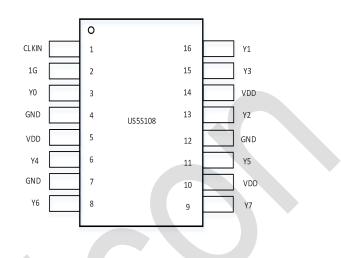

# **Pin Description and Function Table**

### **Table 1: Pin Descriptions**

| Number | Name  | Туре   | Description                                                                                                                                                                              |  |

|--------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | CLKIN | Input  | Single-ended clock input with internal 150-k $\Omega$ (typical) pulldown resistor to GND. Typical connected to a single-ended clock input.                                               |  |

| 2      | 1G    | Input  | Global Output Enable with internal 50-kΩ (typical) pulldown resistor to GND. Typically connected to VDD with external pullup resistor.<br>HIGH: outputs enabled<br>LOW: outputs disabled |  |

| 3      | Y0    | Output | LVCMOS output 0. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 4      | GND   | Power  | Ground.                                                                                                                                                                                  |  |

| 5      | VDD   | Power  | DC power supply, $1.8V - 3.6V$ . Typically connected to a $3.3-V$ , $2.5-V$ , or $1.8-V$ supply. The VDD pin is typically connected to an external $0.1-\mu F$ capacitor near the pin.   |  |

| 6      | Y4    | Output | LVCMOS output 4. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 7      | GND   | Power  | Ground.                                                                                                                                                                                  |  |

| 8      | Y6    | Output | LVCMOS output 6. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 9      | Y7    | Output | LVCMOS output 7. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 10     | VDD   | Power  | DC power supply, $1.8V - 3.6V$ . Typically connected to a $3.3-V$ , $2.5-V$ , or $1.8-V$ supply. The VDD pin is typically connected to an external $0.1-\mu F$ capacitor near the pin.   |  |

| 11     | Y5    | Output | LVCMOS output 5. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 12     | GND   | Power  | Ground.                                                                                                                                                                                  |  |

| 13     | Y2    | Output | LVCMOS output 2. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 14     | VDD   | Power  | DC power supply, $1.8V - 3.6V$ . Typically connected to a $3.3-V$ , $2.5-V$ , or $1.8-V$ supply. The VDD pin is typically connected to an external $0.1-\mu F$ capacitor near the pin.   |  |

| 15     | Y3    | Output | LVCMOS output 3. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

| 16     | Y1    | Output | LVCMOS output 1. Typically connected to a receiver. Unused outputs can be left floating.                                                                                                 |  |

## **Absolute Maximum Ratings**

Exposure to absolute maximum rating conditions for extended periods may affect product reliability. Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of the product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characteristics* is not implied.

| Item                                       | Rating                           |

|--------------------------------------------|----------------------------------|

| V <sub>DD</sub> : Supply voltage           |                                  |

| V <sub>CLKIN</sub> : Input voltage (CLKIN) | 0.5V to 3.6V                     |

| V <sub>IN</sub> : Input voltage (1G)       |                                  |

| V <sub>Yn :</sub> Output pins (Yn)         | -0.5V to V <sub>DD</sub> + 0.3 V |

| T <sub>STG</sub> :Storage Temperature      | -65°C to 150°C                   |

## **ESD** Ratings

|                                   |                                                         | Max   | Unit |

|-----------------------------------|---------------------------------------------------------|-------|------|

|                                   | Human-body model (HBM), ANSI/ESDA/JEDEC JS-001-2017     | ±2500 |      |

| V(ESD)<br>Electrostatic discharge | Machine model (MM), JEDEC Std. JESD22-A115-C            | ±250  | V    |

|                                   | Charged-device model (CDM), ANSI/ESDA/JEDEC JS-002-2018 | ±750  | -    |

## Latch up

|          |                           | Мах  | Unit |

|----------|---------------------------|------|------|

| Leteb un | I-test, JEDEC STD JESD78E | ±200 | mA   |

| Latch up | V-test, JEDEC STD JESD78E | 4.6  | V    |

### Recommended Operating Conditions

| Symbol          | Parameter                                     | Min    | Тур | Мах    | Unit |

|-----------------|-----------------------------------------------|--------|-----|--------|------|

| T <sub>A</sub>  | Ambient air temperature                       | -40    | -   | 85     | °C   |

| TJ              | Junction temperature                          |        | -   | 125    | °C   |

|                 |                                               | 3.3-5% | 3.3 | 3.3+5% |      |

| V <sub>DD</sub> | Power supply for Core and input Buffer blocks | 2.5-5% | 2.5 | 2.5+5% | V    |

|                 |                                               | 1.8-5% | 1.8 | 1.8+5% |      |

# **Electrical Characteristics**

VDD =  $3.3 \text{ V} \pm 5 \%$ ,  $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$ . Typical values are at VDD = 3.3 V,  $25^{\circ}\text{C}$  (unless otherwise noted)

| PA                           | RAMETER                               | TEST CONDITIONS                                                                                                               | MIN                   | TYP  | MAX       | UNIT       |

|------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-----------|------------|

|                              |                                       | All-outputs active, $f_{IN} = 100$ MHz, $C_L = 5pF$ , $V_{DD} = 1.8$ V                                                        |                       | 20   |           |            |

| IDD                          | Core supply current                   | All-outputs active, $f_{IN} = 100$ MHz, $C_L = 5pF$ , $V_{DD} = 2.5$ V<br>All-outputs active, $f_{IN} = 100$ MHz, $C_L = 100$ |                       | 27   |           | mA         |

|                              |                                       | All-outputs active, $IIN = 100$ MHz, $CL = 5pF$ , $V_{DD} = 3.3$ V                                                            |                       | 37   |           |            |

| CLOCK IN                     | IPUT                                  |                                                                                                                               | 1                     | L    |           |            |

|                              |                                       | V <sub>DD</sub> = 3.3 V                                                                                                       | 0.1                   |      | 250       |            |

| fin_se                       | Input frequency                       | VDD = 2.5 V and 1.8 V                                                                                                         | 0.1                   |      | 200       | - MHz      |

| Viн                          | Input high voltage                    |                                                                                                                               | 0.7 x V <sub>DD</sub> |      |           | v          |

| VIL                          | Input low voltage                     |                                                                                                                               |                       |      | 0.3 x Vdd | <b>− v</b> |

| dVın/dt                      | Input slew rate                       | 20% - 80% of input swing                                                                                                      | 0.1                   |      |           | V/ns       |

| lin_leak                     | Input leakage<br>current              |                                                                                                                               | -50                   |      | 50        | uA         |

| $C_{\text{IN}\_\text{SE}}$   | Input capacitance                     | at 25°C                                                                                                                       |                       | 7    |           | pF         |

| CLOCK O                      | UTPUT FOR ALL VDD                     |                                                                                                                               |                       |      |           | 1          |

| fout                         | Output frequency                      | VDD = 3.3 V                                                                                                                   | 0.1                   |      | 250       | MHz        |

| 1001                         |                                       | VDD = 2.5 V and 1.8 V                                                                                                         | 0.1                   |      | 200       |            |

| O <sub>DC</sub>              | Output duty cycle                     | With 50% duty cycle input                                                                                                     | 45                    |      | 55        | %          |

| <b>t</b> start               | Start-up time before output is active | See (1)                                                                                                                       |                       |      | 3         | ms         |

| t <sub>1G_ON</sub>           | Output enable time                    | See (2)                                                                                                                       |                       |      | 5         | cycles     |

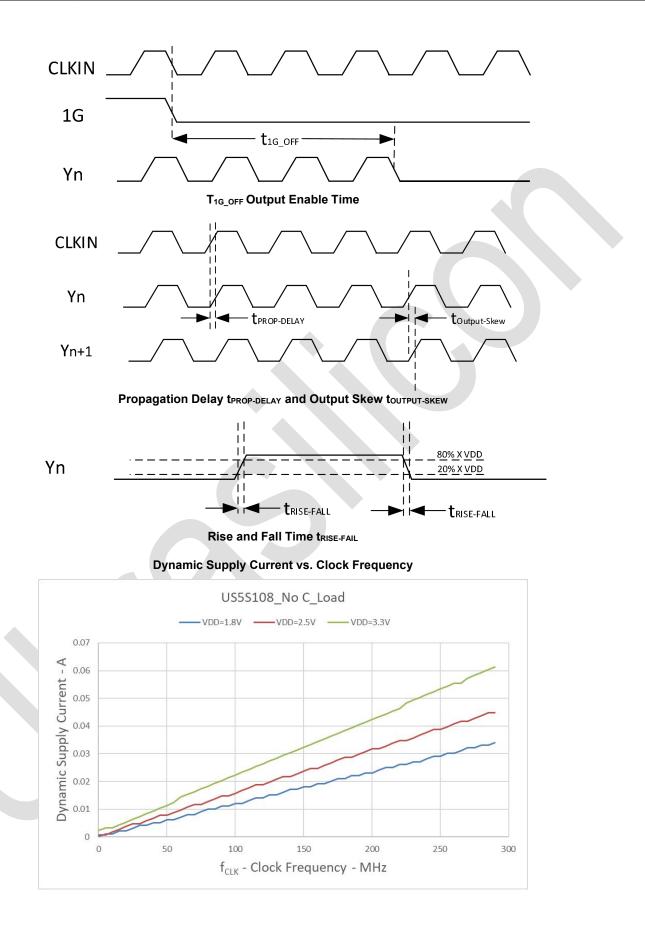

| t <sub>1G_OFF</sub>          | Output disable time                   | See (3)                                                                                                                       |                       |      | 5         | cycles     |

|                              | UTPUT FOR VDD = 3.3                   |                                                                                                                               |                       |      |           |            |

| Vон                          | Output high voltage                   | юн = -1 mA                                                                                                                    | 2.8                   |      |           | v          |

| V <sub>OL</sub>              | Output low voltage                    | IoL = 1 mA                                                                                                                    |                       |      | 0.2       |            |

| t <sub>RISE-FALL</sub>       | Output rise and fall time             | 20/80%, C∟= 5 pF, f <sub>IN</sub> = 156.25 MHz                                                                                |                       | 0.35 | 0.7       | ns         |

| t <sub>output-</sub><br>skew | Output-output skew                    | See (4)                                                                                                                       |                       | 25   | 50        | 20         |

| t <sub>PART-</sub><br>SKEW   | Part-to-part skew                     |                                                                                                                               |                       |      | 450       | – ps       |

| tpropdela<br>Y               | Propagation delay                     | See (5)                                                                                                                       |                       | 1.5  | 2         | ns         |

| t <sub>JITTER-ADD</sub>      | Additive Jitter                       | fin = 100 MHz, Input slew rate = 2 V/ns,<br>Integration range = 12 kHz - 20 MHz                                               |                       | 20   | 35        | fs, RMS    |

| Rout                         | Output impedance                      |                                                                                                                               |                       | 50   |           | Ω          |

| CLOCK C                      | OUTPUT FOR VDD = 2.5                  | 5 V ± 5%                                                                                                                      |                       |      |           |            |

| V <sub>он</sub>              | Output high voltage                   | Iон = -1 mA                                                                                                                   | 0.8 x Vdd             |      |           |            |

| Vol                          | Output low voltage                    | IOL = 1 mA                                                                                                                    |                       |      | 0.2 x Vdd | V          |

| t <sub>RISE-FALL</sub>       | Output rise and fall time             | 20/80%, CL= 5 pF, fin = 156.25 MHz                                                                                            |                       | 0.33 | 0.8       | ns         |

| t <sub>output-</sub><br>skew | Output-output skew                    | See (4                                                                                                                        |                       |      | 50        | ne         |

| t <sub>PART-</sub><br>SKEW   | Part-to-part skew                     |                                                                                                                               |                       |      | 400       | – ps       |

| t <sub>PROP-</sub><br>DELAY  | Propagation delay                     | See (5)                                                                                                                       |                       | 1.5  | 2.5       | ns         |

| tjitter-add                  | Additive Jitter                       | $f_{IN}$ = 100 MHz, Input slew rate = 2 V/ns,<br>Integration range = 12 kHz - 20 MHz                                          |                       | 25   | 45        | fs, RMS    |

| Rout                         | Output impedance                      |                                                                                                                               |                       | 50   |           | Ω          |

(1) Measured from VDD stable to output active, when 1G = HIGH.

(2) Measured from 1G rising edge crossing VIH to first rising edge of Yn.

(3) Measured from 1G falling edge crossing VIL to last falling edge of Yn.

(4) Measured from rising edge of any Yn output to any other Ym output.

| PARAMETER           |                           | TEST CONDITIONS                                                                 | MIN       | TYP  | MAX       | UNIT    |

|---------------------|---------------------------|---------------------------------------------------------------------------------|-----------|------|-----------|---------|

| CLOCK OUTF          | PUT FOR VDD = 1.8 V ± 5%  |                                                                                 | 1         |      | 1         |         |

| Vон                 | Output high voltage       | Іон = -1 mA                                                                     | 0.8 x Vdd |      |           |         |

| Vol                 | Output low voltage        | IoL = 1 mA                                                                      |           |      | 0.2 x VDD | - V     |

| trise-fall          | Output rise and fall time | 20/80%, CL= 5 pF, fin = 156.25 MHz                                              |           | 0.38 | 1         | ns      |

| toutput-skew        | Output-output skew        | See (4)                                                                         |           |      | 50        | ps      |

| <b>t</b> PART-SKEW  | Part-to-part skew         |                                                                                 |           |      | 900       | ps      |

| <b>t</b> PROP-DELAY | Propagation delay         | See (5)                                                                         |           | 1.5  | 3         | ns      |

| tjitter-add         | Additive Jitter           | fin = 100 MHz, Input slew rate = 2 V/ns,<br>Integration range = 12 kHz - 20 MHz |           | 55   | 85        | fs, RMS |

| Rout                | Output impedance          |                                                                                 |           | 50   |           | Ω       |

| GENERAL PU          | RPOSE INPUT (1G)          |                                                                                 | 1         |      |           |         |

| VIH                 | High-level input voltage  |                                                                                 | 0.7 x Vdd |      |           |         |

| VIL                 | Low-level input voltage   |                                                                                 |           |      | 0.3 x VDD | - V     |

| Ін                  | Input high-level current  | VIH = VDD_REF                                                                   |           |      | 67        |         |

| lı∟                 | Input low-level current   | VIL = GND                                                                       |           |      | 1         | μA      |

# **Timing Requirements**

$\mathsf{VDD} = 3.3 \; \mathsf{V} \pm 5 \; \%, \, -40^\circ\mathsf{C} \leq \mathsf{TA} \leq 125^\circ\mathsf{C}$

|              | Power Supply              | Min | Тур | Мах | Unit  |

|--------------|---------------------------|-----|-----|-----|-------|

| $V/t_{RAMP}$ | V <sub>DD</sub> ramp rate | 0.1 | -   | 50  | V/rms |

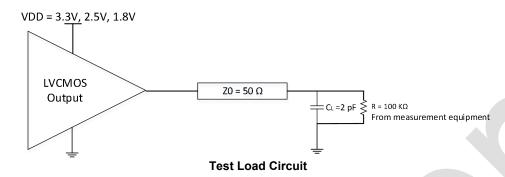

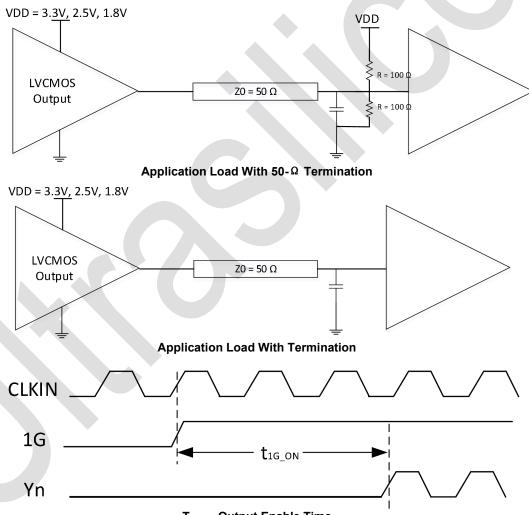

## **Parameter Measurement Information**

#### Note:

1.  $C_L$  include probe and jig capacitance.

2. All input pulses are supplied by generators having the following characteristics: Clock Frequency  $\leq$  250MHz, Z<sub>0</sub> = 50  $\Omega$ , tr < 1.2ns, tf < 1.2ns

T<sub>1G\_ON</sub> Output Enable Time

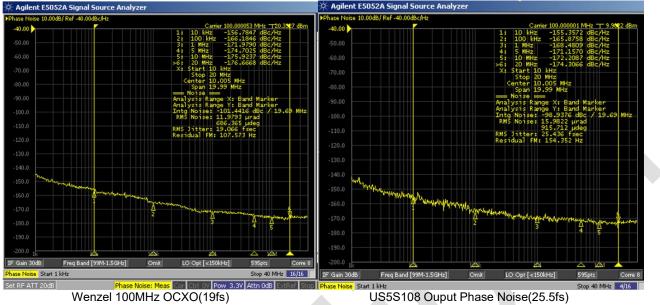

### **Phase Noise Plot**

极景微半导体

The additive phase jitter for this device was measured using the Wenzel 100MHz OCXO(19fs) as an input source with and Agilent E5052A phase noise analyzer. (VDD=3.3V)

## **Detailed Description**

### Overview

The US5S10x family of devices is part of a low-jitter and low-skew LVCMOS fan-out buffer solution. For best signal integrity, it is important to match the characteristic impedance of the US5S10x's output driver with that of the transmission line.

### US5S108 Functional Block Diagram

### **Feature Description**

The outputs of the US5S10x can be disabled by driving the synchronous output enable pin (1G) low. Unused output can be left floating to reduce overall system component cost. Supply and ground pins must be connected to VDD and GND, respectively.

### **Device Functional Modes**

The US5S10x operates from 1.8-V, 2.5-V, or 3.3-V supplies. Table 1 shows the output logics of the US5S10x.

| Table 1. Output Logic Table |                      |        |  |  |  |

|-----------------------------|----------------------|--------|--|--|--|

|                             | Outputs              |        |  |  |  |

| CLKIN                       | 1G                   | Yn     |  |  |  |

| Х                           | L                    | L      |  |  |  |

|                             | Н                    | L      |  |  |  |

| Н                           | Н                    | Н      |  |  |  |

|                             | CLKIN<br>X<br>L<br>H | Inputs |  |  |  |

### **Application and Implementation**

### **Application Information**

The US5S10x family is a low additive jitter LVCMOS buffer solution that can operate up to 250-MHz at  $V_{DD}$  = 3.3 V and 200 MHz at  $V_{DD}$  = 2.5 V to 1.8 V. Low output skew as well as the ability for synchronous output enable is featured to simultaneously enable or disable buffered clock outputs as necessary in the application.

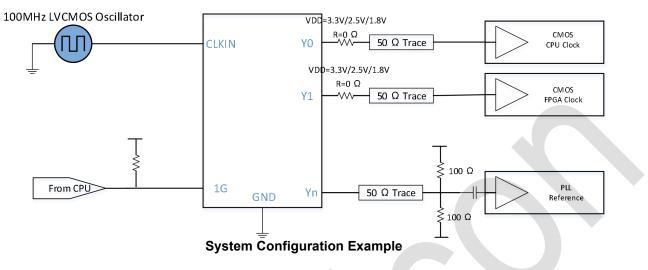

### **Typical Application**

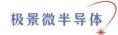

## PACKAGE DIMENSIONS

| SYMBOL |       | Millimeter |      |

|--------|-------|------------|------|

| SIMDUL | Min   | Nom        | Max  |

| А      | -     | -          | 1.20 |

| A1     | 0.05  | -          | 0.15 |

| A2     | 0.90  | 1.00       | 1.05 |

| A3     | 0. 39 | 0.44       | 0.49 |

| b      | 0.20  | _          | 0.28 |

| b1     | 0.19  | 0.22       | 0.25 |

| С      | 0.13  | _          | 0.17 |

| c1     | 0.12  | 0.13       | 0.14 |

| D      | 4.90  | 5.00       | 5.10 |

| E1     | 4.30  | 4.40       | 4.50 |

| Е      | 6.20  | 6.40       | 6.60 |

| е      |       | 0.65BSC    |      |

| L      | 0.45  | 0.60       | 0.75 |

| L1     |       | 1.00REF    |      |

| θ      | 0     | _          | 8°   |

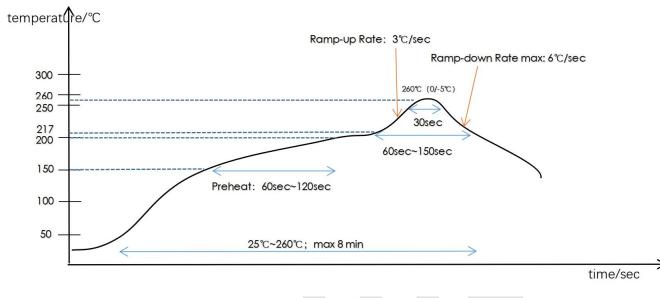

# **Reflow profile**

Recommended Temperature(PB-Free)

| Reflow Condition                            | Convection or<br>IR/Convection |

|---------------------------------------------|--------------------------------|

| Average ramp-up rate (217 °C to Peak)       | 3 °C/second max.               |

| Preheat temperature 175( $\pm 25$ ) °C      | 60-120 seconds                 |

| Temperature maintained above 217 °C         | 60-150 seconds                 |

| Time within 5 °C of actual peak temperature | 30 seconds                     |

| Peak temperature range                      | 260 +0/-5 °C                   |

| Ramp-down rate                              | 6 °C/second max.               |

| Time 25 °C to peak temperature              | 8 minutes max.                 |

| Maximum number of reflow cycles             | $\leq 3$                       |

# **Revision History**

| Date       | Description of Change             | Revision |

|------------|-----------------------------------|----------|

| 2022.05.05 | First Draft.                      | 1.0      |

| 2023.02.10 | Operating frequency range change。 | 1.5      |