### **Description**

The  $\mu$ PD71071 is a high-speed, high-performance direct memory access (DMA) controller that provides high-speed data transfers between peripheral devices and memory. A programmable bus width allows bidirectional data transfer in both 8- and 16-bit systems. In addition, the  $\mu$ PD71071 uses CMOS technology to reduce power consumption.

The  $\mu$ PD71071 can perform a variety of transfer functions including byte/word, memory-to-memory, and transfers between memory and I/O. The  $\mu$ PD71071 also utilizes single, demand, and block mode transfers; release and bus hold modes; and normal and compressed timing.

### **Features**

- ☐ Four independent DMA channels

- ☐ 16M-byte addressing

- ☐ 64K-byte/word transfer count

- ☐ 8- or 16-bit programmable data bus width

- ☐ Enable/disable of individual DMA requests

- ☐ Software DMA requests

- ☐ Enable/disable of autoinitialize

- □ Address increment/decrement

- ☐ Fixed/rotational DMA channel priority

- ☐ Terminal count output signal

- ☐ Forced transfer termination input

- ☐ Cascade capability

- ☐ Programmable DMA request and acknowledge signal polarities

- ☐ High performance: transfers to 5.33 Mbytes/s

- $\square$   $\mu$ PD70108/70116-compatible

- □ CMOS technology

- ☐ Low-power standby mode

- $\square$  Single power supply, 5 V  $\pm 10\%$

- ☐ Industrial temperature range, -40 to +85°C

- ☐ 10 MHz operation

### **Ordering Information**

| Part Number  | Package            | <del></del> |

|--------------|--------------------|-------------|

| μPD71071C-10 | 48-pin plastic DIP |             |

| L-10         | 52-pin PLCC        |             |

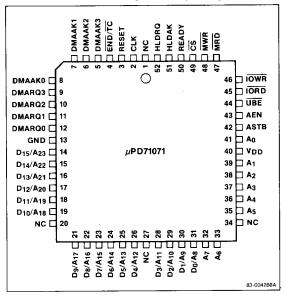

### **Pin Configurations**

### 48-Pin Plastic DIP

### Pin Configurations (cont)

### 52-Pin Plastic Leaded Chip Carrier (PLCC)

### **Pin Functions**

### **CLK** [Clock]

CLK controls the internal operation and data transfer speed of the  $\mu$ PD71071.

### RESET [Reset]

RESET initializes the controller's internal registers and leaves the controller in the idle cycle (CPU controls the bus). Active high.

### END/TC [End/Terminal Count]

This is a bidirectional pin. The END input is used to terminate the current DMA transfer. TC indicates the designated cycles of the DMA count transfer have finished. END/TC is open drain and requires an external pull-up resistor. Active low.

## DMAAK3-DMAAK0 [DMA Acknowledge]

DMAAK3-DMAAK0 indicates to peripheral devices that DMA service has been granted. DMAAK3-DMAAK0 respond respectively to DMA channels 3-0 and the polarities are user programmable.

### Pin Identification

| Symbol                                                               | Function                                     |  |  |  |  |  |

|----------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| A <sub>23</sub> -A <sub>8</sub> /<br>D <sub>15</sub> -D <sub>0</sub> | Bidirectional address/data bus               |  |  |  |  |  |

| IC                                                                   | Internally connected; leave open             |  |  |  |  |  |

| A <sub>7</sub> -A <sub>4</sub>                                       | Address bus output                           |  |  |  |  |  |

| NC                                                                   | Not connected                                |  |  |  |  |  |

| A <sub>3</sub> -A <sub>0</sub>                                       | Bidirectional address bus                    |  |  |  |  |  |

| $v_{DD}$                                                             | Power supply                                 |  |  |  |  |  |

| ASTB                                                                 | Address strobe output                        |  |  |  |  |  |

| AEN                                                                  | Address enable output                        |  |  |  |  |  |

| UBE                                                                  | Upper byte enable input/output               |  |  |  |  |  |

| IORD                                                                 | .1/0 read input/output                       |  |  |  |  |  |

| IOWR                                                                 | I/O write input/output                       |  |  |  |  |  |

| MRD                                                                  | Memory read output                           |  |  |  |  |  |

| MWR                                                                  | Memory write output                          |  |  |  |  |  |

| CS                                                                   | Chip select input                            |  |  |  |  |  |

| READY                                                                | Ready input                                  |  |  |  |  |  |

| HLDAK                                                                | Hold acknowledge input                       |  |  |  |  |  |

| HLDRQ                                                                | Hold request output                          |  |  |  |  |  |

| CLK                                                                  | Clock input                                  |  |  |  |  |  |

| RESET                                                                | Reset input                                  |  |  |  |  |  |

| END/TC                                                               | End DMA transfer input/terminal count output |  |  |  |  |  |

| DMAAK3-<br>DMAAK0                                                    | DMA acknowledge output                       |  |  |  |  |  |

| DMARQ3-<br>DMARQ0                                                    | DMA request input                            |  |  |  |  |  |

| GND                                                                  | Ground                                       |  |  |  |  |  |

### **DMARQ3-DMARQ0 [DMA Request]**

DMARQ3-DMARQ0 accept DMA service requests from peripheral devices. DMARQ3-DMARQ0 respond respectively to DMA channels 3-0 and the polarities are user programmable. DMARQ must remain asserted until DMAAK is asserted.

### GND [Ground]

GND connects to the power supply ground terminal.

## A<sub>23</sub>-A<sub>8</sub>/D<sub>15</sub>-D<sub>0</sub> [Address/Data Bus]

$A_{23}\text{-}A_8/D_{15}\text{-}D_0$  function as a 16-bit, multiplexed address/data bus when the  $\mu\text{PD}71071$  is in the 16-bit data mode. In the 8-bit data mode,  $A_{23}\text{-}A_{16}$  (pins 13-20) become address bits only and  $A_{15}\text{-}A_8/D_7\text{-}D_0$  (pins 21-28) remain an 8-bit multiplexed address/data bus.  $A_{23}\text{-}A_8/D_{15}\text{-}D_0$  are three-state.

### A<sub>7</sub>-A<sub>4</sub>, A<sub>3</sub>-A<sub>0</sub> [Address Bus]

$A_7\text{-}A_4, A_3\text{-}A_0$  function as the lower eight bits of the address bus.  $A_7\text{-}A_4$  output memory addresses during the DMA cycle and become high impedance in the idle cycle.  $A_3\text{-}A_0$  function as the lower four bits of the address bus. In the idle cycle,  $A_3\text{-}A_0$  become address inputs to select internal registers for the CPU to read or write. In the DMA cycle,  $A_3\text{-}A_0$  output memory addresses.

### V<sub>DD</sub> [Power Supply]

V<sub>DD</sub> connects to the +5-V power supply.

### ASTB [Address Strobe]

ASTB latches address  $A_{23}$ - $A_8$  (16-bit mode)/ $A_{15}$ - $A_8$  (8-bit mode) from the address/data bus into an external address latch at the falling edge of ASTB during a DMA cycle. Active high.

### AEN [Address Enable]

AEN enables the output of an external latch that holds DMA addresses. AEN becomes high during the DMA cycle.

### **UBE** [Upper Byte Enable]

$\overline{\text{UBE}}$  indicates the upper byte of the data bus is valid during 16-bit mode. In the idle cycle during data transfer, the  $\mu\text{PD}71071$  acknowledges data on D<sub>15</sub>-D<sub>8</sub> when  $\overline{\text{UBE}}$  is asserted. During a DMA cycle, UBE goes low to signify the presence of valid data on D<sub>15</sub>-D<sub>8</sub>.  $\overline{\text{UBE}}$  has no meaning in 8-bit mode and becomes high impedance in the idle cycle and high level in the DMA cycle. Three-state, active low.

### IORD [I/O Read]

In the idle cycle, IORD inputs a read signal from the CPU. In the DMA cycle, IORD outputs a read signal to an I/O device. Three-state, active low.

## IOWR [I/O Write]

In the idle cycle,  $\overline{IOWR}$  inputs a write signal from the CPU. In the DMA cycle,  $\overline{IOWR}$  outputs a write signal to an I/O device. Three-state, active low.

## MRD [Memory Read]

During the DMA cycle, MRD outputs a read signal to memory. MRD is high impedance during the idle cycle. Three-state, active low.

## MWR [Memory Write]

During the DMA cycle, MWR outputs a write signal to memory. MWR is high impedance during the idle cycle. Three-state, active low.

## CS [Chip Select]

During the idle cycle,  $\overline{CS}$  selects the  $\mu$ PD71071 as an I/O device. Active low.

### READY [Ready]

During a DMA operation, READY indicates that a data transfer for one cycle has been completed and may be terminated. To meet the requirements of low-speed I/O devices or memory, READY may be negated to insert wait states to extend the bus cycle until READY is again asserted.

### **HLDAK** [Hold Acknowledge]

When active, HLDAK indicates that the CPU has granted the  $\mu$ PD71071 the use of the system bus. Active high.

### **HLDRQ** [Hold Request]

HLDRQ outputs a bus hold request to the CPU. Active high.

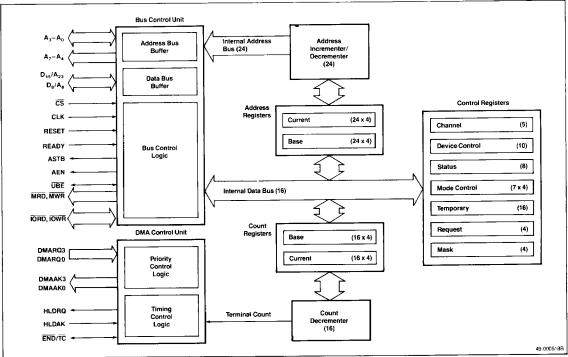

### **Block Diagram Description**

The  $\mu$ PD71071 has the following functional units.

- Bus control unit

- DMA control unit

- Address registers

- Address incrementer/decrementer

- Count registers

- Count decrementer

- Control registers

#### **Bus Control Unit**

The bus control unit consists of the address and data buffers, and bus control logic. The bus control unit generates and receives signals that control addresses and data on the internal address and data buses.

### **DMA Control Unit**

The DMA control unit contains the priority and timing control logic. The priority control logic determines the priority level of DMA requests and arbitrates the use of the bus in accordance with this priority level. The DMA control unit also provides internal timing and controls DMA operations.

### **Block Diagram**

### **Address Registers**

Each of the four DMA channels has one 24-bit base address register and one 24-bit current address register. The base address register holds a value determined by the CPU and transfers this value to the current address register during autoinitialization (address and count are automatically initialized). The channel's current address register is incremented/decremented for each transfer and always contains the address of the data to be transferred next.

### Address Incrementer/Decrementer

The address incrementer/decrementer updates the contents of the current address register whenever a DMA transfer completes.

### **Count Registers**

Each of the four DMA channels has one 16-bit base count register and one 16-bit current count register. The base count register holds a value written by the CPU and transfers the value to the current count register during autoinitialization. A channel's current count register is decremented for each transfer and

generates a terminal count when the count register is decremented to FFFFH.

**Note:** The number of DMA transfer cycles is actually the value of the current count register + 1. Therefore, when programming the count register, specify the number of DMA transfers minus one.

#### Count Decrementer

The count decrementer decrements the contents of the current count register by one when each DMA transfer cycle ends.

### **Control Registers**

The  $\mu$ PD71071 contains the following control registers.

- Channel

- Device

- Status

- Mode

- Temporary

- Request

- Mask

These registers control bus mode, pin active levels, DMA operation mode, mask bits, and other  $\mu$ PD71071 operating functions.

## **Absolute Maximum Ratings**

| Power supply voltage, V <sub>DD</sub>   | −0.5 to +7.0 V                           |

|-----------------------------------------|------------------------------------------|

| Input voltage, V <sub>I</sub>           | -0.5 to V <sub>DD</sub> + 0.3 V          |

| Output voltage, V <sub>0</sub>          | $-0.5 \text{ to V}_{DD} + 0.3 \text{ V}$ |

| Operating temperature, T <sub>OPT</sub> | -40 to +85°C                             |

| Storage temperature, T <sub>STG</sub>   | -65 to +150°C                            |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Capacitance

$T_{\text{A}} = 25\,^{\circ}\text{C}$

|                    |                 | Lir |     | Test |                                       |

|--------------------|-----------------|-----|-----|------|---------------------------------------|

| Parameter          | Symbol          | Тур | Max | Unit | Conditions                            |

| Output capacitance | Co              | 4   | 8   | pF   | f <sub>c</sub> =1.0 MHz<br>unmeasured |

| Input capacitance  | CI              | 8   | 15  | pF   | pins returned<br>to 0 V               |

| I/O capacitance    | C <sub>IO</sub> | 10  | 18  | pF   |                                       |

## **DC Characteristics**

$T_A = -40 \text{ to } +85 \,^{\circ}\text{C}, V_{DD} = 5 \text{ V} \pm 10\%$

|                           |                  | <u> </u>            |       |                       |      |                                           |

|---------------------------|------------------|---------------------|-------|-----------------------|------|-------------------------------------------|

|                           |                  | l                   | imits |                       |      | Test<br>Conditions                        |

| Parameter                 | Symbol           | Min                 | Тур   | Max                   | Unit |                                           |

| Input high<br>voltage     | V <sub>iH</sub>  | 3.3                 |       | V <sub>DD</sub> + 0.3 | V    | CLK input pin                             |

|                           |                  | 2.2                 |       | V <sub>DD</sub> + 0.3 | ٧    | Other inputs                              |

| input low<br>voltage      | V <sub>IL</sub>  | -0.5                |       | 0.8                   | ٧    |                                           |

| Output high voltage       | V <sub>OH</sub>  | 0.7 V <sub>DO</sub> |       |                       | ٧    | $I_{OH} = -400 \mu\text{A}$               |

| Output low voltage        | V <sub>OL</sub>  |                     |       | 0.4                   | ٧    | $I_{0L} = 2.5 \text{ mA};$<br>4.5 mA (TC) |

| Input leakage<br>current  | ILI              |                     |       | ±10                   | μΑ   | $0\ V \leq V_I \leq V_{DD}$               |

| Output leakage<br>current | ILO              |                     |       | ±10                   | μΑ   | $0 \ V \le V_0 \le V_{DD}$                |

| Supply current (dynamic)  | I <sub>DD1</sub> |                     | 15    | 30                    | mA   |                                           |

| Supply current (stable)   | I <sub>DD2</sub> |                     | 10    |                       | μΑ   | Inputs stable outputs open                |

| Supply current (static)   | I <sub>DD2</sub> |                     | 10    |                       | μΑ   |                                           |

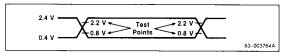

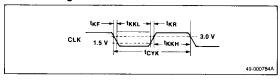

AC Characteristics  $T_A = -40 \text{ to } +85 \,^{\circ}\text{C}, V_{DD} = 5 \text{ V} \pm 10\%$

| Parameter                                        | Symbol             | Min                    | Max | Unit | Test Conditions     |

|--------------------------------------------------|--------------------|------------------------|-----|------|---------------------|

| DMA Mode                                         |                    |                        |     |      |                     |

| Clock cycle                                      | tcyk               | 100                    |     | ns   |                     |

| Clock pulse width high                           | †KKH               | 39                     |     | ns   |                     |

| Clock pulse width low                            | tkkl               | 49                     |     | ns   |                     |

| Clock rise time                                  | t <sub>KR</sub>    |                        | 10  | ns   | 1.5 V → 3.0 V       |

| Clock fall time                                  | t <sub>KF</sub>    |                        | 10  | ns   | 3.0 V → 1.5 V       |

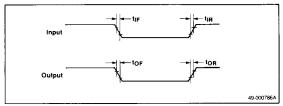

| Input rise time                                  | t <sub>IR</sub>    |                        | 20  | ns   |                     |

| Input fall time                                  | t <sub>IF</sub>    |                        | 12  | ns   |                     |

| Output rise time                                 | t <sub>OR</sub>    | ***                    | 20  | ns   |                     |

| Output fall time                                 | t <sub>OF</sub>    |                        | 12  | ns   |                     |

| DMARQ setup time to CLK high                     | tspa               | 20                     |     | ns   | S1, S0, S3, SW, S4w |

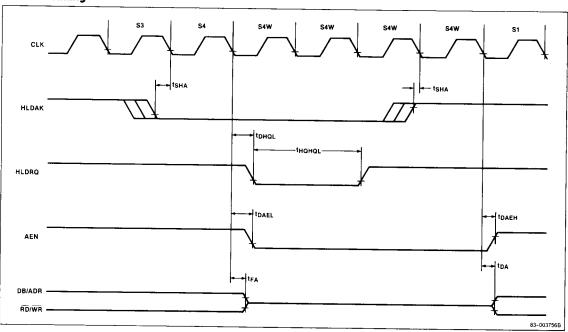

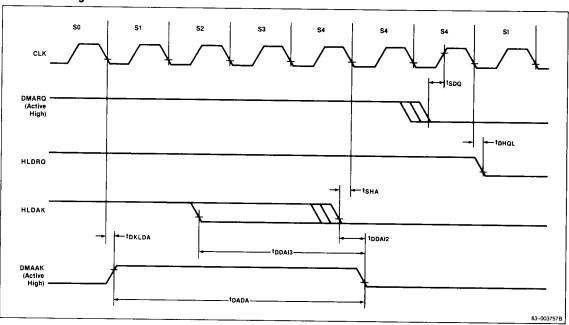

| HLDRQ high delay from CLK low                    | t <sub>DHQH</sub>  | 5                      | 70  | ns   | S1, S4w             |

| HLDRQ low delay from CLK low                     | tDHQL              | 5                      | 70  | ns   | S1, S0, S4w         |

| HLDRQ low level period                           | thahal             | 2t <sub>CYK</sub> - 50 |     | ns   | S4w                 |

| HLDAK high setup time to CLK low                 | t <sub>SHA</sub>   | 20                     |     | ns   | S0, S4, S4w         |

| AEN high delay from CLK low                      | tDAEH              | 5                      | 70  | ns   | S1, S2              |

| AEN low delay time from CLK low                  | tDAEL              | 5                      | 70  | ns   | S1, S4w             |

| ASTB high delay time from CLK low                | t <sub>DSTH</sub>  | 5                      | 70  | ns   | S1                  |

| ASTB low delay time from CLK high                | t <sub>DSTL</sub>  | 5                      | 70  | ns   | S1                  |

| ASTB high level period                           | t <sub>STSTH</sub> | t <sub>KKL</sub> — 15  |     | ns   |                     |

| ADR/UBE/RD/WR active delay from CLK low (Note 1) | t <sub>DA</sub>    | 5                      | 80  | ns   | S1, S2              |

| ADR/UBE/RD/WR float time<br>from CLK low         | t <sub>FA</sub>    | 0                      | 70  | ns   | S1, S4w             |

| ADR setup time to ASTB low                       | tsast              | t <sub>KKL</sub> — 40  |     | ns   |                     |

| ADR hold time to ASTB low                        | †HSTA              | t <sub>KKH</sub> — 20  |     | ns   |                     |

## **AC Characteristics (cont)**

| Parameter                                  | Symbol             | Min                                      | Max                    | Unit | Test Conditions                      |

|--------------------------------------------|--------------------|------------------------------------------|------------------------|------|--------------------------------------|

| DMA Mode (cont)                            |                    |                                          |                        |      |                                      |

| ADR/UBE off delay time from CLK low        | tDAF               | 0                                        | 70                     | ns   | S1, S2                               |

| RD low delay time from ADR float           | t <sub>DAR</sub>   | -10                                      |                        | ns   |                                      |

| Input data delay time from MRD low         | t <sub>DMRID</sub> |                                          | 2t <sub>CYK</sub> - 80 | ns   | S12                                  |

| Input data hold time from MRD high         | t <sub>HMRID</sub> | 0                                        |                        | ns   | S14                                  |

| Output data delay time from CLK low        | t <sub>DOD</sub>   | 10                                       | 80                     | ns   | S22                                  |

| Output data hold time from CLK high        | tHOD               | 10                                       |                        | ns   | S24                                  |

| Output data hold time from MWR high        | thmwod             | t <sub>KKL</sub> — 35                    |                        | ns   |                                      |

| RD low delay time from CLK high            | t <sub>DKHR</sub>  |                                          |                        | ns   | S2 compressed timing                 |

| RD low level period                        | t <sub>RRL1</sub>  | 2t <sub>CYK</sub> - 30                   |                        | ns   | Normal timing                        |

|                                            | tRRL2              | t <sub>CYK</sub> + t <sub>KKH</sub> - 30 |                        | ns   | Compressed timing                    |

| RD high delay time from CLK low            | t <sub>DRH</sub>   | 10                                       | 70                     | ns   | S4                                   |

| ADR delay time from RD high                | t <sub>DRA</sub>   | t <sub>CYK</sub> - 30                    |                        | ns   |                                      |

| WR low delay time from CLK low             | t <sub>DWL1</sub>  | 5                                        | 50                     | ns   | S3 normal write                      |

| WR low delay time from CLK low             | t <sub>DWL2</sub>  | 5                                        | 50                     | ns   | S2 extended write, normal timing     |

| WR low delay time from CLK high            | t <sub>DWL3</sub>  | 5                                        | 50                     | ns   | S2 extended write, compressed timing |

| WR low level period                        | t <sub>WWL1</sub>  | t <sub>CYK</sub> - 30                    |                        | ns   | Normal write                         |

|                                            | t <sub>WWL2</sub>  | 2t <sub>CYK</sub> - 30                   |                        | ns   | Extended write, normal timing        |

|                                            | twwL3              | t <sub>CYK</sub> + t <sub>KKH</sub> - 30 |                        | ns   | Extended write, compressed timing    |

| WR high delay from CLK low                 | t <sub>DWH</sub>   | 5                                        | 50                     | ns   | S4                                   |

| RD low delay time from CLK low             | toklr              | 5                                        | 50                     | ns   | S2 normal timing                     |

| RD, WR low delay from DMAAK active         | todarw             | 0                                        |                        | ns   | S1, S2                               |

| RD high delay time from WR high            | towhrh             | 5                                        | -                      | ns   |                                      |

| DMAAK delay time from CLK high             | <sup>t</sup> DKHDA | 5                                        | 70                     | ns   | S11/0 memory timing                  |

| DMAAK delay time from CLK low              | t <sub>DKLDA</sub> | 10                                       | 90                     | ns   | S1 cascade mode                      |

| DMAAK inactive delay time from<br>CLK high | t <sub>DDAI1</sub> | 5                                        |                        | ns   | \$4                                  |

## **AC Characteristics (cont)**

| Parameter                               | Symbol                                | Min                  | Max                      | Unit | Test Conditions                           |

|-----------------------------------------|---------------------------------------|----------------------|--------------------------|------|-------------------------------------------|

| DMA Mode (cont)                         | · · · · · · · · · · · · · · · · · · · |                      |                          |      |                                           |

| DMAAK inactive delay time from          | t <sub>DDAI2</sub>                    | 5                    | t <sub>KKL</sub> + 70    | ns   | S4 cascade mode, HLDAK low HLDAK low in S |

|                                         | †DDAI3                                | -                    | 4t <sub>KKL</sub> + 70   | ns   | S4 cascade mode, HLDAK low except in S4   |

| DMAAK active level period               | tDADA                                 |                      |                          | ns   | Cascade mode                              |

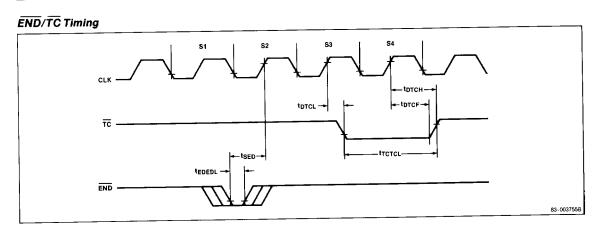

| TC low delay time from CLK high         | †DTCL                                 | 5                    | 70                       | ns   | S3                                        |

| TC off delay time from CLK high         | †DTCF                                 |                      | 30                       | ns   | S4                                        |

| TC high delay time from CLK high        | † <sub>DTCH</sub>                     |                      | $t_{KKH} + t_{CYK} - 10$ | ns   | 0 to 2.2 V (Note 2)                       |

| TC low level period                     | tTCTCL                                | t <sub>CYK</sub> -15 |                          | ns   |                                           |

| END low setup time to CLK high          | t <sub>SED</sub>                      | 20                   |                          | ns   | S2                                        |

| END low level period                    | tededl                                | 50                   |                          | ns   |                                           |

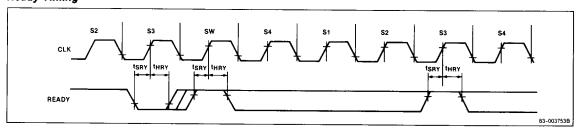

| READY setup time to CLK high            | tsry                                  | 20                   |                          | ns   | \$3, \$W                                  |

| READY hold time from CLK high           | t <sub>HRY</sub>                      | 10                   |                          | ns   | S3, SW                                    |

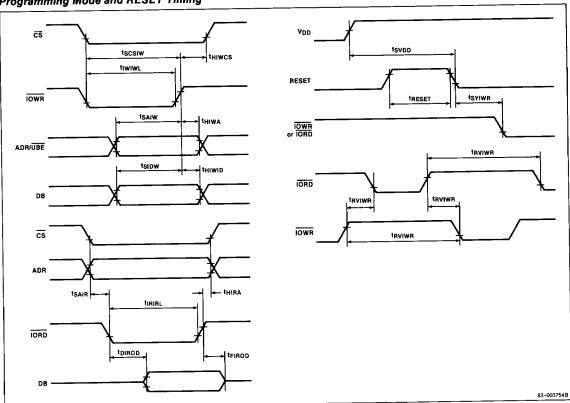

| <b>Programming Mode and RESE</b>        | T                                     |                      |                          |      |                                           |

| IOWR low level period                   | t <sub>IWIWL</sub>                    | 80                   |                          | ns   |                                           |

| CS low setup time to IOWR high          | tscsiw                                | 80                   |                          | ns   |                                           |

| CS hold time from IOWR high             | thiwcs                                | 0                    |                          | ns   |                                           |

| ADR/UBE setup time to IOWR high         | tsalw                                 | 80                   |                          | ns   |                                           |

| ADR/UBE hold time from IOWR high        | t <sub>HIWA</sub>                     | 0                    |                          | ns   |                                           |

| Input data setup time to IOWR high      | tsidiw                                | 80                   |                          | ns   |                                           |

| Input data hold time from IOWR high     | tHIWID                                | 0                    |                          | ns   |                                           |

| IORD low level period                   | t <sub>IRIRL</sub>                    | 120                  |                          | ns   |                                           |

| ADR/CS setup time to IORD low           | tsair                                 | 20                   |                          | ns   |                                           |

| ADR/CS hold time from IORD high         | t <sub>HIRA</sub>                     | 0                    |                          | ns   |                                           |

| Output data delay time from IORD low    | tDIROD                                | 10                   | 100                      | ns   |                                           |

| Output data float time from IORD high   | t <sub>FIROD</sub>                    |                      | 80                       | ns   |                                           |

| RESET high level period                 | TRESET                                | 2t <sub>CYK</sub>    |                          | ns   |                                           |

| V <sub>DD</sub> setup time to RESET low | tsvdd                                 | 500                  |                          | ns   |                                           |

| IOWR/IORD wait time from RESET low      | tsylwr                                | 2t <sub>CYK</sub>    |                          | ns   | RESET low to first read/write             |

| IOWR/IORD recovery time                 | trviwr                                | 160                  |                          | ns   |                                           |

### Notes:

- (1) RD/WR refers to IORD or MRD and IOWR or MWR, respectively.

- (2) For END/TC, output load capacitance = 75 pF maximum. To meet the t<sub>DTCH</sub> parameter use a 2.2-kΩ pull-up resistor with a load capacitance of 75 pF. For other than END/TC, output load capacitance = 100 pF maximum.

## **Timing Waveforms**

## **Timing Measurement Points**

## **Clock Timing**

## Input/Output Edge Timing

# Memory-to-Memory Transfer Timing

### **Ready Timing**

**Programming Mode and RESET Timing**

### **Bus Wait Timing**

## Cascade Timing

## **Functional Description**

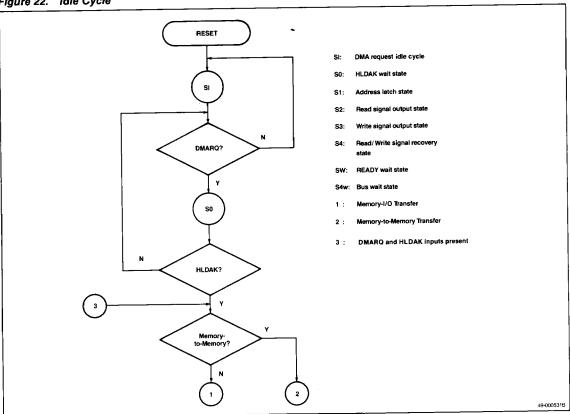

### **DMA Operation**

The  $\mu$ PD71071 functions in three cycles: idle, DMA, and standby. In an idle or standby cycle, the CPU uses the bus, while in a DMA cycle, the  $\mu$ PD71071 uses it.

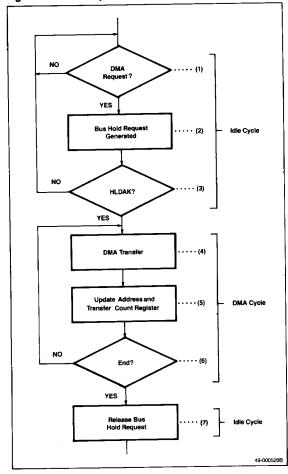

Idle Cycle. In an idle cycle, there are no DMA cycles active, but there may be one or more active DMA requests; however, the CPU has not released the bus. The  $\mu$ PD71071 will sample the four DMARQ input pins at every clock. If one or more inputs are active, the corresponding DMA request bits (RQ) are set in the status register and the  $\mu$ PD71071 sends a bus hold request to the CPU. The  $\mu$ PD71071 continues to sample DMA requests until it obtains the bus.

After the CPU returns a HLDAK signal and the  $\mu$ PD71071 obtains the bus, the  $\mu$ PD71071 stops DMA sampling and selects the DMA channel with the highest priority from the valid DMA request signals. Programming of the  $\mu$ PD71071 is done when the  $\mu$ PD71071 is in the idle cycle or the standby mode.

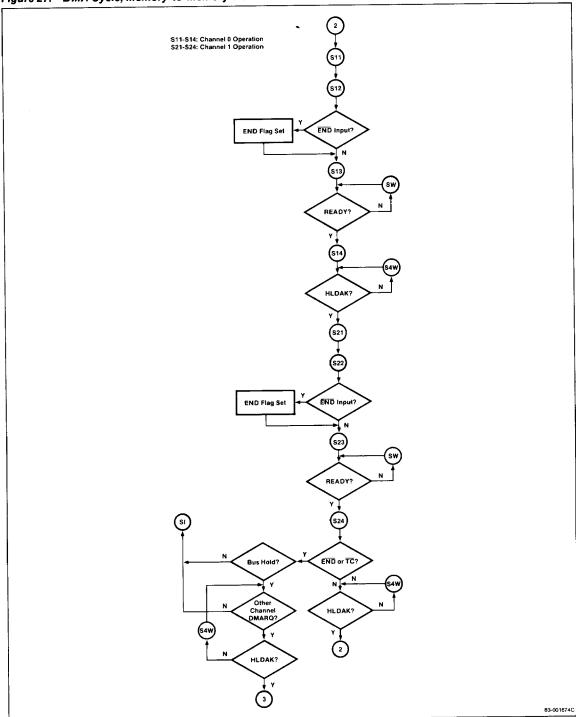

**DMA Cycle.** In a DMA cycle, the  $\mu$ PD71071 controls the bus and performs DMA transfer operations based on programmed information. Figure 1 outlines the sequentialflow of a DMA operation.

Standby Mode. The  $\mu$ PD71071 can also be used in standby mode. It is in standby mode and consumes the static supply current ( $I_{DD2}$ ) when the clock is turned off and no I/O read or write operations are being performed. All internal registers will retain their contents.

The  $\mu$ PD71071 can be programmed (using IOWR) and read (using IORD) with the clock off. The  $\mu$ PD71071 only uses the clock for the DMA data transfer cycles. The clock may be turned off without altering the internal registers when the  $\mu$ PD71071 is in the idle cycle. If the clock is turned off during a DMA transfer, the  $\mu$ PD71071 will not operate correctly. When the clock is off, the DMARQ inputs will not be recognized. The DMARQ inputs could be externally logically ORed and cause an interrupt to the CPU. The CPU could then turn on the clock, thus activating the  $\mu$ PD71071. If the previously programmed mode of operation is still valid, the  $\mu$ PD71071 does not have to be reprogrammed.

## **Data Bus Width**

In order to allow an easy interface with an 8- or 16-bit CPU, the data bus width of the  $\mu$ PD71071 is user programmable for 8 or 16 bits. A 16-bit data bus allows 16-bit memory-to-memory DMA transfers and also provides a one-I/O bus cycle access to the 16-bit internal registers.

Table 1 shows the relationship of the data bus width,  $A_0$ ,  $\overline{UBE}$ , and the internal registers.

Table 1. Data Bus Width

| Bus Width | Ao | UBE | Internal Read/Write Registers                              |

|-----------|----|-----|------------------------------------------------------------|

| 8 bits    | Х  | X   | D <sub>7</sub> -D <sub>0</sub> ←→→ 8-bit internal register |

| 16 bits   | 0  | 1   | D <sub>7</sub> -D <sub>0</sub> ← 8-bit internal register   |

|           | 1  | 0   | D <sub>15</sub> -D <sub>8</sub> ←→ 8-bit internal register |

|           | 0  | 0   | D <sub>15</sub> -D <sub>0</sub> ← 16-bit internal register |

Figure 1. DMA Operation Flow

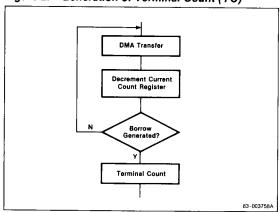

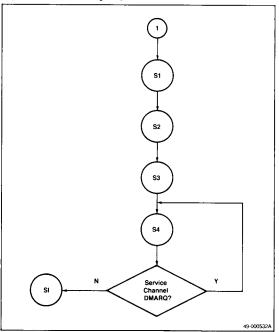

### **Terminal Count**

The  $\mu$ PD71071 ends DMA service when it generates a terminal count ( $\overline{TC}$ ) or when the  $\overline{END}$  input becomes active. A terminal count is produced when a borrow is generated by the current count register and a low-level pulse is output to the  $\overline{TC}$  pin. Figure 2 shows that the current count register is tested after each DMA operation.

If autoinitialize is not set when DMA service ends, the mask register bit applicable to the channel where service ended is set, and the DMARQ input of that channel is masked.

### **DMA Transfer Type**

The type of transfer the  $\mu$ PD71071 performs depends on the following conditions.

- Memory-to-memory transfer enable

- Direction of memory-to-I/O transfer (each channel)

- Transfer mode (each channel)

- Bus mode

Memory-to-Memory Transfer Enable. The  $\mu$ PD71071 can perform memory-to-I/O transfers (one transfer cycle in one bus cycle) and memory-to-memory transfers (one transfer in two bus cycles). To select memory-to-memory transfer, set bit 0 of the device control register to 1. The DMA channels used in memory-to-memory transfers are fixed, with channel 0 as the source channel and channel 1 as the destination channel. Channels 2 and 3 cannot be used in memory-to-memory transfers. The contents of the count registers and word/byte transfer modes of channels 0 and 1 should be the same when performing memory-to-memory transfer.

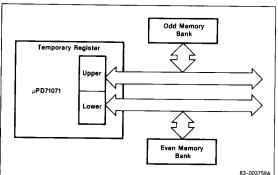

Figure 2. Generation of Terminal Count (TC)

For memory-to-memory byte transfer in 16-bit data bus mode, a read data from upper data bus is to be written to upper data bus, while a read data from lower data bus is to be written to lower data bus. Therefore, start addresses for source and destination must be the even-even or odd-odd. For word transfer, only even-even addresses are to be set for source and destination. (See Byte/Word Transfer paragraphs below.) When DMARQ0 (channel 0) becomes active, the transfer is initiated.

During memory-to-memory bus cycles in the 16-bit mode, data read from the DMAC's upper (lower) data bus is written to the upper (lower) data bus of the destination device. Thus, for word transfers, only even source and destination addresses should be used.

The DMA request input pin or a software DMA request to channel 0 may initiate memory-to-memory transfers. The µPD71071 performs the following operations until a channel 1 terminal count or END input is present:

- During the first bus cycle, the memory data pointed to by the current address register of channel 0 is read into the temporary register of the μPD71071 and the address and count of channel 0 are updated.

- During the second bus cycle, the temporary register data is written to the memory location shown by the current address register of channel 1, and the address and count of channel 1 are updated.

Note: If DMARQ1 (channel 1) becomes active, the µPD71071 will perform memory-to-I/O transfer even though memory-to-memory transfer is selected. Since this may cause erroneous memory-to-memory transfers, mask out channel 1 (DMARQ1) by setting bit 1 of the mask register to 1 before starting memory-to-memory transfers.

During memory-to-memory transfers, the addresses on the source side (channel 0) can be fixed by setting bit 1 of the device control register to 1. In this manner, a

Figure 3. Memory-to-Memory Transfer in 16-Bit Data Bus Mode

range of memory can be initialized with the same value since the contents of the source address never change. During memory-to-memory transfer, the DMAAK signal and channel 0's terminal count (TC) pulse are not output. (See figure 3.)

Direction of Memory-to-I/O Transfers. All DMA transfers use memory as a reference point. Therefore, a DMA read reads a memory location and writes to an I/O port. A DMA write reads an I/O port and writes the data to a memory location. In memory-to-I/O transfer, use the mode control register to set one of the transfer directions in table 2 for each channel and activate the appropriate control signals.

Table 2. Transfer Direction

| Transfer Direction                                                  | Activated Signals |

|---------------------------------------------------------------------|-------------------|

| Memory → I/O (DMA read)                                             | IOWR, MRD         |

| I/O → memory (DMA write)                                            | IORD, MWR         |

| Verify<br>(Outputs addresses only. Does not<br>perform a transfer.) | <u> </u>          |

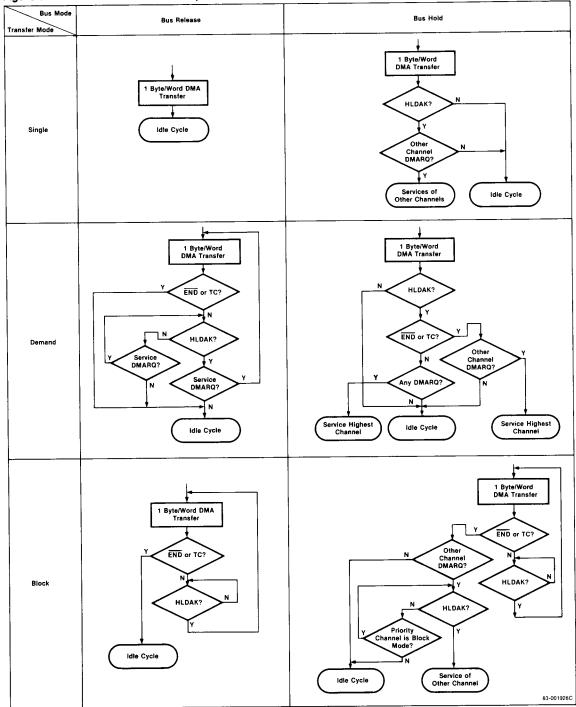

Transfer Modes. In memory-to-I/O transfer, the mode control register selects the single, demand, or block mode of DMA transfer for each channel. The conditions for the termination of each transfer characterize each transfer mode. Memory-to-memory transfers have no relationship to single, demand, or block mode. Memory-to-memory transfers are a separate and distinct type of transfer mode. Table 3 shows the various transfer modes and termination conditions.

Table 3. Transfer Termination

| Transfer Mode        | End of Transfer Conditions                                                                                                                                                         |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Single               | After each byte/word                                                                                                                                                               |  |  |  |  |  |

| Demand               | END input Generation of terminal count When DMA request of the channel in service becomes inactive When DMA request of a channel in higher priority becomes active (bus hold mode) |  |  |  |  |  |

| Block                | END input<br>Generation of terminal count                                                                                                                                          |  |  |  |  |  |

| Memory-to-<br>memory | END input<br>Generation of terminal count                                                                                                                                          |  |  |  |  |  |

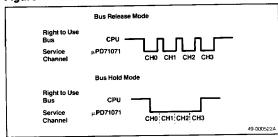

**Bus Modes.** The device control register selects either the bus release or bus hold mode. The bus mode determines when the  $\mu$ PD71071 returns the system bus to the CPU. The  $\mu$ PD71071 can be in either the release or hold modes for the single, demand, or block mode transfers. Therefore, there are six possible mode combinations.

Figure 4 shows that in bus release mode, only one channel can receive service after obtaining the bus. When DMA service ends (end of transfer conditions depend on the transfer mode), the channel returns the bus to the CPU (regardless of the state of other DMA requests) and the  $\mu$ PD71071 enters the idle cycle. When the  $\mu$ PD71071 regains use of the bus, a new DMA operation begins.

Figure 4. Bus Modes

In bus hold mode, several channels can receive service without releasing the bus after obtaining it. If there is another valid DMA request when a channel's DMA service is finished, the new DMA service can begin after the previous service without returning the bus to the CPU. End of transfer conditions depend on the transfer mode. A channel cannot terminate (end count) a transfer mode and immediately start on its next set of transfers. There must be another DMA channel service interleaved or the  $\mu$ PD71071 will put in an idle cycle. The following shows an example of the possible sequences for Channel 2.

CHAN2

$$\rightarrow$$

CHANn (n = 0,1,3)  $\rightarrow$  CHAN2 or, CHAN2  $\rightarrow$  idle  $\rightarrow$  CHAN2

The operation of single, demand, and block mode transfers depends on whether the  $\mu$ PD71071 is in bus release or bus hold mode. In bus release mode, only one type of bus mode (single, demand, or block) is used each time the  $\mu$ PD71071 has the bus. In bus hold mode, multiple types of transfers are possible. Channel 0 might operate in the demand mode, and channel 1, which could get the bus immediately after channel 0, could operate in block mode.

## Single Mode Transfer

In bus release mode, when a channel completes the transfer of a single byte or word, the  $\mu$ PD71071 enters the idle cycle regardless of the state of the DMA request inputs. In this manner, other devices will be able to access the bus on alternate bus cycles.

In bus hold mode, when a channel completes the transfer of a single byte or word, the  $\mu$ PD71071 terminates the channel's service even if it is still asserting a DMA request signal. The  $\mu$ PD71071 will then service the highest priority channel requesting the bus. If there are no requests from any other channel, the  $\mu$ PD71071 releases the bus and enters the idle cycle.

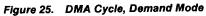

### **Demand Mode Transfer**

In bus release mode, the currently active channel continues its data transfer as long as the DMA request of that channel is active, even though other DMA channels are issuing higher priority requests. When the DMA request of the serviced channel becomes inactive, the µPD71071 releases the bus and enters the idle state, even if the DMA request lines of other channels are active.

In bus hold mode, when the active channel completes a single transfer, the  $\mu$ PD71071 checks DMA request lines (other request lines when END or TC, all request lines including the last serviced channel when there is no END or TC). If there are active requests, the  $\mu$ PD71071 starts servicing the highest priority channel requesting service. If there is no request, the  $\mu$ PD71071 releases the bus and enters the idle state.

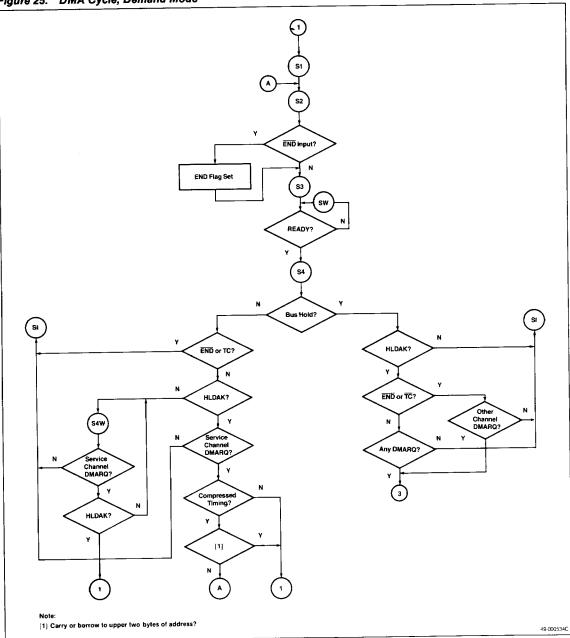

### **Block Mode Transfer**

In bus release mode, the current channel continues data transfer until a terminal count or the external  $\overline{\text{END}}$  signal becomes active. During this time, the  $\mu\text{PD71071}$  ignores all other DMA requests. After completion of the block transfer, the  $\mu\text{PD71071}$  releases the bus and enters the idle cycle even if DMA requests from other channels are active.

In bus hold mode, the current channel transfers data until a terminal count or the external  $\overline{\text{END}}$  signal becomes active. When the service is complete, the  $\mu\text{PD71071}$  checks all DMA requests without releasing the bus. If there is an active request, the  $\mu\text{PD71071}$  immediately begins servicing the request. The  $\mu\text{PD71071}$  releases the bus after it honors all DMA requests or a higher priority bus master requests the bus.

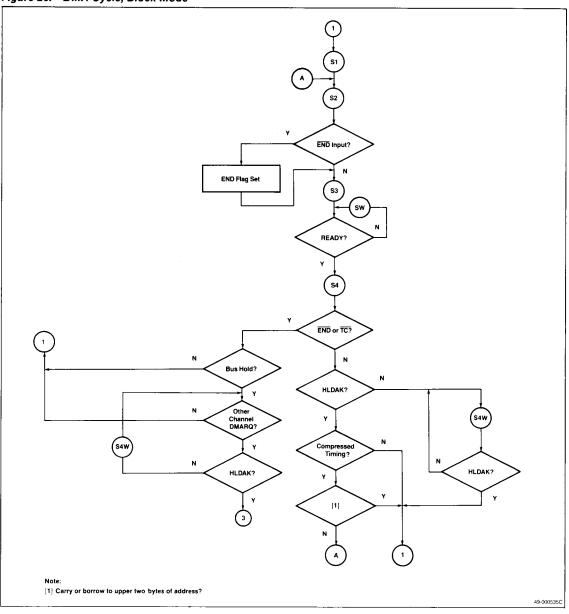

Figure 5 shows the operation flow for the six possible transfer and bus mode operations in DMA transfer.

### Byte/Word Transfer

If the initialize command selects a 16-bit data bus width, the mode control register can specify DMA transfer in byte or word units for each channel. Table 4 shows the update of the address and count registers during byte/word transfer.

Table 4. Address and Count Registers

| Register | Byte Transfer | Word Transfer |  |

|----------|---------------|---------------|--|

| Address  | ± 1           | ± 2           |  |

| Count    | -1            | -1            |  |

During word transfers, two bytes starting at an even address are handled as one word. If word transfer is selected and the initial value of the set address is odd, the  $\mu$ PD71071 will always decrement that address by 1, thus making the address even for the data transfer. For this reason, it is best to select even addresses when transferring words, to avoid destroying data. A<sub>0</sub> and  $\overline{\text{UBE}}$  control byte and word transfers.

Table 5 shows the relationship between the data bus width,  $A_0$  and  $\overline{UBE}$  signals, and data bus status.

Table 5. Data Bus Status

| Data Bus Width | A <sub>0</sub> | UBE   | Data Bus Status                            |

|----------------|----------------|-------|--------------------------------------------|

| 8 bits         | Х              | 1 (1) | D <sub>7</sub> -D <sub>0</sub> valid byte  |

| 16 bits        | 0              | 1     | D <sub>7</sub> -D <sub>0</sub> valid byte  |

|                | 1              | 0     | D <sub>15</sub> -D <sub>8</sub> valid byte |

|                | 0              | 0     | D <sub>15</sub> -D <sub>0</sub> valid word |

#### Note:

(1) Always 1 for an 8-bit bus.

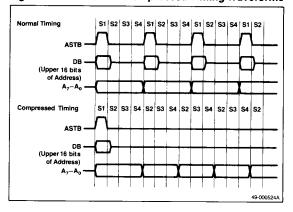

## Compressed Timing

In transfers between I/O and memory, a DMA transfer cycle is normally executed in four clocks. However, when the device control register selects compressed timing, one DMA cycle can be executed in a three-clock bus cycle. Compressed timing may be used in the release or hold modes when doing block transfers between I/O and memory. In the demand mode, only use compressed timing in the bus release mode. Compressed timing mode increases data transfer rates by 33%.

The  $\mu$ PD71071 is able to omit one clock period during compressed timing by not updating the upper 16 bits of the latched address. In block mode and demand bus release mode, addresses are output sequentially and the upper 16 bits of addresses latched in external latches need not be updated except after a carry or borrow from A<sub>7</sub> to A<sub>8</sub>. For this reason, during compressed timing, the S1 state (output of upper 16 bits of an address for external latching) is omitted in the bus cycles except during the first bus cycle when the upper 16 bits of an address are changed. Figure 6 shows one word waveforms for normal and compressed timing.

Figure 5. Transfer and Bus Modes Operations

Figure 6. Normal and Compressed Timing Waveforms

### **Software DMA Requests**

The  $\mu$ PD71071 can accept software DMA requests in addition to DMA requests from the four DMARQ pins. Setting the appropriate bit in the request register generates a software DMA request. The mask register does not mask software DMA requests. Software DMA requests operate differently depending on which bus or transfer mode is used.

**Bus Mode.** When bus release mode is set, the highest priority channel among software DMA requests and DMARQ pins is serviced, and all bits of the request register are cleared when the service is over. Therefore, there is a chance that other software DMA requests will be cancelled.

When bus hold mode is set, only the corresponding bit of the request register is cleared after a DMA service is over. Therefore, all software DMA requests will be serviced in the sequence of their priority level.

Software DMA requests for cascade channels (see Cascade Connection) must be performed in bus hold mode. When a cascade channel is serviced, the master  $\mu$ PD71071 operational mode is changed to bus release mode temporarily and all bits of the request register are cleared when the cascade channel service is over. To avoid this, it is necessary to mask any cascade channels before issuing a software DMA request. After confirming that all DMA software services are complete and all bits of the request register are cleared, the cascade channel masks can be cleared.

**Transfer Mode.** When single or demand mode is set, the applicable request bits are cleared and software DMA service ends with the transfer of one byte/word. When block mode or memory-to-memory modes are set, service continues until END is input or a terminal count is generated. Applicable request bits are cleared when service ends.

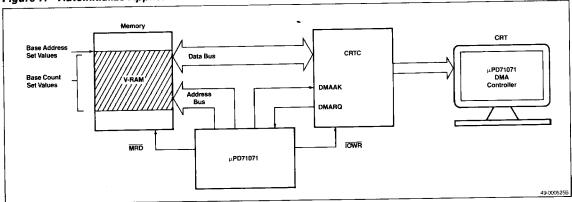

### **Autoinitialize**

When the mode control register is set to autoinitialize a channel, the  $\mu PD71071$  automatically initializes the address and count registers when  $\overline{END}$  is input or a terminal count is generated. The contents of the base address and base count registers are transferred to the current address and current count registers, respectively. The applicable bit of the mask register is unaffected. The applicable bit of the mask register is set for channels not programmed for autoinitialize.

The autoinitialize function is useful for the following types of transfers.

Repetitive Input/Output of Memory Area. Figure 7 shows an example of DMA transfer between a CRT controller and memory. After setting the value in the base and current registers, autoinitialize allows repetitive DMA transfer between the CRT controller and the video memory area without CPU involvement.

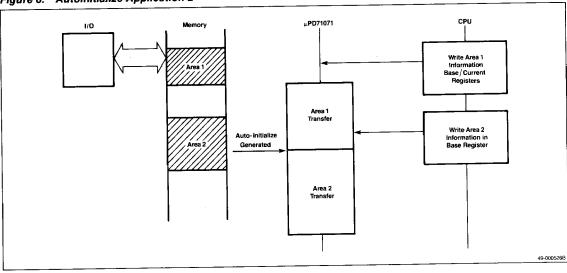

Continuous Transfer of Several Memory Areas. The CPU can indirectly write to the address or count registers by writing to the base registers. New values can be written to the base registers. In the autoinitialize mode, the value in the base register will be transferred to the address/count registers when termination is reached in the address/count registers. Because of this, the autoinitialize function can perform continuous transfer of several contiguous or noncontiguous memory areas during single or demand bus release modes in the following manner.

During the transfer of data in area 1 (the first area being transferred), the CPU can write address and count information about area 2 (the second area to be transferred). Generation of a terminal count for area 1 results in the transfer of information of area 2 to the address and count registers. This will cause area 2 to be transferred. Figure 8 illustrates this procedure.

### **Channel Priority**

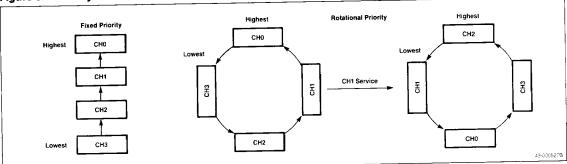

Each of the  $\mu$ PD71071's four channels has its own priority. When there are DMA requests from several channels simultaneously, the channel with the highest priority will be serviced. The device control register selects one of two channel priority methods: fixed and rotational priority. In fixed priority, the priority (starting with the highest) is channel 0, 1, 2, and 3, respectively. In rotational priority, priority order is rotated so that the channel that has just been given service receives the lowest priority and the next highest channel number is given the highest priority. This method prevents exclusive servicing of some channel(s). Figure 9 shows the two priority order methods.

Figure 7. Autoinitialize Application 1

Figure 8. Autoinitialize Application 2

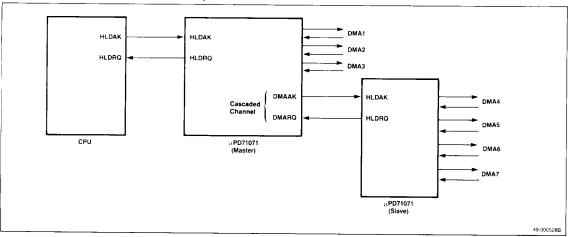

### **Cascade Connection**

The µPD71071 can be cascaded to expand the system DMA channel capacity. To connect a µPD71071 for cascading (figure 10), perform the following operations.

- (1) Connect pins HLDRQ and HLDAK of the secondstage (slave) μPD71071 to pins DMARQ and DMAAK of any channel of the first-stage (master) μPD71071.

- (2) To select the cascade mode of a particular channel of a master μPD71071, set bits 7 and 6 of that channel's mode control register to 11.

When a channel is set to the cascade mode in a master  $\mu$ PD71071, DMARQ, DMAAK, HLDRQ, HLDAK, and RESET are the only valid signals in the master  $\mu$ PD71071. The other signals are disabled. The master cascade channel only intermediates hold request/hold acknowledge between the slave and CPU.

The master  $\mu$ PD71071 always operates in the bus release mode when a cascade channel is in service (even when the bus hold mode is set). Other DMA requests are ignored while a cascade channel is in service. When the slave  $\mu$ PD71071 ends DMA service and moves into an idle cycle, the master also moves to an idle cycle and releases the bus. At this time, all bits of the master's request register are cleared. The master operates its non-cascaded channels normally.

### **Bus Wait Operation**

In systems using a  $\mu$ PD70208/70216 (V40/V50) as the CPU, the refresh control unit in the CPU changes the HLDAK signal to inactive (even during a DMA cycle) and uses the bus. Here, the  $\mu$ PD71071 automatically performs a bus wait operation. This system has a bus master (V40/V50) whose priority level is higher than that of the  $\mu$ PD71071.

The µPD71071 executes the bus wait operation when the HLDAK signal becomes inactive in an operating mode where transfer is executed continuously in block mode, during demand bus release mode, or during memory-to-memory transfer.

When HLDAK becomes inactive during service in other operating modes, the operation returns to the idle cycle and transfers control of the bus to the higher bus master.

Figure 11 shows that when the HLDAK signal becomes inactive during a continuous transfer, the  $\mu$ PD71071 is set up in an S4w state (bus wait). Operation moves to the idle cycle if DMARQ is inactive in the demand mode. The HLDRQ signal is made inactive for a period of about two clocks and the bus is released. The S4w state is repeated until the HLDAK signal again becomes active and the interrupted service is immediately restarted.

Figure 10. Cascade Connection Example

Figure 11. Bus Wait Operation

## Programming the µPD71071

To prepare a channel for DMA transfer, you must select the following characteristics.

- Starting address for the transfer

- Number of byte/word transfers

- DMA operating modes

- Data bus widths

- Active levels of the DMARQ and DMAAK signals

When reading from or writing to a  $\mu$ PD71071 internal register, address lines  $A_3$ - $A_0$  select the register,  $\overline{IORD}$  or  $\overline{IOWR}$  select the data transfer direction, and  $\overline{CS}$  enables the transfer. Table 6 shows the register and command configurations.

Table 6. Register Configuration

| Table 6. Register Comiguration |          |  |  |  |  |  |

|--------------------------------|----------|--|--|--|--|--|

| Register                       | Bit size |  |  |  |  |  |

| Channel                        | 5        |  |  |  |  |  |

| Base address                   | 24 (4)   |  |  |  |  |  |

| Current address                | 24 (4)   |  |  |  |  |  |

| Base count                     | 16 (4)   |  |  |  |  |  |

| Current count                  | 16 (4)   |  |  |  |  |  |

| Mode control                   | 7 (4)    |  |  |  |  |  |

| Device control                 | 10       |  |  |  |  |  |

| Status                         | 8        |  |  |  |  |  |

| Request                        | 4        |  |  |  |  |  |

| Mask                           | 4        |  |  |  |  |  |

| Temporary                      | 16       |  |  |  |  |  |

|                                |          |  |  |  |  |  |

### Note:

When using a 16-bit CPU and selecting a 16-bit data bus, the word IN/OUT instruction can be used to read/write information two bytes at a time. However, commands in table 7 suffixed with B must be issued with the byte IN/OUT instruction.

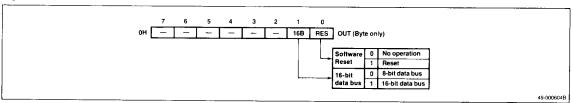

### Initialize

Use the initialize command as a software initialize to the  $\mu$ PD71071 or to set the width of the data bus. When using a 16-bit CPU, set the data bus width to 16 bits first. Figure 12 shows the initialize command format.

Bit 0. When the RES bit is set, the internal state of the  $\mu$ PD71071 is initialized and will be the same as when a hardware reset is used (except for data bus width selection). A software reset leaves bit 16B intact whereas a hardware reset selects the 8-bit data bus. After initialization, the registers are as in table 8 and the RES bit is cleared automatically.

Table 8. Register Initialization

| Register       | Initialization Operation            |  |  |  |

|----------------|-------------------------------------|--|--|--|

| Initialize     | Clears bit 0 only                   |  |  |  |

| Address        | No change                           |  |  |  |

| Count          | No change                           |  |  |  |

| Channel        | Selects channel 0, current and base |  |  |  |

| Mode control   | Clears all bits                     |  |  |  |

| Device control | Clears all bits                     |  |  |  |

| Status         | Clears bits 3-0 only                |  |  |  |

| Request        | Clears all bits                     |  |  |  |

| Mask           | Sets all bits (masks all channels)  |  |  |  |

| Temporary      | Clears all bits                     |  |  |  |

Bit 1. The 16B bit determines the data bus width. When using the  $\mu$ PD71071 in a 16-bit system, set this bit immediately after a hardware reset since a hardware reset always initializes it to the 8-bit data bus mode.

49-000603B

Table 7. Command Configuration

| Address  | R/W           | Command Name                      | MSB     | _           | Forn       | nat       |      |            | LSB        |  |

|----------|---------------|-----------------------------------|---------|-------------|------------|-----------|------|------------|------------|--|

| он       | W(B)          | Initialize                        |         | <del></del> |            |           |      | 16B        | RES        |  |

|          | R(B)          | Channel Register                  |         | 1           | BASE       | SEL3      | SEL2 |            |            |  |

| 1H       | N(D)          | Read                              |         | L           | BASE       | SEL3      | SEL2 | SEL1       | SEL0       |  |

|          | W(B)          | Channel Register<br>Write         |         |             | -          |           | BASE | SE         | ĽСН        |  |

| 2H       | R/W           | Count Register<br>Read/Write      | C7 C6   | C5          | C4         | СЗ        | C2   | C1         | C0         |  |

| 3H       | R/W           |                                   | C15 C14 | C13         | C12        | C11       | C10  | C9         | C8         |  |

| 4H       | R/W           | Address Business                  | A7 A6   | A5          | A4         | A3        | A2   | A1         | <b>A</b> 0 |  |

| 5H<br>6H | R/W<br>R/W(B) | Address Register<br>Read/Write    | A15 A14 | A13         | A12<br>A20 | A11       | A10  | A9         | A8         |  |

| - 011    | 1,11(0)       |                                   | AZ3 AZZ | AZI         | AZU        | A19       | A18  | A17        | A16        |  |

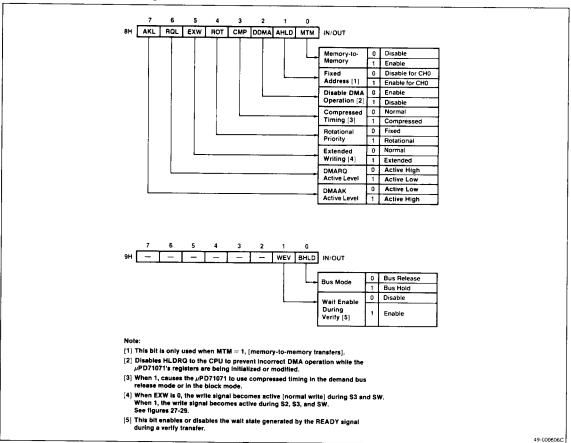

| 8H<br>9H | R/W<br>R/W    | Device Control<br>Reg. Read/Write | AKL RQL | EXW         | ROT        | СМР       | DDMA | AHLD       | MTM        |  |

| 90       |               |                                   |         |             |            |           |      | WEV        | BHLD       |  |

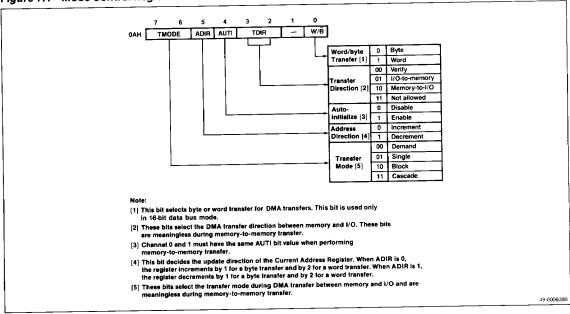

| 0AH      | R/W(B)        | Mode Control<br>Reg. Read/Write   | TMODE   | ADIR        | AUTI       | TD        | IR   | _          | W/B        |  |

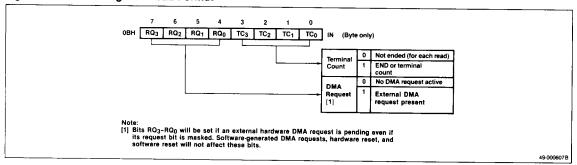

| овн      | R(B)          | Status Register<br>Read           | RQ3 RQ2 | RQ1         | RQ0        | TC3       | TC2  | TC1        | TC0        |  |

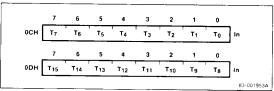

| осн      | R             | Temporary Reg.<br>(lower) Read    | T7 T6   | T5          | T4         | <b>†3</b> | T2   | <b>T</b> 1 | T0         |  |

| ODH      | R             | Temporary Reg.<br>(higher) Read   | T15 T14 | T13         | T12        | T11       | T10  | T9         | T8         |  |

| 0EH      | R/W(B)        | Request Reg.<br>Read/Write        |         | _           |            | SRQ3      | SRQ2 | SRQ1       | SRQ0       |  |

| 0FH      | R/W(B)        | Mask Reg.<br>Read/Write           |         | _           | =]         | МЗ        | M2   | M1         | MO         |  |

Figure 12. Initialize Command Format

## **Channel Register**

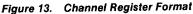

This command reads and writes the channel register that selects one of four DMA channels for programming the address, count, and mode control registers. Figure 13 shows the channel register read/write format.

### **Channel Register Read**

**SEL3-SEL0.** These mutually exclusive bits show which of the four channels is currently selected for programming.

**BASE.** Base = 0. The current register may be read. During a write, the base and current registers will be written to simultaneously.

Base = 1. Only the base registers may be read or written to.

### **Channel Register Write**

**SELCH.** This bit selects the channel to be programmed.

**BASE.** Base = 0. The current register may be read. During a write, the base and current registers will be written to simultaneously.

Base = 1. Only the base registers may be read or written to.

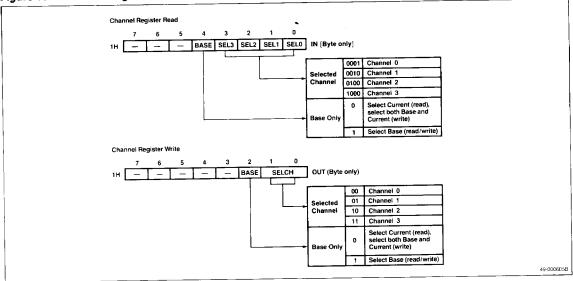

### Count Register Read/Write

When the 16-bit bus mode is selected, the IN/OUT instruction can directly transfer 16-bit data. The channel register selects one of the count registers. When bit 2 of the channel register write is cleared, a write to the count register updates both the base and current count registers with the new data. If bit 2 of the channel register write is set, a write to the count register only affects the base count register.

The base count registers hold the initial count value until a new count is specified. If autoinitialize is enabled, this value is transferred to the current count register when an END or TC is generated. For each DMA transfer, the current count register is decremented by one. Figure 14 shows the count register read/write format.

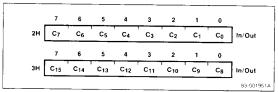

### Address Register Read/Write

When a 16-bit data bus width is selected, the IN/OUT instruction can directly transfer the lower two bytes (4H and 5H) of the register. You must use the byte IN/OUT instruction with the upper byte (6H) of the register. The channel register selects one of the address registers. When bit 2 of the channel register is cleared, a write to the address register updates both the base and current address registers with the new data. If bit 2 of the channel register is set, a write to the address register only affects the base address register.

The base register holds the starting address value until a new setting is made and this value is transferred to the current address register during autoinitialization. For each DMA transfer, the current address register is updated  $\pm 2$  during word transfer and  $\pm 1$  during byte transfer. Figure 15 shows the address register read/write format.

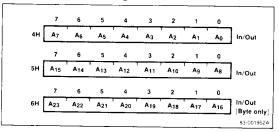

## **Device Control Register Read/Write**

The device control command reads from and writes to the device control register. When using a 16-bit data bus, use the word IN/OUT instruction to read and write 16-bit data. Figure 16 shows the device control register read/write format.

Figure 14. Count Register Read/Write Format

Figure 15. Address Register Read/Write Format

Figure 16. Device Control Register Read/Write Format

## Mode Control Register Read/Write

This command reads from and writes to the mode control register to specify the operating mode for each channel. The channel register selects the mode control register to be programmed. This command must be issued by the byte IN/OUT instruction. Figure 17 shows the mode control register read/write format.

## **Status Register Read**

This command reads the status register for the individual DMA channels. The register has DMA request states and terminal count or END information. This command must be issued by the byte IN instruction. Figure 18 shows the status register read format.

## **Temporary Register Read**

When a 16-bit data bus is selected, the IN instruction will read 16-bit data with this command. The last data transferred in memory-to-memory transfer is stored in the temporary register. Figure 19 shows the temporary register read format.

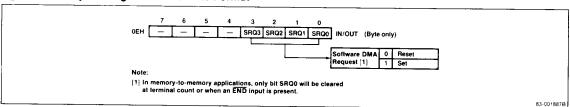

## Request Register Read/Write

This command reads from and writes to the request register to generate DMA requests by software for the four corresponding DMA channels. This command may be issued by the byte IN/OUT instruction. Figure 20 shows the reguest register read/write format.

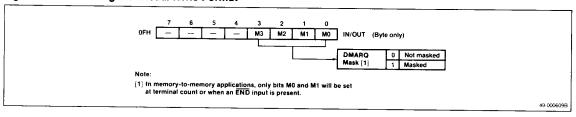

## Mask Register Read/Write

This command reads from and writes to the mask register to mask or unmask external DMA requests for the corresponding four DMA channels (DMARQ3-DMARQ0). This command may be issued by the byte IN/OUT instruction. Figure 21 shows the mask register read/write format.

### **DMA Transfer Modes**

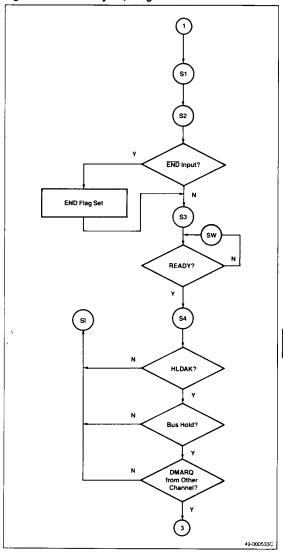

Figures 22-27 show state transition diagrams for the different modes of DMA transfer.

Figure 23 shows the state of a master  $\mu$ PD71071 when an input from a slave  $\mu$ PD71071 (cascaded  $\mu$ PD71071) is using the system bus.

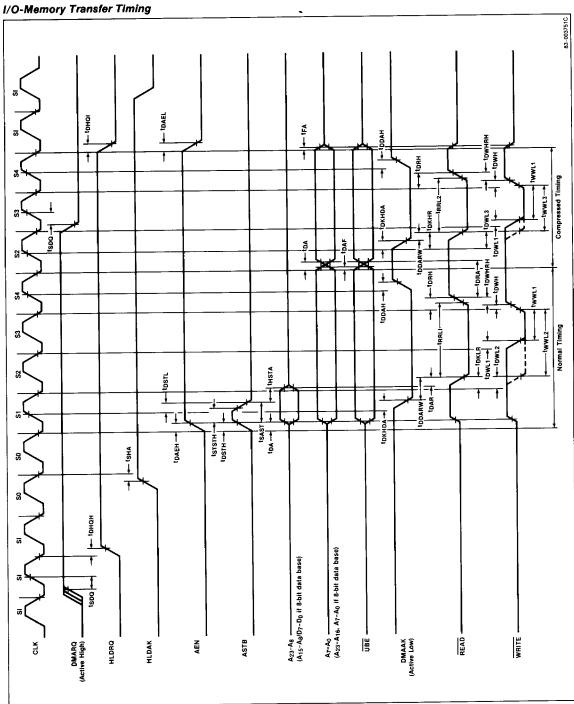

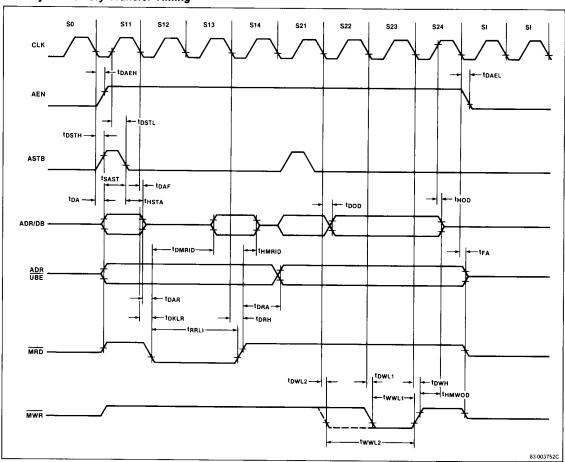

## **Transfer Timing**

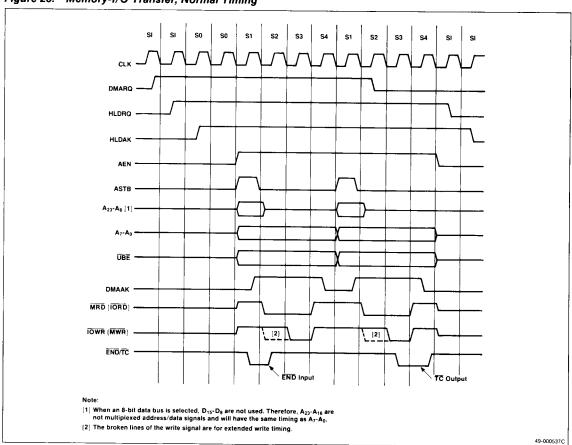

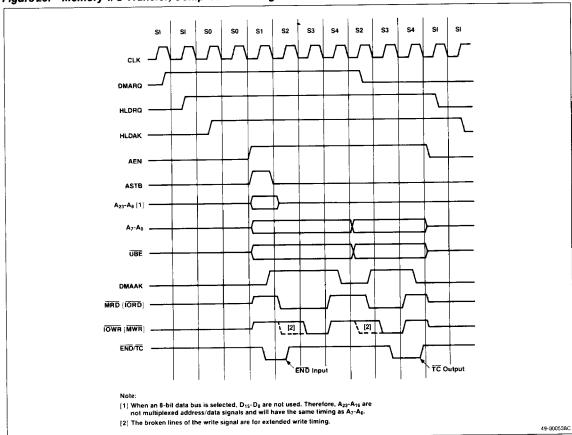

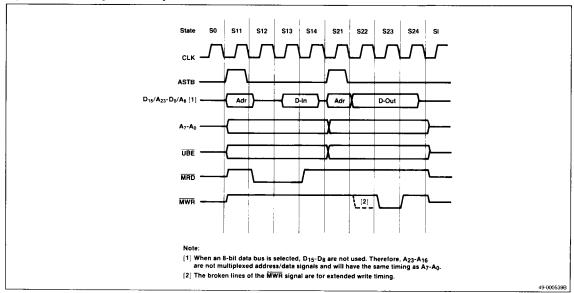

Figures 28-30 show  $\mu PD71071$  timing waveforms.

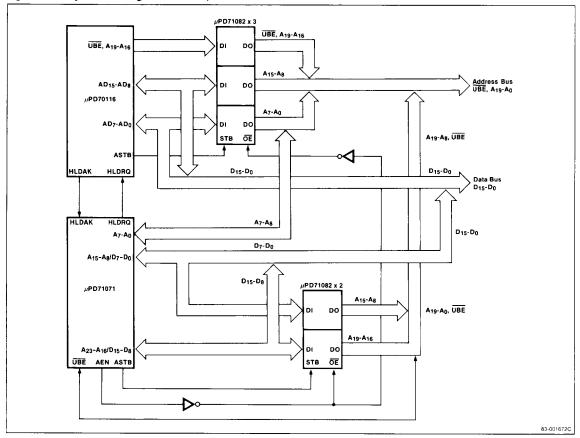

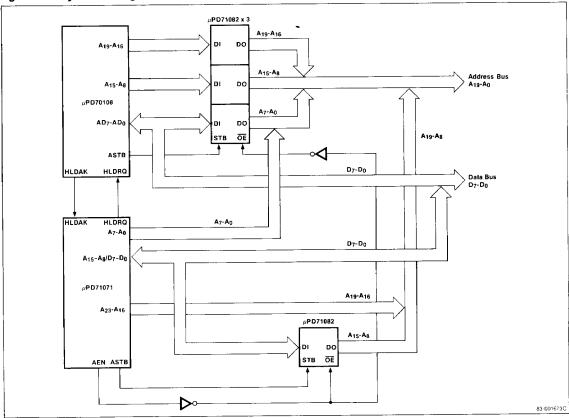

## **Examples of System Configuration**

Figures 31-32 show system configuration examples using the 8-bit  $\mu$ PD70108 CPU and the 16-bit  $\mu$ PD70116 CPU. The  $\mu$ PD71082 externally latches addresses and data.

Figure 17. Mode Control Register Read/Write Format

## Figure 18. Status Register Read Format

Figure 19. Temporary Register Read Format

## Figure 20. Request Register Read/Write Format

## Figure 21. Mask Register Read/Write Format

Figure 22. Idle Cycle

Figure 23. DMA Cycle, Cascade Mode

Figure 24. DMA Cycle, Single Mode

Figure 26. DMA Cycle, Block Mode

Figure 27. DMA Cycle, Memory-to-Memory Transfer

Figure 28. Memory-I/O Transfer, Normal Timing

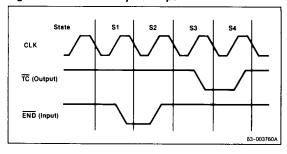

Figure 31. END/TC Input/Output

Figure 32. System Configuration with  $\mu$ PD70108

Figure 33. System Configuration with μPD70116