# MOS INTEGRATED CIRCUIT $\mu PD16662$

# 240 OUTPUT LCD COLUMN (SEGMENT) DRIVER WITH BUILT-IN RAM

The  $\mu$ PD16662 is a column (segment) driver which contains a RAM capable of full dot LCD drive. With 240 outputs, this driver has a display RAM of 240 x 160 x 2 bits built in, and 4 gray scales of display are possible. Any 4 gray scales can be selected from 25 levels of the gray scale pallet. The driver can be combined with the  $\mu$ PD16667 to display from 240 x 160 dots to 480 x 320 dots.

#### **Features**

• Display RAM incorporated: 240 x 160 x 2 bits

• Logic voltage: 3.0V to 3.6V

• Duty: 1/160

• Output count: 240 outputs

Capable of gray scale display: 4 gray scales (can be selected from 25 levels of the gray scale pallet)

• Memory management: packed pixel system

• 8/16-bit data base

#### **Ordering Information**

| Part number     | Package                                   |

|-----------------|-------------------------------------------|

| μPD16662N -×××  | TCP(TAB)                                  |

| μPD16662N - 051 | Standard TCP (OLB: 0.2 mm pitch; folding) |

The TCP's external shape is custom-ordered. Therefore, if you have a shape in mind, please contact an NEC salesperson.

The information in this document is subject to change without notice.

\*

#### Pin name

| Classification       | Voltage | Pin Name Note  | I/O | Function                                                |

|----------------------|---------|----------------|-----|---------------------------------------------------------|

| CPU I/F              | 3.3 V   | D0 to D15      | I/O | Data bus 16                                             |

|                      |         | A0 to A16      | - 1 | Address bus 17                                          |

|                      |         | /CS            | - 1 | Chip select                                             |

|                      |         | /OE            | ı   | Read signal                                             |

|                      |         | /WE            | - 1 | Write signal                                            |

|                      |         | /UBE           | - 1 | High byte enable                                        |

|                      |         | RDY            | 0   | Ready signal to CPU (Ready state at H)                  |

| Control signals      | 3.3 V   | PL0            | ı   | Specifies the LSI allocation locations (No. 0 to 3).    |

|                      |         | PL1            | - 1 | Specifies the LSI allocation locations (No. 0 to 3).    |

|                      |         | DIR            | - 1 | Specifies the liquid-crystal panel allocation direction |

|                      |         |                |     | (longitudinal; lateral)                                 |

|                      |         | MS             | - 1 | Master/slave switching (Master mode at H)               |

|                      |         | BMODE          | - 1 | Data bus bit select pin ("H" = 8bit, "L" = 16bit)       |

|                      |         | /REFRH         | I/O | Self diagnostic reset pin (Wired OR connection)         |

|                      |         | TEST           | - 1 | Test pin (Test mode at H, using the pull-down buffer)   |

|                      |         | /RESET         | - 1 | Reset                                                   |

|                      |         | /DOFF          | - 1 | Display OFF signal input                                |

|                      |         | OSC1           | -   | Oscillator pin                                          |

|                      |         | OSC2           | -   | Oscillator pin                                          |

|                      | 5.0 V   | STB            | I/O | Column driving signal strobe                            |

|                      |         |                |     | (MS signal "H" = output, MS signal "L" = input )        |

|                      |         | /FRM           | I/O | Frame signal(MS pin "H" = output , MS pin "L" = input ) |

|                      |         | PULSE          | I/O | 25-gray level pulse modulation clock                    |

|                      |         | L1             | I/O | Row driver drive level selection signal (1st line)      |

|                      |         | L2             | I/O | Row driver drive level selection signal (2nd line)      |

|                      |         | /DOUT          | 0   | Display OFF signal output                               |

| Liquid-crystal drive |         | Y1 to Y240     | 0   | Liquid-crystal drive output                             |

| Powers               |         | GND            | -   | Ground (two 5-V pins; three 3-V pins)                   |

|                      |         | Vcc1           | -   | 5-V power level                                         |

|                      |         | Vcc2           | -   | 3.3-V power level                                       |

|                      |         | Vo             | -   | Liquid-crystal drive analog power                       |

|                      |         | V <sub>1</sub> | -   | Liquid-crystal drive analog power                       |

|                      |         | V <sub>2</sub> | -   | Liquid-crystal drive analog power                       |

Remark /xxx indicates active low signal.

Note 3.3-V power pins : D0 - D15, A0 - A16, /CS, /OE, /WE, /UBE, RDY, BMODE, PL0, PL1, DIR, OSC1,

OSC2, /RESET, /DOFF, TEST, MS

5-V power pins : STB, /FRM, L1, L2, /DOUT, PULSE

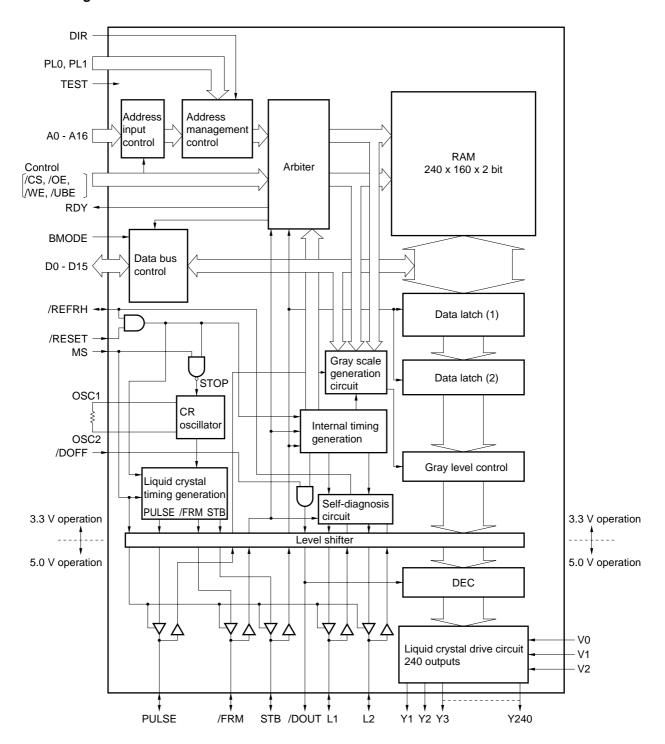

# **Block Diagram**

#### **Block Functions**

#### (1) Address management circuit

The address management circuit converts addresses transferred from the system through A0 to A16 into addresses compatible with the memory map of the built-in RAM. This function can be used to address up to 480 x 320 dots with four of these LSIs, thus making it possible to configure a liquid crystal display system without difficulty. Moreover, addresses 1FFF0H to 1FFFFH are allocated to the gray scale pallet register, making it possible to choose any 4 gray scales from the 25-level pallet.

#### (2) Arbiter

The arbiter adjusts the contention between the RAM access from the system and the RAM read on the liquid-crystal drive side.

#### (3) RAM

Static RAM (single port) of 240 by 160 by 2 bits

#### (4) Data bus control

This circuit controls the data transfer directions through the read/write from the system. It also performs an 8/16-bit switch via the BMODE pin.

#### (5) Gray scale generation circuit

This circuit realizes the 25 levels by frame thinning out and pulse width modulation.

#### (6) Internal timing generation

Internal timing to each block is generated from /FRM and STB signals.

#### (7) CR oscillator

The CR oscillator generates the clock which will become a criterion of the frame frequency in master mode. 1/2592 of this oscillation becomes the frame frequency. For example, if the frame frequency is 70 Hz, the required oscillation frequency is 181.44 kHz. As the CR oscillator has a built-in capacitor, adjust the required oscillation frequency with an external resistor.

In slave mode, the oscillation is stopped.

#### (8) Liquid crystal timing generation

In master mode, /FRM (frame signal), STB (column drive signal strobe), and PULSE (25-gray-scale pallet pulse modulation clock) are generated.

#### (9) Gray scale control

This circuit realizes a four-gray scale display.

#### (10) Data latch (1)

Reads and latches 240-pixel data from the RAM.

#### (11) Data latch (2)

Latches 240-pixel data synchronously with the STB signal.

#### (12) Level shifter

The level shifter converts from the operating voltage (3.3 V) of the internal circuit to the liquid-crystal drive circuit and low driver interface voltage (5 V).

#### (13) DEC

Decodes the gray scale display data to make it compatible with the liquid-crystal drive voltages Vo, V1 and V2.

#### (14) Liquid crystal drive circuit

This circuit selects one of the liquid-crystal drive powers V<sub>0</sub>, V<sub>1</sub>, and V<sub>2</sub>, which are compatible with the gray scale display data and the display OFF signal (/DOFF), to generate the liquid crystal applied voltage.

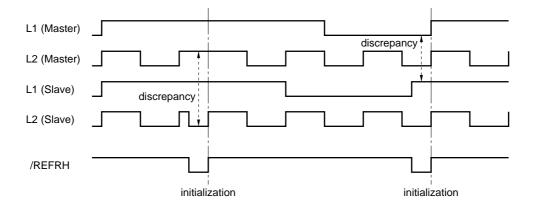

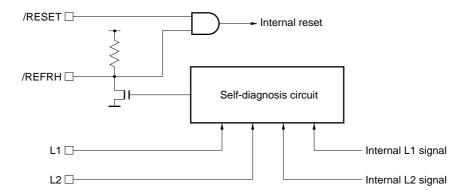

# (15) Self diagnostic circuit

If the operation timing of the master chip and slave chip has deviated due to external noise, this circuit will detect the problem and generate a total column/driver refresh signal.

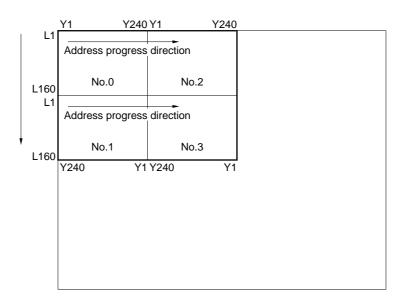

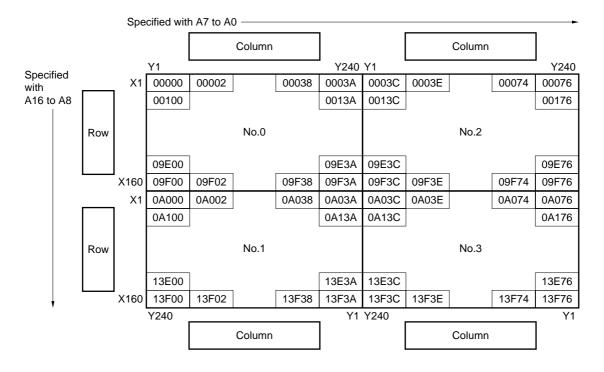

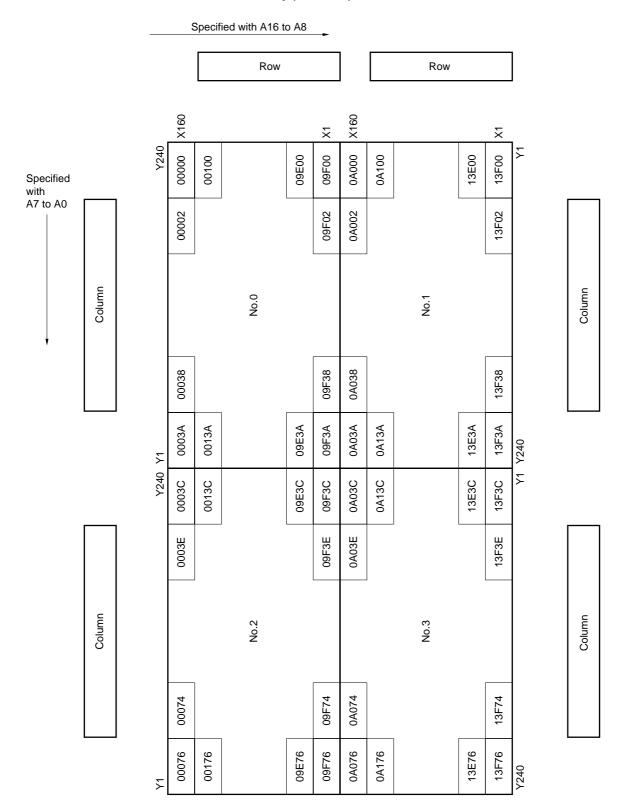

#### Address map image diagram (Example of VGA-half size configuration)

Column direction specified with A7 to A0

#### Data bus

The byte data lined up on the data bus is based on the Little Endian - an NEC/Intel-series bus.

#### 1. 16 bit data bus (BMODE = L)

• Bytes (8 bytes) access

Addresses proceed as  $\rightarrow$  shown on right.

| D0 to D7 | D8 to D15 |

|----------|-----------|

| 00000H   | 00001H    |

| 00002H   | 00003H    |

| 00004H   | 00005H    |

|          | :<br>:    |

| :        | :         |

• Words (16 bits) access

Addresses proceed as  $\rightarrow$  shown on right.

| D0 to D7 | D8 to D15 |

|----------|-----------|

| 000      | 00H       |

| 000      | 02H       |

| 000      | 04H       |

|          | ·<br>·    |

|          |           |

For the access from the system to be performed in units of words (16 bits), or of bytes (8 bytes), the /UBE (high byte enable) and A0 are used to show whether valid data are in the bytes of either (or both) of D0 to D7 and D8 to D15.

| /CS | /OE | /WE | /UBE | A0 | MODE           | I/       | 0         |

|-----|-----|-----|------|----|----------------|----------|-----------|

|     |     |     |      |    |                | D0 to D7 | D8 to D15 |

| Н   | Х   | Х   | Х    | Х  | Not Selected   | Hi-Z     | Hi-Z      |

| L   | L   | Н   | L    | L  | Read           | Dout     | Dout      |

|     |     |     | L    | Н  |                | Hi-Z     | Dout      |

|     |     |     | Н    | L  |                | Dout     | Hi-Z      |

| L   | Н   | L   | L    | L  | Write          | Din      | Din       |

|     |     |     | L    | Н  |                | X        | Din       |

|     |     |     | Н    | L  |                | Din      | Х         |

| L   | Н   | Н   | X    | Х  | Output disable | Hi-Z     | Hi-Z      |

| L   | X   | X   | Н    | Н  |                | Hi-Z     | Hi-Z      |

$\textbf{Remark} \quad X \quad : Don't \ Care$

Hi-Z: High impedance

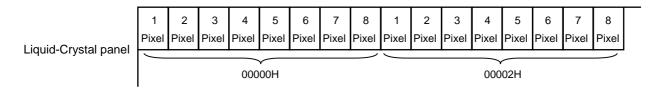

# 2. 8 bit data bus (BMODE = H)

D0 to D7

00000H

Addresses proceed as → 00001H

shown on right. 00002H

:

:

| /CS | /OE | /WE | MODE           | I/        | 0         |  |  |

|-----|-----|-----|----------------|-----------|-----------|--|--|

|     |     |     |                | D0 to D7  | D8 to D15 |  |  |

| Н   | Х   | Х   | Not Selected   | Hi-Z      | Note      |  |  |

| L   | L   | Н   | Read           | Dout      | Note      |  |  |

| L   | Н   | L   | Write          | Din       | Note      |  |  |

| L   | Н   | Н   | Output disable | Hi-Z Note |           |  |  |

Remark X : Don't Care

Hi-Z: High impedance

$\textbf{Note} \;\; \textbf{Use D8 - D15} \; \textbf{and /UBE} \; \textbf{to open or connect to the GND because they are internally pulled down when} \;\;$

BMODE = H.

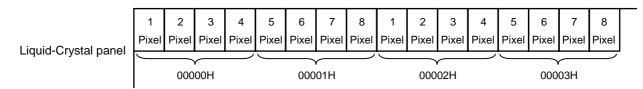

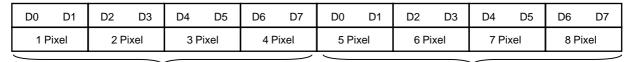

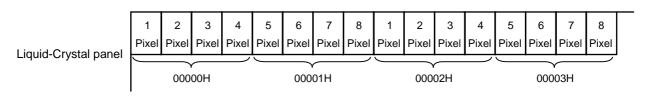

# Relationship between data bits and pixels

As the display is in four gray scales, each pixel consists of two bits.

The RAM is configured with four pixels (8 pixels per word) using the packed pixel system.

#### (1) BMODE = L

#### Bytes (8 bits) access

|               | D0 | D1  | D2   | D3  | D4   | D5  | D6   | D7            | D8            | D9  | D10  | D11 | D12  | D13 | D14  | D15           |

|---------------|----|-----|------|-----|------|-----|------|---------------|---------------|-----|------|-----|------|-----|------|---------------|

| 1 Pixel       |    | 2 P | ixel | 3 P | ixel | 4 P | ixel | 5 P           | ixel          | 6 P | ixel | 7 P | ixel | 8 P | ixel |               |

| $\overline{}$ |    |     |      |     | _    |     |      | $\overline{}$ | $\overline{}$ |     |      |     |      |     |      | $\overline{}$ |

00000H 00001H

#### Words (16 bits) access

| D0      | D1 | D2  | D3   | D4  | D5   | D6  | D7   | D8  | D9   | D10 | D11  | D12 | D13  | D14 | D15  |

|---------|----|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|-----|------|

| 1 Pixel |    | 2 F | ixel | 3 P | ixel | 4 P | ixel | 5 P | ixel | 6 P | ixel | 7 P | ixel | 8 P | ixel |

#### 00000H

#### (2) BMODE = H

00000H 00001H

#### **Gray scale control**

The  $\mu$ PD16662 gray scale control realizes 25 levels of the gray scale pallet through frame thinning and pulse width modulation. It chooses four gray scales and records them in the gray scale pallet register before use.

#### Gray scale pallet register

Through the use of the gray scale pallet register, four gray scales are pre-selected from 25 levels. The gray scale pallet register is allocated in addresses 1FFF0H to 1FFFFH, and the relationship between the register and the gray scale data is shown in the following table. The initial values are also allocated as below. The gray scale pallet register can set each column/driver configuration position (No.0 to 3) decided by PL0 and PL1.

| Address | Configuration position | Gray scale dat | ta (Display data)  | Initial value |

|---------|------------------------|----------------|--------------------|---------------|

|         | No.                    | Dn+1 Note      | Dn <sup>Note</sup> |               |

| 1FFF0H  | No.0                   | 0              | 0                  | 00000B        |

| 1FFF1H  |                        | 0              | 1                  | 01000B        |

| 1FFF2H  |                        | 1              | 0                  | 10000B        |

| 1FFF3H  |                        | 1              | 1                  | 11000B        |

| 1FFF4H  | No.1                   | 0              | 0                  | 00000B        |

| 1FFF5H  |                        | 0              | 1                  | 01000B        |

| 1FFF6H  |                        | 1              | 0                  | 10000B        |

| 1FFF7H  |                        | 1              | 1                  | 11000B        |

| 1FFF8H  | No.2                   | 0              | 0                  | 00000B        |

| 1FFF9H  |                        | 0              | 1                  | 01000B        |

| 1FFFAH  |                        | 1              | 0                  | 10000B        |

| 1FFFBH  |                        | 1              | 1                  | 11000B        |

| 1FFFCH  | No.3                   | 0              | 0                  | 00000B        |

| 1FFFDH  |                        | 0              | 1                  | 01000B        |

| 1FFFEH  |                        | 1              | 0                  | 10000B        |

| 1FFFFH  |                        | 1              | 1                  | 11000B        |

**Note** n = 0, 2, 4, 6

# Relationship between gray scale and gray scale pallet data

The relationship between the gray scale and the gray scale pallet data that is set by the gray scale pallet register is as follows.

| PMODE    |      | Remark |    |    |    |     |

|----------|------|--------|----|----|----|-----|

|          | D4   | D3     | D2 | D1 | D0 |     |

| Pixel 0  | 0    | 0      | 0  | 0  | 0  | OFF |

| Pixel 1  | 0    | 0      | 0  | 0  | 1  |     |

| Pixel 2  | 0    | 0      | 0  | 1  | 0  |     |

| Pixel 3  | 0    | 0      | 0  | 1  | 1  |     |

| Pixel 4  | 0    | 0      | 1  | 0  | 0  |     |

| Pixel 5  | 0    | 0      | 1  | 0  | 1  |     |

| Pixel 6  | 0    | 0      | 1  | 1  | 0  |     |

| Pixel 7  | 0    | 0      | 1  | 1  | 1  |     |

| Pixel 8  | 0    | 1      | 0  | 0  | 0  | 1/3 |

| Pixel 9  | 0    | 1      | 0  | 0  | 1  |     |

| Pixel 10 | 0    | 1      | 0  | 1  | 0  |     |

| Pixel 11 | 0    | 1      | 0  | 1  | 1  |     |

| Pixel 12 | 0    | 1      | 1  | 0  | 0  |     |

| Pixel 13 | 0    | 1      | 1  | 0  | 1  |     |

| Pixel 14 | 0    | 1      | 1  | 1  | 0  |     |

| Pixel 15 | 0    | 1      | 1  | 1  | 1  |     |

| Pixel 16 | 1    | 0      | 0  | 0  | 0  | 2/3 |

| Pixel 17 | 1    | 0      | 0  | 0  | 1  |     |

| Pixel 18 | 1    | 0      | 0  | 1  | 0  |     |

| Pixel 19 | 1    | 0      | 0  | 1  | 1  |     |

| Pixel 20 | 1    | 0      | 1  | 0  | 0  |     |

| Pixel 21 | 1    | 0      | 1  | 0  | 1  |     |

| Pixel 22 | 1    | 0      | 1  | 1  | 0  |     |

| Pixel 23 | 23 1 |        | 1  | 1  | 1  |     |

| Pixel 24 | 1    | 1      | 0  | 0  | 0  | ON  |

#### LSI arrangement and address management

Addresses can be managed to allow up to four of these LSIs to be used to configure a liquid-crystal display of up to half VGA size (320 x 480 dots). Up to four of these LSIs can be connected on the same bus sharing the /CS, /WE, and /OE pins. On the system side, one screen of the liquid crystal display can be treated as one memory area, and it is not necessary to decode for more than one  $\mu$ PD16662. The PL0 and PL1 pins are used to specify LSI No. and to determine the LSI arrangement. The DIR pins are used to determine the directions (vertical, horizontal) of the liquid-crystal display.

| PL1 | PL0 | LSI No. |

|-----|-----|---------|

| 0   | 0   | No. 0   |

| 0   | 1   | No. 1   |

| 1   | 0   | No. 2   |

| 1   | 1   | No. 3   |

#### 1. Addresses of the VGA half-size horizontally (DIR = "0")

# 2. Addresses of the VGA half-size horizontally (DIR = "1")

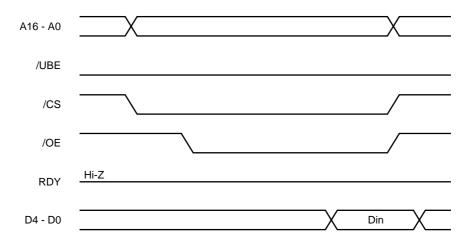

#### **CPU Interface**

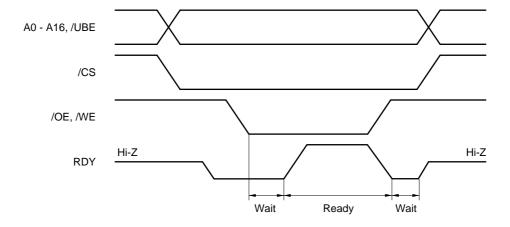

#### 1. Function of the RDY (Ready) pin

The built-in RAM is a single-port RAM. To prevent contention between the access from the CPU side and the reading by the liquid-crystal drive side, the RDY pin performs a Wait operation on the CPU.

#### ★ • Timing

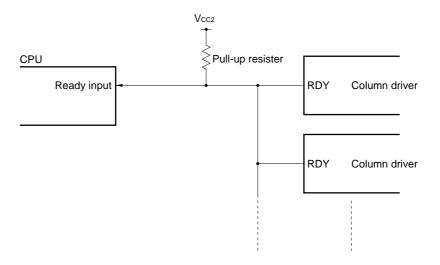

#### • Connection of the RDY pin

The RDY pin uses a three-state buffer. The RDY pin should be connected to an external pull-up resister. If more than one LSI are used, the RDY pins of each LSI are wired together.

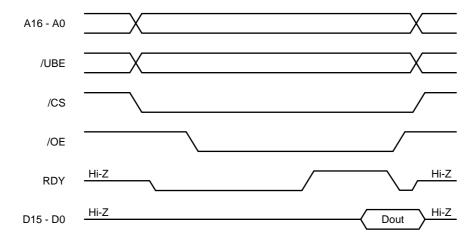

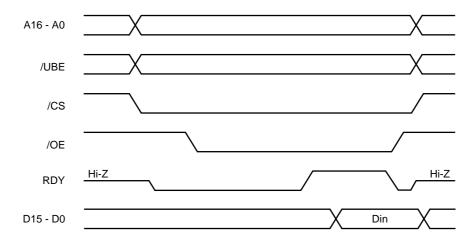

# ★ 2. Access Timing

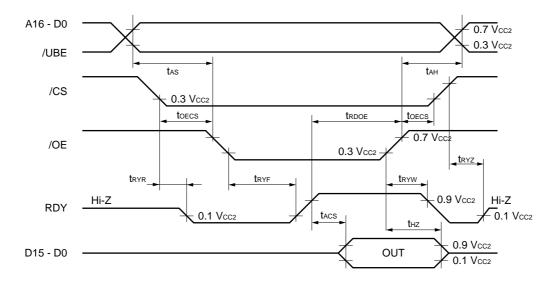

# (1) Display data read timing

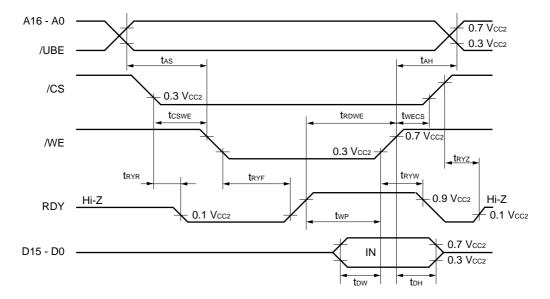

# (2) Display data write timing

# (3) Gray scale pallet data write timing

# **Liquid-Crystal Timing Generation**

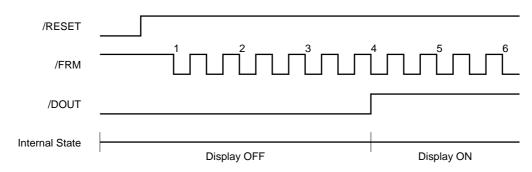

#### 1. Reset State

If the circuit is placed in the reset state, the internal counter is zero-cleared.

After cancelling the reset, the display OFF function operates during the 4-frame cycle even when the /DOFF pin is at H.

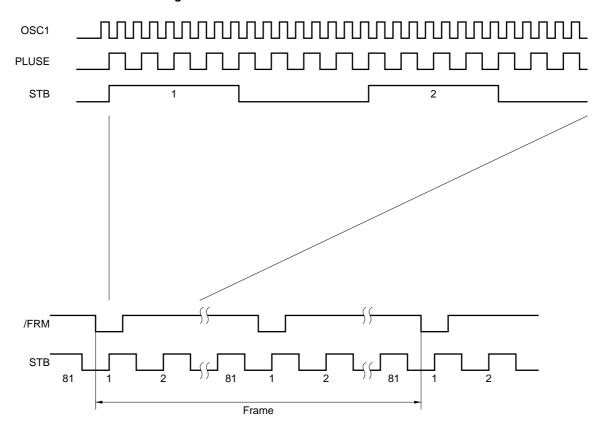

# 2. Liquid-Crystal Timing Generating Circuit

If the circuit is set to Master mode when MS = H, the /FRM and STB signals are generated timed with a duty ratio 1/160.

Generates the driver drive voltage selection signals L1 and L2 for the row driver.

The /FRM is generated twice per frame. The STB is generated 81 times per half a frame; and 162 times per frame.

#### • Generation of /FRM and STB signals

#### • Generation of L1 and L2 signals

|   | STB | 1 | 2 | 3 | 4 | <br>1 | 2 | 3 | 4 | <br>1 | 2 | 3 | 4 | <br>1 | 2 | 3 | 4 |  |

|---|-----|---|---|---|---|-------|---|---|---|-------|---|---|---|-------|---|---|---|--|

|   | L1  | 1 | 1 | 1 | 1 | <br>1 | 1 | 1 | 1 | <br>0 | 0 | 0 | 0 | <br>0 | 0 | 0 | 0 |  |

| Ī | L2  | 1 | 0 | 1 | 0 | <br>0 | 1 | 0 | 1 | <br>0 | 1 | 0 | 1 | <br>1 | 0 | 1 | 0 |  |

# Self diagnostic function

This is a function to check whether the timing of each column/driver has deviated due to external noise. The slave chip compares the L1 and L2 generated internally with the L1 and L2 of the master chip, and when there is discordance, it sends a total column/driver refresh signal. When a refresh signal is received, the internal reset is activated and timing is initialized. In this case, the /REFRH = L time and the four frame interval display are turned OFF. The L1, L2 discordance will be monitored at the rising edge of the FRM once every 1/2 frame.

#### • Block configuration drawing (slave side)

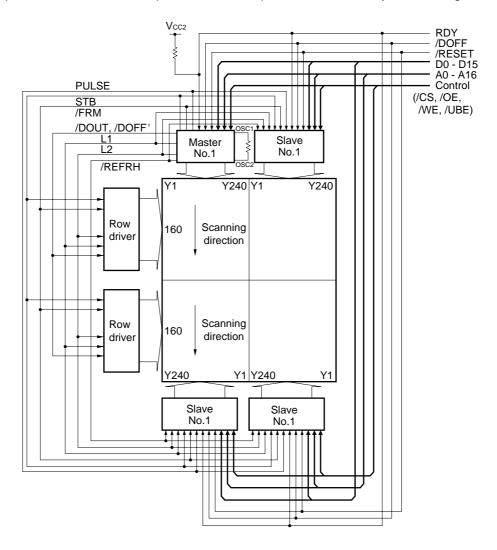

#### **System Configuration Example**

An example of configuring a liquid-crystal panel of VGA half-size ( $480 \times 320$  dots lengthwise) by using four LSIs and two row drivers.

- Each column driver sets the LSI No. with PL0, PL1 pins.

- The DIR pins of each column driver are all set to low level.

- Only one of the column drivers is set to the master; all the others are set to the slave. Signals are supplied from the master column driver to the slave column driver and to the row driver.

- Connect a resistor for the oscillator to the OSC1 and OSC2 pins of the master. Leave the OSC1 and OSC2 pins of the slave open.

- The signals from the system (D0 through D15, A0 through A16, /CS, /OE, /WE, /UBE, RDY, /RESET, and /DOFF) are connected to all the column drivers in parallel. Connect a pull-up resistor to the RDY signal.

- The TEST pin is used to test the LSI. Open or connect this pin to GND when the system is configured.

**Remark** The /DOFF' pin is an input pin of  $\mu$ PD16667.

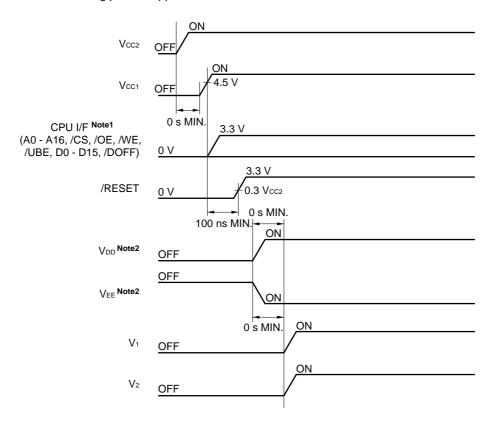

# Chip set power-ON sequence

It is recommended to turn on power in the following sequence:

$Vcc2 \rightarrow Vcc1 \rightarrow input \rightarrow Vdd, \ Vee \rightarrow V1, \ V2$

Be sure to turn on LCD driving power supplies V<sub>1</sub> and V<sub>2</sub> last.

Notes 1. It is possible to input the selected pins (PI0, PL1, DIR, MS, and BMODE) at the same time as Vcc2.

2. It is not necessary to have VDD and VEE ON at the same time. VDD and VEE are the liquid crystal power supply of row driver.

Caution Turn off power to the chip set in the reverse sequence to the turn-on sequence.

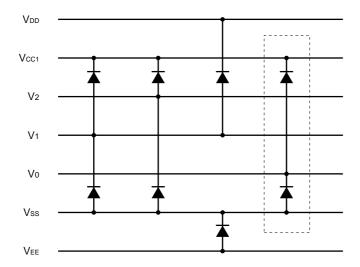

# Example of layout of internal Schottky barrier diode of module to reinforce power supply protection

(Use a Schottky barrier diode with Vf = 0.5 V MAX.)

Include the diodes enclosed in the dotted line in the above figure when Vo is not 0 V (GND).

Note  $V_{\text{DD}}$  and  $V_{\text{EE}}$  are the liquid crystal power supply of row driver.

# **Electrical specifications**

1. Absolute Maximum Ratings (T<sub>A</sub> = +25 °C)

| Parameter                | Symbol             | Rating            | Unit | Notes |

|--------------------------|--------------------|-------------------|------|-------|

| Supply voltage (1)       | Vcc1               | -0.5 to +6.5      | V    | 1     |

| Supply voltage (2)       | Vcc2               | -0.5 to +4.5      | V    | 2     |

| Input/Output voltage (1) | VI/01              | -0.5 to Vcc1 +0.5 | V    | 1     |

| Input/Output voltage (2) | V <sub>I/O2</sub>  | -0.5 to Vcc2 +0.5 | V    | 2     |

| Input/Output voltage (3) | V1/03              | -0.5 to Vcc1 +0.5 | V    | 3, 4  |

| Operating temperature    | TA                 | -20 to +70        | °C   |       |

| Storage temperature      | T <sub>stg</sub> . | -40 to +125       | °C   |       |

- Notes 1. 5 V power signal (/FRM, STB, /DOUT, L1, L2, PULSE)

- 2. 3.3 V power signal (MS, DIR, PL0 to PL1, A0 to A16, /CS, /OE, /WE, /UBE, RDY, D0 to D15, /RESET, OSC1, OSC2, /DOFF, TEST, BMODE, /REFRH)

- 3. Liquid-crystal drive powers (V<sub>0</sub>, V<sub>1</sub>, V<sub>2</sub>, Y1 to Y240)

- 4.  $V_0 < V_1 < V_2$

2. Recommended Operating Range (T<sub>A</sub> = 20 to +70 C, V<sub>O</sub> = 0 V)

| Parameter                   | Symbol         | MIN.           | TYP. | MAX.             | Unit | Notes |

|-----------------------------|----------------|----------------|------|------------------|------|-------|

| Supply voltage (1)          | Vcc1           | 4.5            | 5.0  | 5.5              | V    |       |

| Supply voltage (2)          | Vcc2           | 3.0            | 3.3  | 3.6              | V    |       |

| Input voltage (1)           | VI1            | 0              |      | Vcc <sub>1</sub> | V    | 1     |

| Input voltage (2)           | VI2            | 0              |      | Vcc2             | V    | 2     |

| V1 Input voltage            | V <sub>1</sub> | V <sub>0</sub> |      | V <sub>2</sub>   | V    |       |

| V2 Input voltage            | V <sub>2</sub> | V <sub>1</sub> |      | Vcc1             | V    |       |

| External resistance for OSC | Rosc           | 30             | 62   | 90               | kΩ   |       |

Notes 1. 5 V power signal (/FRM, STB, L1, L2, PULSE)

2. 3.3 V power signal (MS, DIR, PL0 to PL1, A0 to A16, /CS, /OE, /WE, /UBE, RDY, D0 to D15, /RESET, OSC1, OSC2, /DOFF, TEST, BMODE, /REFRH)

$\star$

#### 3. DC Characteristics

(Unless otherwise specified, Vcc1 = 4.5 to 5.5 V, Vcc2 = 3.0 to 3.6 V. V0 = 0 V, V1 = 1.4 to 2.0 V, V2 = 2.8 to 4.0 V, VA = -20 to +70 °C)

| = -20 to +70 °C)                              |                  | , , , , , , , , , , , , , , , , , , , |           |      |         | 1    | I                                  | 1     |

|-----------------------------------------------|------------------|---------------------------------------|-----------|------|---------|------|------------------------------------|-------|

| Parameter                                     |                  | Symbol                                | MIN.      | TYP. | MAX.    | Unit | Remark                             | Notes |

| High-level input voltage (1)                  | Vcc1             | VIH1                                  | 0.7 Vcc1  |      |         | V    |                                    | 1     |

| Low-level input voltage (1)                   |                  | VIL1                                  |           |      | 0.3Vcc1 | V    |                                    | 1     |

| High-level input voltage (2)                  | Vcc2             | VIH2                                  | 0.7 Vcc2  |      |         | V    |                                    | 2     |

| Low-level input voltage (2)                   |                  | V <sub>IL2</sub>                      |           |      | 0.3Vcc2 | V    |                                    | 2     |

| High-level output voltage (1)                 |                  | V <sub>IH3</sub>                      | 0.8 Vcc2  |      |         | V    |                                    | 4     |

| Low-level output voltage (1)                  |                  | VIL4                                  |           |      | 0.2Vcc2 | V    |                                    | 4     |

| High-level output voltage (2)                 | Vcc1             | Vон1                                  | Vcc1 -0.4 |      |         | V    | Iон = −1 mA                        | 3     |

| Low-level output voltage (2)                  |                  | V <sub>OL1</sub>                      |           |      | 0.4     | V    | loL = 2 mA                         | 3     |

| High-level output voltage (3)                 |                  | V <sub>OH2</sub>                      | Vcc1 -0.4 |      |         | V    | Iон = −2 mA                        | 1     |

| Low-level output voltage (3)                  |                  | Vol3                                  |           |      | 0.4     | V    | loL = 4 mA                         | 1, 4  |

| High-level output voltage (3)                 | Vcc2             | Vонз                                  | Vcc2 -0.4 |      |         | V    | Iон = −1 mA                        | 5     |

| Low-level output voltage (3)                  |                  | Vol3                                  |           |      | 0.4     | V    | loL = 2 mA                         | 5     |

| Input leakage current (1)                     |                  | l <sub>11</sub>                       |           |      | ±10     | μΑ   | Without TEST pin, V1 = Vcc2 or GND |       |

| Input leakage current (2)                     |                  | l <sub>12</sub>                       | 10        | 40   | 100     | μΑ   | Pull down (TEST pin ) V1 = Vcc2    |       |

| Current consumption for display operation (1) | Vcc1             | IMAS1                                 |           |      | 100     | μΑ   | master                             | 6     |

| Current consumption for display operation (2) | Vcc2             | IMAS2                                 |           |      | 250     | μΑ   | master                             | 6     |

| Current consumption for display operation (3) | V <sub>CC1</sub> | IsLV1                                 |           |      | 60      | μΑ   | slave                              | 6     |

| Current consumption for display operation (4) | Vcc2             | Íslv2                                 |           |      | 150     | μΑ   | slave                              | 6     |

| Liquid crystal drive output on resistance     |                  | Ron                                   |           | 1    | 2       | kΩ   |                                    | 7     |

Notes 1. 5 V signal (/FRM, STB, L1, L2, PULSE)

- 2. 3.3 V signal (MS, DIR, PL0 to PL1, A0 to A16, /CS, /OE, /WE, /UBE, RDY, D0 to D15, /RESET, /DOFF, TEST, BMODE)

- 3. /DOUT pin

- 4. /REFRH pin

- 5. D0 to 15, RDY, and OSC2 pins

- **6.** With the frame frequency at 70 Hz without output load and CPU no access (D0 to D15, A0 to A16, /UBE = GND, /CS, /OE, /WE = Vcc2)

- 7. This refers to the resistance value between a Y pin and a V pin (either of V<sub>0</sub>, V<sub>1</sub> and V<sub>2</sub>) when the load current (IoN = 100  $\mu$ A) is passed to a pin of Y1 to Y240.

# 4. AC Characteristics 1 Display data transfer timing

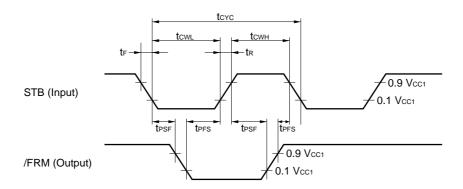

# (1) Master mode

(Unless otherwise specified, Vcc1 = 4.5 to 5.5 V, Vcc2 = 3.0 to 3.6 V. V0 = 0 V, V1 = 1.4 to 2.0 V, V2 = 2.8 to 4.0 V,

$T_A = -20$  to +70 °C, frame frequency 70 Hz (fosc = 181.44 kHz), output load: 100 pF)

|                      |              |      |         | , ·  |      | 1 /    |

|----------------------|--------------|------|---------|------|------|--------|

| Parameter            | Symbol       | MIN. | TYP.    | MAX. | Unit | Remark |

| STB clock cycle time | tcyc         | 87   | 16/fosc |      | μs   |        |

| STB high-level width | tсwн         | 43   | 8/fosc  |      | μs   |        |

| STB low-level width  | tcwL         | 43   | 8/fosc  |      | μs   |        |

| STB rise time        | <b>t</b> R   |      |         | 100  | ns   |        |

| STB fall time        | tr           |      |         | 100  | ns   |        |

| STB -/FRM delay time | tpsf         | 20   |         |      | μs   |        |

| /FRM -STB delay time | <b>t</b> PFS | 20   |         |      | μs   |        |

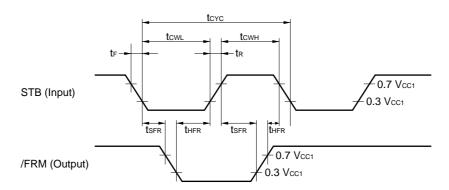

# (2) Slave mode

(Unless otherwise specified, Vcc1 = 4.5 to 5.5 V, Vcc2 = 3.0 to 3.6 V. V0 = 0 V, V1 = 1.4 to 2.0 V, V2 = 2.8 to 4.0 V,

$T_A = -20 \text{ to } +70 \, ^{\circ}\text{C}$

| Parameter            | Symbol     | MIN. | TYP. | MAX. | Unit | Remark |

|----------------------|------------|------|------|------|------|--------|

| STB clock cycle time | tcyc       | 10   |      |      | μs   |        |

| STB High-level width | tсwн       | 4    |      |      | μs   |        |

| STB low-level width  | tcwL       | 4    |      |      | μs   |        |

| STB rise time        | <b>t</b> R |      |      | 150  | ns   |        |

| STB fall time        | tr         |      |      | 150  | ns   |        |

| /FRM setup time      | tsfr       | 1    |      |      | μs   |        |

| /FRM hold time       | ther       | 1    |      |      | μs   |        |

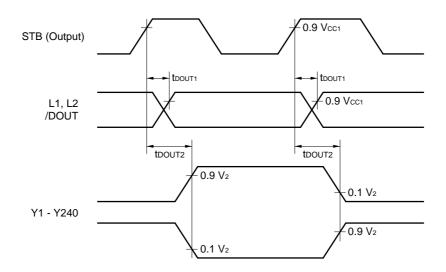

# (3) Items common to the master and slaves

(Unless otherwise specified,  $V_{CC1} = 4.5$  to 5.5 V,  $V_{CC2} = 3.0$  to 3.6 V.  $V_0 = 0$  V,  $V_1 = 1.4$  to 2.0 V,  $V_2 = 2.8$  to 4.0 V,  $V_3 = -20$  to +70 °C)

| Parameter                         | Symbol         | MIN. | TYP. | MAX. | Unit | Remark              |

|-----------------------------------|----------------|------|------|------|------|---------------------|

| Output delay time (L1, L2, /DOUT) | <b>t</b> DOUT1 |      | 50   | 100  | ns   | Without output load |

| Output delay time (Y1 to Y240)    | <b>t</b> DOUT2 |      | 90   | 150  | ns   | Without output load |

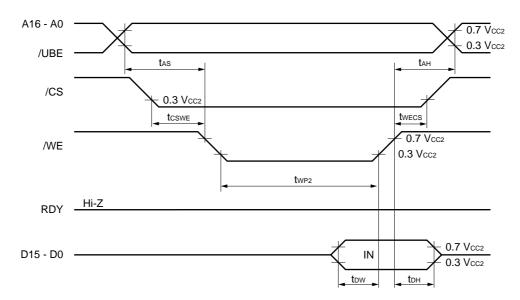

# 5. AC Characteristics 2 Graphic Access Timing

(Unless otherwise specified, Vcc1 = 4.5 to 5.5 V, Vcc2 = 3.0 to 3.6 V. V0 = 0 V, V1 = 1.4 to 2.0 V, V2 = 2.8 to 4.0 V,

$TA = -20 \text{ to } +70 \,^{\circ}\text{C}, \text{ tr} = \text{tf} = 5 \text{ ns})$

| Parameter                             | Symbol            | MIN. | TYP. | MAX.  | Unit | Remark     | Notes |

|---------------------------------------|-------------------|------|------|-------|------|------------|-------|

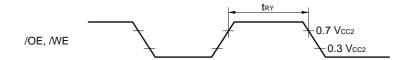

| /OE, /WE recovery time                | try               | 30   |      |       | ns   |            |       |

| Address setup time                    | <b>t</b> AS       | 10   |      |       | ns   |            |       |

| Address hold time                     | <b>t</b> AH       | 20   |      |       | ns   |            |       |

| RDY output delay time                 | tryr              |      |      | 30    | ns   | CL = 15 pF |       |

| RDY float time                        | tryz              |      |      | 30    | ns   |            | 3     |

| Wait state time                       | tryw              |      |      | 35    | ns   |            | 1     |

| Ready state time (without contention) | t <sub>RYF1</sub> |      | 60   | 100   | ns   |            | 1     |

| Ready state time (with contention)    | tryf2             |      | 650  | 1,200 | ns   |            | 1     |

| Data access time (Read cycle)         | tacs              |      |      | 100   | ns   |            | 2     |

| Data float time (Read cycle)          | tнz               |      |      | 40    | ns   |            | 3     |

| /CS - /OE time (Read cycle)           | tcsoe             | 10   |      |       | ns   |            |       |

| /OE - /CS time (Read cycle)           | toecs             | 20   |      |       | ns   |            |       |

| Write pulse width 1 (Write cycle 1)   | twp1              | 50   |      |       | ns   |            | 1     |

| Write pulse width 2 (Write cycle 2)   | twp2              | 50   |      |       | ns   |            | 1     |

| Data setup time (Write cycle 1, 2)    | tow               | 20   |      |       | ns   |            |       |

| Data hold time (Write cycle 1, 2)     | <b>t</b> DH       | 20   |      |       | ns   |            |       |

| /CS - /WE time (Write cycle 1, 2)     | tcswe             | 10   |      |       | ns   |            |       |

| /WE - /CS time (Write cycle 1, 2)     | twecs             | 20   |      |       | ns   |            |       |

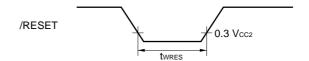

| Reset pulse width                     | twres             | 100  |      |       | ns   |            |       |

| RDY - /OE time                        | <b>t</b> RDOE     |      |      | -     | _    |            | 4     |

| RDY - /WE time                        | <b>t</b> RDWE     |      |      | -     | -    |            | 4     |

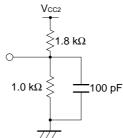

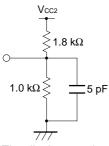

Notes 1. Load circuit

$V_{CC2}$   $1.8 \text{ k}\Omega$   $1.0 \text{ k}\Omega$  60 pF

2. Load circuit

Load circuit

**4.** The display may be affected if the time from the rising of RDY to /OE or /WE is too long. It is recommended that trdoe and trdwe be 1,000 ns MAX.

# /OE, /WE recovery time

# ★ Read cycle

# ★ Write cycle 1 (Display data write)

# Write cycle 2 (Gray scale pallet data write)

# Reset pulse width

#### 6. AC Characteristics 3 CR Oscillator

$$(Vcc2 = 3.0 \text{ to } 3.6 \text{ V}, TA = -20 \text{ to } +70 ^{\circ}\text{C})$$

| Parameter             | Symbol | MIN. | TYP. | MAX. | Unit | Remark                     |

|-----------------------|--------|------|------|------|------|----------------------------|

| Oscillation frequency | fosc   | 160  | 190  | 220  | kHz  | External resistance: 62 kΩ |

| Frame frequency       | _      | 61.7 | 73.3 | 84.9 | Hz   | External resistance: 62 kΩ |

#### Relation between oscillation frequency, frame frequency, and STB frequency

The relation between the oscillation frequency, frame frequency, and STB frequency is as follows:

Frame frequency =

$$\frac{1}{162 \times 2 \times 8}$$

x Oscillation frequency

STB frequency =

$$\frac{1}{2 \times 8}$$

x Oscillation frequency

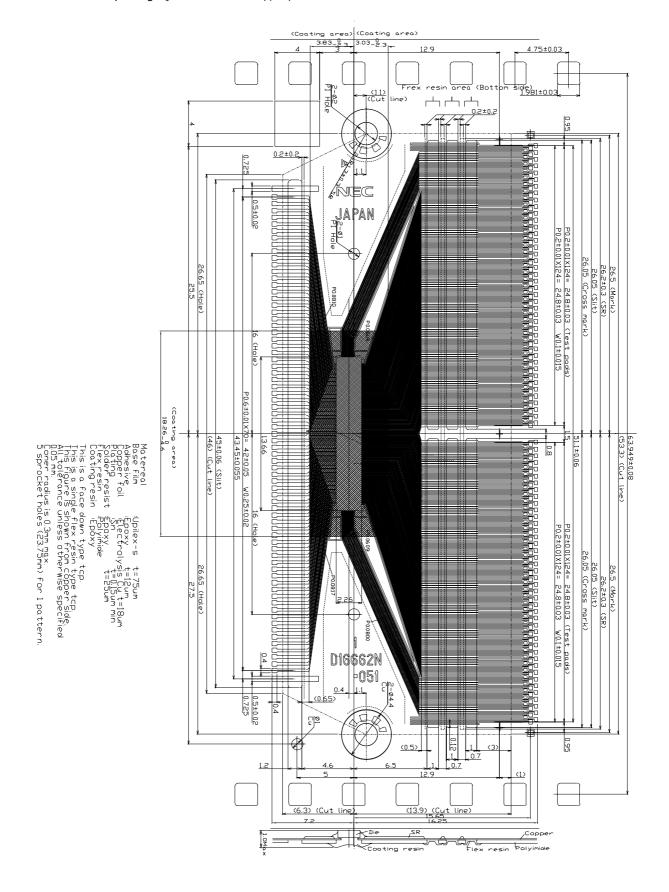

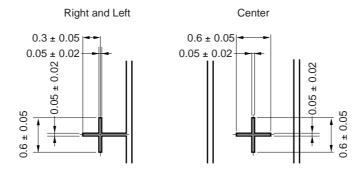

#### ★ Package drawings

Standard TCP package (µPD16662N - 051)(1/3)

Standard TCP package ( $\mu$ PD16662N - 051)(2/3)

Detail of output side test pad and alignment mark

Detail of cross mark

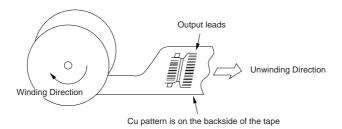

# TCP tape winding direction

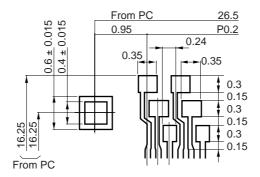

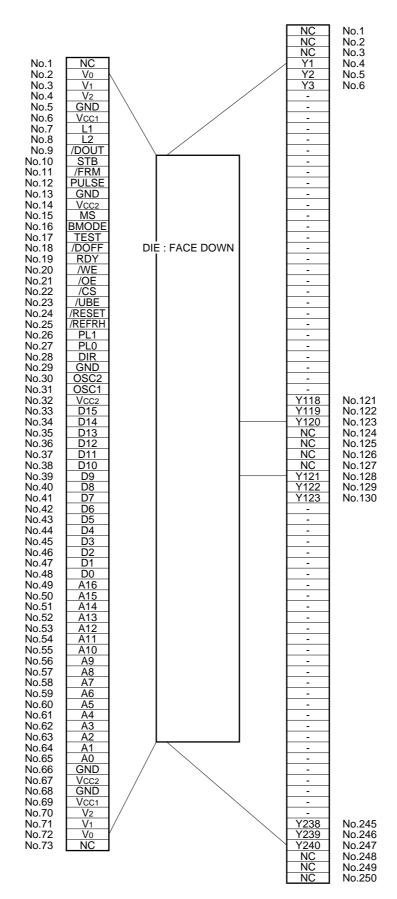

Standard TCP package ( $\mu$ PD16662N - 051) (3/3) Pin connection

[MEMO]

[MEMO]

# NOTES FOR CMOS DEVICES-

# (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.