# 3V DUAL DOWNCONVERTER AND PLL FREQUENCY SYNTHESIZER

# **UPB1004GS**

#### **FEATURES**

• INTEGRATED RF BLOCK:

RF & IF Downconverter + PLL frequency synthesizer

• **DOUBLE-CONVERSION:** f1stIF = 61.380 MHz

f2ndIF = 4.092 MHz

DADT NUMBER

• ADJUSTABLE GAIN: 20 dB range MIN

• FIXED DIVISION PRESCALER

• LOW POWER CONSUMPTION: 37.5 mA @ 3 V

SMALL 30 PIN SSOP PACKAGE

• TAPE AND REEL PACKAGING AVAILABLE

#### DESCRIPTION

The UPB1004GS is a Silicon Monolithic Integrated Circuit designed for low cost GPS receivers. The IC combines a double-conversion RF/IF downconverter block and a PLL frequency synthesizer on one chip. The device operates on a 3 V supply voltage and is housed in a small 30 pin SSOP package, resulting in low power consumption and reduced board space. The device is manufactured using the NESAT<sup>TM</sup> III 20 GHz ft silicon bipolar process.

NEC's stringent quality assurance and test procedures ensure the highest reliability and performance.

LIDD4004CC

#### ELECTRICAL CHARACTERISTICS (TA = 25°C, Vcc = 3 V, unless otherwise specified)

|                     | PART NUMBER PACKAGE OUTLINE                                                             | UPB1004GS<br>S30 |                   |       |      |

|---------------------|-----------------------------------------------------------------------------------------|------------------|-------------------|-------|------|

| SYMBOLS             | PARAMETERS AND CONDITIONS                                                               | UNITS            | MIN               | TYP   | MAX  |

| Icc                 | Total Circuit Current, No Signals                                                       | mA               | 31.1              | 37.5  | 50.7 |

| RF Downco           | onverter Block (fRFin = 1575.42 MHz, f1stLOin = 1636.80 MH                              | Iz, PLOin = -10  | dBm, ZL = Zs = 50 | Ω)    | •    |

| Icc1                | Circuit Current 1, No Signals                                                           | mA               | 7.2               | 10    | 12.1 |

| CGRF                | RF Conversion Gain, PRFin = -40 dBm                                                     | dB               | 9.5               | 12.5  | 15.5 |

| NFRF                | RF SSB Noise Figure, PRFin = -40 dBm                                                    | dB               |                   | 12.5  | 15.5 |

| Po(sat)RF           | Maximum IF Output, PRFin = -10 dBm                                                      | dBm              | -8                | -5    | -2   |

| LOIF                | LO Leakage to IF Pin, fLoin = 1636.80 MHz                                               | dBm              |                   | -30   |      |

| LORF                | LO Leakage to RF Pin, fLoin = 1636.80 MHz                                               | dBm              |                   | -30   |      |

| IIP3RF              | Input 3rd Order Intercept Point, fRFin1 = 1600 MHz, fRFin2 = 1605 MHz, fLOin = 1570 MHz | dBm              |                   | -6    |      |

|                     | nverter Block (f1stlFin = 61.38 MHz, f2ndLOin = 65.472 MHz,                             |                  |                   |       |      |

| Icc2                | Circuit Current 2, No Signals                                                           | mA               | 2.7               | 3.8   | 4.7  |

| CGIF                | IF Conversion Gain at Max. Gain, P1stlFin = -50 dBm                                     | dB               | 37                | 40    | 43   |

| NFIF                | IF SSB Noise Figure at Max. Gain, P1stlFin = -50 dBm                                    | dB               | 12                | 15    | 18   |

| Po(sat)IF           | Maximum 2nd IF Output Level at Max. Gain,<br>P1stIFin = -20 dBm                         | dBm              | -3                | 0     | +3   |

| Vgc                 | Gain Control Voltage, Voltage at Max. Gain of CGIF                                      | V                |                   |       | 1.0  |

| Dgc                 | Gain Control Range                                                                      | dB               | 20                |       |      |

| LO <sub>2ndIF</sub> | D2ndIF LO Leakage to 2nd IF, f2ndL0in = 65.472 MHz                                      |                  |                   | -20   |      |

| LO1stIF             | LO Leakage to 1st IF, f2ndLOin = 65.472 MHz                                             | dBm              |                   | -40   |      |

|                     | Differ (f2ndIF= 4.092 MHz, Zs = 50 $\Omega$ , Zo = 2 k $\Omega$ )                       |                  |                   |       |      |

| Іссз                | Circuit Current 3, No Signals                                                           | mA               | 1.2               | 1.7   | 2.3  |

| S21                 | Gain  S <sub>21</sub>  , Z <sub>0</sub> = 1 M $\Omega$ // 27 pF                         | dB               | 37                | 40    | 43   |

| V2ndIFout           | Output Voltage, $Zo = 1M\Omega // 27 pF$                                                | mVp-p            | 600               |       |      |

| PLL Synthe          |                                                                                         | mA               |                   |       |      |

| ICC4                | , , , , , ,                                                                             |                  | 20                | 22    | 31.6 |

| fpD                 | 111 111                                                                                 |                  | 8.0               | 8.184 | 8.4  |

| VREFin              |                                                                                         |                  | 200               |       |      |

| VLP(H)              | Loop Filter Output Level (H)                                                            | V                | 2.8               |       |      |

| VLP(L)              | Loop Filter Output Level (L)                                                            | V                |                   |       | 0.4  |

| VREFout             | Reference Output Voltage, Zo = 1 M $\Omega$ // 27 pF                                    | VP-P             | 1.0               |       |      |

# ABSOLUTE MAXIMUM RATINGS<sup>1</sup> (TA = 25°C)

| SYMBOLS            | SYMBOLS PARAMETERS             |    | RATINGS     |  |  |  |

|--------------------|--------------------------------|----|-------------|--|--|--|

| Vcc Supply Voltage |                                | V  | 3.6         |  |  |  |

| Icc                | Circuit Current                | mA | 62          |  |  |  |

| Pp                 | Power Dissipation <sup>2</sup> | mW | 433         |  |  |  |

| Тор                | Operating Temperature          | °C | -40 to +85  |  |  |  |

| Тѕтс               | Storage Temperature            | °C | -55 to +150 |  |  |  |

#### Notes:

- 1. Operation in excess of any one of these parameters may result in permanent damage.

- 2. Mounted on a 50 x 50 x 1.6 mm double-sided copper clad epoxy glass PWB ( $T_A = +85^{\circ}C$ ).

# RECOMMENDED OPERATING CONDITIONS

| SYMBOLS                  | PARAMETERS                       | UNITS | MIN    | TYP     | MAX    |

|--------------------------|----------------------------------|-------|--------|---------|--------|

| Vcc                      | Supply Voltage                   | V     | 2.7    | 3.0     | 3.3    |

| Тор                      | Operating Temperature            | °C    | -40    | +25     | +85    |

| fRFin RF Input Frequency |                                  | MHz   |        | 1575.42 |        |

| f1stLOin                 | 1st LO Oscillating<br>Frequency  | MHz   | 1616.8 | 1636.8  | 1656.8 |

| f1stIFIN                 | 1st IF Input Frequency           | MHz   |        | 61.38   |        |

| f2ndLOin                 | 2nd LO Input Frequency           | MHz   |        | 65.472  |        |

| f2ndIFin<br>f2ndIFout    | 2nd IF Input/Output Frequency    | MHz   |        | 4.092   |        |

| fTCXOin<br>fTCXOout      | Reference Input/Output Frequency | MHz   |        | 16.368  |        |

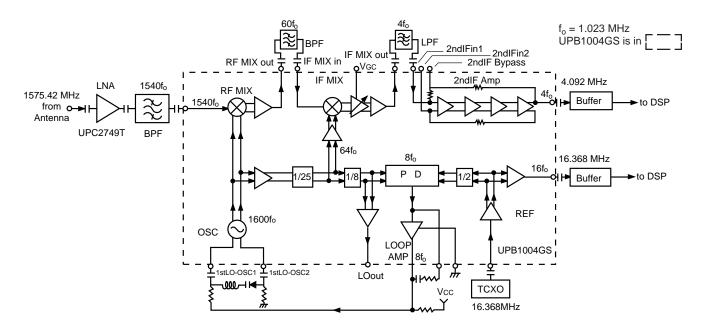

## **APPLICATION EXAMPLE**

#### **GPS Receiver RF Block**

Note: This diagram schematically shows only the UPB1004's internal functions on the system. This diagram does not represent the actual application circuit.

# **PIN FUNCTIONS**

| Pin No. | Symbol               | Applied<br>Voltage<br>(V)   | Pin<br>Voltage<br>(V)                      | Function and Application                                                                                                             | Internal Equivalent Circuit |

|---------|----------------------|-----------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| 3       | RF MIXout            | _                           | 1.68                                       | Output pin of RF mixer.<br>1st IF filter must be inserted<br>between pin 1 & 3.                                                      | 4<br>1st LO                 |

| 4       | Vcc (RF MIX)         | 2.7 to 3.3                  | _                                          | Supply voltage pin of RF mixer block. This pin must be decoupled with a capacitor (~1000 pF).                                        | -osc 3                      |

| 5       | RF MIXin             | _                           | 1.20                                       | Input pin of RF mixer.<br>1 575.42 MHz band pass filter<br>must be inserted between pin 5 and<br>external LNA.                       |                             |

| 6       | GND (RF MIX)         | GND                         | _                                          | Ground pin of RF mixer.                                                                                                              |                             |

| 7       | Vcc<br>(1stLO-OSC)   | 2.7 to 3.3                  | _                                          | Supply voltage pin of differential amplifier for 1st LO oscillator circuit.                                                          | VCC                         |

| 8       | 1stLO-OSC1           | _                           | 1.75                                       | Pins 8 & 9 are each base pins of the differential amplifier for 1st LO                                                               | Prescaler Input             |

| 9       | 1stLO-OSC2           | _                           | 1.75                                       | oscillator. These pins should be equipped with LC and varactor circuit to oscillate at 1636.8 MHz as VCO.                            | 8 9 7                       |

| 10      | GND<br>(1stLO-OSC)   | GND                         | _                                          | Ground pin of differential amplifier for 1st LO oscillator circuit.                                                                  | 10                          |

| 11      | Vcc (phase detector) | 2.7 to 3.3                  | _                                          | Supply voltage pin of phase detector and active loop filter.                                                                         |                             |

| 12      | PD-Vout3             | Pull-up<br>with<br>resistor |                                            | Pins of active loop filter for tuning VCO. The active transistors configured with darlington pair                                    | 11                          |

| 13      | PD-Vout2             | _                           | Output in accordance with phase difference | are built on-chip. Pin 14 should be pulled down with external resistor. Pin 12 to 13 should be equipped with external RC in order to | 13<br>PD 12                 |

| 14      | PD-Vout1             | GND                         |                                            | adjust damping factor and cutoff frequency. This tuning voltage output must be connected to varactor diode of 1st LO-OSC.            | 15 14                       |

| 15      | GND (phase detector) | GND                         | _                                          | Ground pin of phase detector and active loop filter.                                                                                 |                             |

| 16      | Vcc (divider block)  | 2.7 to 3.3                  | _                                          | Supply voltage pin of prescalers.                                                                                                    | (6) IF MIX PD PD            |

| 17      | LOout                | _                           | 1.98                                       | Monitor pin of comparison frequency at phase detector.                                                                               | 1st UO OSC +25 +8           |

| 18      | GND (divider block)  | GND                         |                                            | Ground pin of prescalers and LOout amplifier.                                                                                        | osc Ref.                    |

# **PIN FUNCTIONS**

| Pin No. | Symbol                | Applied<br>Voltage<br>(V) | Pin<br>Voltage<br>(V) | Function and Application                                                                                                       | Internal Equivalent Circuit              |

|---------|-----------------------|---------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 19      | TCXOin                | _                         | 1.97                  | Input pin of reference frequency. This pin should be equipped with external TCXO of 16.368 MHz.                                | 20                                       |

| 20      | Vcc (reference block) | 2.7 to 3.3                | _                     | Supply voltage pin of input/output amplifiers in reference block.                                                              | (19)                                     |

| 21      | TCXOout               | _                         | 1.75                  | Output pin of reference frequency. The frequency from pin 19 can be measured at 1 V <sub>P-P</sub> swing.                      | PD 18                                    |

| 22      | 2ndlFout              | _                         | 1.65                  | Output pin of 2nd IF amplifier. This output is a 4.092 MHz clipped sinewave.                                                   |                                          |

| 23      | Vcc<br>(2ndIF AMP)    | 2.7 to 3.3                | _                     | Supply voltage pin of 2nd IF amplifier.                                                                                        | 23 * * * * * * * * * * * * * * * * * * * |

| 24      | 2ndIF bypass          | _                         | 2.25                  | Bypass pin of 2nd IF amplifier input 1. This pin should be grounded through a capacitor.                                       | 24) 22                                   |

| 25      | 2ndlFin2              |                           | 2.25                  | Pin of 2nd IF amplifier input 2. This pin should be grounded through capacitor.                                                | 25 0 0 0                                 |

| 26      | 2ndlFin1              | _                         | 2.25                  | Pin of 2nd IF amplifier input 1. 2nd IF filter must be inserted between pins 26 & 28.                                          | (27)                                     |

| 27      | GND<br>(2ndIF AMP)    | GND                       | _                     | Ground pin of 2nd IF amplifier.                                                                                                |                                          |

| 28      | IF MIXout             |                           | 1.80                  | Output pin from IF mixer. IF mixer output signal goes through gain control amplifier before this emitter follower output port. | (30)                                     |

| 29      | Vgc (IF MIX)          | 0 to 3.3                  |                       | Gain control voltage pin of IF mixer output amplifier. This voltage performs forward control (Vcc up→Gain down).               |                                          |

| 30      | Vcc (IF MIX)          | 2.7 to 3.3                | _                     | Supply voltage pin of IF mixer, gain control amplifier and emitter follower transistor.                                        | 2nd Lo                                   |

| 1       | IF MIXin              | _                         | 1.18                  | Input pin of IF mixer.                                                                                                         | 1 -                                      |

| 2       | GND (IF MIX)          | GND                       | _                     | Ground pin of IF mixer.                                                                                                        |                                          |

Note: Ground pattern on the board must be formed as wide as possible to minimize ground impedance.

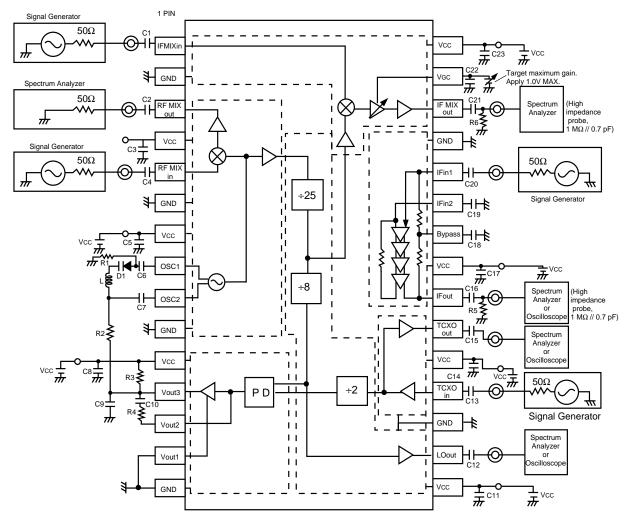

## **TEST CIRCUIT**

NOTE: Spectrum Analyzer to measure frequency. Oscilloscope to measure voltage swing.

#### **COMPONENTS LIST**

| FORM              | SYMBOL                                      | VALUE   |

|-------------------|---------------------------------------------|---------|

|                   | C1 to C5, C8, C11 to C15,C17, C18, C22, C23 | 1000 pF |

|                   | C6, C7                                      | 820 pF  |

| Chip Capacitor    | C9                                          | 6600 pF |

|                   | C19                                         | 9900 pF |

|                   | C10                                         | 0.2 μF  |

| Ceramic capacitor | C16, C20                                    | 0.1 μF  |

|                   | C21                                         | 0.01 μF |

|                   | R1, R2                                      | 15 kΩ   |

| Chip Resistor     | R3                                          | 1.5 kΩ  |

|                   | R4                                          | 3 kΩ    |

|                   | R5, R6                                      | 2 kΩ    |

| Varactor Diode    | D1                                          | _       |

| Chip Inductor     | L                                           | 1.57 nH |

|                   | I .                                         |         |

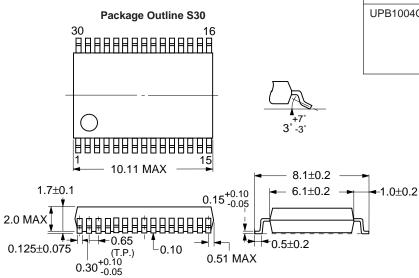

#### **OUTLINE DIMENSIONS** (Units in mm)

#### ORDERING INFORMATION

| Part Number  | Package             | Quantity and Form                                                                           |

|--------------|---------------------|---------------------------------------------------------------------------------------------|

| UPB1004GS-E1 | 30 Pin plastic SSOP | Embossed tape<br>16 mm wide.<br>Qty 2.5 kp/reel.<br>Pin 1 is in tape pull-out<br>direction. |

Note:

Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition.

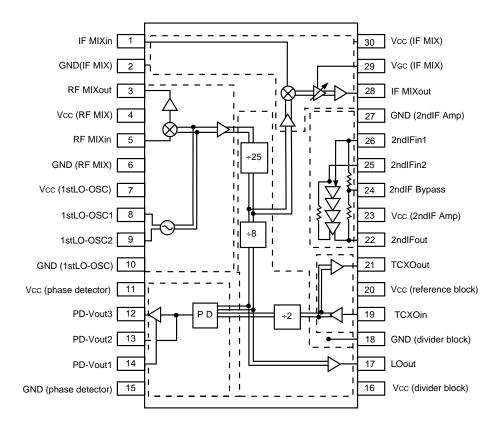

#### INTERNAL BLOCK DIAGRAM