Features

# 12V MOSFET Drivers with Output Disable

# for Single Phase Synchronous-Rectified Buck Converter

## General Description

The uP6281 is a dual, high voltage MOSFET driver optimized for driving two N-Channel MOSFETs in a synchronous-rectified buck converter. Each driver is capable of driving a 5000pF load with 30ns transition time. This device combined with uPI multi-phase buck PWM controller forms a complete core voltage regulator for advanced micro-processors.

The uP6281 features adaptive anti-shoot-through protection that prevents cross-conduction of the external MOSFET while maintains minimum deadtime for optimized efficiency.

Both gate drives are turned off by pulling low OD# pin or high-impedance at PWM pin, preventing rapid output capacitor discharge during system shutdowns.

Other feature is supply input under voltage lockout. The uP6281 is available in thermal enhanced PSOP-8L or WDFN3x3-8L packages.

### Applications

- Core Voltage Supplies for Desktop, Motherboard CPUs

- High Frequency Low Profile DC/DC Converters

- High Current Low Voltage DC/DC Converters

All-In-One Synchronous Buck Drivers

- Bootstrapped High-Side Driver

- Adaptive Anti-Shoot-Through Protection Circuitry

- 1 PWM Signal Generates both Drivers

- Tri-State Input for Bridge Shutdown

- Output Disable Control Turns Off both MOSFETs

- Under Voltage Lockout for Supply Input

- PSOP-8L or WDFN3x3-8L Packages

- RoHS Compliant and Halogen Free

### Ordering Information

| Order Number | Package Type | Remark |

|--------------|--------------|--------|

| uP6281ASU8   | PSOP - 8L    |        |

| uP6281ADD8   | WDFN3x3 - 8L |        |

Note: uPI products are compatible with the current IPC/ JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

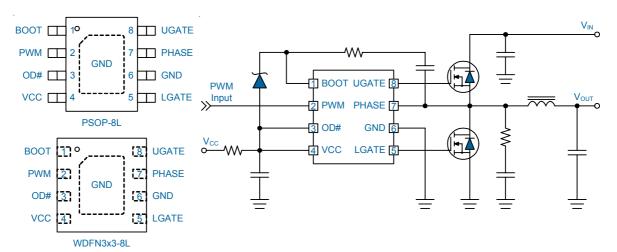

# Pin Configuration & Typical Application Circuit

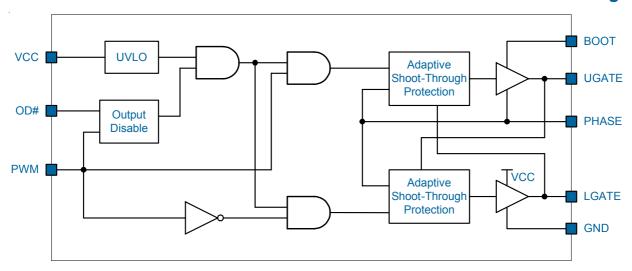

# Functional Block Diagram

# Functional Pin Description

| No. | Pin Name          | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | воот              | <b>Bootstrap Supply</b> for the floating upper gate driver. Connect the bootstrap capacitor $C_{\text{BOOT}}$ between BOOT pin and the PHASE pin to form a bootstrap circuit. The bootstrap capacitor provides the charge to turn on the upper MOSFET. Ensure that $C_{\text{BOOT}}$ is placed near the IC.                                                                                                                                    |

| 2   | PWM               | PWM Input. This pin receives logic level input and controls the driver outputs.                                                                                                                                                                                                                                                                                                                                                                |

| 3   | OD#               | Output Disable. This pin disables normal operation and forces both UGATE and LGATE off when it is pulled low.                                                                                                                                                                                                                                                                                                                                  |

| 4   | VCC               | <b>Supply Voltage for the IC.</b> This pin provides bias voltage for the IC. Connect this pin to 12V voltage source and bypass it with an R/C filter.                                                                                                                                                                                                                                                                                          |

| 5   | LGATE             | <b>Lower Gate Driver Output.</b> Connect this pin to the gate of lower MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry to determine when the lower MOSFET has turn off.                                                                                                                                                                                                                                       |

| 6   | GND               | Ground for the IC. All voltages levels are measured with respect to this pin.                                                                                                                                                                                                                                                                                                                                                                  |

| 7   | PHASE             | <b>PHASE Switch Node.</b> Connect this pin to the source of the upper MOSFET and the drain of the lower MOSFET. This pin is used as the sink for the UGATE driver. This pin is also monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off. A Schottky diode between this pin and ground is recommended to reduce negative transient voltage which is common in a power supply system. |

| 8   | UGATE             | <b>Upper Gate Driver Output.</b> Connect this pin to the gate of upper MOSFET. This pin is monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off.                                                                                                                                                                                                                                     |

|     | osed Pad<br>(GND) | <b>Ground for the IC.</b> The exposed pad should be well soldered to PCB for effective heat conduction.                                                                                                                                                                                                                                                                                                                                        |

## Functional Description

The uP6281 is a dual, high voltage MOSFET driver optimized for driving two N-Channel MOSFETs in a synchronous-rectified buck converter. Each driver is capable of driving a 5000pF load with 30ns transition time. This device combined with uPI multi-phase buck PWM controller forms a complete core voltage regulator for advanced microprocessors.

The uP6281 features adaptive anti-shoot-through protection that prevents cross-conduction of the external MOSFET while maintains minimum deadtime for optimized efficiency.

Both gate drives are turned off by pulling low OD# pin or high-impedance at PWM pin, preventing rapid output capacitor discharge during system shutdowns.

Other feature is supply input under voltage lockout. The uP6281 is available in thermal enhanced PSOP-8L or WDFN3x3-8L packages.

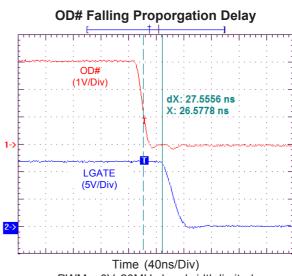

#### **Output Disable**

Logic low of OD# disables the gate drivers and keep both output low. Tie the OD# pin to controller power directly if the output disable function is not used.

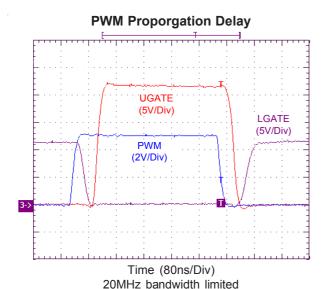

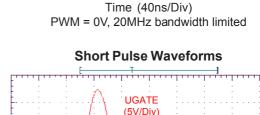

#### **PWM** Input

The PWM pin is a tri-state input. Logic high turns on the high-side gate driver and turns off the low side gate driver once the POR of VCC is granted and OD# is kept high. Logic low turns off the high side gate driver and turns off the low side gate driver.

High impedance input at PWM pin will keep both high-side and low-side gate drivers low and turns off both MOSFETs. The PWM pin voltage is kept around 2.0V by internal bias resistors when floating.

#### **Low Side Driver**

The low-side driver is designed to drive a ground-referenced N-Channel MOSFET. The bias to the low-side driver is internally connected to VCC supply and GND. The low-side driver output is out of phase with the PWM input when it is enabled. The low side driver is held low if the OD# pin is pulled low or high-impedance at PWM pin.

#### **High-Side Driver**

The high-side driver is designed to drive a floating N-Channel MOSFET. The bias voltage to the high-side driver internally connected to BOOT and PHASE pins. An external bootstrap supply circuit that is connected between BOOT and PHASE pins provides the bias current for the high-side gate driver.

The bootstrap capacitor  $C_{\rm BOOT}$  is charged to  $V_{\rm CC}$  when PHASE pin is grounded by turning on the low-side MOSFET. The PHASE raises to  $V_{\rm IN}$  when the high-side MOSFET is turned on, forcing the BOOT pin voltage to  $V_{\rm IN}$  +  $V_{\rm CC}$  that provides voltage to hold the high-side MOSFET on.

The high-side gate driver output is in phase with the PWM input when it is enabled. The high-side driver is held low if the OD# pin is pulled low or high-impedance at PWM pin.

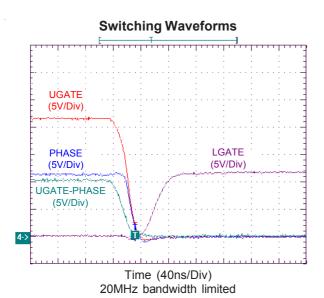

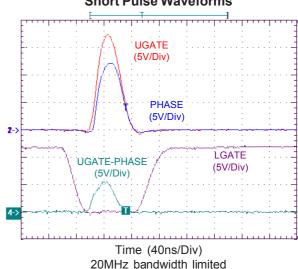

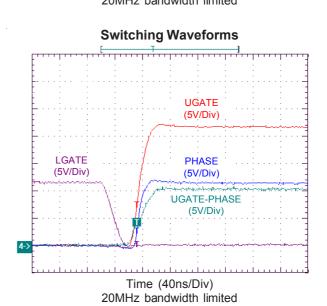

#### **Adaptive Shoot Through Protection**

The adaptive shoot-through circuit prevents the high-side and low-side MOSFETs from being ON simultaneously and conducting destructive large current. It is done by turning on one MOSFET only after the other MOSFET is off already with adequately delay time.

At the high-side off edge, UGATE and PHASE voltages are monitored for anti-shoot-through protection. The uP6281 will not begin to output low-side driver high until both (V $_{\rm UGATE}$  - V $_{\rm PHASE}$ ) and V $_{\rm PHASE}$  are lower than 1.2V, making sure the high-side MOSFET is turned off completely.

At the low-side off edge, LGATE voltage is monitored for anti-shoot-through protection. The uP6281 will not begin to output high-side driver high until  $V_{\text{LGATE}}$  is lower than 1.2V, making sure the low-side MOSFET is turned off completely.

|                                                   |                    | Ab                           | solute Ma   | aximu  | ım R      | ating    |  |  |

|---------------------------------------------------|--------------------|------------------------------|-------------|--------|-----------|----------|--|--|

| Supply Input Voltage, VCC12 (N                    | lote 1)            |                              |             |        | 0.3V      | to +15V  |  |  |

| BOOT to PHASE                                     |                    |                              |             |        | 0.3V      | to +15V  |  |  |

| PHASE to GND                                      |                    |                              |             |        |           |          |  |  |

|                                                   |                    |                              |             |        |           |          |  |  |

|                                                   |                    |                              |             |        | 8\        | / to 30V |  |  |

| BOOT to GND                                       |                    |                              |             |        |           |          |  |  |

| DC<                                               |                    |                              |             |        |           |          |  |  |

|                                                   |                    |                              |             |        | 0.3\      | / to 42V |  |  |

| UGATE to PHASE                                    |                    |                              | 0.014       | (DOOT  | 5114.05   |          |  |  |

|                                                   |                    |                              |             |        |           |          |  |  |

|                                                   |                    |                              | 5V to (I    | BOOT - | PHASE     | + 0.3V)  |  |  |

| LGATE to GND                                      |                    |                              | 0           | 0) (1  | 0.10040   |          |  |  |

|                                                   |                    |                              |             |        | •         |          |  |  |

|                                                   |                    |                              |             |        |           |          |  |  |

|                                                   |                    |                              |             |        |           |          |  |  |

|                                                   |                    |                              |             |        | `         | ,        |  |  |

|                                                   |                    |                              |             |        |           |          |  |  |

| •                                                 |                    |                              |             |        |           |          |  |  |

| Lead Temperature (Soldering, 10                   | sec)               |                              |             |        |           | -260°C   |  |  |

| ESD Rating (Note 2)                               |                    |                              |             |        |           |          |  |  |

| ` ,                                               |                    |                              |             |        |           |          |  |  |

| MM (Machine Mode)                                 |                    |                              |             |        |           | 200V     |  |  |

|                                                   |                    |                              | Thern       | nal In | form      | ation    |  |  |

| Package Thermal Resistance (                      |                    |                              |             |        |           |          |  |  |

| PSOP-8 θ <sub>.IA</sub>                           |                    |                              |             |        |           | 50°C/W   |  |  |

| WDFN3x3-8L θ <sub>JA</sub>                        |                    |                              |             |        |           | 68°C/W   |  |  |

|                                                   |                    |                              |             |        |           |          |  |  |

| WDFN3x3-8L θ <sub>IC</sub>                        |                    |                              |             |        |           | 6°C/W    |  |  |

| Power Dissipation, $P_D @ T_A = 2$                | 5°C                |                              |             |        |           |          |  |  |

| PSOP-8L                                           |                    |                              |             |        |           | - 2.0W   |  |  |

| WDFN3x3-8L                                        |                    |                              |             |        |           | 1.47W    |  |  |

|                                                   |                    | Recommende                   | ed Operat   | ion C  | ondi      | tions    |  |  |

| Operating Junction Temperature                    | - Range (No        | te 4)                        | -           |        |           |          |  |  |

| . •                                               | <b>O</b> (         |                              |             |        |           |          |  |  |

|                                                   | -                  |                              |             |        |           |          |  |  |

| Supply input voitage, v <sub>cc</sub>             |                    |                              |             |        | + 10.6V t | U 13.2V  |  |  |

|                                                   |                    | E                            | lectrical ( | Chara  | cteri     | stics    |  |  |

| $(V_{CC} = 12V, T_A = 25^{\circ}C, unless other)$ | nerwise spec       | ified)                       |             |        |           |          |  |  |

| Parameter                                         | Symbol             | Test Conditions              | Min         | Тур    | Max       | Unit     |  |  |

| Supply Input                                      |                    |                              |             |        |           |          |  |  |

| Supply Input Voltage                              | V <sub>cc</sub>    |                              | 10.8        |        | 13.2      | V        |  |  |

| Supply Input Current                              | I <sub>cc</sub>    | PWM = OD# = 0V, each channel |             | 1      | 2.5       | mA       |  |  |

| VCC POR Rising Threshold                          | V <sub>CCRTH</sub> | V <sub>cc</sub> rising       | 4.0         | 4.2    | 4.4       | V        |  |  |

| VCC POR Hysteresis                                | V <sub>CCHYS</sub> |                              |             | 0.25   |           | V        |  |  |

|                                                   | COULD              |                              |             |        |           |          |  |  |

## Electrical Characteristics

| Parameter                   | Symbol                | Test Conditions                                                          | Min  | Тур  | Max  | Unit |

|-----------------------------|-----------------------|--------------------------------------------------------------------------|------|------|------|------|

| PWM Input                   |                       |                                                                          |      |      |      |      |

| Input High Threshold        | PWM <sub>RTH</sub>    |                                                                          | 3.15 | 3.45 | 3.75 | V    |

| Input Low Threshold         | PWM <sub>FTH</sub>    |                                                                          | 0.6  | 0.9  | 1.2  | V    |

| PWM Floating Voltage        | PWM <sub>FLT</sub>    |                                                                          |      | 2.0  |      | V    |

| DWWW 100 1                  | I <sub>PWM</sub>      | PWM = 0V                                                                 | -420 | -280 | -140 | uA   |

| PWM Input Current           |                       | PWM = 5V                                                                 | 1.0  | 1.6  | 1.9  | mA   |

| Output Disable Input OD#    |                       |                                                                          | -    |      | ı    |      |

| Input High                  | OD# <sub>H</sub>      |                                                                          | 2.6  |      |      | V    |

| Input Low                   | OD# <sub>L</sub>      |                                                                          |      |      | 8.0  | V    |

| OD# Input Current           | l <sub>OD#</sub>      | OD# = 0V to 5V                                                           | -1   |      | 1    | uA   |

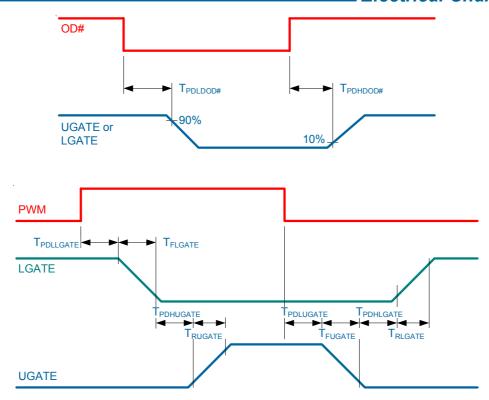

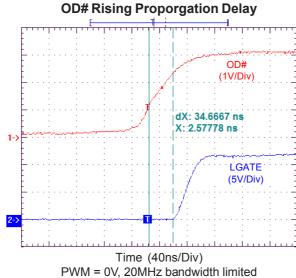

| Dranagation Dalay Time      | T <sub>PDHOD#</sub>   |                                                                          |      | 20   | 45   | ns   |

| Propogation Delay Time      | T <sub>PDLOD#</sub>   |                                                                          |      | 20   | 45   | ns   |

| High Side Driver            |                       |                                                                          |      |      |      |      |

| Output Resistance, Sourcing | R <sub>H_SRC</sub>    | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V, I <sub>UGATE</sub> = -80mA |      | 1.2  | 2.4  | Ω    |

| Output Resistance, Sinking  | R <sub>H_SNK</sub>    | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V, I <sub>UGATE</sub> = 80mA  |      | 0.8  | 1.6  | Ω    |

| Output Rising Time          | T <sub>RUGATE</sub>   | $V_{BOOT} - V_{PHASE} = 12V, C_{LOAD} = 3nF$                             |      | 35   | 45   | ns   |

| Output Falling Time         | T <sub>FUGATE</sub>   | $V_{BOOT} - V_{PHASE} = 12V, C_{LOAD} = 3nF$                             |      | 20   | 30   | ns   |

| Drangation Daloy Time       | T <sub>PDHUGATE</sub> | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V                             |      | 40   | 65   | ns   |

| Propogation Delay Time      | T <sub>PDLUGATE</sub> | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 12V                             |      | 20   | 35   | ns   |

| Low Side Driver             |                       |                                                                          |      |      |      |      |

| Output Resistance, Sourcing | R <sub>L_SRC</sub>    | V <sub>CC</sub> = 12V, I <sub>LGATE</sub> = -80mA                        |      | 1.2  | 2.4  | Ω    |

| Output Resistance, Sinking  | R <sub>L_SNK</sub>    | V <sub>CC</sub> = 12V, I <sub>LGATE</sub> = 80mA                         |      | 0.8  | 1.6  | Ω    |

| Output Rising Time          | T <sub>RLGATE</sub>   | V <sub>CC</sub> = 12V, C <sub>LOAD</sub> = 3nF                           |      | 35   | 45   | ns   |

| Output Falling Time         | T <sub>FLGATE</sub>   | V <sub>CC</sub> = 12V, C <sub>LOAD</sub> = 3nF                           |      | 20   | 30   | ns   |

| Drangation Dalay Time       | T <sub>PDHLGATE</sub> | V <sub>CC</sub> = 12V                                                    |      | 40   | 65   | ns   |

| Propogation Delay Time      |                       | V <sub>CC</sub> = 12V                                                    |      | 20   | 35   | ns   |

### **Electrical Characteristics**

**Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precaution recommended.

- **Note 3.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}$ C on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# **Typical Operation Characteristics**

## Application Information

The power dissipation in uP6281 is dependent of the supply voltage, the PWM frequency and the input capacitance of the MOSFET:

### P<sub>LOSS</sub>

$$= V_{CC} \{I_{CC} + [V_{CC}(C_{ISS\_U} + C_{ISS\_L}) + V_{IN} \times C_{OSS\_U}]f_{PWM}\}$$

where V $_{\rm CC}$  is the supply voltage, I $_{\rm CC}$  is the operation current of the control circuit, C $_{\rm ISS\_U}$  and C $_{\rm ISS\_L}$  are the total input capacitance of the upper and lower MOSFET respectively, V $_{\rm IN}$  is the supply voltage of the buck converter, C $_{\rm OSS\_U}$  is the reverse transfer capacitance regarding the Miller effect and f $_{\rm PWM}$  is the PWM input frequency. Take a typical case for example, V $_{\rm CC}$  = 12V, I $_{\rm CC}$  = 1mA, C $_{\rm ISS\_U}$  = 2x1.5nF, C $_{\rm OSS\_U}$  = 2x0.1nF, V $_{\rm IN}$  = 12V, CISS $_{\rm L}$  = 2x3nF, f $_{\rm OSC}$  = 300kHz, the power dissipation is calculated as:

### $P_{LOSS}$

$= 12V\{1mA + [12V(3nF + 6nF) + 12V \times 0.2nF]300kHz\}$

= 0.41W

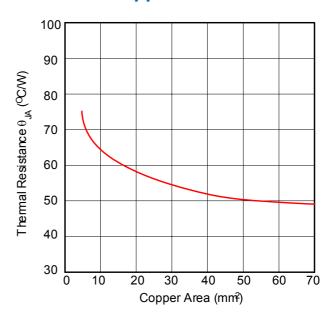

The uP6281 is available in thermal enhanced PSOP-8L or WDFN3x3-8L packages. However, the thermal resistance  $\theta_{JA}$  still highly depends on the PCB design. Copper plane under the exposed pad is an effective heatsink and is useful for improving thermal conductivity. Figure 1 shows the relationship between thermal resistance  $\theta_{JA}$  of PSOP-8L package vs. copper area on a standard JEDEC 51-7 (4 layers, 2S2P) thermal test board at  $T_{A}$  = 25°C. A 50mm² copper plane reduces  $\theta_{JA}$  from 75°C/W to 50°C/W.

Figure 1. Thermal Resistance  $\theta_{JA}$  vs. Copper Area Take the above case for example, 0.41W power loss will cause 0.41W x 50°C/W = 20.5°C temperature raise with 50mm2 copper area.

## Package Information

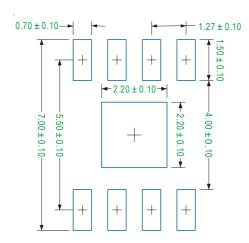

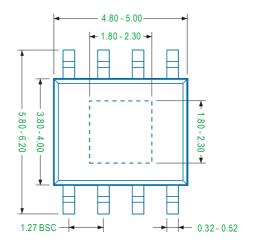

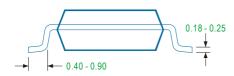

### PSOP-8 Package

#### Recommended Solder Pad Layout

#### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions no not include mold flash or protrusions. Mold flash or protrusions shell not exceed 0.15mm.

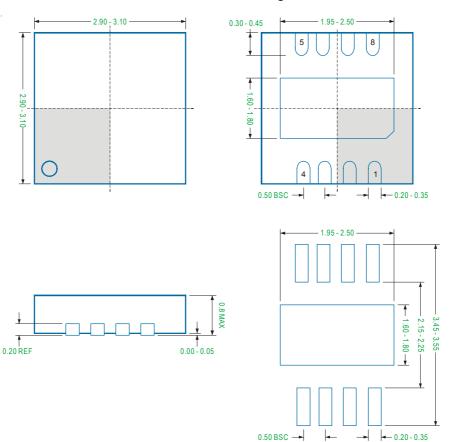

## . Package Information

#### WDFN3x3-8L Package

Recommended Solder Pitch and Dimensions

### Note

1. Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

- 2. Dimensions in Millimeters.

- 3. Drawing not to scale.

- 4. These dimensions no not include mold flash or protrusions. Mold flash or protrusions shell not exceed 0.15mm.