# **UJA1075A**

## High-speed CAN/LIN core system basis chip

Rev. 02 — 28 January 2011

**Product data sheet**

## 1. General description

The UJA1075A core System Basis Chip (SBC) replaces the basic discrete components commonly found in Electronic Control Units (ECU) with a high-speed Controller Area Network (CAN) and a Local Interconnect Network (LIN) interface.

The UJA1075A supports the networking applications used to control power and sensor peripherals by using a high-speed CAN as the main network interface and the LIN interface as a local sub-bus.

The core SBC contains the following integrated devices:

- High-speed CAN transceiver, inter-operable and downward compatible with CAN transceiver TJA1042, and compatible with the ISO 11898-2 and ISO 11898-5 standards

- LIN transceiver compliant with LIN 2.1, LIN 2.0 and SAE J2602, and compatible with LIN 1.3

- Advanced independent watchdog (UJA1075A/xx/WD versions)

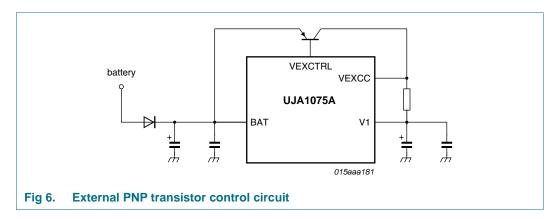

- 250 mA voltage regulator for supplying a microcontroller; extendable with external PNP transistor for increased current capability and dissipation distribution

- Separate voltage regulator for supplying the on-board CAN transceiver

- Serial Peripheral Interface (SPI) (full duplex)

- 2 local wake-up input ports

- Limp home output port

In addition to the advantages gained from integrating these common ECU functions in a single package, the core SBC offers an intelligent combination of system-specific functions such as:

- Advanced low-power concept

- · Safe and controlled system start-up behavior

- Detailed status reporting on system and sub-system levels

The UJA1075A is designed to be used in combination with a microcontroller that incorporates a CAN controller. The SBC ensures that the microcontroller always starts up in a controlled manner.

#### High-speed CAN/LIN core system basis chip

#### 2. Features and benefits

#### 2.1 General

- Contains a full set of CAN and LIN ECU functions:

- CAN transceiver and LIN transceiver

- ◆ Scalable 3.3 V or 5 V voltage regulator delivering up to 250 mA for a microcontroller and peripheral circuitry; an external PNP transistor can be connected for better heat distribution over the PCB

- Separate voltage regulator for the CAN transceiver (5 V)

- Watchdog with Window and Timeout modes and on-chip oscillator

- Serial Peripheral Interface (SPI) for communicating with the microcontroller

- ◆ ECU power management system

- Designed for automotive applications:

- Enhanced ElectroMagnetic Compatibility (EMC) performance

- ◆ ±8 kV ElectroStatic Discharge (ESD) protection Human Body Model (HBM) on the CAN/LIN bus pins and the wake-up pins

- ◆ ±6 kV ElectroStatic Discharge protection IEC 61000-4-2 on the CAN/LIN bus pins and the wake-up pins

- ±58 V short-circuit proof CAN/LIN bus pins

- Battery and CAN/LIN bus pins are protected against transients in accordance with ISO 7637-3

- Supports remote flash programming via the CAN bus

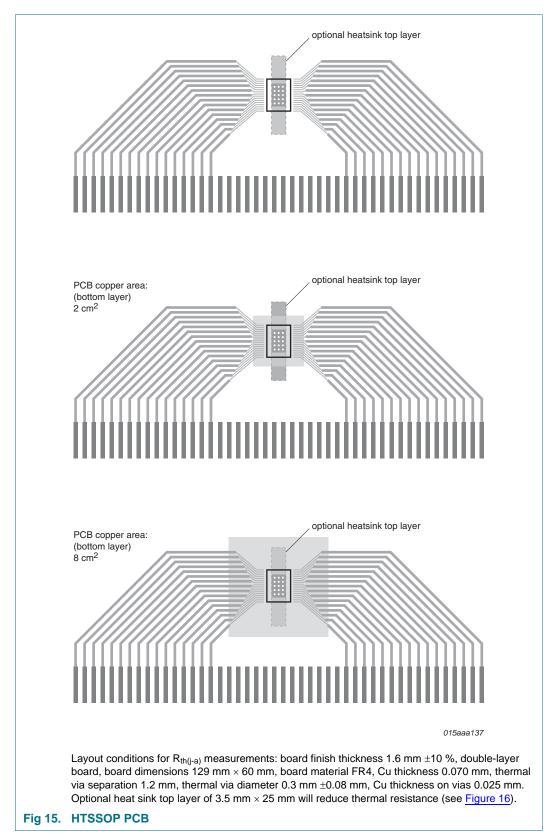

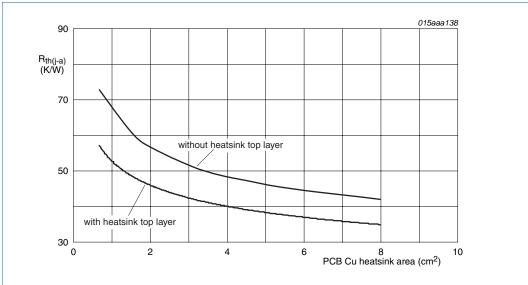

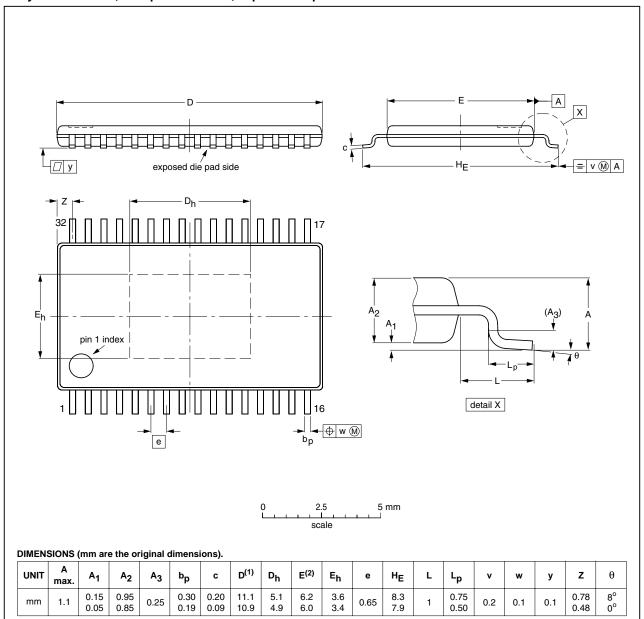

- Small 6.1 mm × 11 mm HTSSOP32 package with low thermal resistance

- Pb-free; Restriction of Hazardous Substances Directive (RoHS) and dark green compliant

#### 2.2 CAN transceiver

- ISO 11898-2 and ISO 11898-5 compliant high-speed CAN transceiver

- Dedicated low dropout voltage regulator for the CAN bus:

- Independent of the microcontroller supply

- Significantly improves EMC performance

- Bus connections are truly floating when power is off

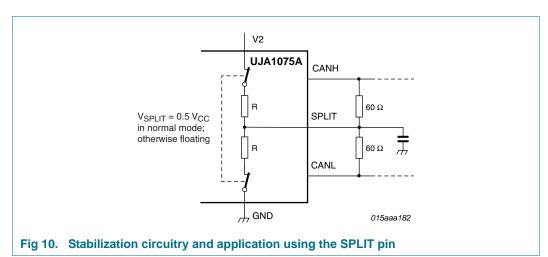

- SPLIT output pin for stabilizing the recessive bus level

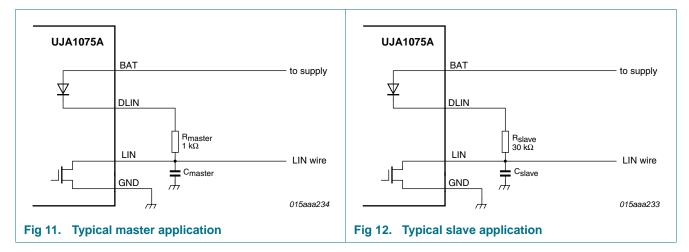

#### 2.3 LIN transceiver

- LIN 2.1 compliant LIN transceiver

- Compliant with SAE J2602

- Downward compatible with LIN 2.0 and LIN 1.3

- Low slope mode for optimized EMC performance

- Integrated LIN termination diode at pin DLIN

### 2.4 Power management

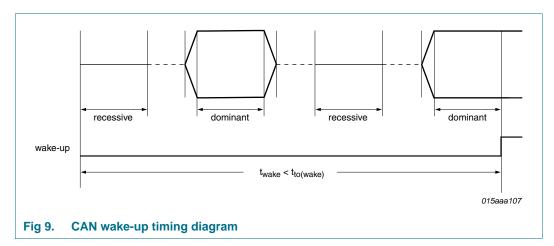

- Wake-up via CAN, LIN or local wake-up pins with wake-up source detection

- 2 wake-up pins:

UJA1075A

#### High-speed CAN/LIN core system basis chip

- WAKE1 and WAKE2 inputs can be switched off to reduce current flow

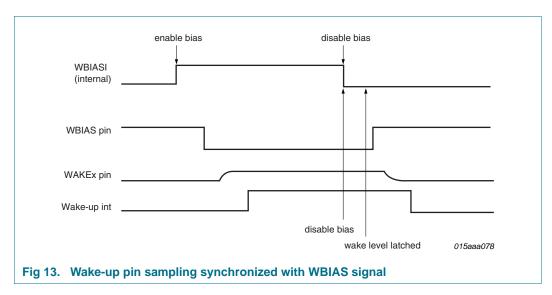

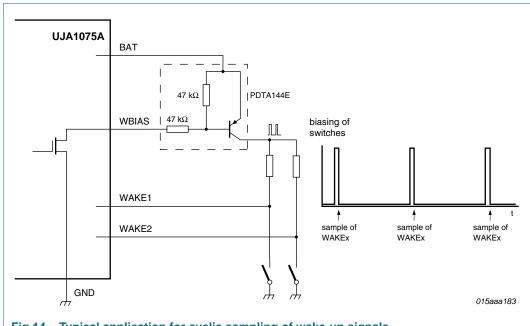

- Output signal (WBIAS) to bias the wake-up pins, selectable sampling time of 16 ms or 64 ms

- Standby mode with very low standby current and full wake-up capability; V1 active to maintain supply to the microcontroller

- Sleep mode with very low sleep current and full wake-up capability

#### 2.5 Control and diagnostic features

- Safe and predictable behavior under all conditions

- Programmable watchdog with independent clock source:

- Window, Timeout (with optional cyclic wake-up) and Off modes supported (with automatic re-enable in the event of an interrupt)

- 16-bit Serial Peripheral Interface (SPI) for configuration, control and diagnosis

- Global enable output for controlling safety-critical hardware

- Limp home output (LIMP) for activating application-specific 'limp home' hardware in the event of a serious system malfunction

- Overtemperature shutdown

- Interrupt output pin; interrupts can be individually configured to signal V1/V2 undervoltage, CAN/LIN/local wake-up and cyclic and power-on interrupt events

- Bidirectional reset pin with variable power-on reset length to support a variety of microcontrollers

- Software-initiated system reset

#### 2.6 Voltage regulators

- Main voltage regulator V1:

- Scalable voltage regulator for the microcontroller, its peripherals and additional external transceivers

- ±2 % accuracy

- ◆ 3.3 V and 5 V versions available

- Delivers up to 250 mA and can be combined with an external PNP transistor for better heat distribution over the PCB

- Selectable current threshold at which the external PNP transistor starts to deliver current

- Undervoltage warning at 90 % of nominal output voltage and undervoltage reset at 90 % or 70 % of nominal output voltage

- ◆ Can operate at V<sub>BAT</sub> voltages down to 4.5 V (e.g. during cranking), in accordance with ISO 7637 pulse 4/4b and ISO 16750-2

- Stable output under all conditions

- Voltage regulator V2 for CAN transceiver:

- Dedicated voltage regulator for on-chip high-speed CAN transceiver

- Undervoltage warning at 90 % of nominal output voltage

- Can be switched off; CAN transceiver can be supplied by V1 or by an external voltage regulator

- Can operate at V<sub>BAT</sub> voltages down to 5.5 V (e.g. during cranking) in accordance with ISO 7637, pulse 4

- Stable output under all conditions

### High-speed CAN/LIN core system basis chip

## 3. Ordering information

Table 1. Ordering information

| Type number[1]    | Package  | <sup>o</sup> ackage                                                                                                          |          |  |  |  |  |

|-------------------|----------|------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|

|                   | Name     | Description                                                                                                                  | Version  |  |  |  |  |

| UJA1075ATW/5V0/WD | HTSSOP32 | plastic thermal enhanced thin shrink small outline package; 32 leads; body width 6.1 mm; lead pitch 0.65 mm; exposed die pad | SOT549-1 |  |  |  |  |

| UJA1075ATW/3V3/WD |          |                                                                                                                              |          |  |  |  |  |

| UJA1075ATW/5V0    |          |                                                                                                                              |          |  |  |  |  |

| UJA1075ATW/3V3    |          |                                                                                                                              |          |  |  |  |  |

<sup>[1]</sup> UJA1075ATW/5V0xx versions contain a 5 V regulator (V1); UJA1075ATW/3V3xx versions contain a 3.3 V regulator (V1); WD versions contain a watchdog.

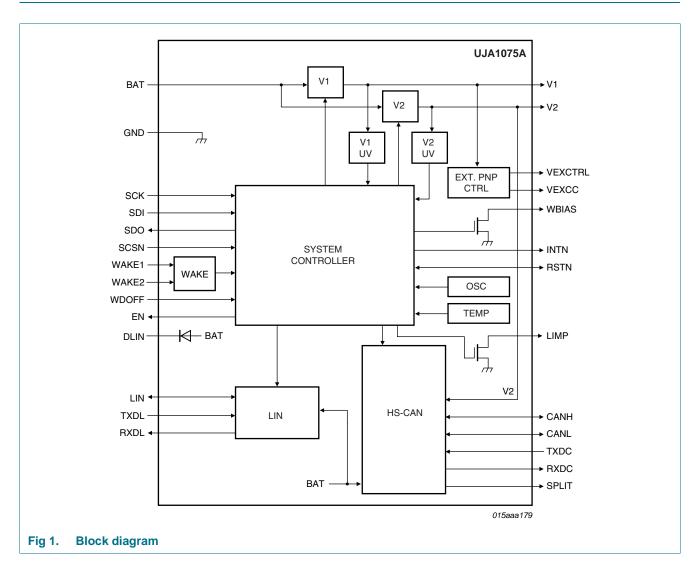

## 4. Block diagram

## High-speed CAN/LIN core system basis chip

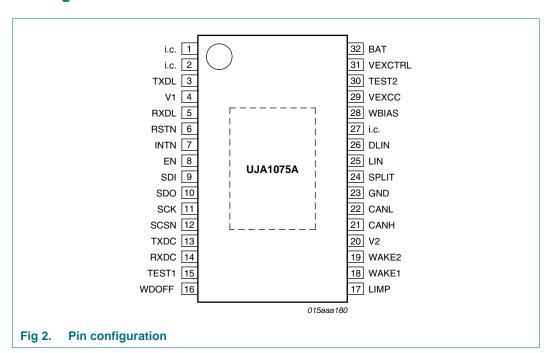

## 5. Pinning information

### 5.1 Pinning

## 5.2 Pin description

Table 2. Pin description

|        | 4000 | · · · · · · · · · · · · · · · · · · ·                                                    |

|--------|------|------------------------------------------------------------------------------------------|

| Symbol | Pin  | Description                                                                              |

| i.c.   | 1    | internally connected; should be left floating                                            |

| i.c.   | 2    | internally connected; should be left floating                                            |

| TXDL   | 3    | LIN transmit data input                                                                  |

| V1     | 4    | voltage regulator output for the microcontroller (5 V or 3.3 V depending on SBC version) |

| RXDL   | 5    | LIN receive data output                                                                  |

| RSTN   | 6    | reset input/output to and from the microcontroller                                       |

| INTN   | 7    | interrupt output to the microcontroller                                                  |

| EN     | 8    | enable output                                                                            |

| SDI    | 9    | SPI data input                                                                           |

| SDO    | 10   | SPI data output                                                                          |

| SCK    | 11   | SPI clock input                                                                          |

| SCSN   | 12   | SPI chip select input                                                                    |

| TXDC   | 13   | CAN transmit data input                                                                  |

| RXDC   | 14   | CAN receive data output                                                                  |

| TEST1  | 15   | test pin; pin should be connected to ground                                              |

| WDOFF  | 16   | WDOFF pin for deactivating the watchdog                                                  |

| LIMP   | 17   | limp home output                                                                         |

#### High-speed CAN/LIN core system basis chip

Table 2. Pin description ...continued

| Symbol  | Pin | Description                                                                                                            |

|---------|-----|------------------------------------------------------------------------------------------------------------------------|

| WAKE1   | 18  | local wake-up input 1                                                                                                  |

| WAKE2   | 19  | local wake-up input 2                                                                                                  |

| V2      | 20  | 5 V voltage regulator output for CAN                                                                                   |

| CANH    | 21  | CANH bus line                                                                                                          |

| CANL    | 22  | CANL bus line                                                                                                          |

| GND     | 23  | ground                                                                                                                 |

| SPLIT   | 24  | CAN bus common mode stabilization output                                                                               |

| LIN     | 25  | LIN bus line                                                                                                           |

| DLIN    | 26  | LIN termination resistor connection                                                                                    |

| i.c.    | 27  | internally connected; should be left floating                                                                          |

| WBIAS   | 28  | control pin for external wake biasing transistor                                                                       |

| VEXCC   | 29  | current measurement for external PNP transistor; this pin is connected to the collector of the external PNP transistor |

| TEST2   | 30  | test pin; pin should be connected to ground                                                                            |

| VEXCTRL | 31  | control pin of the external PNP transistor; this pin is connected to the base of the external PNP transistor           |

| BAT     | 32  | battery supply for the SBC                                                                                             |

|         |     |                                                                                                                        |

The exposed die pad at the bottom of the package allows for better heat dissipation from the SBC via the printed-circuit board. The exposed die pad is not connected to any active part of the IC and can be left floating, or can be connected to GND.

## 6. Functional description

The UJA1075A combines the functionality of a high-speed CAN transceiver, a LIN transceiver, two voltage regulators and a watchdog (UJA1075A/xx/WD versions) in a single, dedicated chip. It handles the power-up and power-down functionality of the ECU and ensures advanced system reliability. The SBC offers wake-up by bus activity, by cyclic wake-up and by the activation of external switches. Additionally, it provides a periodic control signal for pulsed testing of wake-up switches, allowing low-current operation even when the wake-up switches are closed in Standby mode.

All transceivers are optimized to be highly flexible with regard to bus topologies. In particular, the high-speed CAN transceiver is optimized to reduce ringing (bus reflections).

V1, the main voltage regulator, is designed to power the ECU's microcontroller, its peripherals and additional external transceivers. An external PNP transistor can be added to improve heat distribution. V2 supplies the integrated high-speed CAN transceiver. The watchdog is clocked directly by the on-chip oscillator and can be operated in Window, Timeout and Off modes.

### High-speed CAN/LIN core system basis chip

## 6.1 System Controller

### 6.1.1 Introduction

The system controller manages register configuration and controls the internal functions of the SBC. Detailed device status information is collected and presented to the microcontroller. The system controller also provides the reset and interrupt signals.

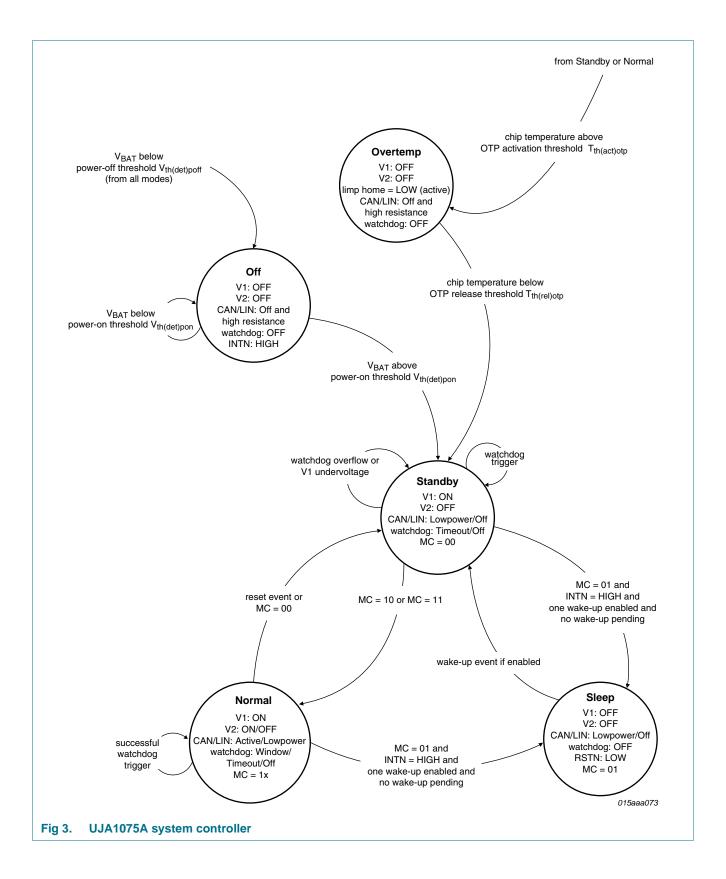

The system controller is a state machine. The SBC operating modes, and how transitions between modes are triggered, are illustrated in <u>Figure 3</u>. These modes are discussed in more detail in the following sections.

#### High-speed CAN/LIN core system basis chip

#### High-speed CAN/LIN core system basis chip

#### 6.1.2 Off mode

The SBC switches to Off mode from all other modes if the battery supply drops below the power-off detection threshold ( $V_{th(det)poff}$ ). In Off mode, the voltage regulators are disabled and the bus systems are in a high-resistive state. The CAN bus pins are floating in this mode.

As soon as the battery supply rises above the power-on detection threshold ( $V_{th(det)pon}$ ), the SBC goes to Standby mode, and a system reset is executed (reset pulse width of  $t_{w(rst)}$ , long or short; see Section 6.5.1 and Table 11).

#### 6.1.3 Standby mode

The SBC will enter Standby mode:

- From Off mode if V<sub>BAT</sub> rises above the power-on detection threshold (V<sub>th(det)pon</sub>)

- From Sleep mode on the occurrence of a CAN, LIN or local wake-up event

- From Overtemp mode if the chip temperature drops below the overtemperature protection release threshold, T<sub>th(rel)otp</sub>

- From Normal mode if bit MC is set to 00 or a system reset is performed (see Section 6.5)

In Standby mode, V1 is switched on. The CAN and LIN transceivers will either be in a low-power state (Lowpower mode; STBCC/STBCL = 1; see <u>Table 6</u>) with bus wake-up detection enabled or completely switched off (Off mode; STBCC/STBCL = 0) - see <u>Section 6.7.1</u> and <u>Section 6.8.1</u>. The watchdog can be running in Timeout mode or Off mode, depending on the state of the WDOFF pin and the setting of the watchdog mode control bit (WMC) in the WD\_and\_Status register (Table 4).

The SBC will exit Standby mode if:

- Normal mode is selected by setting bits MC to 10 (V2 disabled) or 11 (V2 enabled)

- Sleep mode is selected by setting bits MC to 01

- The chip temperature rises above the OverTemperature Protection (OTP) activation threshold, T<sub>th(act)otp</sub>, causing the SBC to enter Overtemp mode

#### 6.1.4 Normal mode

Normal mode is selected from Standby mode by setting bits MC in the Mode\_Control register (Table 5) to 10 (V2 disabled) or 11 (V2 enabled).

In Normal mode, the CAN physical layer will be enabled (Active mode; STBCC = 0; see <u>Table 6</u>) or in a low-power state (Lowpower mode; STBCC = 1) with bus wake-up detection active.

In Normal mode, the LIN physical layer will be enabled (Active mode; STBCL = 0; see <u>Table 6</u>) or in a low-power state (Lowpower mode; STBCL = 1) with bus wake-up detection active.

The SBC will exit Normal mode if:

- Standby mode is selected by setting bits MC to 00

- Sleep mode is selected by setting bits MC to 01

- A system reset is generated (see <u>Section 6.1.3</u>; the SBC will enter Standby mode)

#### High-speed CAN/LIN core system basis chip

The chip temperature rises above the OTP activation threshold, T<sub>th(act)otp</sub>, causing the SBC to switch to Overtemp mode

#### 6.1.5 Sleep mode

Sleep mode is selected from Standby mode or Normal mode by setting bits MC in the Mode\_Control register (Table 5) to 01. The SBC will enter Sleep mode providing there are no pending interrupts (pin INTN = HIGH) or wake-up events and at least one wake-up source is enabled (CAN, LIN or WAKE). Any attempt to enter Sleep mode while one of these conditions has not been satisfied will result in a short reset (3.6 ms minimum pulse width; see Section 6.5.1 and Table 11).

In Sleep mode, V1 and V2 are off and the bus transceivers will be switched off (Off mode; STBCC/STBCL = 0; see <u>Table 6</u>) or in a low-power state (Lowpower mode; STBCC/STBCL = 1) with bus wake-up detection active - see <u>Section 6.7.1</u> and <u>Section 6.8.1</u>). The watchdog is off and the reset pin is LOW.

A CAN, LIN or local wake-up event will cause the SBC to switch from Sleep mode to Standby mode, generating a (short or long; see Section 6.5.1) system reset. The value of the mode control bits (MC) will be changed to 00 and V1 will be enabled.

#### 6.1.6 Overtemp mode

The SBC will enter Overtemp mode from Normal mode or Standby mode when the chip temperature exceeds the overtemperature protection activation threshold,  $T_{th(act)otp}$ ,

In Overtemp mode, the voltage regulators are switched off and the bus systems are in a high-resistive state. When the SBC enters Overtemp mode, the RSTN pin is driven LOW and the limp home control bit, LHC, is set so that the LIMP pin is driven LOW.

The chip temperature must drop a hysteresis level below the overtemperature shutdown threshold before the SBC can exit Overtemp mode. After leaving Overtemp mode the SBC enters Standby mode and a system reset is generated (reset pulse width of  $t_{\text{W(rst)}}$ , long or short; see Section 6.5.1 and Table 11).

### 6.2 SPI

#### 6.2.1 Introduction

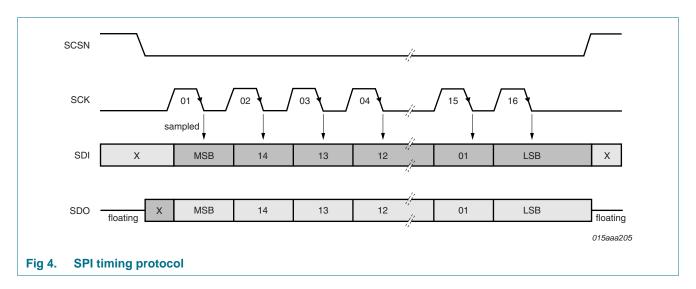

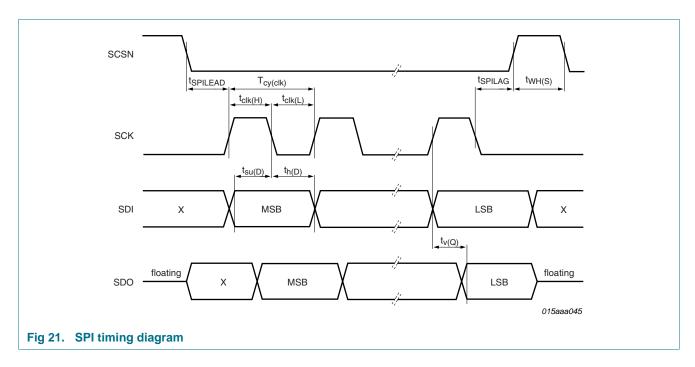

The Serial Peripheral Interface (SPI) provides the communication link with the microcontroller, supporting multi-slave operations. The SPI is configured for full duplex data transfer, so status information is returned when new control data is shifted in. The interface also offers a read-only access option, allowing registers to be read back by the application without changing the register content.

The SPI uses four interface signals for synchronization and data transfer:

- SCSN: SPI chip select; active LOW

- SCK: SPI clock; default level is LOW due to low-power concept

- SDI: SPI data input

- SDO: SPI data output; floating when pin SCSN is HIGH

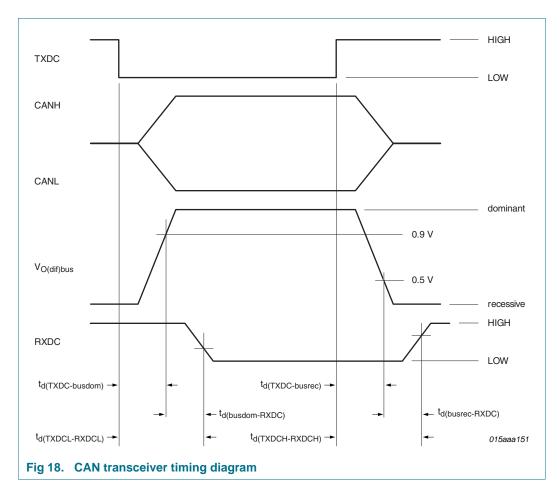

Bit sampling is performed on the falling clock edge and data is shifted on the rising clock edge (see Figure 4).

## High-speed CAN/LIN core system basis chip

### 6.2.2 Register map

The first three bits (A2, A1 and A0) of the message header define the register address. The fourth bit (RO) defines the selected register as read/write or read only.

Table 3. Register map

| Address bits 15, 14 and 13 | Write access bit 12 = 0       | Read/Write access bits 11 0 |

|----------------------------|-------------------------------|-----------------------------|

| 000                        | 0 = read/write, 1 = read only | WD_and_Status register      |

| 001                        | 0 = read/write, 1 = read only | Mode_Control register       |

| 010                        | 0 = read/write, 1 = read only | Int_Control register        |

| 011                        | 0 = read/write, 1 = read only | Int_Status register         |

## High-speed CAN/LIN core system basis chip

## 6.2.3 WD\_and\_Status register

Table 4. WD\_and\_Status register

| Bit   | Symbol     | Access | Power-on default | Description                                                                                                |

|-------|------------|--------|------------------|------------------------------------------------------------------------------------------------------------|

| 15:13 | A2, A1, A0 | R      | 000              | register address                                                                                           |

| 12    | RO         | R/W    | 0                | access status                                                                                              |

|       |            |        |                  | 0: register set to read/write                                                                              |

|       |            |        |                  | 1: register set to read only                                                                               |

| 11    | WMC        | R/W    | 0                | watchdog mode control                                                                                      |

|       |            |        |                  | 0: Normal mode: watchdog in Window mode; Standby mode: watchdog in Timeout mode                            |

|       |            |        |                  | 1: Normal mode: watchdog in Timeout mode; Standby mode: watchdog in Off mode                               |

| 10:8  | NWP[1]     | R/W    | 100              | nominal watchdog period                                                                                    |

|       |            |        |                  | 000: 8 ms                                                                                                  |

|       |            |        |                  | 001: 16 ms                                                                                                 |

|       |            |        |                  | 010: 32 ms                                                                                                 |

|       |            |        |                  | 011: 64 ms                                                                                                 |

|       |            |        |                  | 100: 128 ms                                                                                                |

|       |            |        |                  | 101: 256 ms                                                                                                |

|       |            |        |                  | 110: 1024 ms                                                                                               |

|       |            |        |                  | 111: 4096 ms                                                                                               |

| 7     | WOS/SWR    | R/W    | -                | watchdog off status/software reset                                                                         |

|       |            |        |                  | 0: WDOFF pin LOW; watchdog mode determined by bit WMC                                                      |

|       |            |        |                  | <ol> <li>watchdog disabled due to HIGH level on pin WDOFF; results in software<br/>reset</li> </ol>        |

| 6     | V1S        | R      | -                | V1 status                                                                                                  |

|       |            |        |                  | 0: V1 output voltage above 90 % undervoltage recovery threshold ( $V_{uvr}$ ; see <u>Table 10</u> )        |

|       |            |        |                  | 1: V1 output voltage below 90 % undervoltage detection threshold (V <sub>uvd</sub> ; see <u>Table 10</u> ) |

| 5     | V2S        | R      | -                | V2 status                                                                                                  |

|       |            |        |                  | 0: V2 output voltage above undervoltage release threshold (V <sub>uvr</sub> ; see <u>Table 10</u> )        |

|       |            |        |                  | 1: V2 output voltage below undervoltage detection threshold (V <sub>uvd</sub> ; see <u>Table 10</u> )      |

| 4     | WLS1       | R      | -                | wake-up 1 status                                                                                           |

|       |            |        |                  | 0: WAKE1 input voltage below switching threshold (V <sub>th(sw)</sub> )                                    |

|       |            |        |                  | 1: WAKE1 input voltage above switching threshold (V <sub>th(sw)</sub> )                                    |

| 3     | WLS2       | R      | -                | wake-up 2 status                                                                                           |

|       |            |        |                  | 0: WAKE2 input voltage below switching threshold (V <sub>th(sw)</sub> )                                    |

|       |            |        |                  |                                                                                                            |

|       |            |        |                  | 1: WAKE2 input voltage above switching threshold (V <sub>th(sw)</sub> )                                    |

<sup>[1]</sup> Bit NWP is set to its default value (100) after a reset.

## High-speed CAN/LIN core system basis chip

## 6.2.4 Mode\_Control register

Table 5. Mode\_Control register

| Table 5 | . Mode_C   | ontrol reg | gister           |                                                                                                                                                                                                                                                      |

|---------|------------|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Symbol     | Access     | Power-on default | Description                                                                                                                                                                                                                                          |

| 15:13   | A2, A1, A0 | R          | 001              | register address                                                                                                                                                                                                                                     |

| 12      | RO         | R/W        | 0                | access status                                                                                                                                                                                                                                        |

|         |            |            |                  | 0: register set to read/write                                                                                                                                                                                                                        |

|         |            |            |                  | 1: register set to read only                                                                                                                                                                                                                         |

| 11:10   | MC         | R/W        | 00               | mode control                                                                                                                                                                                                                                         |

|         |            |            |                  | 00: Standby mode                                                                                                                                                                                                                                     |

|         |            |            |                  | 01: Sleep mode                                                                                                                                                                                                                                       |

|         |            |            |                  | 10: Normal mode; V2 off                                                                                                                                                                                                                              |

|         |            |            |                  | 11: Normal mode; V2 on                                                                                                                                                                                                                               |

| 9       | LHWC[1]    | R/W        | 1                | limp home warning control                                                                                                                                                                                                                            |

|         |            |            |                  | 0: no limp home warning                                                                                                                                                                                                                              |

|         |            |            |                  | 1: limp home warning is set; next reset will activate LIMP output                                                                                                                                                                                    |

| 8       | LHC[2]     | R/W        | 0                | limp home control                                                                                                                                                                                                                                    |

|         |            |            |                  | 0: LIMP pin set floating                                                                                                                                                                                                                             |

|         |            |            |                  | 1: LIMP pin driven LOW                                                                                                                                                                                                                               |

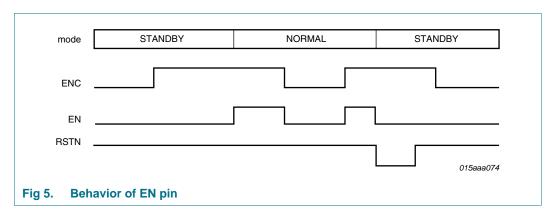

| 7       | ENC        | R/W        | 0                | enable control                                                                                                                                                                                                                                       |

|         |            |            |                  | 0: EN pin driven LOW                                                                                                                                                                                                                                 |

|         |            |            |                  | 1: EN pin driven HIGH in Normal mode                                                                                                                                                                                                                 |

| 6       | LSC        | R/W        | 0                | LIN slope control                                                                                                                                                                                                                                    |

|         |            |            |                  | 0: normal slope, 20 kbit/s                                                                                                                                                                                                                           |

|         |            |            |                  | 1: low slope, 10.4 kbit/s                                                                                                                                                                                                                            |

| 5       | WBC        | R/W        | 0                | wake bias control                                                                                                                                                                                                                                    |

|         |            |            |                  | 0: pin WBIAS floating if WSEn = 0; 16 ms sampling if WSEn = 1                                                                                                                                                                                        |

|         |            |            |                  | 1: pin WBIAS LOW if WSEn = 0; 64 ms sampling if WSEn = 1                                                                                                                                                                                             |

| 4       | PDC        | R/W        | 0                | power distribution control                                                                                                                                                                                                                           |

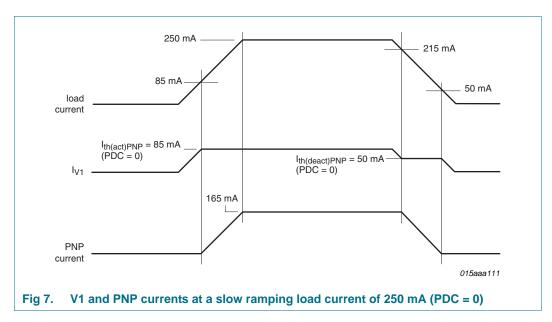

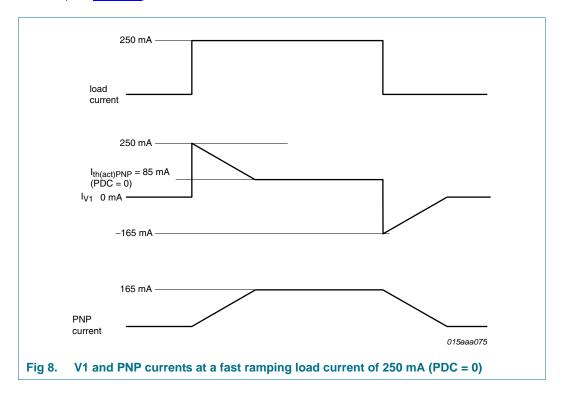

|         |            |            |                  | 0: V1 threshold current for activating the external PNP transistor; load current rising; $I_{th(act)PNP} = 85$ mA; V1 threshold current for deactivating the external PNP transistor; load current falling; $I_{th(deact)PNP} = 50$ mA; see Figure 7 |

|         |            |            |                  | 1: V1 threshold current for activating the external PNP transistor; load current rising; $I_{th(act)PNP} = 50$ mA; V1 threshold current for deactivating the external PNP transistor; load current falling; $I_{th(deact)PNP} = 15$ mA; see Figure 7 |

| 3:0     | reserved   | R          | 0000             |                                                                                                                                                                                                                                                      |

|         |            |            |                  |                                                                                                                                                                                                                                                      |

<sup>[1]</sup> Bit LHWC is set to 1 after a reset.

<sup>[2]</sup> Bit LHC is set to 1 after a reset, if LHWC was set to 1 prior to the reset.

## High-speed CAN/LIN core system basis chip

## 6.2.5 Int\_Control register

Table 6. Int Control register

| Bit             | Symbol     | Access | Power-on default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|------------|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:13           | A2, A1, A0 | R      | 010              | register address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12              | RO         | R/W    | 0                | access status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |            |        |                  | 0: register set to read/write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 |            |        |                  | 1: register set to read only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11              | V1UIE      | R/W    | 0                | V1 undervoltage interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |            |        |                  | 0: V1 undervoltage warning interrupts cannot be requested                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |            |        |                  | 1: V1 undervoltage warning interrupts can be requested                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10              | V2UIE      | R/W    | 0                | V2 undervoltage interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |            |        |                  | 0: V2 undervoltage warning interrupts cannot be requested                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                 |            |        |                  | 1: V2 undervoltage warning interrupts can be requested                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9               | STBCL      | R/W    | 0                | LIN standby control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                 |            |        |                  | 0: When the SBC is in Normal mode (MC = 1x):                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |            |        |                  | LIN is in Active mode. The wake-up flag (visible on RXDL) is cleared regardless of the value of $V_{\text{BAT}}$ .                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |            |        |                  | When the SBC is in Standby/Sleep mode (MC = 0x):                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |            |        |                  | LIN is in Off mode. Bus wake-up detection is disabled. LIN wake-up interrupts cannot be requested.                                                                                                                                                                                                                                                                                                                                                                                                              |

|                 |            |        |                  | 1: LIN is in Lowpower mode with bus wake-up detection enabled, regardless of the SBC mode (MC = xx). LIN wake-up interrupts can be requested.                                                                                                                                                                                                                                                                                                                                                                   |

| 0               |            | _      | _                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0               | reserved   | R      | 0                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 | WIC1       | R/W    | 0                | wake-up interrupt 1 control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                 |            |        |                  | wake-up interrupt 1 control 00: wake-up interrupt 1 disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                 |            |        |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                 |            |        |                  | 00: wake-up interrupt 1 disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |            |        |                  | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7:6             |            |        |                  | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7:6             | WIC1       | R/W    | 00               | <ul><li>00: wake-up interrupt 1 disabled</li><li>01: wake-up interrupt 1 on rising edge</li><li>10: wake-up interrupt 1 on falling edge</li><li>11: wake-up interrupt 1 on both edges</li></ul>                                                                                                                                                                                                                                                                                                                 |

| 7:6             | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control                                                                                                                                                                                                                                                                                                                               |

| 7:6             | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled                                                                                                                                                                                                                                                                                              |

| 7:6             | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled 01: wake-up interrupt 2 on rising edge                                                                                                                                                                                                                                                       |

| 7:6<br>5:4      | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled 01: wake-up interrupt 2 on rising edge 10: wake-up interrupt 2 on falling edge                                                                                                                                                                                                               |

| 7:6<br>5:4      | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled 01: wake-up interrupt 2 on rising edge 10: wake-up interrupt 2 on falling edge 11: wake-up interrupt 2 on both edges                                                                                                                                                                         |

| 7:6<br>5:4      | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled 01: wake-up interrupt 2 on rising edge 10: wake-up interrupt 2 on falling edge 11: wake-up interrupt 2 on both edges CAN standby control                                                                                                                                                     |

| 7:6<br>5:4      | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled 01: wake-up interrupt 2 on rising edge 10: wake-up interrupt 2 on falling edge 11: wake-up interrupt 2 on both edges CAN standby control 0: When the SBC is in Normal mode (MC = 1x): CAN is in Active mode. The wake-up flag (visible on RXDC) is cleared                                   |

| 8<br>7:6<br>5:4 | WIC1       | R/W    | 00               | 00: wake-up interrupt 1 disabled 01: wake-up interrupt 1 on rising edge 10: wake-up interrupt 1 on falling edge 11: wake-up interrupt 1 on both edges wake-up interrupt 2 control 00: wake-up interrupt 2 disabled 01: wake-up interrupt 2 on rising edge 10: wake-up interrupt 2 on falling edge 11: wake-up interrupt 2 on both edges  CAN standby control 0: When the SBC is in Normal mode (MC = 1x): CAN is in Active mode. The wake-up flag (visible on RXDC) is cleared regardless of V2 output voltage. |

## High-speed CAN/LIN core system basis chip

Table 6.

Int\_Control register ...continued

| Bit | Symbol | Access | Power-on default | Description                                                                                                     |  |

|-----|--------|--------|------------------|-----------------------------------------------------------------------------------------------------------------|--|

| 2   | RTHC   | R/W    | 0                | reset threshold control                                                                                         |  |

|     |        |        |                  | 0: The reset threshold is set to the 90 % V1 undervoltage detection voltage ( $V_{uvd}$ ; see <u>Table 10</u> ) |  |

|     |        |        |                  | 1: The reset threshold is set to the 70 % V1 undervoltage detection voltage ( $V_{uvd}$ ; see <u>Table 10</u> ) |  |

| 1   | WSE1   | R/W    | 0                | WAKE1 sample enable                                                                                             |  |

|     |        |        |                  | 0: sampling continuously                                                                                        |  |

|     |        |        |                  | 1: sampling of WAKE1 is synchronized with WBIAS (sample rate controlled by WBC)                                 |  |

| 0   | WSE2   | R/W    | 0                | WAKE2 sample enable                                                                                             |  |

|     |        |        |                  | 0: sampling continuously                                                                                        |  |

|     |        |        |                  | 1: sampling of WAKE1 is synchronized with WBIAS (sample rate controlled by WBC)                                 |  |

## High-speed CAN/LIN core system basis chip

## 6.2.6 Int\_Status register

Table 7. Int\_Status register[1]

| 12         RO         R/W         0         access status           0: register set to read/write         1: register set to read only           11         V1UI         R/W         0         V1 undervoltage interrupts           0: no V1 undervoltage warning interrupt pending         1: V1 undervoltage warning interrupt pending           10         V2UI         R/W         0         V2 undervoltage warning interrupt pending           11         V2UI         R/W         0         UN wake-up interrupt pending           11         V2UI         R/W         0         UN wake-up interrupt pending           12         V2 Undervoltage warning interrupt pending         1: V2 undervoltage warning interrupt pending           12         V2 Undervoltage warning interrupt pending           13         V2 Undervoltage warning interrupt pending           15         V2 Undervoltage warning interrupt pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit   | Symbol     | Access | Power-on default | Description                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--------|------------------|-------------------------------------------------|

| 1: register set to read/write   1: register set to read only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15:13 | A2, A1, A0 | R      | 011              | register address                                |

| 1: register set to read only           11         V1UI         R/W         0         V1 undervoltage interrupts           0: no V1 undervoltage warning interrupt pending         1: V1 undervoltage warning interrupt pending           10         V2UI         R/W         0         V2 undervoltage warning interrupt pending           1: V2 undervoltage warning interrupt pending         1: V2 undervoltage warning interrupt pending           1: V2 undervoltage warning interrupt pending         1: V2 undervoltage warning interrupt pending           8         reserved         R         0           7         CI         R/W         0         Cyclic interrupt pending           1: cyclic interrupt pending         1: cyclic interrupt pending           6         WI1         R/W         0         wake-up interrupt 1 pending           1: cyclic interrupt pending         1: cyclic interrupt 1 pending           1: wake-up interrupt 1 pending         1: wake-up interrupt 1 pending           5         POSI         R/W         1         power-on status interrupt           0: no ovalus interrupt pending         1: power-on interrupt pending           4         WI2         R/W         0         wake-up interrupt 2 pending           3         CWI         R/W         0         CAN wake-up interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12    | RO         | R/W    | 0                | access status                                   |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |            |        |                  | 0: register set to read/write                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |            |        |                  | 1: register set to read only                    |

| 1: V1 undervoltage warning interrupt pending           10         V2UI         R/W         0         V2 undervoltage interrupts           0: no V2 undervoltage warning interrupt pending         1: V2 undervoltage warning interrupt pending           9         LWI         R/W         0         LIN wake-up interrupt pending           8         reserved         R         0           7         CI         R/W         0         cyclic interrupt pending           1: cyclic interrupt pending         1: cyclic interrupt pending           6         WI1         R/W         0         wake-up interrupt 1 pending           5         POSI         R/W         1         power-on interrupt 1 pending           5         POSI         R/W         1         power-on interrupt pending           4         WI2         R/W         0         wake-up interrupt 2           0: no wake-up interrupt 2 pending         1: wake-up interrupt 2 pending           3         CWI         R/W         0         CAN wake-up interrupt pending           1: CAN wake-up interrupt pending         1: CAN wake-up interrupt pending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11    | V1UI       | R/W    | 0                | V1 undervoltage interrupts                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |            |        |                  | 0: no V1 undervoltage warning interrupt pending |

| 0: no V2 undervoltage warning interrupt pending   1: V3 undervoltage warning interrupt pending   1: LIN wake-up interrupt pending   1: cyclic interrupt pending   1: cyclic interrupt pending   1: cyclic interrupt pending   1: cyclic interrupt pending   1: wake-up interrupt 1 pending   1: wake-up interrupt 1 pending   1: wake-up interrupt 1 pending   1: wake-up interrupt pending   1: power-on interrupt pending   1: power-on interrupt pending   1: power-on interrupt 2 pending   1: wake-up interrupt pending   1: CAN wake-up interrupt pending |       |            |        |                  | 1: V1 undervoltage warning interrupt pending    |

| 9         LWI         R/W         0         LIN wake-up interrupt 0: no LIN wake-up interrupt pending 1: cyclic interrupt pending 1: wake-up interrupt 1 pending 1: power-on status interrupt 1 pending 1: power-on interrupt pending 1: power-on interrupt pending 1: power-on interrupt pending 1: wake-up interrupt 2 pending 1: wake-up interrupt pending 1: cAN wake-up interrupt                                                         | 10    | V2UI       | R/W    | 0                | V2 undervoltage interrupts                      |