### TW2851

FN7743 Rev. 0.00 August 17, 2012

# 4-Channel A/V Decoder with Multiplexer/VGA/LCD Display Processor for Security Applications

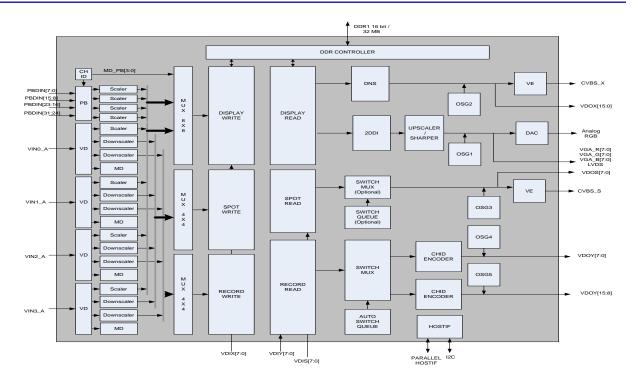

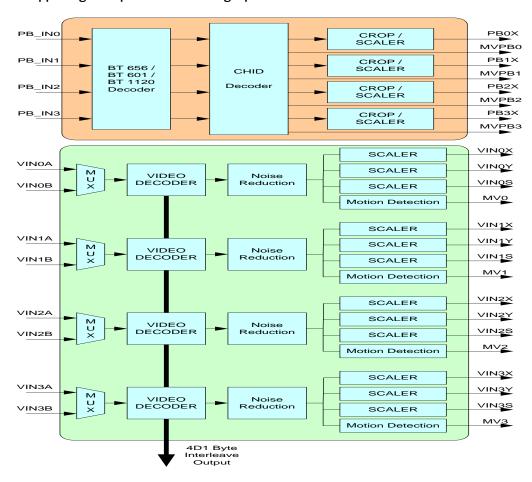

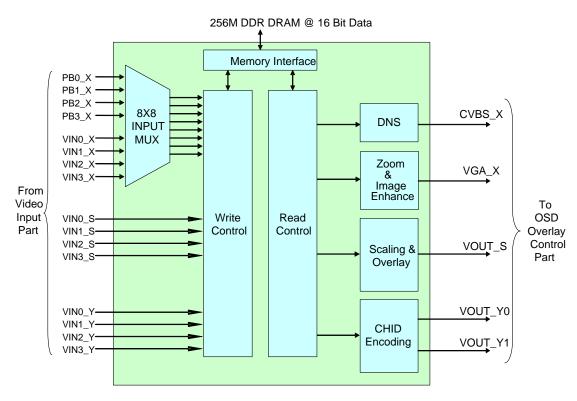

The TW2851 is a fully integrated A/V decoder, multiplexer, and display processor chip. It has eight CVBS analog inputs fed into four internal high quality NTSC/PAL video decoders. It has four digital input ports supporting various type of input format, including four BT 656 inputs, two BT 601 inputs, or one 1120 playback input. It has one optional VGA display controller or LCD panel controller, two CVBS display, one digital SPOT output, two digital recorder outputs, and one digital display output. Every output has its associated graphic overlay function that displays bitmap for OSG, single box, 2D array box, borders, privacy mask, and mouse cursor.

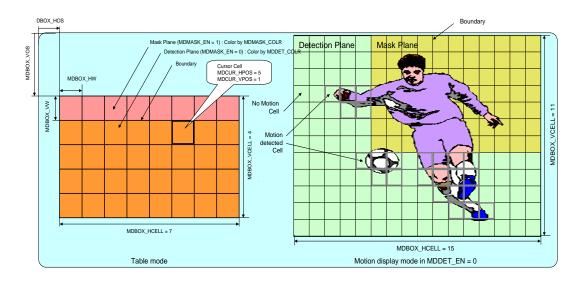

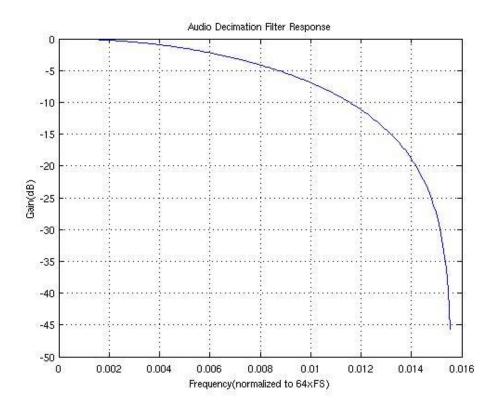

The four built-in video decoders include four antialiasing filters, 10bit Analog-to-Digital converters, proprietary digital gain/clamp controller, and high quality Y/C separator to reduce cross-noise. Associated with each video decoder, there are built-in motion, blind, and night detectors to provide alarm signals, a noise reducer to reduce the impulse noise, and 3 sets of downscalers to provide proper video size into the display, record, and SPOT multiplexers.

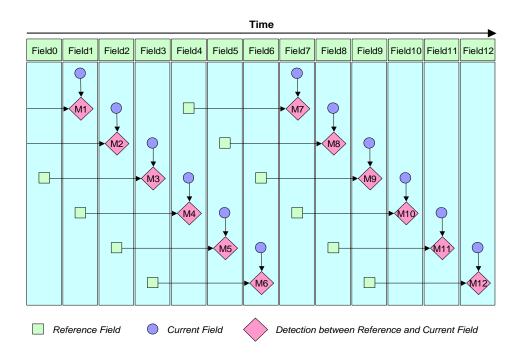

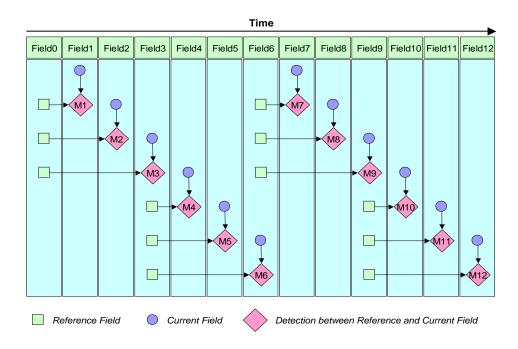

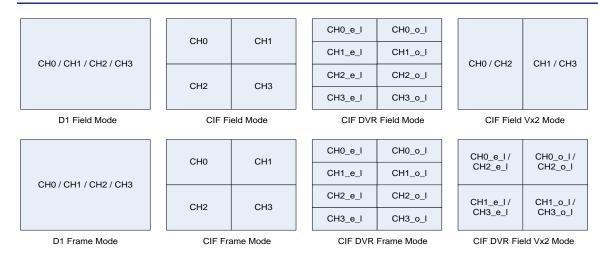

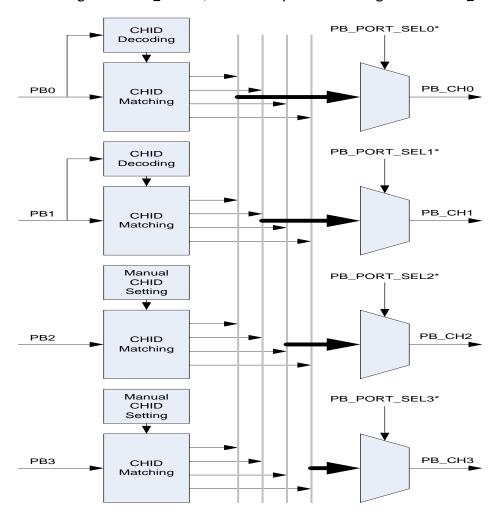

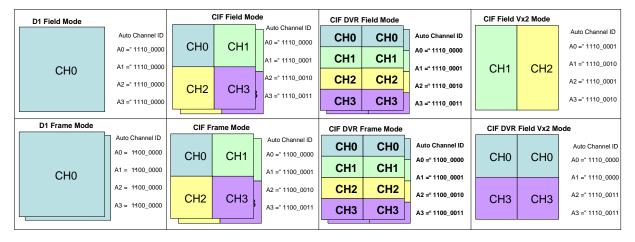

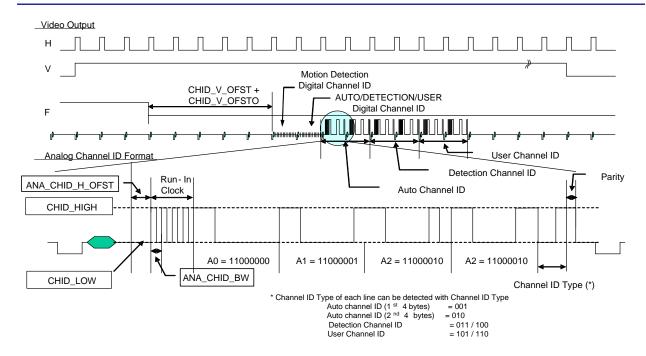

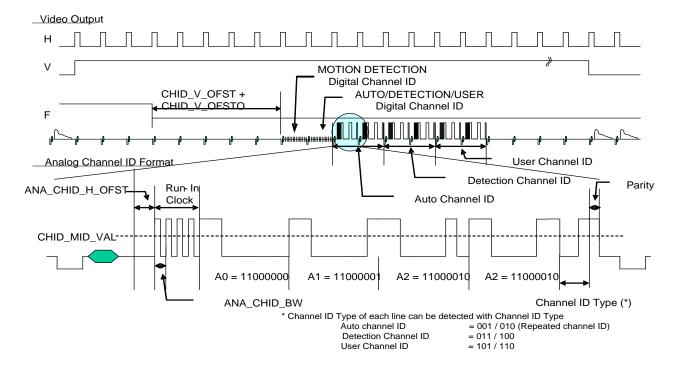

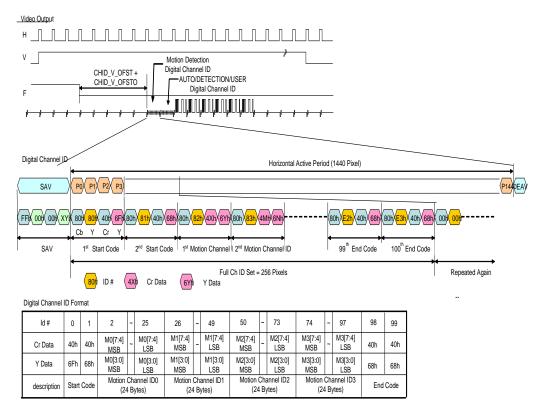

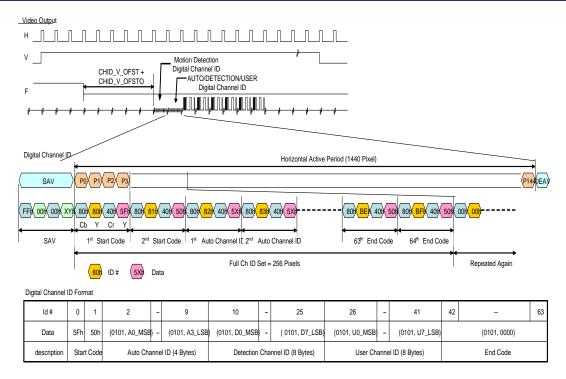

The TW2851 MUX function selects video inputs from any video decoder/ digital inputs to any of recording / SPOT / VGA display / CVBS display outputs flexibly. The recording multiplexer supports frame / field and byte-interleaved multi-channel video streams in the format of BT 656, BT 1120 to interface with external video compression CODEC. The frame / field allocation of each channel can be flexibly configurable in the multi-channel video stream. The multi-channel video stream features built-in channel ID to identify channels of interest for the CODEC or playback module to properly demultiplex the multi-channel stream into single channel streams. The motion / night / blind detection information are also embedded as part of the channel ID.

The display multiplexer displays up to 8 video windows, with 4 for video decoders and 4 for either digital interface or video decoder interface to support pseudo 8 channel inputs. The location and size of each of the 8 display windows are flexibly configurable. The multiplexed display video is sent

to both VGA / LCD and the CVBS output simultaneously. Before the VGA / LCD output, there is a 2D de-interlacer converting the interlaced video into progressive for any PC monitor / LCD panel with resolution up to WXGA+ (1440x900) resolution. The VGA interface provides RGB component with both analog output through 3 embedded DACs and digital TTL outputs. The LVDS interface provides single or dual channel output to drive various TFT LCD panels.

The SPOT multiplexer functions as a either SPOT display or a secondary record mux. It supports single D1 frame rate output. When used as display purpose, it is capable of supporting 1 / 4 windows in a fixed configuration. When used as record mux purpose, it is capable of supporting quad window or frame / field interleave multi-channel stream in single D1 frame rate.

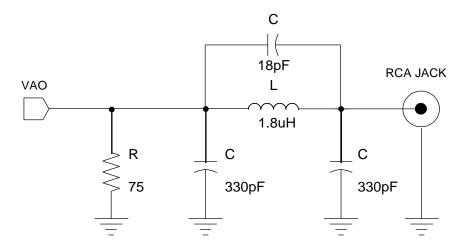

There are two built-in video encoders features two 10-bit embedded DACs to provide 2 CVBS outputs. The two video encoders are flexibly configurable to output any two of the display, SPOT and record path video content.

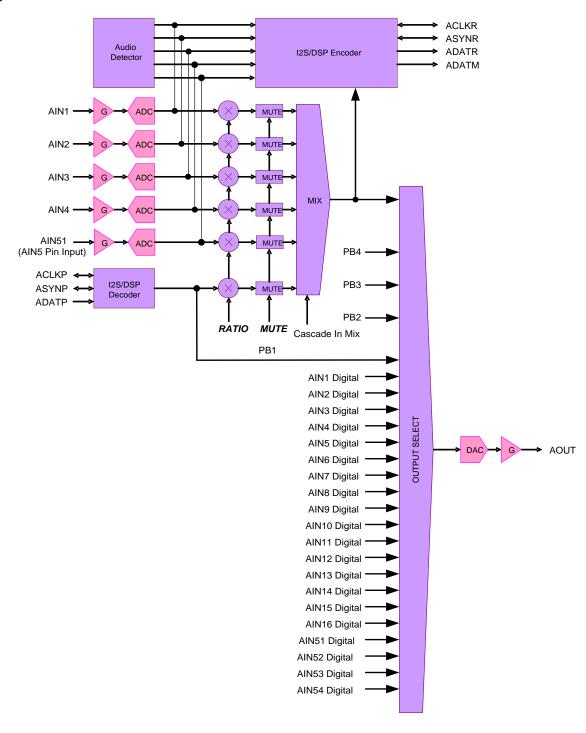

The TW2851 also includes an audio CODEC with five audio Analog-to-Digital converters and one Digital-to-Analog converter. A built-in audio multiplexer generates digital outputs for recording / mixing and accepts digital input for playback.

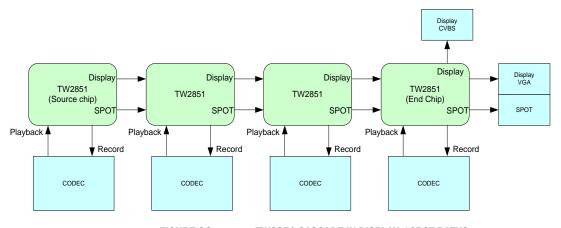

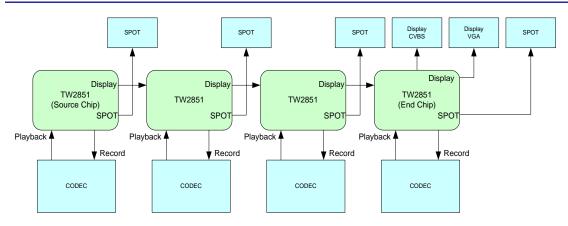

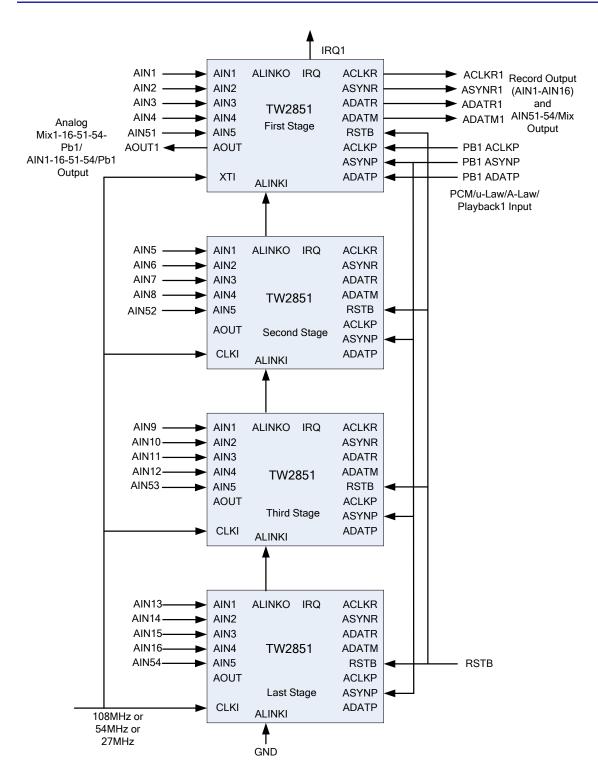

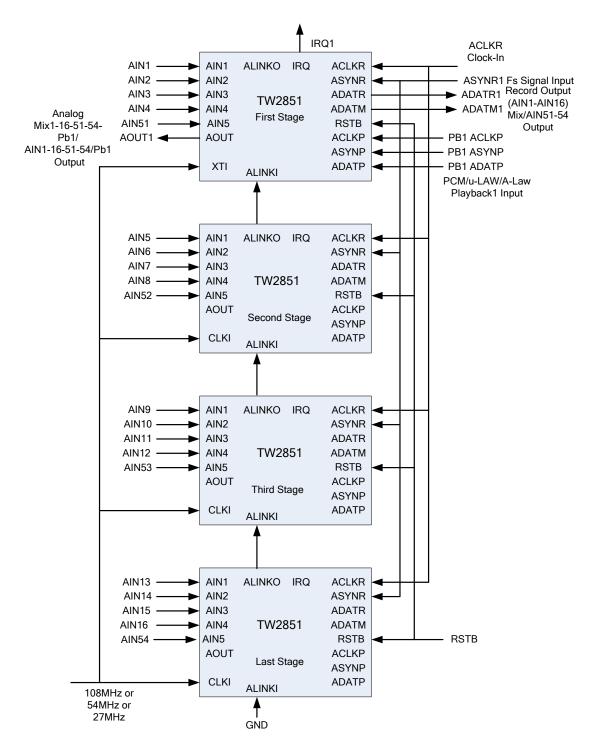

TW2851 features a cascade function to allow up to 4 TW2851 chips to connect together to increase the total number of channels / windows supported in VGA display and SPOT display. With 4 chips cascaded together, the VGA display path can display up to 32 display windows, and the SPOT display can display up to 16 windows.

### **Analog Video Decoder**

- 4 sets of video decoder accept all NTSC(M/N/4.43) / PAL (B/D/G/H/I/K/L/M/N/60) standards with auto detection

- 8 CVBS analog inputs for pseudo 8 channel support

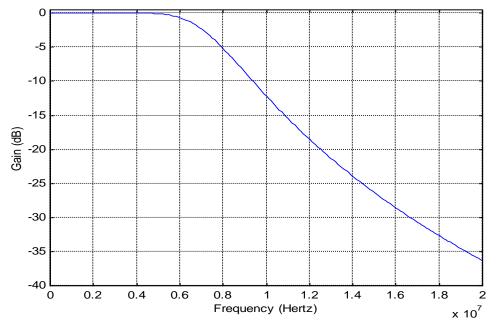

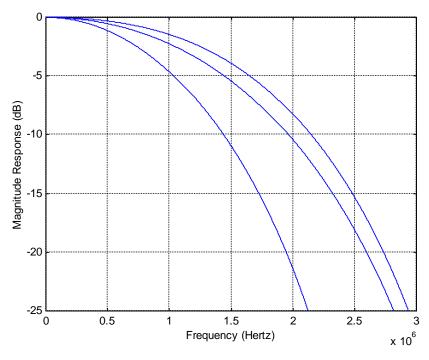

- Integrated video analog anti-aliasing filters and 10 bit CMOS ADCs for each video decoder

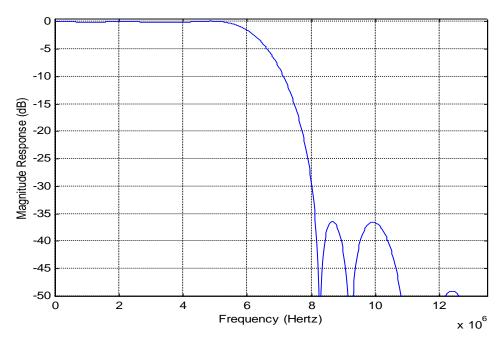

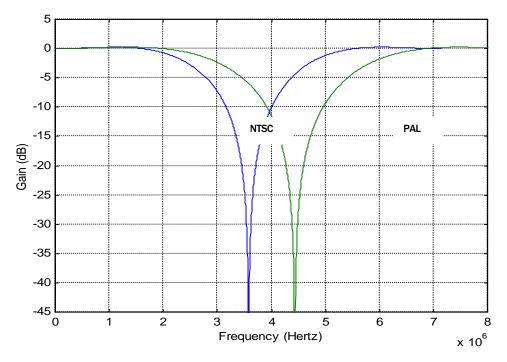

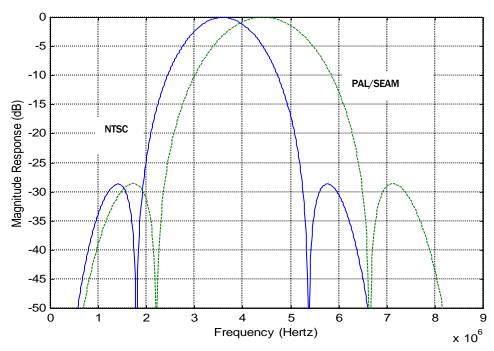

- High performance adaptive 4H comb filters for all NTSC/PAL standards

- IF compensation filter for improvement of color demodulation

- Color Transient Improvement (CTI)

- Automatic white peak control

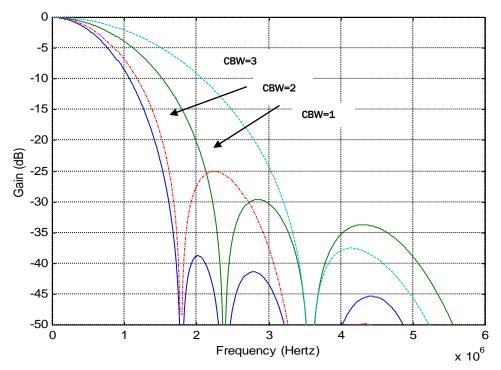

- Triple high performance scalers scale video input independently for each of display, recording and SPOT path

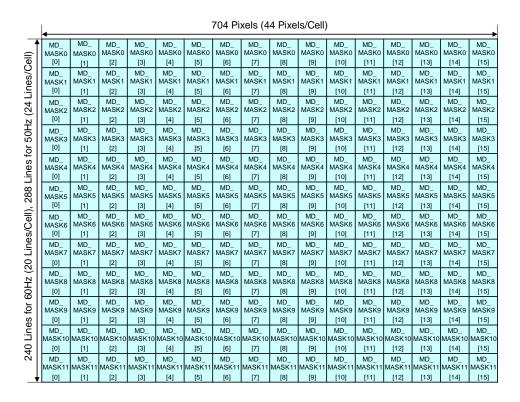

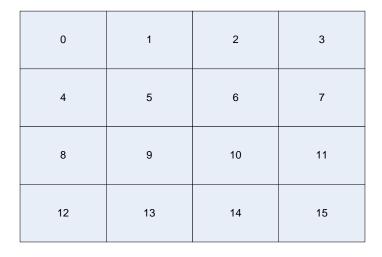

- Four built-in motion detectors with 16 X 12 cells, four blind and night detectors

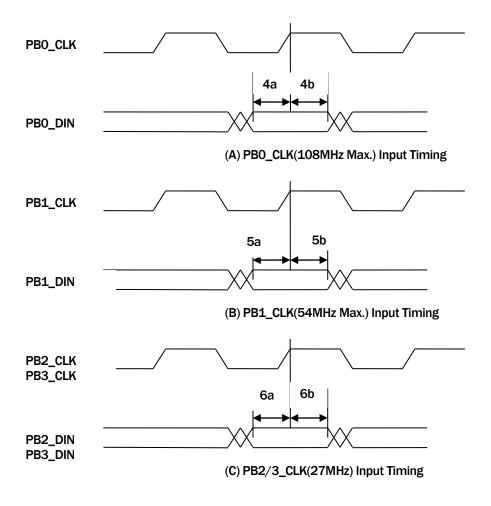

### **Digital Input Ports**

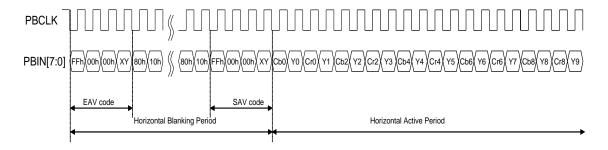

- Supports up to 4 BT. 656 ports, 2 BT. 601, 1 port RGB, or 1 port BT. 1120. The BT 1120 supports a 54 MHz channel with 4 D1 put together.

- Auto cropping / strobe for playback input using 2 built-in Analog / Digital Channel ID decoder for selecting 4 out of maximum of 16 channels from multi-channel input stream

- 4 built-in down scalers for displaying arbitrary size windows on the display output

### **Analog/Digital VGA Display**

- Native Resolution of VGA, D1, SVGA, XGA, up to WXGA+ (1440x900), capable of displaying 4 D1 screens side by side without downscaling.

- Up-Scaler for ZOOM function and playback of full screen D1 image

- 3 Built-in DACs for analog VGA RGB output

- Digital RGB interface in 24-bit TTL output

- DDC channel interface to read the external monitor configuration

- Built-in 2D De-interlacer for progressive output

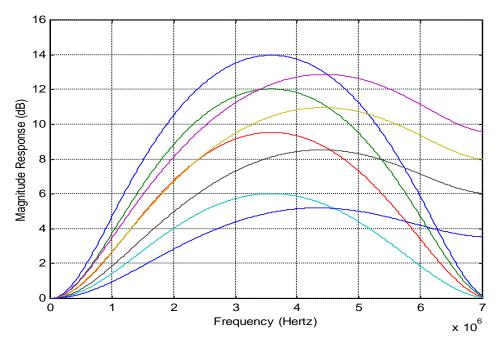

- Sharpness control with horizontal/vertical peaking

- Black/White Stretch

- Programmable hue, brightness, saturation, contrast

- Independent RGB gain and offset controls

- Programmable Gamma correction for each of RGB

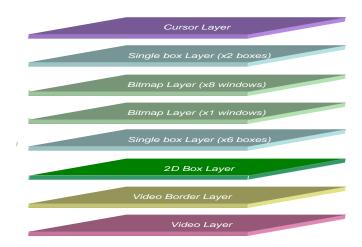

- Built-in 2-layer 9-window bitmap OSG with 16-bit per pixel color

- Hardware OSG bitmap up-scaler to allow same content displayed on both VGA/LCD and CVBS output

- Additional OSG layers such as window border box, 2D motion box, Privacy Mask overlay, and Mouse **Cursor support**

- Programmable hue, saturation, contrast, brightness and sharpness

- Proprietary fast video locking system for non-realtime application

- Noise Reduction to remove impulse noise

### **TFT LCD Panel Support**

- Supports panel with similar resolution as the VGA

- Supports single or dual channel LVDS panel

- Supports Panel power sequencing.

- Supports DPMS for monitor power management

### **Display CVBS Output**

- Display Output through one of the two built-in CVBS video encoder

- Built-in 2-layer 9-windows bitmap OSG with 16-bit per pixel color

- Additional OSG layers such as window border box, 2D motion box, mouse cursor, and Privacy Mask

### **Display Multiplexer**

- Displays 8 windows for 4 video decoder inputs plus 4 digital input channels or 8 video decoder channels to support pseudo 8-channel

- Either Live or Strobe capture mode for pseudo 8channel support

- Horizontal / Vertical mirroring for each window

- Last field / frame image captured when video-loss detected

- Simultaneous output to both VGA/LCD and CVBS output with the same video content

### Record Multiplexer

- 2 ports of BT. 656, 1 port BT. 601, or 1 port of BT.1120-like digital Interface support up to 4 D1 real-time recording output to external CODEC

- Supports Frame/Field Interleaved mode with 8 picture types or byte interleaved stream for multichannel video output

- Either Live or Strobe capture mode for pseudo 8channel support

- Supports dynamic field / frame picture-type and channel allocation through a switching queue up to 2048 entries

- Horizontal / Vertical mirroring for each window

- 2 Built-in channel ID encoder carrying channel and motion / blind / night detection information of each field/frame in multi-channel stream

- Two built-in 8-window bitmap OSG with 16-bit per pixel color for each of the two record output ports

- Field switching capable OSG supports 4 different contents changing from field to field through switching queue

- Additional OSG layers such Privacy Mask overlay. and Mouse Cursor

### **SPOT Multiplexer**

- Optionally configured as network output mode through a BT. 656 digital interface to support frame/field interleave feature similar to record path Switch mode

- SPOT analog output configurable through one of the two built-in CVBS video encoder

- LIVE capture mode in FULL D1, Quad CIF and 16 **QCIF** windows

- Strobe capture mode for pseudo 8-channel support

- Video window arrangement independent of the recording and display output

- Horizontal and Vertical Mirroring for each channel

- Built-in 8 windows bitmap OSGs with 16-bit per pixel color

- Additional OSG layers such as window border box, Privacy Mask overlay, and Mouse Cursor support

#### **Dual Video Encoders**

- Flexibly shared by Display, Record and SPOT

- Analog NTSC/PAL standards

- Programmable bandwidth of luminance and chrominance signal for each path

- Two 10-bit video CMOS DACs

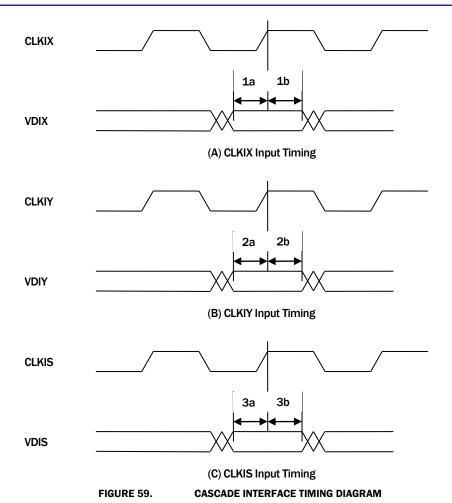

### **Cascade Capability**

- VGA display cascade mode displays up to 32 windows (16 video input and 16 playback input) on both VGA/LCD and CVBS output using 4 TW2851 chips

- SPOT display cascade support up to 16 channels at the D1 output

- Built-in 8 windows bitmap OSG with 16-bit per pixel color

- Additional OSG layers such as window border box, 2D motion box, mouse cursor, and Privacy Mask overlay

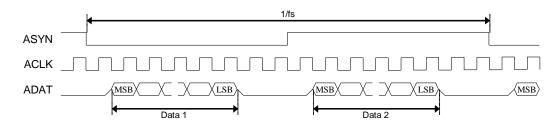

#### **Audio CODEC**

- Integrated five audio ADCs and one audio DAC providing multi-channel audio mixed analog output

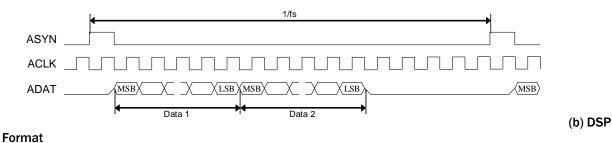

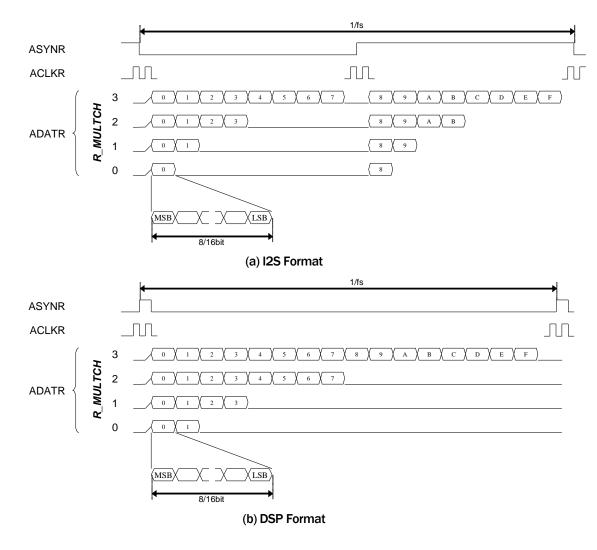

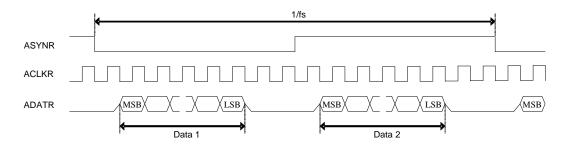

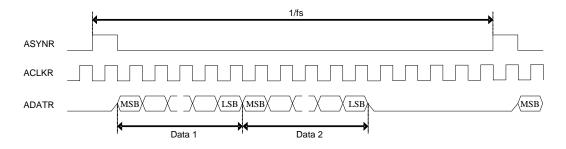

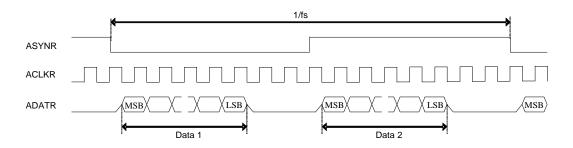

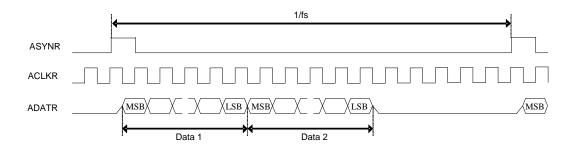

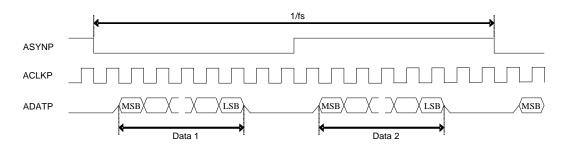

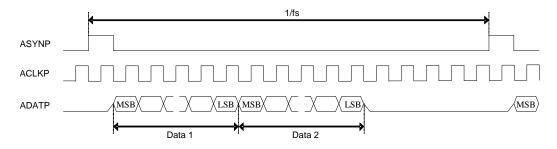

- Supports a standard I2S interface for record output and playback input

- PCM 8/16 bit and u-Law/A-Law 8bit for audio word length

- Programmable audio sample rate that covers popular frequencies of 8/16/32/44.1/48kHz

#### External DDR SDRAM

- Single centralized external DDR SDRAM of 256 Mb (32 MB) capacity

- 16-bit wide data bus running at 166 MHz

- Auto-refresh

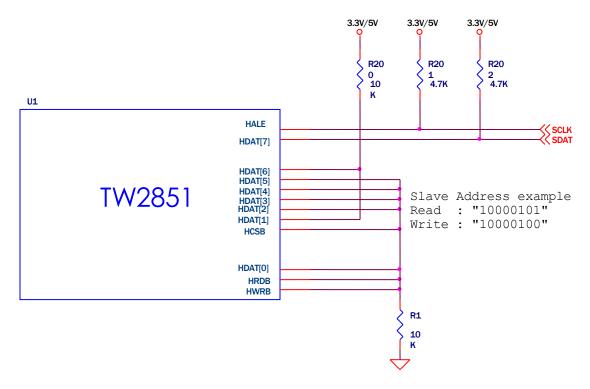

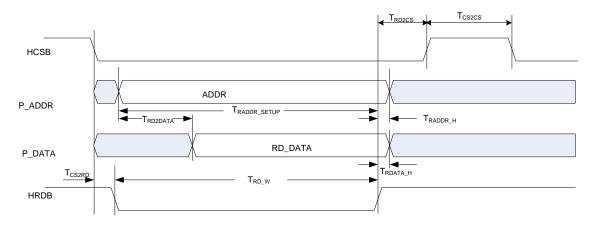

#### **Host Interface**

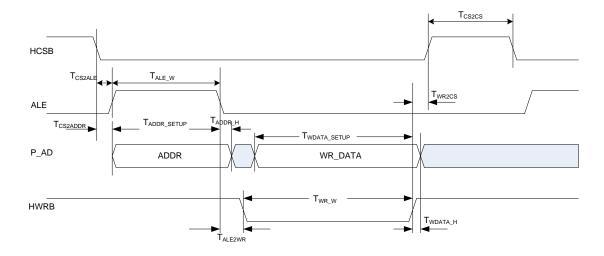

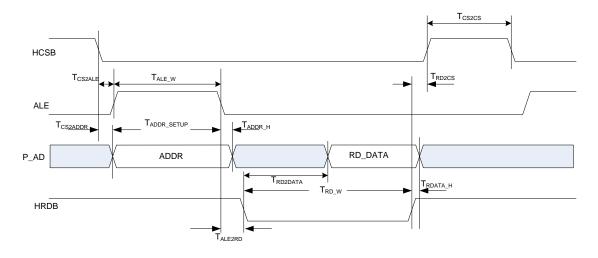

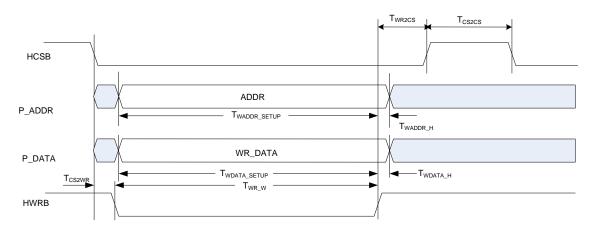

- MCU parallel interface with 8 / 16 bits data bus and 8 /12-bit address bus for higher MCU interface throughput

- Supports both address / data separate or multiplexed mode

- Burst write for faster OSG bitmap upload

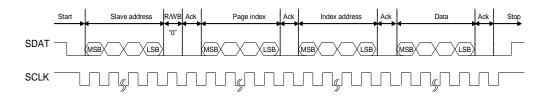

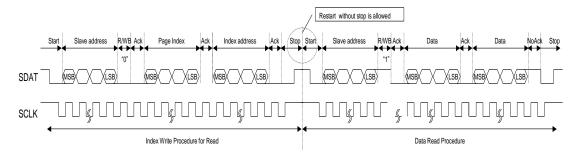

- Serial I<sup>2</sup>C interface

- PS2 mouse port support

### System Clock

- Single 27 MHz external crystal clock input

- 3 built-in PLLs for internal clock generation

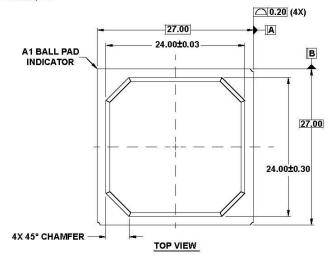

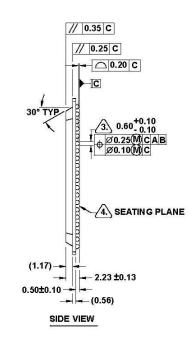

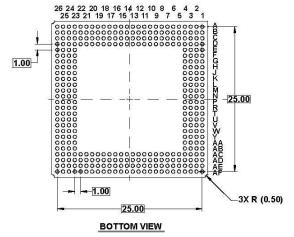

### **Package**

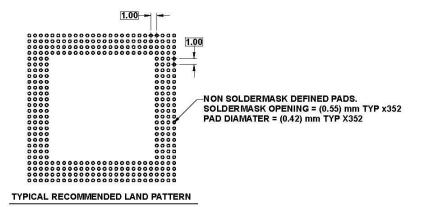

• 352 BGA

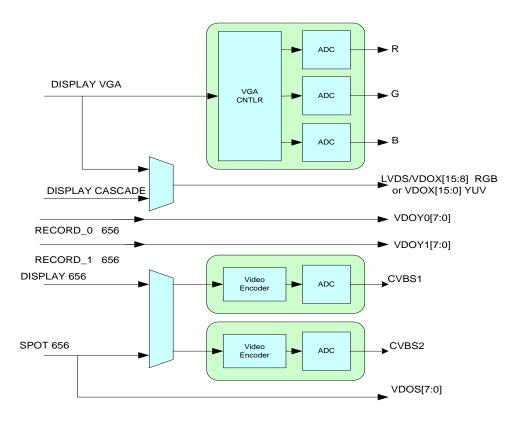

FIGURE 1.TW2851 4-CHANNEL A/V DECODER/MULTIPLEXER/DISPLAY PROCESSOR BLOCK-DIAGRAM

## **Ordering Information**

| PART NUMBER   | PART          | PACKAGE                  | PKG.       |  |

|---------------|---------------|--------------------------|------------|--|

| (NOTE 1)      | MARKING       | (PB-FREE)                | DWG. #     |  |

| TW2851-BB2-GR | TW2851 BB2-GR | 352 LEAD BGA (27mmx27mm) | V352.27X27 |  |

#### NOTE:

1. These Intersil Pb-free BGA packaged products employ special Pb-free material sets; molding compounds/die attach materials and SnAg -e2 solder ball terminals, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free BGA packaged products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## **Table of Contents**

| Analog Video Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Digital Input Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                           |

| Analog/Digital VGA Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                           |

| TFT LCD Panel Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2                                                                                           |

| Display CVBS Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| Display Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                           |

| Record Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2                                                                                           |

| SPOT Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

| Dual Video Encoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3                                                                                           |

| Cascade Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                                                           |

| Audio CODEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |

| External DDR SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |

| Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

| System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                             |

| Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |

| Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

| Table of Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                             |

| Table of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

| Table List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                             |

| Pin Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10                                                                                          |

| TW2851 (352 BGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

| Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                                                          |

| Analog Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                                                          |

| Digital VGA/LVDS Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                             |

| Host Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

| Audio Digital Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |

| Digital Input Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |

| Digital Output Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

| DDR SDRAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

| Misc Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

| Power / Ground Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                             |

| CVBS Video Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |