# **DATA SHEET**

#### HIGH-FIDELITY HEADPHONE AMPLIFIER

## TSDP1xx

### DESCRIPTION

The TSDP1xx is a Cap less Direct Connect<sup>™</sup> Ground-Referenced Output Headphone amplifier with independent left/right volume and GPIO control. It provides high quality audio fidelity with SNR of 105dB and output power of 180mW per channel. The differential inputs allow for flexible input configuration that maximizes noise rejection for best in class CMRR.

### TARGET APPLICATIONS

- Tablets

- Mobile Phones

- Stereo Audio Headsets

- Notebook Computers

- High Fidelity Audio Applications

#### **FEATURES**

- The Class H TSDP1xx Capless DirectConnect™ Feature

- Eliminates Large Output DC Blocking Capacitors

- Reduces Board Area

- Reduces Component Height and Cost

- Full Bass Response Without Attenuation

- No Pop on start-up or power-down

- SNR of 105dB

- Reduced BOM Cost

- Class H reduces power consumption by as much as 45% at typical listening levels

- Low Quiescent Current

- 180mW Per Channel into 16Ω

- Charge-pump allows for true ground centered outputs

- Independent Left/Right Volume and Mute Control

- Power Supply Voltage Range: 2.5 V to 5.5 V

- High Power Supply Rejection Ratio (>100 dB PSRR)

- Differential Inputs for Maximum Noise Rejection Ratio (90 dB CMRR)

- Optional register controlled High-Impedance

Outputs When Disabled

- GPIO Control for Hardware Shutdown

- Advanced Finer Control via Register control

- 20 Pin, 4 mm x 4 mm QFN RoHS Package

|                                                                                                           | BLOCK DIAGRAMS<br>DESCRIPTION                                                            |  |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| J. I. IIICIIIdi                                                                                           | Oscillator                                                                               |  |

|                                                                                                           | 3.1.0.1. Oscillator Control Register                                                     |  |

|                                                                                                           |                                                                                          |  |

|                                                                                                           | 3.1.0.2. Oscillator Control Register                                                     |  |

|                                                                                                           |                                                                                          |  |

|                                                                                                           | one/ DirectConnect™                                                                      |  |

|                                                                                                           | Headphone Amplifiers                                                                     |  |

| 4.1.2.                                                                                                    | Volume Control                                                                           |  |

|                                                                                                           | 4.1.2.1. Volume Control Register                                                         |  |

|                                                                                                           | Current Limiter                                                                          |  |

| 4.1.4.                                                                                                    | Anti-pop Circuit                                                                         |  |

|                                                                                                           | 4.1.4.1. Click and Pop                                                                   |  |

|                                                                                                           | 4.1.4.2. Anti Pop Control Register                                                       |  |

|                                                                                                           | Short-Circuit Protection                                                                 |  |

|                                                                                                           | Pump                                                                                     |  |

|                                                                                                           | of Operation                                                                             |  |

|                                                                                                           | tection and Configuration Algorithm                                                      |  |

|                                                                                                           | Shutdown                                                                                 |  |

| 4.5.1.                                                                                                    | Thermal Shutdown Registers                                                               |  |

|                                                                                                           | 4.5.1.1. Temp Sensor Control/Status                                                      |  |

|                                                                                                           | 4.5.1.2. Headphone Thermal Shutdown Control Register                                     |  |

| 4.6. Asynchr                                                                                              | onous I2C                                                                                |  |

| 4.6.1.                                                                                                    | I2C, 2-Wire Control Interface                                                            |  |

|                                                                                                           | 4.6.1.1. Register Write Cycle                                                            |  |

|                                                                                                           | 4.6.1.2. Register Burst Write Cycle                                                      |  |

|                                                                                                           | 4.6.1.3. Register Read Cycle                                                             |  |

|                                                                                                           | 4.6.1.4. Page Register Burst Read Cycle                                                  |  |

| . REGISTERS                                                                                               | 3                                                                                        |  |

|                                                                                                           | 5.0.0.1. Control Register                                                                |  |

|                                                                                                           | 5.0.0.2. Control Register                                                                |  |

|                                                                                                           | 5.0.0.3. Control Register                                                                |  |

|                                                                                                           | 5.0.0.4. Control Register                                                                |  |

|                                                                                                           | 5.0.0.5. Control Register                                                                |  |

|                                                                                                           | 5.0.0.6. Control Register                                                                |  |

|                                                                                                           | 5.0.0.7. Control Register                                                                |  |

|                                                                                                           | 5.0.0.8. Control Register                                                                |  |

|                                                                                                           | 5.0.0.9. Control Register                                                                |  |

|                                                                                                           | 5.0.0.10. Control Register                                                               |  |

| 5.1. Register                                                                                             | r Map                                                                                    |  |

|                                                                                                           | Register Map Summary Table                                                               |  |

|                                                                                                           | URATION AND DESCRIPTION                                                                  |  |

|                                                                                                           | QFN TSCS10XX                                                                             |  |

|                                                                                                           | QFN TSCS11XX                                                                             |  |

|                                                                                                           | le for pin QFN package                                                                   |  |

|                                                                                                           | NCTION                                                                                   |  |

|                                                                                                           | RISTICS                                                                                  |  |

| CHARACIE                                                                                                  | idelity                                                                                  |  |

|                                                                                                           | al Specifications                                                                        |  |

| 7.1. Audio Fi                                                                                             | Absolute Maximum Ratings:                                                                |  |

| 7.1. Audio Fi<br>7.2. Electrica                                                                           |                                                                                          |  |

| 7.1. Audio Fi<br>7.2. Electrica<br>7.2.1.                                                                 |                                                                                          |  |

| 7.1. Audio Fi<br>7.2. Electrica<br>7.2.1.<br>7.3. Recomn                                                  | nended Operating Conditions                                                              |  |

| 7.1. Audio Fi<br>7.2. Electrica<br>7.2.1.<br>7.3. Recomn<br>7.4. Characte                                 | nended Operating Conditions                                                              |  |

| 7.1. Audio Fi<br>7.2. Electrica<br>7.2.1.<br>7.3. Recomn<br>7.4. Charact<br>7.5. Low Pov                  | nended Operating Conditions<br>eristics<br>wer Mode Power Consumption                    |  |

| 7.1. Audio Fi<br>7.2. Electrica<br>7.2.1.<br>7.3. Recomn<br>7.4. Charact<br>7.5. Low Pov<br>8. APPLICATIO | nended Operating Conditions<br>eristics<br>wer Mode Power Consumption<br><b>DN NOTES</b> |  |

| 7.1. Audio Fi<br>7.2. Electrica<br>7.2.1.<br>7.3. Recomm<br>7.4. Charact<br>7.5. Low Pov<br>6. APPLICATIO | nended Operating Conditions<br>eristics<br>wer Mode Power Consumption                    |  |

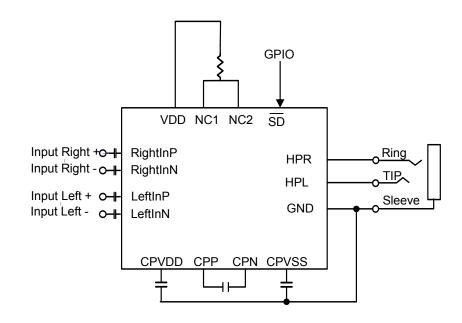

| Figure 1. Block Diagram                                                                               | 5  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2. conventional headphone amplifier connection to the headphone jack and output signal diagram |    |

| Figure 3. Page Register Write -2 Wire Serial Control Interface                                        | 14 |

| Figure 4. Page Register Burst Write Cycle                                                             | 15 |

| Figure 5. Page Register Single Byte Read Cycle                                                        | 15 |

| Figure 6. Page Register Burst Multi-byte Read Cycle                                                   | 16 |

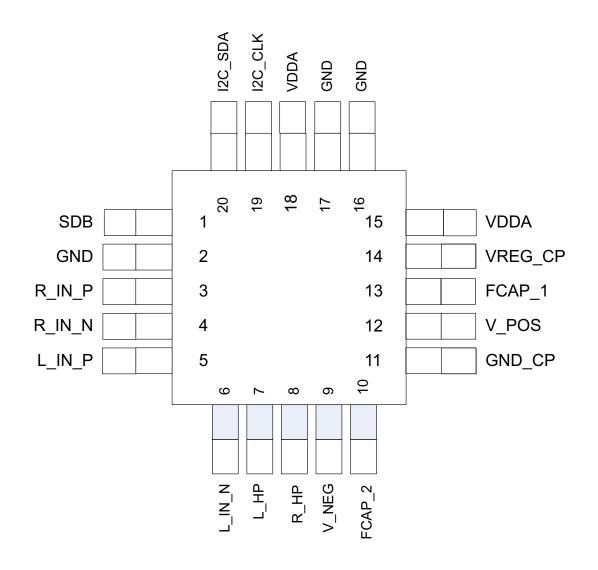

| Figure 7. 20-Pin TSDP1xxQFN                                                                           | 23 |

| Figure 8. 20-Pin TSDP11XX QFN                                                                         | 24 |

#### **1. PRODUCT OVERVIEW**

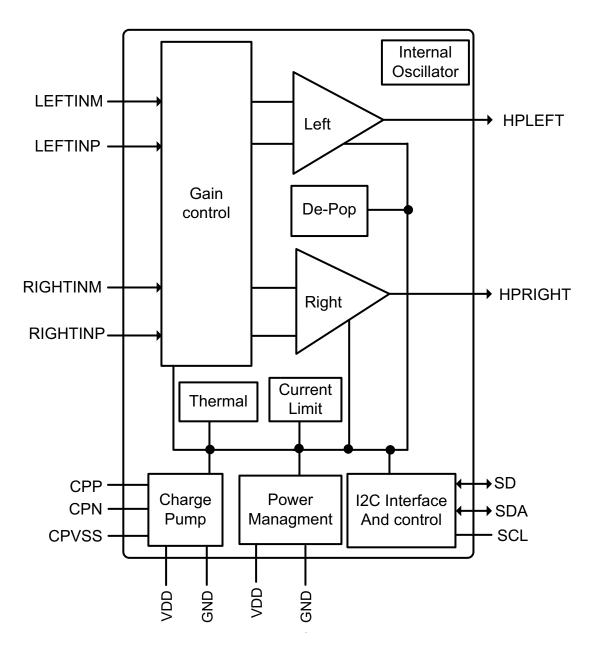

The TSDP1xx stereo Class H Capless DirectConnect<sup>™</sup> headphone amplifier is optimally designed for portable applications. The GPIO control allows the device to be put in a low power shutdown mode. The TSDP1xx is a high fidelity amplifier with SNR of 104dB. With a PSRR greater than 90dB. The TSDP1xx can be connected directly to a battery without compromising the listening experience. The output noise of 6.3µVrms (typical *A-weighted*) provides a minimal noise background during periods of silence. Configurable differential inputs and high CMRR allow for maximum noise rejection in the noisy mobile environment.TSDP1xx is available in a 4x4mm QFN package. The TSDP1xx stereo headphone DirectConnect<sup>™</sup> architecture eliminates the large output coupling capacitors typically required for single-supply headphone drivers. The device consists of two 210mW Class AB headphone drivers, supply controlled with Class H charge-pump, shutdown control, and comprehensive click-and-pop suppression circuitry. The charge pump uses VREG to create a positive supply (CPVDD) and inverts VREG to create a negative supply (CPVSS). The headphone drivers operate from these bipolar supplies with their outputs biased around GND. The drivers have almost twice the supply range compared to other 3V/5V single-supply drivers, increasing the available output power. Additionally, by being biased around physical GND, the typical power-on pops and clicks are eliminated.

The benefit of this GND bias is that the driver outputs do not have the typical VDD/2 DC component. The large DC-blocking capacitors are unnecessary, thus improving frequency response while conserving board space and system cost. Each channel has independent left/right, software controlled gain and mute, this makes it possible to optimize power savings and click-and-pop suppression in mixed-mode operation, mono/stereo click-and-pop suppression that eliminates audible transients on startup and shutdown. Additionally, the TSDP1xxfeatures thermal overload and short-circuit protection.

### 2. DETAILED BLOCK DIAGRAMS

Figure 1. Block Diagram

#### 3. FUNCTION DESCRIPTION

### 3.1. Internal Oscillator

The TSDP1xx uses an internal oscillator to generate a master reference clock. This clock is used to run the charge pump, anti-pop circuitry monitor the chip temperature sensor and shutdown circuitry. The oscillator runs at 830kHz(typical). The internal oscillator can be varied with register control. The adjustment of frequency can be done with registers if needed.

| Register Address                   | Bit | Label                  | Туре | Default | Description                                                                                                          |  |  |  |

|------------------------------------|-----|------------------------|------|---------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Reg 22<br>SELF_OSC_CTRL1<br>(15Ch) | 7:6 | SELFOSC_DIV<br>CLK_SEL | RW   | 0h      | Selects the initial divider from the selfosc input clock<br>to be used for the chopping clock & apopclock<br>setting |  |  |  |

|                                    | 5:4 | SELFOSC_VC<br>HP_SEL   | RW   | 0h      | Selects the divider from the selfosc input clock to be used for the Charge Pump clock setting                        |  |  |  |

|                                    | 3:0 | SELFOSC_FRE<br>Q_SEL   | RW   | 5h      | Selects the desired output frequency setting                                                                         |  |  |  |

3.1.0.1. Oscillator Control Register

| 3.1.0.2. | Oscillator Control Register |

|----------|-----------------------------|

|----------|-----------------------------|

| Register Address         | Bit | Label                    | Туре | Default | Description                                                                          |

|--------------------------|-----|--------------------------|------|---------|--------------------------------------------------------------------------------------|

|                          | 7:5 | RESERVED                 | RO   | 0h      | Reserved                                                                             |

|                          | 4   | SELFOSC_PW<br>D          | RW   | 0h      | Powers down (i.e. when high) the self oscillator circuitry                           |

| Reg 23<br>SELF_OSC_CTRL2 | 3   | SELFOSC_RST<br>B         | RW   | 1h      | resets (i.e. when low) the dflops in the divider circuitry                           |

| (16h)                    | 2   | SELFOSC_CH<br>PRCLK_PWDB | RW   | 0h      | Powers down (i.e. when low) the chopping clock output                                |

|                          | 1   | SELFOSC_AP<br>OPCLK_PWDB | RW   | 1h      | Powers down (i.e. when low) the antipop clock output (i.e. also used for tempsensor) |

|                          | 0   | SELFOSC_AP<br>OPCLK_SEL  | RW   | 0h      | Selects the desired output frequency for the apopclock setting                       |

### 4. AUDIO INPUTS

The TSDP1xx provides differential audio analog inputs

#### 4.1. Headphone/ DirectConnect™

Single-supply headphone drivers traditionally have their outputs biased about a half the nominal DC voltage for maximum dynamic range. In other words, to block the DC bias, large capacitors are needed to couple the signal to the headphone driver. Without these capacitors, wasted large DC current will unnecessarily flow to the headphone speaker, and possibly damage both headphone driver and/or speaker. The Capless DirectConnect<sup>™</sup> architecture uses charge pump to create an internal negative supply. This allows the outputs of the TSDP1xx to be centered around GND. In addition, the creation of the negative internal supply doubles the dynamic range while operating from a single supply. With the ground (GND) reference, there is no need for the large DC-blocking capacitors. Instead of two large very linear capacitors that can be as much as 220µF (often tantalum capacitors for linearity), the TSDP1xx charge pump requires four small value capacitors. This reduces board space and BOM cost, while improving the frequency response of the headphone driver.

The HPR/HPL pins can drive a  $16\Omega$ ,  $32\Omega$  headphone load or line output load up to  $10K\Omega$  without any external components. The signal volume of the headphone amplifier volume can be independently adjusted under software control by writing to HPVOL\_L and HPVOL\_R. Also setting the volume to 00000 will power down amp. The amplifier can be set to mute by enabling the mute register or setting the volume to 00010. The output remains at ground, so that no click noise is produced when muting or un-muting. Gains above 0dB run the risk of clipping large signals.

#### 4.1.1. Headphone Amplifiers

Single-supply headphone amplifiers typically require dc-blocking capacitors. The capacitors are required because most headphone amplifiers have a dc bias on the outputs pin. If the dc bias is not removed, the output signal is severely clipped, and large amounts of dc current rush through the headphones, potentially damaging them. The functional diagram shown above illustrates the conventional headphone amplifier connection to the headphone jack and output signal. DC blocking capacitors are typically large in value to avoid attenuation of Bass (or low frequency) content. The headphone speakers (typical resistive values of  $16\Omega$  or  $32\Omega$ ) combine with the dc blocking capacitors to form a high-pass filter. Equation 1 shows the relationship between

the load impedance (RL), the capacitor (CO), and the pass frequency (fC).

$$F_{c} = \frac{1}{2\pi * R_{L} * C_{0}}$$

(1)

Co can be determined from (1), where the load impedance and the cutoff frequency are known thus:

$$C_0 = \frac{1}{2\pi * R_L * F_c}$$

If fc is low, the capacitor must then have a large value because the load resistance is small. Large capacitance values require large package sizes. Large package sizes consume PCB area, stand high above the PCB, increase cost of assembly, and can reduce the fidelity of the audio output signal.

(2)

#### 4.1.2. Volume Control

The TSDP1xx features two independent controls for left/right volume ranging from +6dB to -22dB and mute. Changes in volume are walked automatically to the new target volume using an advanced pop suppression circuitry which eliminates unwanted audio pops and clicks at the output.

Channel volume can be controlled across a gain and attenuation range of -22dB to +6dB (1.0dB steps). The level of attenuation is specified by 5-bit code 'VOL\_x', where 'x' is L, or R. The value 00010" indicates mute; other values describe the number of 1.0dB steps above -22dB.

| 4.1.2.1. Volume Control Register |     |                        |      |         |                                                                                                                                                                                                           |  |  |

|----------------------------------|-----|------------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register Address                 | Bit | Label                  | Туре | Default | Description                                                                                                                                                                                               |  |  |

|                                  | 7   | RESERVED               | RW   | 0       | Reserved                                                                                                                                                                                                  |  |  |

|                                  | 6   | HP_DISCHOP_AN<br>TIPOP | RW   | 1       | Disables the chopping for antipop when high.<br>Only turns chopping at power up/down (i.e.<br>code 1) on when both d2a_dischop_antipop<br>low and d2a_dischop_amp is high.                                |  |  |

| Reg 19<br>HDPH_CTR2((12h)        | 5   | HP_DISCHOP_AM<br>P     | RW   | 1       | Will enable chopping always when low and disable chopping when high.                                                                                                                                      |  |  |

|                                  | 4:0 | HP_CNT_TARGET<br>_L    | RW   | 10      | Sets the left channel final target gain for the<br>anti-pop ramping circuitry (00000==><br>pwd,00010==> mute,00011==> -22.8919dB,<br>10000b==> 0dB, 10100b ==> +2dB, 11001b<br>==> +4dB, 11111b ==> +6dB) |  |  |

|                                  | 7   | RESERVED               | RW   | 0       | Reserved                                                                                                                                                                                                  |  |  |

|                                  | 6   | RESERVED               | RW   | 0       | Reserved                                                                                                                                                                                                  |  |  |

| Reg 20                           | 5   | RESERVED               | RW   | 0       | Reserved                                                                                                                                                                                                  |  |  |

| HDPH_CTRL3(13h)                  | 4:0 | HP_CNT_TARGET<br>_R    | RW   | 10      | Sets the right channel final target gain for the<br>anti-pop ramping circuitry (10000b==> 0dB,<br>10100b ==> +2dB, 11001b ==> +4dB, 11111b<br>==> +6dB)                                                   |  |  |

#### 4.1.3. Current Limiter

Advanced short-circuit protection protects amplifier outputs from shorting conditions

To avoid damage to the outputs if a short circuit condition should occur, the headphone amplifier implements a current limiter protection circuits. The headphone output amplifier will detect the load current and limit its output if in an over current state.

| Register Address          | Bit | Label    | Туре | Default | Description                                                                                                                      |

|---------------------------|-----|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------|

|                           | 7:6 | HP_ILIM  | RW   | 3h      | Sets the current output limit for the headphones (i.e.<br>00b ==> powerdown, 01b ==> ~ 100mA, 10b ==><br>~150mA, 11b ==> ~200mA) |

|                           | 5   | HPL_PWD  | RW   | 0h      | Left Headphone power down                                                                                                        |

|                           | 4   | HPR_PWD  | RW   | 0h      | Right Headphone power down                                                                                                       |

| Reg 18<br>HDPH CTRL1(11h) | 3   | RESERVED | RW   | 0h      | Reserved.                                                                                                                        |

|                           | 2   | RESERVED | RW   | 0h      | Reserved.                                                                                                                        |

|                           | 1   | HPL_MUTE | RW   | 0h      | Left Headphone mute (sets ampfiier to unity gain with postive differential input set to GNDA)                                    |

|                           | 0   | HPR_MUTE | RW   | 0h      | Right Headphone mute (sets ampfiier to unity gain with postive differential input set to GNDA)                                   |

#### 4.1.4. Anti-pop Circuit

Advanced anti-pop circuit prevents amplifier outputs from creating audible pop conditions

#### 4.1.4.1. Click and Pop

Due to the nature of power management and audio path configurability, many situations will introduce undesirable sounds. It is not possible to prevent loud pops in all situations, but it is desired to prevent pops under many situations. The headphone should be fully powered down prior to removal of VDD

| State Change       | Description                   | Desired<br>(dBV Awt) |

|--------------------|-------------------------------|----------------------|

| Application of VDD | Headphone Output 10K-ohm load | -65                  |

| Application of VDD | Headphone Output 32-ohm load  | -65                  |

| Removal of VDD     | Headphone Output 10K-ohm load | -65                  |

| Removal of VDD     | Headphone Output 32-ohm load  | -65                  |

Table 1.

| 4.1.4.2. | Anti Pop Control Register |

|----------|---------------------------|

|----------|---------------------------|

| Register Address          | Bit | Label                  | Туре | Default | Description                                                                                                                                                                                                                                                    |

|---------------------------|-----|------------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | 7   | RESERVED               | RW   | 0h      | Reserved                                                                                                                                                                                                                                                       |

|                           | 6   | RESERVED               | RW   | 0h      | Reserved                                                                                                                                                                                                                                                       |

|                           | 5   | RESERVED               | RW   | 1h      | Reserved                                                                                                                                                                                                                                                       |

|                           | 4   | HP_OUTGND_<br>REG      | RW   | 0h      | Register used to control the headphone output grounding switch when d2a_hp_outgnd_ovrd is set high                                                                                                                                                             |

| Reg 21<br>HDPH_CTRL4(14h) | 3   | HP_OUTGND_<br>OVRD     | RW   | 0h      | Over rides (i.e. when high) the antipop ramping control of the headphone output grounding switch with value from "d2a_hp_outgnd_reg"                                                                                                                           |

|                           | 2   | RESERVED               | RW   | 0h      | Reserved                                                                                                                                                                                                                                                       |

|                           | 1   | RESERVED               | RW   | 0h      | Reserved                                                                                                                                                                                                                                                       |

|                           | 0   | HP_CONNECT<br>_GND_VAG | RW   | 1h      | Turns on switches (i.e. when high) at the<br>differential inputs to reference inputs to ground<br>(i.e. DC blocking caps cause inputs to need<br>reference). This was mainly added incase we<br>needed to tristate inputs for Global Headset<br>functionality. |

### 4.1.5. Short-Circuit Protection

The right channel and left channel audio outputs have independent current limit detection circuits with common register control settings. The current limit can be set to ~100mA , ~150mA, ~200mA, or the protection circuit can be disabled.

The current limiting allows limiting the power delivered to the load without disabling the amplifiers. The lowest setting allows limiting the power delivered to the load to just above 1VRMS into a 16 ohm load while still protecting against a short circuit event. The highest setting protects against a short circuit event while still delivering the maximum power into a 16 ohm load.

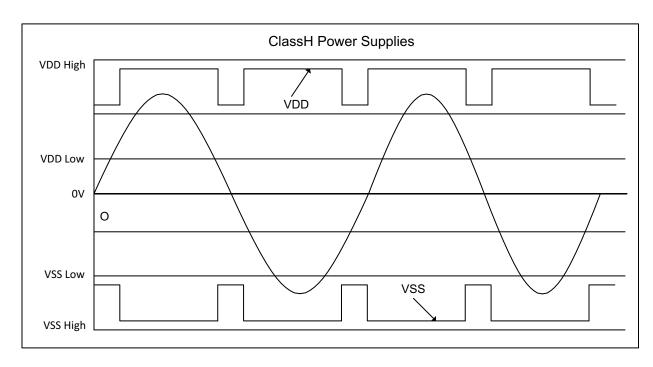

### 4.2. Charge Pump

#### Charge Pump Class H

The TSDP1xx features 830kHz switching low-noise charge pump architecture. The architecture features controlled switching that minimizes noise generated by turn-on and turn-off transients. The switching frequency is well beyond the audio range, and does not interfere with the audio signals. By controlling the Clocking of the switches, the impulse current noise caused by the parasitic bond wire and trace inductance is minimized or completely eliminated. Although not typically required, additional high-frequency noise attenuation can be achieved by increasing the size of the capacitor at CPVSS to CPGND, CPVDD to CPGND as well as CFLY (fly cap) between CPFP and CPFN. The TSDP1xxclass H amplifier employs a class AB output stage with power-supply voltages that are adjusted based on the output signal level. The output stage senses the output voltage level and adjusts the charge pump supply voltage dynamically. As indicated in the figure below, the adjustment is made on a cycle by cycle basis. Thus when the music level is small, the charge pump supply voltage is correspondingly decreased; and when the music level is high, the charge pump voltage is increased. For typical listening level, this feature can lower the power used in playback mode by almost 45% thus extending battery life by several hours or alternatively the designer could save BOM cost and board space by using smaller battery.

#### **Charge Pump Capacitors**

The VREG output (i.e. pin14) should have a 10uF capacitor to ensure both stability and reduced ripple on the LDO output while supplying power to create the class H output supplies. The charge pump outputs CPVDD (pin 12), CPVSS (pin 9) are the class H output supplies providing power to the headphone amplifiers and should each be decoupled to ground with 5uF capacitors. The generated supply voltage across these capacitors will change dependent on the combination of the two headphone output signal levels. A 5uF capacitance should also be placed across the CPFP (pin 13) and CPFN (pin 10) nodes. This capacitor helps create the positive (CPVDD) and negative (CPVSS) supply voltages via charge sharing. Providing a 10uF to the VDD (pin 15) will help to reduce instantaneous demands from the power supply when providing

power to the LDO. It should be noted that using a 0.1uF ceramic capacitor in parallel with the larger Tantalum capacitors at all supply pins can help to reduce unwanted high frequency noise on the supplies at the pins.

#### Short-Circuit Protection

The Charge Pump also has short circuit detection circuitry which will disable the Charge Pump if a short circuit causes too large a current demand. The Charge Pump will be disabled for 511 charge pump clock cycles and then re-enabled for 63 charge pump clock cycles to see if the short circuit event has been removed. This algorithm will continue until the short circuit event has been removed.

| Register Address       | Bit | Label            | Туре | Default | Description                                                                                                                                                                                     |

|------------------------|-----|------------------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        | 7:4 | 0]               | RO   | 0       | Reserved.                                                                                                                                                                                       |

| Reg14                  | 3   | RESVERED         | RW   | 1       | resets (i.e. when low)the dflop used to latch the<br>output of the comparator detecting Charge<br>Pump Short Circuit event and resets the LSFR<br>used to time the short circuit event checking |

| CP_SCUR_CTRL1<br>(0Dh) | 2   | VCHP_SC_PW<br>D  | RW   | 0       | Powers down the Charge Pumpe Short Circuit block                                                                                                                                                |

|                        | 1   | VCHP_SC_BYP<br>S | RW   | 0       | Bypasses the Short Circuit Event and forces<br>Charge Pump to keep running                                                                                                                      |

|                        | 0   | RESVERED         | RW   | 0       | Reserved                                                                                                                                                                                        |

#### 4.3. Modes of Operation

HiZ is enabled, when the headphone amplifiers are powered down, by writing logic 1 in register 14 (i.e. HDPH\_CTRL4), bit 3 and ensuring that register 14 bits 4 and 0 are set to logic 0. Place logic 0 in register 14, bit 3 and logic 1 in register 14 bit 0 to disable the HiZ state of the outputs. The HiZ state puts the headphone outputs into a state of high impedance. Use this configuration when the outputs of the TSDP1xxshare traces with other devices whose outputs may be active.

### 4.4. Jack Detection and Configuration Algorithm

The "SD" pin of the TSDP1xxcan be utilized to effect a Jack Detection and power up the chip when a plug is in inserted in to the Jack. The Jack pin connected to the SD pin should be default ground prior to inserting the plug and pulled to VDDA when the plug is inserted into the JACK

#### 4.5. Thermal Shutdown

There are 2 trip points, "high" and "low". The "high" trip point should always be set to a higher value than the "low" trip point. If the temperature of the chip increases above the "high" trip point, the headphone outputs will be powered down which will cause the output volumes to be decreased from the current volume toward mute and then the amplifiers will be powered down. The amplifiers will not be powered back up until the temperature on the chip has reduced to the "low" trip point. When the temperature drops below the "low" trip point, the amplifiers will be allowed to power back up and ramp back to the original volume setting. With proper settings on the clock division multiplexers, the "high" and "low" trip points are polled every ~1.5msec or ~3msec.

#### 4.5.1. Thermal Shutdown Registers

#### 4.5.1.1. Temp Sensor Control/Status

The temperature sensor circuit is configured and monitored using the Temp Sensor Control/Status Register

| Register Address                                                      | Bit | Label            | Туре | Default | Description                                                                                                                                         |

|-----------------------------------------------------------------------|-----|------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Reg 28-<br>TEMP_SENSE_CT<br>RL1(1Bh)<br>Temp Sensor<br>Control/Status | 7:5 | HI_TEMP_SEL      | RW   | 3       | Temp sensor block hi trip points (<br>000b==>110C, 001b==>125C, 010b==>140C,<br>011b==>155C, 100b==>170C, 101b==>185C,<br>110b==>200C,111b==>215C)  |

|                                                                       | 4:2 | LO_TEMP_SEL<br>] | RW   | 2       | Temp sensor block low trip points (<br>000b==>110C, 001b==>125C, 010b==>140C,<br>011b==>155C, 100b==>170C, 101b==>185C,<br>110b==>200C,111b==>215C) |

|                                                                       | 1:0 | VBG_TRIM_SE<br>L | RW   | 1       | Adjusts the VBG voltage in the Tempsensor by<br>8mV increments (i.e. 00 ==> 1.215V, , 01b ==><br>1.223V, 10b ==> 1.2318V, 11b ==> 1.24V)            |

#### 4.5.1.2. Headphone Thermal Shutdown Control Register

The thermal shutdown algorithm is configured using the Speaker Thermal Algorithm Control Register

| Register Address                                | Bit | Label              | Туре | Default | Description                                     |

|-------------------------------------------------|-----|--------------------|------|---------|-------------------------------------------------|

|                                                 | 7:3 | RESERVED           | RO   | 0       | Reserved                                        |

| Reg 29<br>TEMP_SENSE_CT                         | 2   | RESERVED           | RW   | 0       | Reserved                                        |

| RL2(1Ch)<br>Speaker Thermal<br>Shutdown Control | 1   | TEMPSENSE_<br>PWD  | RW   | 0       | Temp sensor power down 1b=power down            |

| Chataown Control                                | 0   | TEMPSENSE_<br>RSTB | RW   | 1       | Temp sensor reset-0b, reset the tempsense logic |

### 4.6. Asynchronous I2C

#### 4.6.1. *I*<sup>2</sup>C, 2-Wire Control Interface

The TSDP1xx device includes a 2-Wire  $I^2C$  compatible interface for communicating with an external controller. This interface supports communication to external micro-controller or other  $I^2C$  compatible peripheral chips. The  $I^2C$  interface supports normal and fast mode operation.

#### **Device Address Register 0**

| Register Address | Bit | Label         | Туре | Default | Description                 |

|------------------|-----|---------------|------|---------|-----------------------------|

| Reg 1            | 7:1 | DEV_ADD0[6:0] | RW   | 68      | Register I2C Device Address |

| DEVADD0((00h)    | 0   | RSVD          | R    | 0       | Reserved                    |

#### TSDP1xx

**Headphone Amplifier**

#### **Device Identification Register**

| Register Address    | Bit | Label       | Туре | Default       | Description                                                                                                  |

|---------------------|-----|-------------|------|---------------|--------------------------------------------------------------------------------------------------------------|

| Reg 2<br>DEVID(01h) | 7:0 | DEV_ID[7:0] | R    | 01000x<br>xxb | 8-bit device identification number. The least significant three bits reflect the state of the Bond-Out pins. |

#### **Device Revision Register**

| Register Address | Bit | Label        | Туре | Default | Description                                                                                         |

|------------------|-----|--------------|------|---------|-----------------------------------------------------------------------------------------------------|

| Reg 3            | 7:4 | MAJ_REV[3:0] | R    | 0001    | 4-bit major revision number (all layer)<br>currently = 1 (1st release)<br>MMMM.mmmm currently = 1.0 |

| DEVREV(02h)      | 3:0 | MIN_REV[3:0] | R    | 0000    | 4-bit minor revision number (metal revision)<br>currently = 0 (no revisions-initial release)        |

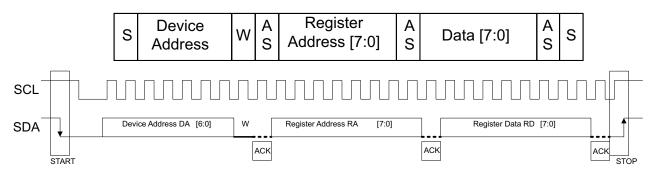

#### 4.6.1.1. Register Write Cycle

The controller indicates the start of data transfer with a high to low transition on SDA while SCL remains high, signalling that a device address and data will follow. All devices on the 2-wire bus respond to the start condition and shift in the next eight bits on SDIN (7-bit address + Read/Write bit, MSB first). If the device address received matches the address of the TSDP1xx and the R/W bit is '0', indicating a write, then the TSDP1xx responds by pulling SDA low on the next clock pulse (ACK); otherwise, the TSDP1xx returns to the idle condition to wait for a new start condition and valid address.

Once the TSDP1xx has acknowledged a correct device address, the controller sends the TSDP1xx register address. The TSDP1xx acknowledges the register address by pulling SDA low for one clock pulse (ACK). The controller then sends a byte of data (B7 to B0), and the TSDP1xx acknowledges again by pulling SDA low.

When there is a low to high transition on SDA while SCL is high, the transfer is complete. After receiving a complete address and data sequence the TSDP1xx returns to the idle state. If a start or stop condition is detected out of sequence, the device returns to the idle condition.

Figure 3. Page Register Write -2 Wire Serial Control Interface

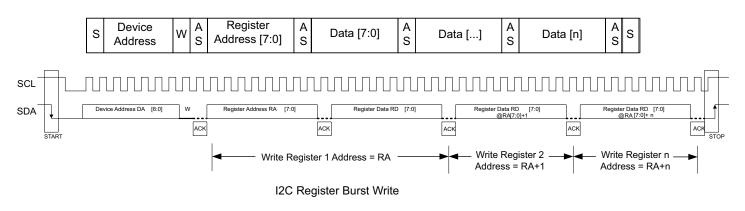

#### 4.6.1.2. Register Burst Write Cycle

The controller may write more than one register within a single write cycle. To write additional registers, the controller will not generate a stop or start (repeated start) command after receiving the acknowledge for the second byte of information (register address and data). Instead the controller will continue to send bytes of data. After each byte of data is received, the register address is incremented.

Figure 4. Page Register Burst Write Cycle

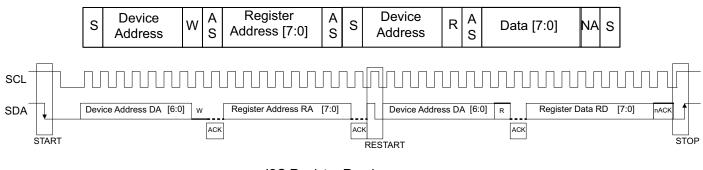

#### 4.6.1.3. Register Read Cycle

The controller indicates the start of data transfer with a high to low transition on SDA while SCL remains high, signalling that a device address and data will follow. If the device address received matches the address of the TSDP1xx and the R/W bit is '0', indicating a write, then the TSDP1xx responds by pulling SDA low on the next clock pulse (ACK); otherwise, the TSDP1xx returns to the idle condition to wait for a new start condition and valid address.

Once the TSDP1xx has acknowledged a correct address, the controller sends a restart command (high to low transition on SDA while SCL remains high). The controller then re-sends the devices address with the R/W bit set to '1' to indicate a read cycle. The TSDP1xx acknowledges by pulling SDA low for one clock pulse. The controller then receives a byte of register data (B7 to B0).

For a single byte transfer, the host controller will not acknowledge (high on data line) the data byte and generate a low to high transition on SDA while SCL is high, completing the transfer. If a start or stop condition is detected out of sequence, the device returns to the idle condition.

I2C Register Read

Figure 5. Page Register Single Byte Read Cycle

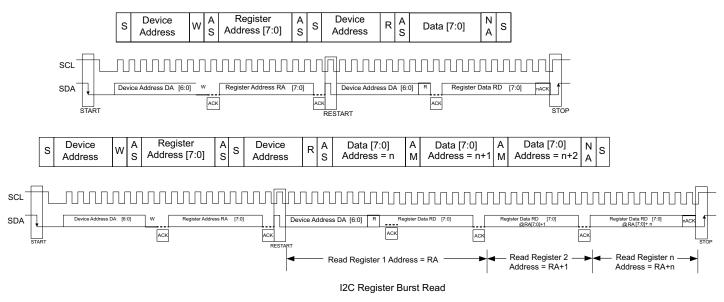

#### 4.6.1.4. Page Register Burst Read Cycle

The controller may read more than one register within a single read cycle. To read additional registers, the controller will not generate a stop or start (repeated start) command after sending the acknowledge for the byte of data. Instead the controller will continue to provide clocks and acknowledge after each byte of received data. The TSDP1xx will automatically increment the internal register address after each register has had its data successfully read (ACK from host) but will not increment the register address if the data is not received correctly by the host (nACK from host) or if the bus cycle is terminated

unexpectedly. By automatically incrementing the internal register address after each byte is read, all the internal registers of the TSDP1xx may be read in a single read cycle.

Figure 6. Page Register Burst Multi-byte Read Cycle

## 5. REGISTERS

| Register Address      | Bit | Label               | Туре | Default | Description                                                                                             |

|-----------------------|-----|---------------------|------|---------|---------------------------------------------------------------------------------------------------------|

|                       | 7   | VREG_SC_DE<br>T     | RO   | 0h      | Short Circuit Detected on LDO output when<br>high( Requires vreg_sc_rstb in Reg8(07h) to be<br>toggled) |

|                       | 6   | VDDA_BELOW<br>_3P1V | RO   | 0h      | Detects VDDA supply level for 2.5V operation (i.e. trip ~3.1V)                                          |

|                       | 5   | SUPPLY_OSC          | RO   | 0h      | Detects VDDA supply level for 3.3 to 5V operation (i.e. trip ~4.16V)                                    |

| Reg 4<br>STATUS0(03h) | 4   | RESERVED            | RO   | 0h      | Reserved                                                                                                |

|                       | 3   | RESERVED            | RO   | 0h      | Reserved                                                                                                |

|                       | 2   | TEMP_OVERH<br>EAT   | RO   | 0h      | Temp sensor statemachine overheat output.                                                               |

|                       | 1   | OVERHEAT_HI<br>GH   | RO   | 0h      | Temp sensor high overheat indicator.                                                                    |

|                       | 0   | OVERHEAT_L<br>OW    | RO   | 0h      | Temp sensor low overheat indicator.                                                                     |

5.0.0.1. Control Register

5.0.0.2. Control Register

| Register Address      | Bit | Label       | Туре | Default | Description                                                                                    |

|-----------------------|-----|-------------|------|---------|------------------------------------------------------------------------------------------------|

|                       | 7:2 | RESERVED    | RO   | 0h      | Reserved                                                                                       |

| Reg 5<br>STATUS1(04h) | 1   | SD          | RO   | 0h      | Input signal Shutdown from Pin.                                                                |

|                       | 0   | VCHP_SC_DET | RO   | 0h      | Short Circuit Detected on Charge Pump VPOS or VNEG output when high( Will automatically reset) |

| Register Address       | Bit | Label                  | Туре | Default | Description                 |  |  |  |  |  |

|------------------------|-----|------------------------|------|---------|-----------------------------|--|--|--|--|--|

|                        | 7   | DELAY_MODE             | RW   | 0h      | Reserved                    |  |  |  |  |  |

|                        | 6   | MODE_DELAY<br>_BYPS    | RW   | 1h      | Reserved                    |  |  |  |  |  |

| Reg 6<br>CP_CTRL1(05h) | 5:3 | VCHP_CLKSEL            | RW   | 1h      | Reserved                    |  |  |  |  |  |

|                        | 2   | VCHP_HIZ_VP<br>OS_OVRD | RW   | 0h      | Reserved                    |  |  |  |  |  |

|                        | 1   | VCHP_HIZ               | RW   | 0h      | Reserved                    |  |  |  |  |  |

|                        | 0   | VCHP_PWD               | RW   | 0h      | Powers down the Charge Pump |  |  |  |  |  |

#### 5.0.0.3. Control Register

### 5.0.0.4. Control Register

| Register Address       | Bit | Label           | Туре | Default | Description                                                                                                              |

|------------------------|-----|-----------------|------|---------|--------------------------------------------------------------------------------------------------------------------------|

|                        | 7:4 | RESERVED        | RO   | 0h      | Reserved                                                                                                                 |

| Reg 7<br>CP_CTRL2(06h) | 3   | AB_OVR_MOD<br>E | RW   | 0h      | When "d2a_ab_ovr_en" is high, this bit will<br>select the mode of operation (i.e. 0==> Split<br>Mode, 1 ==> Invert Mode) |

|                        | 2   | AB_OVR_EN       | RW   |         | Enables the over riding of the automatic Class<br>H operation when high                                                  |

|                        | 1:0 | DROP_SEL        | RW   | 0h      | Timing options for delaying the change from Invert to Split                                                              |

### 5.0.0.5. Control Register

| Register Address        | Bit | Label            | Туре | Default | Description                                                                                                               |

|-------------------------|-----|------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------|

|                         | 7   | RESERVED         | RO   | 0h      | Reserved                                                                                                                  |

|                         | 6:5 | VREG_SEL         | RW   | 2h      | Selects the output voltage setting for the<br>LDO (i.e. 00b => 2.395V, 01b ==> 2.592V,<br>10b ==> 2.793V, 11b ==> 3.076V) |

| Reg 8<br>VREG_CTRL(07h) | 4   | VREG_SC_RST<br>B | RW   | 1h      | Resets the Short Circuit detection latched output                                                                         |

|                         | 3   | RESERVED         | RW   | 0h      | Reserved                                                                                                                  |

|                         | 2   | RESERVED         | RW   | 0h      | Reserved                                                                                                                  |

| -                       | 1   | RESERVED         | RW   | 0h      | Reserved                                                                                                                  |

|                         | 0   | VREG_PWD         | RW   | 0h      | Powers down the LDO output and pulls the LDO output to ground.                                                            |

| Register Address | Bit | Label            | Туре | Default | Description                    |  |  |  |  |

|------------------|-----|------------------|------|---------|--------------------------------|--|--|--|--|

|                  | 7   | RESERVED         | RO   | 0h      | Reserved                       |  |  |  |  |

|                  | 6   | RESERVED         | RW   | 1h      | Reserved                       |  |  |  |  |

| Reg 9            | 5   | RESERVED         | RW   | 0h      | Reserved                       |  |  |  |  |

| VDDA_SENSE_CT    | 4   | RESERVED         | RW   | 0h      | Reserved                       |  |  |  |  |

| RL(08h)          | 3   | VDDSENSE_P<br>WD | RW   | 0h      | Powers down the vddsense block |  |  |  |  |

|                  | 2   | RESERVED         | RW   | 1h      | Reserved                       |  |  |  |  |

|                  | 1:0 | RESERVED         | RW   | 0h      | Reserved                       |  |  |  |  |

### 5.0.0.6. Control Register

### 5.0.0.7. Control Register

| Register Address     | Bit | Label    | Туре | Default | Description                                                      |

|----------------------|-----|----------|------|---------|------------------------------------------------------------------|

| Reg 25               | 7:1 | RESERVED | RO   | 0h      | Reserved                                                         |

| BIASG_CTRL2(18<br>h) | 0   | POR      | RW   | 0h      | This signal is Ored with the POR output to generate "a2d_por_5v" |

### 5.0.0.8. Control Register

| Register Address          | Bit | Label                | Туре | Default | Description                                    |

|---------------------------|-----|----------------------|------|---------|------------------------------------------------|

|                           | 7:4 | RESERVED             | RO   | 0h      | Reserved                                       |

| Reg 26<br>REF_SUP_CTRL(19 | 3   | REFSUPPLY<br>DET_PWD | RW   | 0h      | Powers down the refsupply detection amplifier. |

| h)                        | 2   | RESERVED             | RW   | 0h      | Reserved                                       |

|                           | 1   | RESERVED             | RW   | 0h      | Reserved                                       |

|                           | 0   | RESERVED             | RW   | 0h      | Reserved                                       |

| Register Address        | Bit | Label                  | Туре | Default | Description                                         |  |  |

|-------------------------|-----|------------------------|------|---------|-----------------------------------------------------|--|--|

|                         | 7   | SD_B_PUB               | RW   | 1h      | SD pin pull up resistor, 1 is off                   |  |  |

|                         | 6   | SD_B_PD                | RW   | 1h      | SD pin pull down resistor, 1 is on                  |  |  |

|                         | 5   | I2C_DATA_PU<br>B       | RW   | 0h      | I2C data pin pull up resistor, 0 is on              |  |  |

| Reg 30                  | 4   | I2C_DATA_PD            | RW   | 0h      | I2C data pin pull down resistor,0 is off            |  |  |

| PAD_CTRLTATUS0<br>(1Dh) | 3   | I2C_CLK_PUB            | RW   | 0h      | i2c clock pin pull up resistor, 0 is on             |  |  |

|                         | 2   | I2C_CLK_PD             | RW   | 0h      | i2c clock pin pull down resistor, 0 is off          |  |  |

|                         | 1   | CLK_DEGLITC<br>H_BYPS  | RW   | 0h      | Bypasses the deglitch circuitry in the I2C CLK pad  |  |  |

|                         | 0   | DATA_DEGLIT<br>CH_BYPS | RW   | 0h      | Bypasses the deglitch circuitry in the I2C DATA pad |  |  |

#### 5.0.0.9. Control Register

### 5.0.0.10. Control Register

| Register Address        | Bit | Label           | Туре | Default | Description                  |

|-------------------------|-----|-----------------|------|---------|------------------------------|

| Dog 21                  | 7:1 | RESERVED        | RO   | 0h      | Reserved                     |

| Reg 31<br>SHUTDOWN(1Eh) | 0   | SHOUTDOWN_<br>B | RW   | 1h      | Software Controlled Shutdown |

### 5.1. Register Map

### 5.1.1. Register Map Summary Table

#### Table 2. Register Map

| Register | Name                 | Remarks          | Bit[7]                      | Bit[6]                       | Bit[5]                     | Bit[4]                | Bit[3]                   | Bit[2]                      | Bit[1]                      | Bit[0]                      | Default |

|----------|----------------------|------------------|-----------------------------|------------------------------|----------------------------|-----------------------|--------------------------|-----------------------------|-----------------------------|-----------------------------|---------|

| R1 (00h) | DEVADD0              | Device Address 0 |                             | DEV_ADD0[6:0]                |                            |                       |                          |                             | RSVD                        | 68h                         |         |

| R2 (01h) | DEVID                | Device iD        |                             |                              |                            | DEV_AD                | DD1[6:0]                 |                             |                             |                             | 40h     |

| R3 (02h) | DEVREV               | Device Revision  |                             | MAJ_R                        | EV[3:0]                    |                       |                          | MIN_REV[3:0]                |                             |                             | 10h     |

| R4 (03h) | STATUS               | Status           | VREG_SC<br>_DET             | VDDA_BEL<br>OW_3P1V          | SUPPLY_O<br>SC             |                       |                          | TEMP_OVE<br>RHEAT           | OVERHEA<br>T_HIGH           | OVERHEA<br>T_LOW            | 00h     |

| R5 (04h) | STATUS               | Status           |                             |                              |                            |                       |                          |                             | SD                          | VCHIP_SC<br>_DET            | 00h     |

| R6 (05h) | CP_CTRL1L            | Control          | DELAY<br>MODE               | MODE_DELAY<br>_BYPAS         | v                          | CHP_CLKSE             | EL                       | VCHP_HIZ_V<br>POS_OVRD<br>] | VCHP_HIZ                    | VCHP_PWD                    | 48h     |

| R7(06h)  | CP_CTRL2             | Control          |                             |                              |                            |                       | AB_OVER_<br>MODE         | AB_OVER_<br>EN              | DRO                         | P_SEL                       | 0h      |

| R8 0(7h) | VREG_CTRL            | REG Control      |                             | VREG_SEL                     | VREG_SEL                   | VREG_RST<br>B         | VREGHA<br>LFCUR          | VREG_GND<br>SHRT            | VREG_BYP<br>AS              | VREG_PW<br>D                | 50h     |

| R9(08h)  | VDAA_SENS<br>E_CTRL  | SENSE Control    |                             | VDDSENSE_<br>VREG_SEL_<br>OV | VDDSENSE<br>_MODE_OV<br>RD | VDDSENSE<br>_HALFCUR  | VDDSENSE<br>_PWD         | VDDSENSE<br>_RSTB           | VDD_T                       | RP_SEL                      | 44      |

| R10(09h) | CLSH_SENS<br>E_CTRL1 |                  |                             | RESE                         | RVED                       |                       | REFN_SEL<br>_PWD         | REFP_SEL<br>_PWD            | HPSENSE_<br>HALFCUR         | HPSENSE_<br>PWD             | 0h      |

| R11(OAh) | CLSH_SENS<br>E_CTRL2 |                  | HP_RE                       | FNS_SEL                      | HP_RE                      | FNI_SEL               | HP_REF                   | PS_SEL                      | HP_RE                       | FPI_SEL                     | 0h      |

| R12(0Bh) | HI_CUR_CTR<br>L1     |                  |                             |                              | SW1_SW4_<br>KILL_EN        | SW_INVER<br>T_KILL_EN | SW1_WEA<br>K_STRONG<br>B |                             | STARTUP_<br>CNT_64_32<br>B  | STARTUP_<br>SW_EN           | 37h     |

| R13(0Ch) | HI_CUR_CTR<br>L2     |                  |                             |                              |                            | I                     | SW_REF                   | NS_SEL                      | SW_RE                       | FPI_SEL                     | 0h      |

| R14(0Dh) | CP_SCUR_C<br>TRL1    |                  |                             |                              |                            |                       | VCHP_SC_<br>RSTB         | VCHP_SC_<br>PWD             | VCHP_SC_<br>BYPS            | VCHP_SC_<br>HALFCUR         | 08h     |

| R15(0Eh) | CP_SCUR_C<br>TRL2    |                  | SC_RE                       | FPI_SEL                      | SC_REF                     | PS_SEL                | SC_REI                   | FNI_SEL                     | SC_REF                      | NS_SEL                      | 80h     |

| R16(0Fh) | CP_REG_CT<br>RL1     |                  |                             |                              | I                          |                       | CLKREG_R<br>STB          | CLKREG_P<br>WD              | CLKREG_B<br>YPS             | CLKREG_H<br>ALFCUR          | 08h     |

| R17(10h) | CP_REG_CT<br>RL2     |                  |                             |                              | CLKREG_                    | REFP_SEL              | CLKREG_F                 | REFNI_SEL                   | CLKREG_F                    | REFNS_SEL                   | 0h      |

| R18(11h) | HDPH_CTRL<br>1       |                  | HP_                         | _ILIM                        | HPL_PWD                    | HPR_PWD               | HP_PWD_O<br>VRD          | HP_ANTIP<br>OP_BYPAS<br>S   | HPL_MUTE                    | HPR_MUTE                    | C0h     |

| R19(12h) | HDPH_CTRL<br>2       |                  | BST_HP_G<br>AIN             | HP_DISCHO<br>P_ANTIPOP       | HP_DISCH<br>OP_AMP         |                       | HP_                      | _CNT_TARGE                  | T_L                         |                             | 10h     |

| R20(13h) | HDPH_CTRL            |                  |                             | REDUCE_HP<br>_IBAT           | HP_D3                      |                       | HP_                      | _CNT_TARGE                  | T_R                         |                             | 10h     |

| R21(14h) | HDPH_CTRL<br>4       |                  | HP_ANTIP<br>OP_CNT_L<br>OAD | HP_ANTIPO<br>P_CNT_HOL<br>D  | HP_ANTIP<br>OP_RSTB        | HP_OUTGN<br>D_REG     | HPOUTGN<br>D_OVRD        | HP_AMPIN<br>_GND_REG        | —                           | HP_CONNE<br>CT_GND_V<br>AG  | 21h     |

| R22(15h) | SELF_OSC_<br>CTRL1   |                  | SELFOSC_                    | DIVCLK_SEL                   | SEL                        | FOSC_VCHP             | _SEL                     | SEL                         | FOSC_FERQ                   | _SEL                        | 05h     |

| R23(16h) | SELF_OSC_<br>CTRL2   |                  |                             |                              | 1                          | SELFOSC_<br>PWD       | SELFOSC_<br>RSTB         | SELFOSC_<br>CHPCLK_P<br>WDB | SELFOSC_<br>AOPCLK_P<br>WDB | SELFOSC_<br>APOPCLK_<br>SEL | 0Ah     |

| Register | Name                 | Remarks           | Bit[7]   | Bit[6]       | Bit[5]           | Bit[4]          | Bit[3]            | Bit[2]               | Bit[1]                | Bit[0]                | Default |

|----------|----------------------|-------------------|----------|--------------|------------------|-----------------|-------------------|----------------------|-----------------------|-----------------------|---------|

| R24(17h) | BIASG_CTRL<br>1      |                   |          | IBIAS_NONDAC |                  |                 |                   | IBIAS_GEN<br>_MUX    | 0h                    |                       |         |

| R25(18h) | BIASG_CTRL<br>2      |                   |          |              |                  |                 |                   |                      |                       | POR                   | 0h      |

| R26(19h) | REF_SUP_C<br>TRL     |                   |          |              |                  |                 | REFSUPPL<br>Y_PWD | SUPOVR_V<br>AL       | SUPOVR_E<br>N         | INVERT_SU<br>PPLY_OSC | 0h      |

| R27(1Ah) | BANGAP_CT<br>RL      |                   |          | BGCORE_BYPS  |                  |                 |                   | BGCORE_I<br>BIAS_MUX | 0h                    |                       |         |

| R28(1Bh) | TEMP_SENS<br>E_CTRL1 | TEMPATURE Control | I        | HI_TEMP_SEL  | -                |                 | IO_TEMP_SEI       | _                    | VBG_TF                | RIM_SEL               | 69h     |

| R29(1Ch) | TEMP_SENS<br>E_CTRL2 |                   |          |              |                  |                 |                   | TS_TEST_<br>MODE     | TEMPSENS<br>E_PWD     | TEMPSENS<br>E_RSTB    | 01h     |

| R30(1Dh) | PAD_CTRL             |                   | SD_B_PUB | SD_B_PD      | I2C_DATA_<br>PUB | I2C_DATA_<br>PD | I2C_CLK_P<br>UB   | I2C_CLK_P<br>D       | CLK_DEGLI<br>TCH_BYPS | _                     | C0h     |

| R31(1Eh) | SHUTDOWN             |                   |          |              |                  |                 |                   |                      |                       | SHUTDOW<br>N_B        | 01h     |

| R32(1Fh) | SPARE2               |                   | TST      |              |                  |                 |                   | 0h                   |                       |                       |         |

| R33(1Gh) | SPARE2               |                   |          | TST          |                  |                 |                   |                      | 0h                    |                       |         |

#### Notes:

1 Registers not described in this map should be considered "reserved".

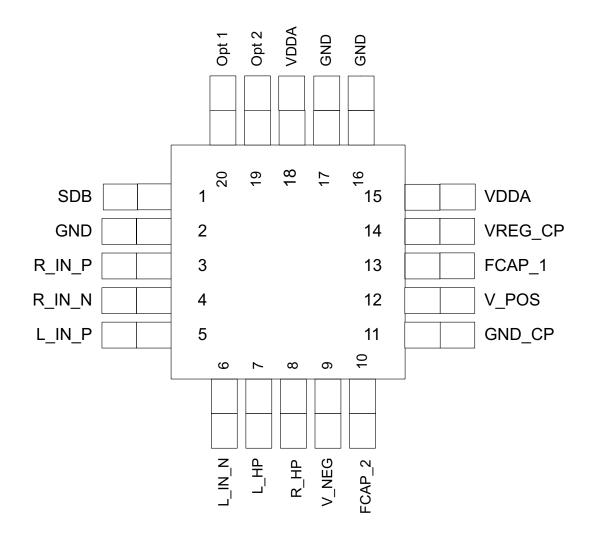

### 6.PIN CONFIGURATION AND DESCRIPTION

#### 6.1. 20-Pin QFN TSCS10XX

Figure 7. 20-Pin TSDP1xxQFN

TSDP1XX

### 6.2. 20-Pin QFN TSCS11XX

Figure 8. 20-Pin TSDP11XX QFN

### 6.3. Pin Table for pin QFN package

#### POWER

| Pin Name | Pin Function                | I/O        | Internal<br>Pull-up<br>Pull-down | 20 pin<br>location |

|----------|-----------------------------|------------|----------------------------------|--------------------|

| VDDA     | Positive supply             | I(Power)   | -                                | 18,15              |

| GND      | Ground supply               | I(Power)   | -                                | 2,16,17            |

| V_POS    | Charge pump positive supply | I(Power)   | -                                | 12                 |

| V_NEG    | Charge pump negative supply | I(Power)   | -                                | 9                  |

| FCAP_1   | Flying cap                  | I/O(Power) | -                                | 13                 |

| FCAP_2   | Flying cap                  | I/O(Power) | -                                | 10                 |

| VREG_CP  | LDO filter CAP              | I/O(Power) |                                  | 14                 |

#### ANALOG INPUT

| Pin Name | Pin Function               | I/O       | Internal<br>Pull-up<br>Pull-down | 20 pin<br>location |

|----------|----------------------------|-----------|----------------------------------|--------------------|

| L_IN_P   | Left Audio Positive Input  | I(Analog) | None                             | 5                  |

| L_IN_N   | Left Audio Negative Input  | I(Analog) | None                             | 6                  |

| R_IN_P   | Right Audio Positive Input | I(Analog) | None                             | 3                  |

| R_IN_N   | Right Audio Negative Input | I(Analog) | None                             | 4                  |

#### ANALOG OUTPUT

| Pin Name | Pin Function                                     | I/O       | Internal<br>Pull-up<br>Pull-down | 20 pin<br>location |

|----------|--------------------------------------------------|-----------|----------------------------------|--------------------|

| L_HP     | Audio Headphone Output Left - ground referenced  | O(Analog) | None                             | 7                  |

| R_HP     | Audio Headphone Output Right - ground referenced | O(Analog) | None                             | 8                  |

#### 10 pins DATA and CONTROL

| Pin Name | Pin Function                                         | I/O          | Internal<br>Pull-up<br>Pull-down | 20 pin<br>location |

|----------|------------------------------------------------------|--------------|----------------------------------|--------------------|

| I2C_CLK  | I <sup>2</sup> C shift clock for serial control port | I(Digital)   | Pull-Up                          | 19                 |

| I2C_SDA  | I <sup>2</sup> C shift data for serial control port  | I/O(Digital) | Pull-Up                          | 20                 |

| SD       | Shutdown Control for chip                            | I(Digital)   | Pull-Down                        |                    |

### 6.4. PIN FUNCTION

|     |         |              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN |         | INPUT/OUTPUT |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| QFN | NAME    |              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | POWER        | Shutdown SD is active low SD turns the IC on and off When                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1   | SD      | I (DIG)      | <ul> <li>Shutdown. SD is active low. SD turns the IC on and off. When SD is low, the device is in shutdown mode and the jack insertion detect circuitry is active. SD has to be high to turn on the device and run the jack configuration detect algorithm. Typically, SD is held low until the system gets an interrupt from the IC, indicating that a jack has been inserted. The system then pulls SD high.</li> <li>0 = The IC is in shutdown mode with jack detection circuitry active.</li> <li>1 = The IC is active. The jack configuration algorithm runs</li> </ul> |

| 2   | GND     | P (GND)      | immediately after a load has been detected.<br>Headphone Ground Reference. This need to be very clean<br>ground for best results.                                                                                                                                                                                                                                                                                                                                                                                                                                            |