SLWS051 - JANUARY 1999

- Power Amplifier for 1.9-GHz CDMA Applications

- 0.5-Micron GaAs MESFET Technology

- Operates from 3-V to 3.6-V Supply

- High Output Power . . . 27.5-dBm Typical at 3-V Supply and 1.9 GHz

- Gain Linearity Better Than 0.5 dB Over a 37-dB Dynamic Range

- High Adjacent Channel Power Rejection

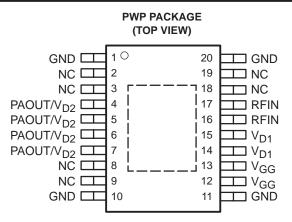

- 20-Pin Plastic Surface-Mount TSSOP PWP PowerPAD<sup>™</sup> (PWP)

#### description

The TRF4002 personal communications system (PCS) RF power amplifier is a gallium arsenide (GaAs), integrated circuit housed in a 20-pin plastic surface-mount, thin-shrink small outline package (TSSOP). The package has a solderable pad that improves the package thermal performance by bonding the pad to an external thermal plane. The pad also acts as a low-inductance electrical path-to-ground and must be electrically connected to the printed-circuit board (PCB) ground plane as a continuation of the regular package terminals that are designated GND. The integrated circuit is suitable for 1.9-GHz code-division multiple-access (CDMA) applications.

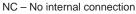

The TRF4002 is a power amplifier that uses a two-stage topology with an on-/off-chip output inductor and impedance matching network to minimize cost. It is suitable for use in mobile systems that require high linearity. It can deliver 27.5-dBm typical output power optimized for minimum adjacent channel power.

These devices have no built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

SLWS051 - JANUARY 1999

#### functional block diagram

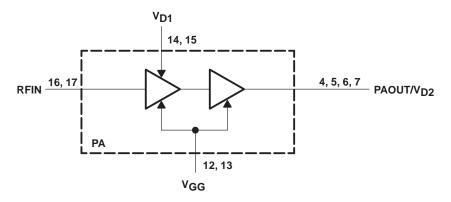

### application circuit

NOTE: Backside must be electrically grounded

SLWS051 - JANUARY 1999

#### **Terminal Functions**

| TERMINAL              |                       | 1/0 | DECONIDION                            |  |  |

|-----------------------|-----------------------|-----|---------------------------------------|--|--|

| NAME                  | NO.                   | I/O | DESCRIPTION                           |  |  |

| GND                   | 1, 10, 11, 20         |     | Ground                                |  |  |

| PAOUT/V <sub>D2</sub> | 4, 5, 6, 7            | I/O | RF output and second-stage drain bias |  |  |

| RFIN                  | 16, 17                | I   | RF input                              |  |  |

| V <sub>GG</sub>       | 12, 13                | I   | Gate bias voltage                     |  |  |

| V <sub>D1</sub>       | 14, 15                | I   | First-stage drain bias                |  |  |

| NC                    | 2, 3, 8, 9, 18,<br>19 |     | No internal connection                |  |  |

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>D1.</sub> V <sub>D2</sub> (see Note 1) 0 V to 5 | V  |

|------------------------------------------------------------------------------|----|

| Bias voltage, V <sub>GG</sub> (see Note 2)                                   | V  |

| Input power, RFIN                                                            | sm |

| Continuous power dissipation at or below $T_A = 25^{\circ}C$                 | W  |

| Operating free-air temperature range, T <sub>A</sub>                         | °C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NO

2.  $V_{D1} = V_{D2} = 0 V$

#### recommended operating conditions

|                                                         | MIN  | NOM   | MAX  | UNIT |

|---------------------------------------------------------|------|-------|------|------|

| Drain supply voltage, V <sub>D1</sub> , V <sub>D2</sub> | 3    |       | 3.6  | V    |

| Gate bias voltage, V <sub>GG</sub>                      | -0.6 | -0.35 | -0.2 | V    |

| Operating free-air temperature, T <sub>A</sub>          | -30  |       | 80   | °C   |

SLWS051 - JANUARY 1999

### electrical characteristics over recommended operating free-air temperature range,

### $V_{D1} = V_{D2} = 3 V, V_{GG} = -0.35 V$

|                              | PARAMETER                                     |                           | TEST CONDITIONS                     | MIN  | TYP <sup>†</sup> | MAX  | UNIT |

|------------------------------|-----------------------------------------------|---------------------------|-------------------------------------|------|------------------|------|------|

| Input frequency range (RFIN) |                                               |                           |                                     | 1850 |                  | 1910 | MHz  |

| <sup>t</sup> d(on)           | Turn-on time,(see Note 3)                     |                           |                                     |      |                  | 50   | μs   |

| <sup>t</sup> d(off)          | Turn-off time, (see Note 4)                   |                           |                                     |      | 50               | μs   |      |

|                              | Gain                                          |                           | 17                                  | 18   | 19               | dB   |      |

|                              | Noise figure                                  |                           |                                     |      | 10               | dB   |      |

|                              | Reverse isolation                             |                           | 40                                  |      |                  | dB   |      |

|                              | Input VSWR (RFIN) (see Note 5)                |                           |                                     |      | 2:1              |      |      |

|                              | Output VSWR (PAOUT/VD2) (see Not              | Small signal conditions   |                                     | 2:1  |                  |      |      |

|                              | Nominal linear output power                   |                           |                                     | 27.5 |                  | dBm  |      |

|                              | Power-added efficiency                        | P <sub>O</sub> = 27.7 dBm |                                     | 30%  |                  |      |      |

|                              | Gain linearity                                |                           | –10 dBm < P <sub>O</sub> < 27.7 dBm |      |                  | ±0.5 | dB   |

|                              | Adjacent channel power rejection (see Note 6) | >±1.25-MHz offset         |                                     | -44  |                  |      | dBc  |

|                              |                                               | > $\pm$ 2.25-MHz offset   |                                     | -54  |                  |      | dBc  |

|                              | Harmonics                                     |                           |                                     |      | -30              | dBc  |      |

|                              | Quiescent current                             |                           |                                     | 450  |                  | mA   |      |

<sup>†</sup> Typical values are at  $T_A = 25^{\circ}C$

NOTES: 3. Turn-on time is that time between the instant the power amplifier bias voltage changes from 0 V and the instant when the device output power is within ±1 dB of its rated output value.

4. Turn-off time is that time between the instant that the PA bias voltage begins to fall and the instant when the PA current consumption is less than 1 mA.

5. VSWR = voltage standing wave ratio

6. Measured at 27.5-dBM total output power with CDMA input signal.

#### stability

| PARAMETER | TEST CONDITIONS                     | MIN | түр† | MAX | UNIT |

|-----------|-------------------------------------|-----|------|-----|------|

| Stability | Output VSWR < 6:1, All phase angles |     |      | -70 | dBc  |

<sup>†</sup> Typical values are at  $T_A = 25^{\circ}C$

SLWS051 - JANUARY 1999

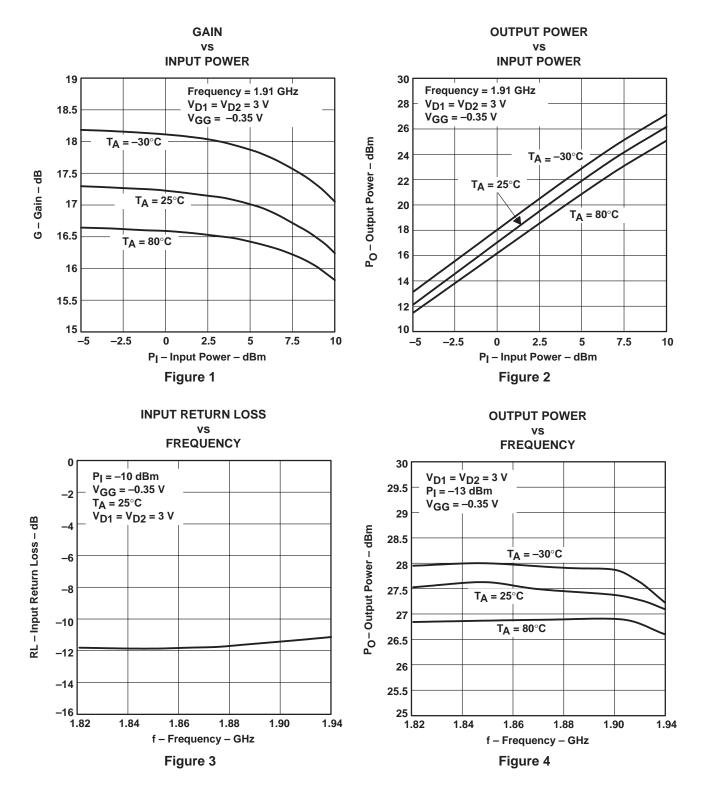

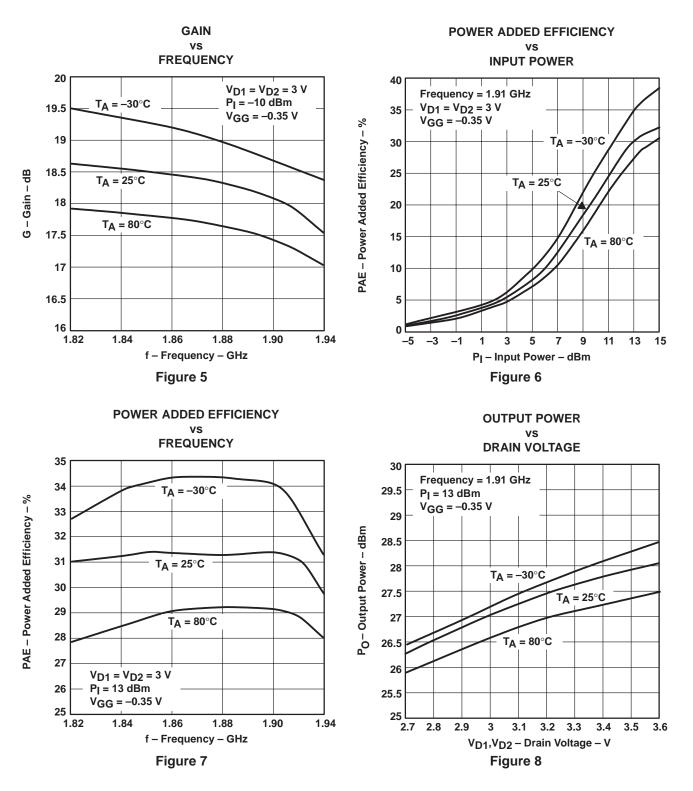

#### **TYPICAL CHARACTERISTICS**

SLWS051 - JANUARY 1999

### **TYPICAL CHARACTERISTICS**

SLWS051 - JANUARY 1999

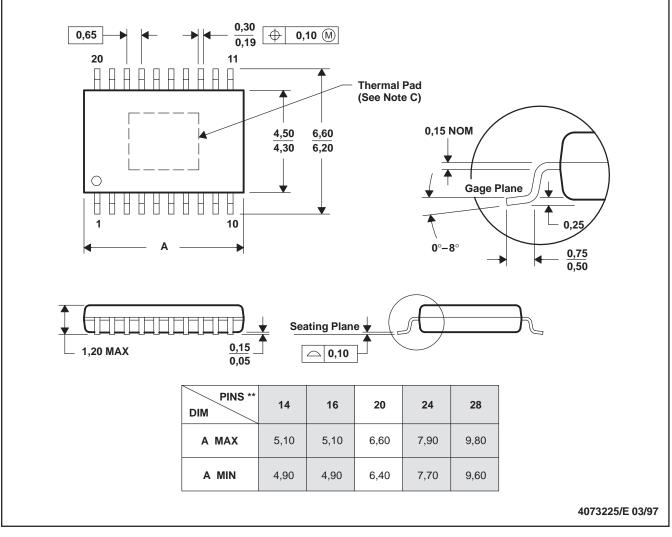

#### **MECHANICAL DATA**

## PWP (R-PDSO-G\*\*)

#### PowerPAD<sup>™</sup> PLASTIC SMALL-OUTLINE PACKAGE

20-PIN SHOWN

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. The package thermal performance may be enhanced by bonding the thermal pad to an external thermal plane. This solderable pad is electrically and thermally connected to the backside of the die and possibly selected leads. The maximum pad size on the printed-circult board should be equal to the package body size – 2,0mm.

PowerPAD is a trademark of Texas Instruments Incorporated.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated