SLWS057 - AUGUST 1999

- 2-GHz Main Synthesizer, Which Incorporates a Dual-Mode 32/33 and 64/65 Prescaler for Fractional-N Operation

- 200-MHz Auxiliary Synthesizer, Which Incorporates an 8/9 Prescaler

- Separate Supply Terminals for Main and Auxiliary Charge Pumps

- Internal Compensation for Fractional Spurs

- Low Phase Noise

- Normal and Integral Charge Pump Outputs

- Fully Programmable Main and Auxiliary Dividers

- Serial Data Interface

- Direct I/Q Modulator

- Control Logic for Power-Down Modes

- Single-Sideband Suppressed Carrier (SSBSC) Converter to Generate TX Carrier

- 200-MHz TXIF Synthesizer and Oscillator

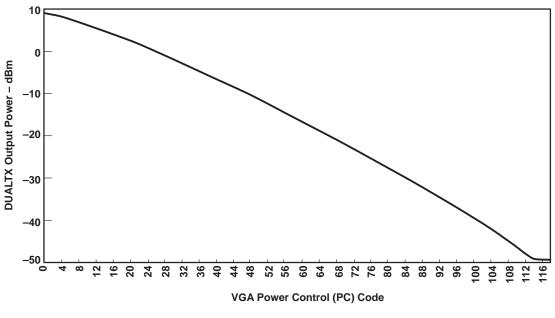

- Variable Gain Amplifier (VGA) With 50 dB of Dynamic Range

- 900-MHz Power Amplifier (PA) Driver With 9 dBm Typical Output Power

- Reference and Clock Buffers

- 158 mA Typical Total Operating Current at 3.75 V Supply

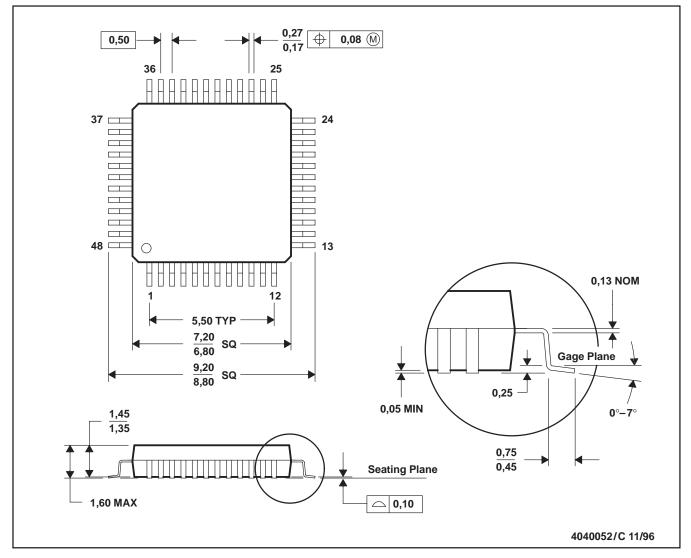

- 48-Pin Quad Flatpack (LQFP)

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Pleas Texas

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1999, Texas Instruments Incorporated

SLWS057 – AUGUST 1999

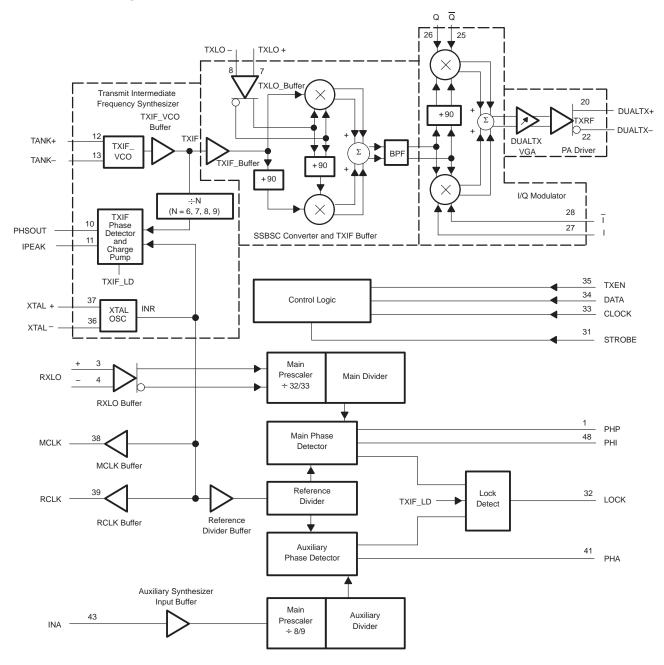

#### description

The TRF3040 is an integrated transmit modulator/synthesizer circuit suitable for 900-MHz analog and digital cellular telephones. It consists of a transmit intermediate frequency (TXIF) synthesizer and oscillator, a single-sideband suppressed carrier (SSBSC) converter, a direct conversion I/Q modulator, a variable gain amplifier (VGA) with a power amplifier (PA) driver, a main channel fractional-N synthesizer, an auxiliary channel synthesizer, a crystal oscillator reference buffer, and clock buffers in a small surface-mount package. Very few external components are required.

The TXIF synthesizer produces the offset signal, TXIF, needed to translate the external local oscillator (TXLO) signal to the correct transmission frequency. The TXIF\_VCO (voltage controlled oscillator) can operate from 90 MHz to 200 MHz, depending on the component values chosen for the external tank circuit. The TXLO signal may be differential or single-ended input.

The direct conversion I/Q modulator places the modulation signal ( $\pi$ /4-DQPSK, FM) directly on top of the transmit carrier frequency.

The VGA has an output range of -41 dBm to 9 dBm into a 200- $\Omega$  differential load. The balanced output signal simplifies the board layout making it easier to meet isolation requirements.

SLWS057 - AUGUST 1999

#### functional block diagram

SLWS057 - AUGUST 1999

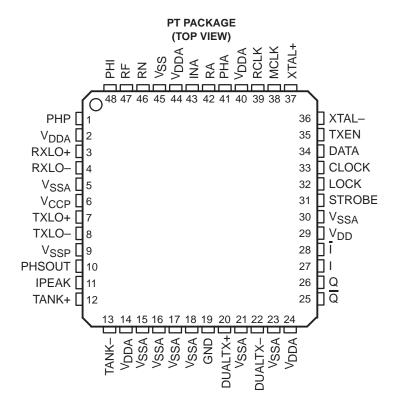

## **Terminal Functions**

| TERMI<br>NAME    | INAL<br>NO. | I/O | DESCRIPTION                                                  |

|------------------|-------------|-----|--------------------------------------------------------------|

| CLOCK            | 33          | 1   | Serial clock input                                           |

| DATA             | 34          | 1   | Serial data input                                            |

| DUALTX+          | 20†         | 0   | Differential RF power amplifier driver                       |

| DUALTX-          | 22†         | 0   | Differential RF power amplifier driver                       |

| GND              | 19          |     | Substrate (GND)                                              |

| Ī                | 28          | 1   | Baseband inverting in-phase modulation input                 |

| I                | 27          | 1   | Baseband noninverting in-phase modulation input              |

| INA              | 43          | 1   | Auxiliary synthesizer input                                  |

| IPEAK            | 11          |     | TX offset loop charge pump current setting resistor          |

| LOCK             | 32          | 0   | Lock detect output                                           |

| MCLK             | 38†         | 0   | Buffered master clock output                                 |

| PHA              | 41          | 0   | Auxiliary charge pump output                                 |

| PHI              | 48†         | 0   | Main charge pump integral output                             |

| PHP              | 1           | 0   | Main charge pump proportional output                         |

| PHSOUT           | 10          | 0   | TX offset charge pump output                                 |

| Q                | 25          | 1   | Baseband inverting quadrature modulation input               |

| Q                | 26          | 1   | Baseband noninverting quadrature modulation input            |

| RA               | 42          |     | Auxiliary charge pump current setting resistor               |

| RCLK             | 39†         | 0   | Buffered reference clock output                              |

| RF               | 47          |     | Fractional compensation charge pump current setting resistor |

| RN               | 46          |     | Main charge pump current setting resistor                    |

| RXLO+            | 3           | 1   | Differential main synthesizer positive input                 |

| RXLO-            | 4           | 1   | Differential main synthesizer negative input                 |

| STROBE           | 31          | 1   | Data strobe input                                            |

| TANK+            | 12          | 1   | Differential TXIF_VCO tank positive input                    |

| TANK-            | 13          | 1   | Differential TXIF_VCO tank negative input                    |

| TXEN             | 35          | 1   | Transmit enable                                              |

| TXLO+            | 7           | 1   | Differential transmit LO positive input                      |

| TXLO-            | 8           | 1   | Differential transmit LO negative input                      |

| VCCP             | 6           |     | Main charge pump and bandgap supply voltage                  |

| V <sub>DD</sub>  | 29          |     | Digital supply voltage                                       |

|                  | 2           |     | Main prescaler and bandgap supply voltage                    |

|                  | 14          |     | TX offset loop supply voltage                                |

| V <sub>DDA</sub> | 24†         |     | RF modulator supply voltage                                  |

|                  | 40          |     | Oscillator and buffers supply voltage                        |

|                  | 44          |     | Auxiliary charge pump supply voltage                         |

|                  | 17, 18      |     | RF modulator ground                                          |

|                  | 5           |     | Main prescaler and bandgap ground                            |

| VSSA             | 15          |     | TX offset loop ground                                        |

| - 35A            | 16          |     | TX offset loop and charge pump ground                        |

|                  | 21, 23      |     | PA driver ground                                             |

|                  | 30          |     | Oscillator, MCLK, and RCLK ground                            |

| VSS              | 45          |     | Digital ground                                               |

| V <sub>SSP</sub> | 9           |     | Main charge pump ground                                      |

| XTAL+            | 37          | I   | Crystal oscillator base input                                |

| XTAL-            | 36          | 0   | Crystal oscillator emitter input                             |

<sup>†</sup> Pins have limited ESD protection

SLWS057 - AUGUST 1999

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Power supply voltage range, V <sub>CCP</sub> , V <sub>DD</sub> , V <sub>DDA</sub> (see Note 1) | –0.3 V to 4.5 V              |

|------------------------------------------------------------------------------------------------|------------------------------|

| Voltage applied to any other terminal, $V_{IN}$                                                | V to $V_{CC}/V_{DD}$ + 0.3 V |

| Operation junction temperature, T <sub>Jmax</sub>                                              | 150°C                        |

| Operating temperature, T <sub>A</sub>                                                          | – 40°C to 85°C               |

| Storage temperature, T <sub>stg</sub>                                                          | – 65°C to 150°C              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device, at these or any other conditions beyond those indicated under "recommended operating conditions", is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage values are in respect to Voota (Voota = Voota = CND)

NOTE 1: Voltage values are in respect to  $V_{SSA}$  ( $V_{SSA} = V_{SSP} = V_{SS} = GND$ )

#### recommended operating conditions

| PARAMETER                                                                                                             | MIN                 | NOM                 | MAX                  | UNIT |

|-----------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|----------------------|------|

| Supply voltage, V <sub>CCP</sub> , V <sub>DD</sub> , V <sub>DDA</sub>                                                 | 3.6                 | 3.75                | 3.9                  | V    |

| High-level input voltage, VIH (CLOCK, DATA, STROBE, TXEN)                                                             | $0.7 \times V_{DD}$ |                     | V <sub>DD</sub> +0.3 | V    |

| Low-level input voltage, VIL (CLOCK, DATA, STROBE, TXEN)                                                              | -0.3                |                     | $0.3 \times V_{DD}$  | V    |

| Main synthesizer input frequency, fIN(RXLO±)                                                                          |                     |                     | 2000                 | MHz  |

| Main synthesizer input power, $P_{IN(RXLO\pm)}$ , (AC coupled, 50- $\Omega$ single ended, 100- $\Omega$ differential) |                     | -17                 |                      | dBm  |

| Transmit LO input frequency, fIN(TXLO±)                                                                               |                     |                     | 1050                 | MHz  |

| Transmit LO input power, $P_{IN(TXLO\pm)}$ , (AC coupled, 50- $\Omega$ single ended, 100- $\Omega$ differential)      |                     | -10                 |                      | dBm  |

| TXIF_VCO tank differential input frequency, fIN(TANK±)                                                                |                     |                     | 200                  | MHz  |

| Crystal oscillator input frequency, fIN(XTAL+)                                                                        |                     |                     | 25                   | MHz  |

| Auxiliary synthesizer input frequency, fIN(INA)                                                                       |                     |                     | 200                  | MHz  |

| Auxiliary synthesizer input voltage, V <sub>IN(INA)</sub> , (AC coupled)                                              | 0.2                 |                     |                      | Vpp  |

| In-phase differential input, I/I (quiescent)                                                                          |                     | V <sub>DDA</sub> /2 |                      | V    |

| Quadraphase differential input, Q/Q (quiescent)                                                                       |                     | V <sub>DDA</sub> /2 |                      | V    |

| Operating free-air temperature, T <sub>A</sub>                                                                        | -40                 | 25                  | 85                   | °C   |

#### dc electrical characteristics $V_{CCP} = V_{DD} = V_{DDA} = 3.75$ V, $T_A = 25^{\circ}C$ (unless otherwise noted)

#### supply current I = $I_{CCP} + I_{DD} + I_{DDA}$

|           | PARAMETER                                                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------|-------------------------------------------------------------|-----------------|-----|-----|-----|------|

| ISLEEP    | Sleep mode supply current                                   |                 |     | 2   | 3   | mA   |

| ISTANDBY  | Standby mode supply current                                 |                 |     | 22  |     | mA   |

| IOPER_ANA | Operating supply current – full power analog mode (MODE=0)  |                 |     | 142 |     | mA   |

| IOPER_DIG | Operating supply current – full power digital mode (MODE=1) |                 |     | 158 |     | mA   |

# dc electrical characteristics V<sub>CCP</sub> = V<sub>DD</sub> = V<sub>DDA</sub> = 3.75 V, T<sub>A</sub> = 25°C (unless otherwise noted) (continued)

#### digital interface

|     | PARAMETER            | TEST CONDITIONS         | MIN                     | TYP | MAX   | UNIT |

|-----|----------------------|-------------------------|-------------------------|-----|-------|------|

| Vei | Output voltage, low  | I <sub>O</sub> = 1 μA   |                         |     | 0.050 | V    |

| VOL | Oulput voltage, low  | I <sub>O</sub> = 2 mA   |                         |     | 0.4   | V    |

| Val |                      | I <sub>O</sub> = −1 μA  | V <sub>DD</sub> - 0.050 |     |       | V    |

| VOH | Output voltage, high | $I_{O} = -2 \text{ mA}$ | V <sub>DD</sub> - 0.4   |     |       | V    |

SLWS057 - AUGUST 1999

#### charge pump PHA

|                                 | PARAMETER                                        | TEST CONDITIONS                                     | MIN | TYP | MAX | UNIT |

|---------------------------------|--------------------------------------------------|-----------------------------------------------------|-----|-----|-----|------|

| IPHA                            | Output current at PHA                            |                                                     | 200 | 250 | 300 | μA   |

| <u>∆I<sub>PHA</sub></u><br>∏PHA | Relative output current variation (see Figure 1) | $R_A = 100 \text{ k}\Omega$ , $V_{PHA} = V_{DDA}/2$ |     | 2%  | 10% |      |

| ∆IPHA                           | Output current matching PHA (see Figure 1)       |                                                     |     |     | 10% |      |

#### charge pump PHP, normal mode, $V_{RF} = V_{DDA}$ (see Note 2)

|                      | PARAMETER                                        | TEST C                   | ONDITIONS               | MIN  | TYP  | MAX  | UNIT |

|----------------------|--------------------------------------------------|--------------------------|-------------------------|------|------|------|------|

| I <sub>PHP</sub>     | Output current at PHP                            |                          |                         | ±250 | ±288 | ±320 | μΑ   |

| <u>∆IPHP</u><br>∏PHP | Relative output current variation (see Figure 1) | CN = 128,<br>RN = 120 kΩ | $V_{PHP} = V_{DDA/2}$ , |      | 2%   | 10%  |      |

| $\Delta I_{PHP}$     | Output current matching PHP (see Figure 1)       |                          |                         |      |      | 10%  |      |

NOTE 2: When a serial input word A is programmed, the main charge pump on the PHP and PHI is in the speed-up mode as long as STROBE is high in standard programming or until the speed-up mode counter reaches its terminal count. When this is not the case, the main charge pumps are in normal mode.

#### charge pump PHP, speed-up mode, $V_{RF} = V_{DDA}$ (see Note 2)

|                                 | PARAMETER                                        | TEST C                   | ONDITIONS              | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|--------------------------------------------------|--------------------------|------------------------|------|------|------|------|

| IPHP                            | Output current at PHP                            |                          |                        | ±1.2 | ±1.6 | ±1.9 | mA   |

| <u>∆I<sub>PHP</sub></u><br>∏PHP | Relative output current variation (see Figure 1) | CN = 128,<br>RN = 120 kΩ | $V_{PHP} = V_{DDA/2},$ |      | 2%   | 10%  |      |

| $\Delta I_{PHP}$                | Output current matching PHP (see Figure 1)       |                          |                        |      |      | 10%  |      |

NOTE 2: When a serial input word A is programmed, the main charge pump on the PHP and PHI is in the speed-up mode as long as STROBE is high in standard programming or until the speed-up mode counter reaches its terminal count. When this is not the case, the main charge pumps are in normal mode.

#### charge pump PHI, speed-up mode, $V_{RF} = V_{DDA}$ (see Note 2)

|                      | PARAMETER                                        | TEST                           | CONDITIONS                                  | MIN  | TYP | MAX  | UNIT |

|----------------------|--------------------------------------------------|--------------------------------|---------------------------------------------|------|-----|------|------|

| IPHI                 | Output current at PHI                            |                                |                                             | ±3.3 | ±4  | ±4.5 | mA   |

| <u>∆Iphi</u><br>∏Phi | Relative output current variation (see Figure 1) | CN = 128,<br>CK = 3,<br>CL = 1 | RN = 120 kΩ,<br>VPHA = V <sub>DDA</sub> /2, |      | 2%  | 10%  |      |

| ΔIPHI                | Output current matching PHI (see Figure 1)       |                                |                                             |      |     | 10%  |      |

NOTE 2: When a serial input word A is programmed, the main charge pump on the PHP and PHI is in the speed-up mode as long as STROBE is high in standard programming or until the speed-up mode counter reaches its terminal count. When this is not the case, the main charge pumps are in normal mode.

SLWS057 - AUGUST 1999

# dc electrical characteristics $V_{CCP} = V_{DD} = V_{DDA} = 3.75$ V, $T_A = 25^{\circ}C$ (unless otherwise noted) (continued)

#### fractional compensation PHP, normal mode, V<sub>RN</sub> = V<sub>DDA</sub> (see Note 2)

|                            | PARAMETER                                   | TEST                 | CONDITIONS                       | MIN  | TYP  | MAX  | UNIT |

|----------------------------|---------------------------------------------|----------------------|----------------------------------|------|------|------|------|

| IPHP-FR                    | Output current PHP vs. fractional numerator | FMOD = 1,            | RF = 120 kΩ,                     | -340 | -270 | -170 | nA   |

| <u>∆IPHP–FR</u><br>∏PHP–FR | Relative output current (see Figure 1)      | CN = 128,<br>CK = 3, | $V_{PHP} = V_{DDA/2},$<br>CL = 1 |      |      | 10%  |      |

NOTE 2: When a serial input word A is programmed, the main charge pump on the PHP and PHI is in the speed-up mode as long as STROBE is high in standard programming or until the speed-up mode counter reaches its terminal count. When this is not the case, the main charge pumps are in normal mode.

#### fractional compensation PHP, speed-up mode, $V_{RN} = V_{DDA}$ (see Note 2)

|                            | PARAMETER                                   | TEST C               | ONDITIONS               | MIN  | TYP  | MAX  | UNIT |

|----------------------------|---------------------------------------------|----------------------|-------------------------|------|------|------|------|

| IPHP-FR                    | Output current PHP vs. fractional numerator | FMOD = 1,            | RF = 120 kΩ,            | -1.7 | -1.4 | -1.1 | μΑ   |

| <u>∆IPHP–FR</u><br>∏PHP–FR | Relative output current (see Figure 1)      | CN = 128,<br>CK = 3, | VPHP =VDDA/2,<br>CL = 1 |      |      | 15%  |      |

NOTE 2: When a serial input word A is programmed, the main charge pump on the PHP and PHI is in the speed-up mode as long as STROBE is high in standard programming or until the speed-up mode counter reaches its terminal count. When this is not the case, the main charge pumps are in normal mode.

#### fractional compensation PHI, speed-up mode, V<sub>RN</sub> = V<sub>DDA</sub> (see Note 2)

|                               | PARAMETER                                   | TEST C               | ONDITIONS                                         | MIN  | TYP | MAX  | UNIT |

|-------------------------------|---------------------------------------------|----------------------|---------------------------------------------------|------|-----|------|------|

| IPHI-FR                       | Output current PHI vs. fractional numerator | FMOD = 1,            | RF = 120 kΩ,                                      | -5.1 | -4  | -2.9 | μΑ   |

| <u>∆Iphi–fr</u><br>I Iphi–fri | Relative output current (see Figure 1)      | CN = 128,<br>CK = 3, | V <sub>PHI</sub> = V <sub>DDA/2</sub> ,<br>CL = 1 |      |     | 15%  |      |

NOTE 2: When a serial input word A is programmed, the main charge pump on the PHP and PHI is in the speed-up mode as long as STROBE is high in standard programming or until the speed-up mode counter reaches its terminal count. When this is not the case, the main charge pumps are in normal mode.

#### charge pump leakage currents

| PARAMETER        |                            | TEST COND                      | MIN               | TYP | MAX  | UNIT |    |

|------------------|----------------------------|--------------------------------|-------------------|-----|------|------|----|

| I <sub>PHI</sub> | Output leakage current PHI |                                |                   |     | ±0.1 | ±10  | nA |

| IPHA             | Output leakage current PHA | $V_{RF} = V_{RN} = V_{DDA}, V$ | PHP = 0 to $VDDA$ |     | ±0.1 | ±10  | nA |

SLWS057 - AUGUST 1999

# ac electrical characteristics $V_{CCP} = V_{DD} = V_{DDA} = 3.75 V$ , $T_A = 25^{\circ}C$ (unless otherwise noted)

#### transmit intermediate frequency synthesizer, SSBSC converter and I/Q modulator

|               | PARAMETER                                                                                  | TEST CONDITIONS                                                         | MIN  | TYP  | MAX                   | UNIT    |

|---------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|-----------------------|---------|

| TXLO±         | Transmit LO input frequency                                                                |                                                                         | 900  |      | 1100                  | MHz     |

| TXLO±         | Transmit LO input power                                                                    | AC coupled;<br>50- $\Omega$ single-ended,<br>100- $\Omega$ differential | -13  | -10  |                       | dBm     |

| TANK±         | TXIF_VCO tank differential input frequency range                                           |                                                                         |      | 155  |                       | MHz     |

| PHSOUT        | TXIF_PD charge pump output level                                                           |                                                                         | 0.5  |      | V <sub>DDA</sub> -0.5 | V       |

| IPEAK         | TXIF_PD charge pump current setting                                                        | RIPEAK = 13 kΩ                                                          |      | 2.3  |                       | mA      |

| Kφ            | TXIF_PD phase gain                                                                         | PLL in phase lock                                                       |      | 1.46 |                       | mA/ra   |

|               | XTAL oscillator input frequency                                                            |                                                                         | 15   |      | 25                    | MHz     |

| XTAL+         | XTAL negative resistance                                                                   | With external capacitors                                                |      | -100 |                       | Ω       |

|               | Frequency range                                                                            |                                                                         |      | 20   |                       | MHz     |

| RCLK,<br>MCLK | Output levels                                                                              | RCLK, MCLK load circuit                                                 | 0.7  | 1    | 1.4                   | Vpp     |

| IVICLN        | Harmonic content                                                                           | 1                                                                       | 10   |      |                       | dBc     |

|               | Differential input frequency                                                               |                                                                         |      |      | 1.8                   | MHz     |

|               | Differential modulation level                                                              |                                                                         | 0.8  | 0.9  | 1.0                   | VPEA    |

| I/I, Q/Q      | Differential input impedance                                                               |                                                                         | 10   |      |                       | kΩ      |

|               | DC bias point                                                                              |                                                                         | 1.65 | 1.7  | 2.0                   | V       |

| TXRF          | TX operating frequency range                                                               |                                                                         | 820  |      | 920                   | MHz     |

|               | RF output frequency                                                                        | SE = 1, TXEN = 1,<br>AMPS/DAMPS                                         | 820  |      | 853                   | MHz     |

|               | Output power (I/Q set to typical conditions)                                               | Open collector, matched to 200 $\Omega$ differential impedance          |      | 9    |                       | dBm     |

|               | Gain flatness                                                                              |                                                                         |      | 1    |                       | dB      |

|               |                                                                                            | 3rd order                                                               | 33   | 36   |                       | dBc     |

|               | Linearity in DAMPS mode (I/Q in phase, levels set to nominal conditions Pout set to 8 dBm) | 5th order                                                               | 45   | 62   |                       | dBc     |

|               | nominal conditions Four set to 6 dbin)                                                     | 7th order                                                               | 53   | 70   |                       | dBc     |

|               |                                                                                            | VGA set to Pout = 8 dBm                                                 | 26   | 40   |                       |         |

|               | Carrier suppression, I & Q in quadrature                                                   | VGA set to Pout = -38 dBm                                               |      | 33   |                       | dBc     |

| DUALTX±       | Sideband suppression, I & Q in quadrature                                                  |                                                                         | 25   | 43   |                       | dBc     |

|               | Adjacent channel noise power                                                               | Ar 30 kHz offset                                                        |      | -95  |                       | dBc/H   |

|               | Alternate channel noise power                                                              | At 60 kHz offset                                                        |      | -101 |                       | dBc/H   |

|               |                                                                                            | TXLO                                                                    | 21   | 33   |                       |         |

|               |                                                                                            | Upper sideband                                                          | 21   | 60   |                       | 1       |

|               | TXLO conversion products (see Note 3)                                                      | TXLO –2×TXIF                                                            | 15   |      |                       | dBc     |

|               |                                                                                            | TXLO ±3×TXIF                                                            | 36   |      |                       | · · · · |

|               |                                                                                            | Harmonics $\leq 10$ th                                                  | 21   |      |                       | 1       |

|               | Broadband noise (0-dB VGA or 9-dBm output,<br>whichever is less                            | 869 to 894 MHz                                                          |      | -124 |                       | dBc/H   |

NOTE 3: Parameters may vary depending on external output matching circuit.

SLWS057 – AUGUST 1999

# ac electrical characteristics $V_{CCP} = V_{DD} = V_{DDA} = 3.75$ V, $T_A = 25^{\circ}C$ (unless otherwise noted) (continued)

#### frequency synthesizers

#### main divider

|       | PARAMETER                                         | TEST CONDITIONS                                                                 | MIN | TYP | MAX  | UNIT |

|-------|---------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|------|------|

| RXLO± | Main synthesizer input frequency                  |                                                                                 |     |     | 2000 | MHz  |

| RXLO± | Main synthesizer input power                      | AC coupled, external shunt 50- $\Omega$ single-ended, 100 $\Omega$ differential |     | -17 |      | dBm  |

| RXLO± | Main synthesizer input harmonics and subharmonics | No multiclocking                                                                | 30  |     |      | dBc  |

#### reference divider

| PARAMETER |                     | TEST CONDITIONS  | MIN | TYP | MAX | UNIT |

|-----------|---------------------|------------------|-----|-----|-----|------|

| INR       | Operating frequency |                  |     |     | 25  | MHz  |

|           | Harmonics           | No multiclocking | 10  |     |     | dBc  |

#### auxiliary divider

| PARAMETER |                                                                                                                                                    | TEST CONDITIONS | MIN              | TYP | MAX | UNIT |     |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----|-----|------|-----|

|           | Auxiliary synthesizer input frequency         A         Auxiliary synthesizer input signal amplitude         Auxiliary synthesizer input harmonics |                 |                  |     | 110 |      | MHz |

| INA       |                                                                                                                                                    |                 | No multiclocking | 0.2 |     |      | VPP |

|           |                                                                                                                                                    |                 |                  | 10  |     |      | dBc |

| 7         | Auxiliary synthesizer input impedance                                                                                                              | Resistance      |                  | 5   | 100 |      | kΩ  |

| ZINA      |                                                                                                                                                    |                 |                  |     |     | 3    | pF  |

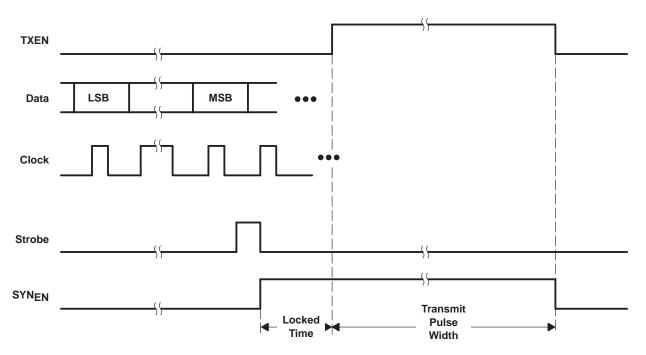

#### timing requirements, serial data interface (see Figure 6)

|                      | PARAMETER                                  | TEST CONDITIONS    | MIN TYP MAX                                                                                   | UNIT  |  |

|----------------------|--------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------|-------|--|

| DATA                 | Serial data input rate                     |                    | 10                                                                                            | MHz   |  |

| CLOCK                | Serial data clock input                    |                    | 10                                                                                            | MHz   |  |

| STROBE               | Serial data strobe input                   |                    | 10                                                                                            |       |  |

| TYEN                 | Transmit anoble                            | Transmit enable    | TXEN=1                                                                                        | Logio |  |

| TXEN Transmit enable |                                            | Transmit disable   | TXEN=0                                                                                        | Logic |  |

| t <sub>su</sub>      | Setup time: Data to CLOCK, CLOCK to STROBE |                    | 30                                                                                            | ns    |  |

| t <sub>k</sub>       | Hold time. CLOCK to DATA                   |                    | 30                                                                                            | ns    |  |

|                      |                                            | CLOCK              | 30                                                                                            |       |  |

|                      |                                            | STROBE (B-G words) | 100                                                                                           | ]     |  |

| t <sub>sw</sub> Puls | Pulse width                                | A-word, $PR = 01$  | $1/f_{VCO} \times (NM2 \times 65) + t_W$                                                      | ns    |  |

|                      |                                            | A-word, PR = 10    | $\begin{array}{c} 1/f_{VCO} \times (NM2 \times 65) + \\ (NM3+1) \times 72) + t_W \end{array}$ |       |  |

SLWS057 - AUGUST 1999

#### PARAMETER MEASUREMENT INFORMATION

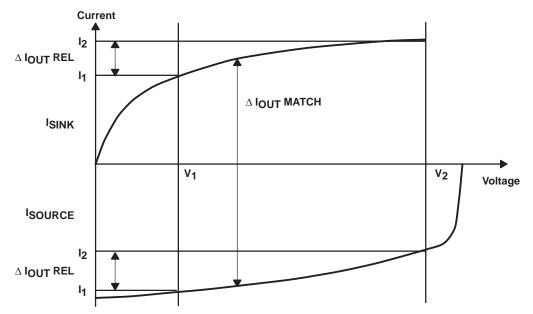

#### charge-pump current output definitions

Figure 1. Charge-Pump Output Current Definitions

The relative output current variation is defined as the percent difference between charge-pump current output at two charge-pump output voltages and the mean charge-pump current output (see Figure 1):

$$\frac{\Delta I_{OUT REL}}{|I_{OUT MEAN}|} = 2 \times \frac{(I_2 - I_1)}{|(I_2 + I_1)|} \times 100\%; \text{ with } V_1 = 0.7 \text{ V}, V_2 = V_{DDA} - 0.8 \text{ V}.$$

Output current matching is defined as the difference between charge-pump sinking current output and charge-pump sourcing current output at a given charge-pump output (see Figure 1).

$\Delta I_{OUT MATCH} = I_{SINK} - I_{SOURCE}$ ; with  $V_1 \leq Voltage \leq V_2$ .

SLWS057 - AUGUST 1999

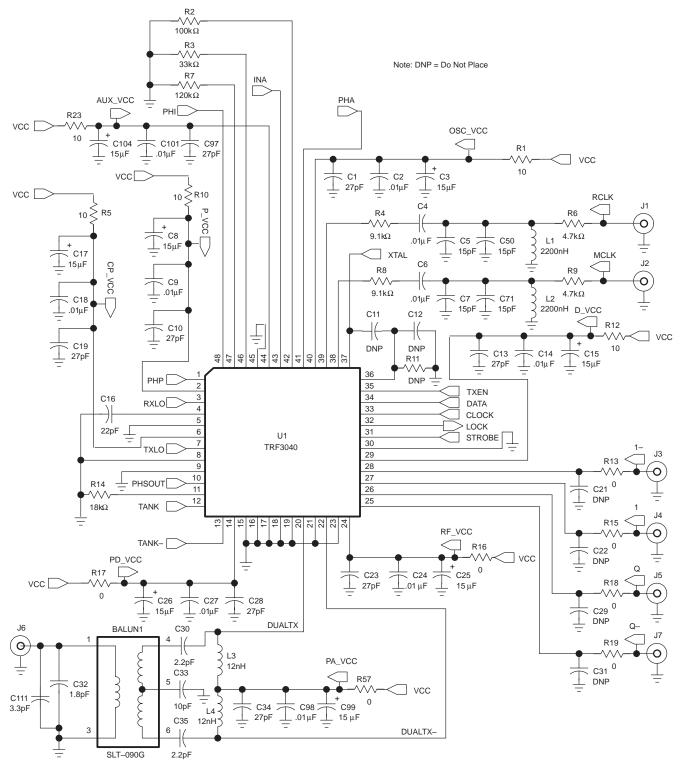

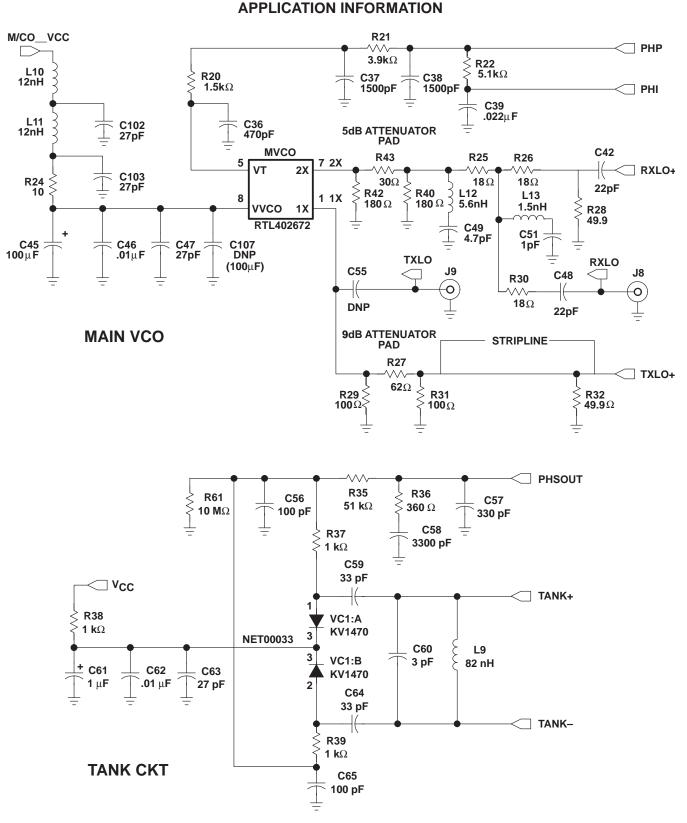

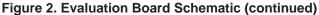

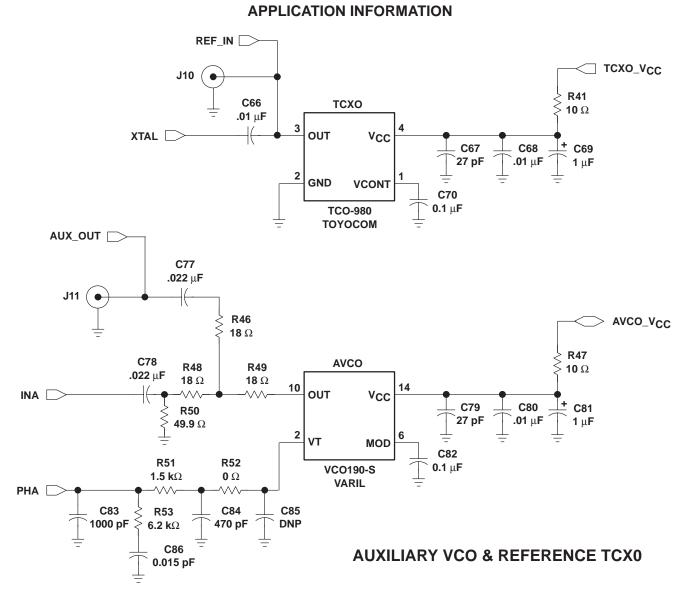

#### **APPLICATION INFORMATION**

Figure 2. Evaluation Board Schematic

SLWS057 - AUGUST 1999

SLWS057 - AUGUST 1999

Figure 2. Evaluation Board Schematic (continued)

SLWS057 - AUGUST 1999

Figure 2. Evaluation Board Schematic (PC Interface and Evaluation Board DC Supply Circuitry Only) (continued)

SLWS057 - AUGUST 1999

#### **APPLICATION INFORMATION**

#### Table 1. TRF3040 Evaluation Board Parts List

| DESIGNATORS                                                  | DESCRIPTION        | VALUE    | QTY | SIZE<br>(mm) | MANUFACTURER | MANUFACTURER<br>P/N |

|--------------------------------------------------------------|--------------------|----------|-----|--------------|--------------|---------------------|

| C 1, 10, 13, 19, 23, 28, 34, 47, 63,<br>67,79, 97, 102, 103  | Capacitor          | 27 pF    | 14  | 0603         | Murata       | GRM39COG series     |

| C 2, 4, 6, 9, 14, 18, 24, 27,46, 62, 66, 68, 80, 92, 98, 101 | Capacitor          | 0.01 μF  | 16  | 0603         | Murata       | GRM39COG series     |

| C 3, 8, 15, 17, 25, 26, 99, 104                              | Tantalum capacitor | 15 μF    | 8   | 6032–C       | Venkel       | TA010TCM series     |

| C 5, 7, 50, 71                                               | Capacitor          | 15 pF    | 4   | 0603         | Murata       | GRM39COG series     |

| C 11, 12, 21, 22, 29, 31, 55, 85, 107                        | Capacitor          | DNP      | 9   |              |              |                     |

| C 16, 42, 48                                                 | Capacitor          | 22 pF    | 3   | 0402         | Murata       | GRM39COG series     |

| C 30, 35                                                     | Capacitor          | 2.2 pF   | 2   | 0603         | Murata       | GRM39COG series     |

| C 32                                                         | Capacitor          | 1.8 pF   | 1   | 0603         | Murata       | GRM39COG series     |

| C 33                                                         | Capacitor          | 10 pF    | 1   | 0603         | Murata       | GRM39COG series     |

| C 36, 84                                                     | Capacitor          | 470 pF   | 2   | 0603         | Murata       | GRM39COG series     |

| C 37, 38                                                     | Capacitor          | 1500 pF  | 2   | 0603         | Murata       | GRM39COG series     |

| C 39, 77, 78                                                 | Capacitor          | 0.022 μF | 3   | 0603         | Murata       | GRM39COG series     |

| C 45                                                         | Tantalum capacitor | 100 μF   | 1   | 6032-C       | Venkel       | TA010TCM series     |

| C 49, C51                                                    | Capacitor          | 3.9 pF   | 1   | 0603         | Murata       | GRM39COG series     |

| C 55                                                         | Capacitor          | DNP      | 1   | 0402         |              |                     |

| C 56, 65                                                     | Capacitor          | 100 pF   | 2   | 0603         | Murata       | GRM39COG series     |

| C 57                                                         | Capacitor          | 330 pF   | 1   | 0603         | Murata       | GRM39COG series     |

| C 58                                                         | Capacitor          | 3300 pF  | 1   | 0603         | Murata       | GRM39COG series     |

| C 59, 64                                                     | Capacitor          | 33 pF    | 2   | 0603         | Murata       | GRM39COG series     |

| C 60                                                         | Capacitor          | 3 pF     | 1   | 0603         | Panasonic    | ECU-V1 series       |

| C 61, 69, 81, 87, 88, 89, 90, 91, 94, 100                    | Tantalum capacitor | 1 μF     | 10  | 3216-A       | Venkel       | TA010TCM series     |

| C 70, 82, 93, 95, 96                                         | Capacitor          | 0.1 μF   | 5   | 0603         | Murata       | GRM39COG series     |

| C 83                                                         | Capacitor          | 1000 pF  | 1   | 0603         | Murata       | GRM39COG series     |

| C 86                                                         | Capacitor          | 0.015 μF | 1   | 0603         | Murata       | GRM39COG series     |

| C 109, 110                                                   | Tantalum capacitor | 10 μF    | 2   | 3216-A       | Venkel       | TA010TCM series     |

| C 111                                                        | Capacitor          | 3.3 pF   | 1   | 0603         | Murata       | GRM39COG series     |

| 8 J 8                                                        | SMA-V              |          | 1   |              | EF Johnson   | 142-0701-201        |

| L 1, 2                                                       | Inductor           | 2200 nH  | 2   | 1008         | Coilcraft    | 0603HS series       |

| L 3, 4, 10, 11                                               | Inductor           | 12 nH    | 4   | 0603         | Coilcraft    | 0603HS series       |

| L 12, 13                                                     | Inductor           | 4.7 nH   | 1   | 0603         | Coilcraft    | 0603HS series       |

| L9                                                           | Inductor           | 82 nH    | 1   | 0603         | Coilcraft    | 0603HS series       |

| R 1, 5, 10, 12, 23, 24, 41, 47                               | Resistor           | 10       | 8   | 0603         | Panasonic    | ERJ-3GSYJ series    |

| R 2                                                          | Resistor           | 100K     | 1   | 0603         | Panasonic    | ERJ-3GSYJ series    |

| R 3                                                          | Resistor           | 33K      | 1   | 0603         | Panasonic    | ERJ-3GSYJ series    |

| R 4, 8                                                       | Resistor           | 9.1K     | 2   | 0603         | Panasonic    | ERJ-3GSYJ series    |

| R 6, 9                                                       | Resistor           | 4.7K     | 2   | 0603         | Panasonic    | ERJ-3GSYJ series    |

| R 7                                                          | Resistor           | 120K     | 1   | 0603         | Panasonic    | ERJ-3GSYJ series    |

| R 11                                                         | Resistor           | DNP      | 1   | 0603         | Panasonic    | ERJ-3GSYJ series    |

SLWS057 - AUGUST 1999

#### **APPLICATION INFORMATION**

#### Table 1. TRF3040 Evaluation Board Parts List (continued)

| DESIGNATORS                      | DESCRIPTION                      | VALUE | QTY | SIZE<br>(mm) | MANUFACTURER      | MANUFACTURER<br>P/N |

|----------------------------------|----------------------------------|-------|-----|--------------|-------------------|---------------------|

| R 13, 15, 16, 17, 18, 19, 52, 57 | Resistor                         | 0     | 8   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 14                             | Resistor                         | 18K   | 1   | 0603         | Panasonic         | ERS-36SYJ series    |

| R 20, 51                         | Resistor                         | 1.5K  | 2   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 22                             | Resistor                         | 5.1K  | 1   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 25, 26, 30                     | Resistor                         | 18    | 3   | 0402         | Panasonic         | ERJ-2GEJ series     |

| R 27                             | Resistor                         | 62    | 1   | 0402         | Panasonic         | ERJ-2GEJ series     |

| R 28, 32                         | Resistor                         | 49.9  | 2   | 0402         | Panasonic         | ERJ-2GEJ series     |

| R 29, 31                         | Resistor                         | 100   | 2   | 0402         | Panasonic         | ERJ-2GEJ series     |

| R 40, 42                         | Resistor                         | 430   | 2   | 0402         | Panasonic         | ERJ-2GEJ series     |

| R 46, 48, 49                     | Resistor                         | 18    | 3   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 50                             | Resistor                         | 49.9  | 1   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 35, 79                         | Resistor                         | 51    | 2   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 36                             | Resistor                         | 360   | 1   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 37, 38, 39                     | Resistor                         | 1K    | 3   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 43                             | Resistor                         | 10    | 1   | 0402         | Panasonic         | ERJ-2GEJ series     |

| R 53                             | Resistor                         | 6.2K  | 1   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 55, 56, 58, 64, 65, 66         | Resistor                         | 220   | 6   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 59, 60, 63, 67, 80             | Trimpot                          | 1K    | 5   | 3313J        | Bourns            | 3313J-1-102E        |

| R 61                             | Resistor                         | 10M   | 1   | 0805         | Panasonic         | ERJ-3GSYJ series    |

| R 68                             | Trimpot                          | 500   | 1   | 3313J        | Bourns            | 3313J-1-102E        |

| R 69, 70, 71, 72                 | Resistor                         | 1.8K  | 4   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 73, 74, 75, 76                 | Resistor                         | 3.6K  | 4   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 77                             | Resistor                         | 2K    | 1   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| R 78                             | Resistor                         | 2.7K  | 1   | 0603         | Panasonic         | ERJ-3GSYJ series    |

| U 1                              | Integrated circuit               |       | 1   |              | Texas Instruments | TRF3040             |

| U 3, 4, 5, 6                     | Opto-coupler                     |       | 4   |              | Motorola          | 4N28S               |

| U 7                              | Opto-coupler                     |       | 1   |              | Motorola          | MOC8030             |

| VC 1                             | Varactor                         |       | 1   |              | Toko              | KV1470              |

| VR 1, 2, 3, 5, 6                 | Voltage regulator                |       | 5   |              | Motorola          | LM317LD             |

| VR 4                             | Voltage regulator                |       | 1   |              | Motorola          | LM317MDT            |

| BALUN 1                          | Transformer                      | 4:1   | 1   |              | Hitachi           | SLT-090G            |

| P 1                              | DB25M                            |       | 1   |              | AMP               | 747238-4            |

| J 1, 2, 6, 9, 10, 11             | SMA_H                            |       | 7   |              | EF Johnson        | 142-0701-831        |

| J 3, 4, 5, 7                     | BNC-90                           |       | 4   |              | AMP               | 413631-1            |

| MVCO                             | Voltage-controlled<br>oscillator |       | 1   |              | Panasonic         | RTL402672           |

| AVCO                             | Voltage-controlled oscillator    |       | 1   |              | Vari–L            | VCO190-S            |

SLWS057 - AUGUST 1999

#### **APPLICATION INFORMATION**

| DESIGNATORS                                                                                                                                       | DESCRIPTION                                   | VALUE | QTY | SIZE<br>(mm) | MANUFACTURER              | MANUFACTURER<br>P/N |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|-----|--------------|---------------------------|---------------------|

| тсхо                                                                                                                                              | Temperature-Compensated<br>Crystal Oscillator |       | 1   |              | Toyocom                   | TCO-980 series      |

| CLOCK_TP1<br>DATA_TP1<br>LD_TP1<br>TXEN_TP1<br>STROBE_TP1<br>MVCO_TP<br>OPTO_VCC_TP<br>+5V_TP<br>AVCO_VCC_TP<br>TXCO_TP<br>VCC_TP<br>POWER<br>GND | Test probe connector                          |       | 13  |              | Components<br>Corporation | TP-105-01 series    |

#### Table 1. TRF3040 Evaluation Board Parts List (continued)

SLWS057 - AUGUST 1999

#### **PRINCIPLES OF OPERATION**

#### operational modes

The TRF3040 has two separate operational modes: an advanced mobile phone system (AMPS) mode, and a digital advanced mobile phone system (DAMPS) mode, both of which are selected based on which cellular system is in use. In addition, the TRF3040 can be operated in different power-saving mode settings. The power-saving modes disable the circuitry that is not in use at the time in order to reduce power consumption. During sleep mode, only the circuitry required to provide a master clock to the digital portion of the system is active. In standby mode, the main synthesizer, the auxiliary synthesizer, and the master clock circuitries are enabled. In transmit mode, all functions of the device are enabled. Table 2 describes the functions that are enabled during each mode, and Table 3 describes the related programming control bit(s).

|                          |       | AMPS/DAMP | S        |

|--------------------------|-------|-----------|----------|

| FUNCTION ENABLED         | SLEEP | STANDBY   | TRANSMIT |

| Crystal oscillator       | Х     | Х         | Х        |

| TXIF phase detector      |       |           | Х        |

| ÷N                       |       |           | Х        |

| TXIF buffer              |       |           | Х        |

| TXIF_VCO                 |       |           | Х        |

| TXIF_VCO buffer          |       |           | Х        |

| SSCSB converter          |       |           | Х        |

| MCLK buffer              | Х     | Х         | Х        |

| RCLK buffer              |       | Х         | Х        |

| TXLO buffer              |       |           | Х        |

| RXLO buffer              |       | Х         | Х        |

| I/Q modulator            |       |           | Х        |

| DUALTX VGA               |       |           | Х        |

| Control logic            | Х     | Х         | Х        |

| Reference divider buffer |       | Х         | Х        |

| Auxiliary divider buffer |       | Х         | Х        |

| Main phase detector      |       | Х         | Х        |

| Auxiliary phase detector |       | Х         | Х        |

| Lock detect              |       | Х         | Х        |

| Table 2 | TRF3040   | Power-Mode     | Function  | llsane |

|---------|-----------|----------------|-----------|--------|

|         | 1111 3040 | F OWEI -INIOUE | I UNCLION | Usaye  |

| Table 3. TRF3040 | Programming | Power-Mode I | Function |

|------------------|-------------|--------------|----------|

|------------------|-------------|--------------|----------|

| FIELD BIT(S) | SLEEP | STANDBY | TRANSMIT |

|--------------|-------|---------|----------|

| SM           | 0:on  | 1:off   | 1:off    |

| SE           | 0:off | 0:off   | 1:on     |

| EA           | 0:off | 1:on    | 1:on     |

| EM           | 0:off | 1:on    | 1:on     |

#### frequency synthesizer

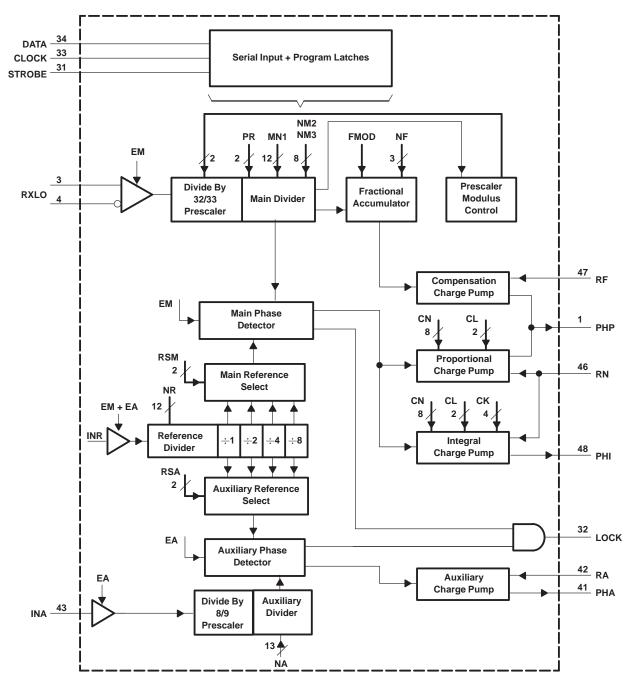

The frequency synthesizer consists of the serial data interface, the main channel synthesizer, and the auxiliary synthesizer. Figure 3 illustrates the functionality of the frequency synthesizer.

SLWS057 - AUGUST 1999

#### **PRINCIPLES OF OPERATION**

Figure 3. Frequency Synthesizer Functional Block Diagram

SLWS057 – AUGUST 1999

#### PRINCIPLES OF OPERATION

#### serial programming input

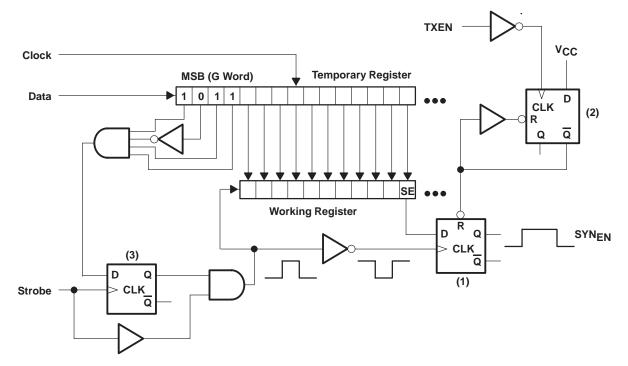

The TRF3040 operates using CLOCK, DATA, and STROBE pins of the serial data interface. The serial programming data is structured into 24-bit words, of which one or four bits are dedicated address bits.

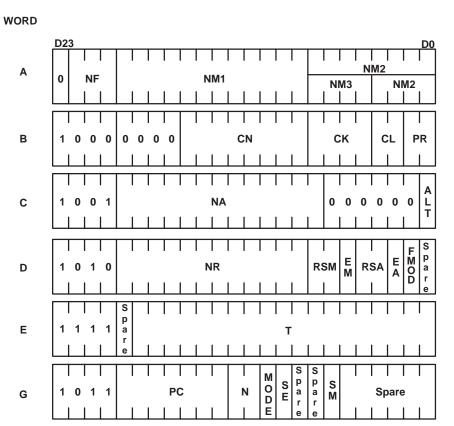

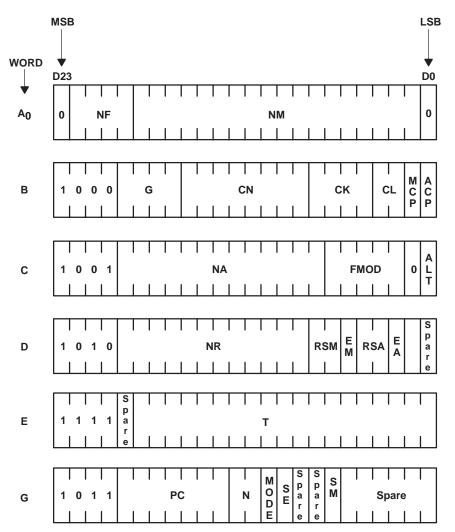

Figure 4 shows the format and the content of each word. Table 4 lists the symbols, number of bits, and the function for each word used in the standard programming mode (ALT = 0). Similarly, the alternate programming mode (ALT = 1) is described in Figure 5 and Table 5.

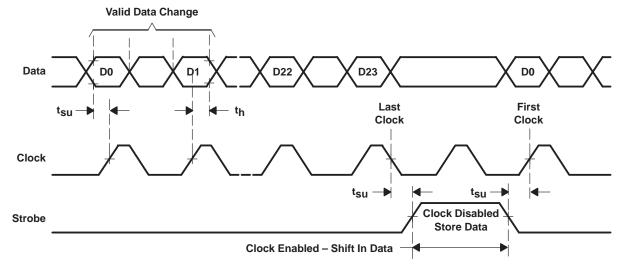

Figure 6 shows the timing diagram for the serial input. When the STROBE goes low, the signal on the DATA input is clocked into a shift register on the positive edges of the CLOCK. When the STROBE goes high, depending on the 1 or 4 address bit(s), data is latched into different working or temporary registers. To fully program the modulator/synthesizer, five words must be sent: G, D, C, B, and A. The E-word is for testing purposes only.

The A-word contains new data for the main divider. The A-word is loaded into the working registers only when a main divider synchronization signal is active to avoid phase jumps when reprogramming the main divider.

The data for CN and PR is stored by the B-word in temporary registers. The data in these temporary registers is loaded into the work registers together with the A-word. This avoids false main-divider input when the A-word is loaded.

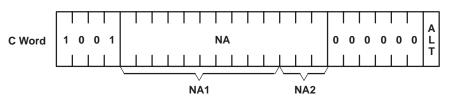

The value of the auxiliary divider ratio, NA, is defined by a 13-bit field, and the operational mode of the main synthesizer is determined by the least significant bit (LSB) of the C-word:

Standard mode: ALT = 0 Alternate mode: ALT = 1

The content of the D-word defines the operation of the reference divider. The OR function of bits EA and EM enables the buffer/amplifier input stage. The reference divider ratio is determined by the value of NR. The main and auxiliary synthesizer sections can individually select a reference postscaler division of 1, 2, 4, or 8 by selecting fields RSM and RSA, respectively.

The G-word programs all other functions: VGA power control,  $\div$  N (TXIF loop), SE (TXIF synthesizer loop enable), AMPS and DAMPS modes, and sleep mode.

The E-word is for testing purposes only and is reset when programming the D-word.

SLWS057 - AUGUST 1999

#### PRINCIPLES OF OPERATION

Figure 4. Serial Input Word Format (Standard Programming, ALT = 0)

SLWS057 - AUGUST 1999

#### PRINCIPLES OF OPERATION

#### Table 4. Standard Programming (ALT = 0) Function Table (see Notes 4 and 5)

| SYMBOL | BITS                         | FUNCTION                                                                                                                |

|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| NM1    | 12                           | Number of main divider cycles when the prescaler is programmed in ratio R1 <sup>†</sup>                                 |

| NM2    | 8 if PR = X1<br>4 if PR = X0 | Number of main divider cycles when the prescaler is programmed in ratio R2 $^{\dagger}$                                 |

| NM3    | 4 if PR = X0<br>0 otherwise  | Number of main divider cycles when the prescaler is programmed in ratio R3 $^{\dagger}$                                 |

| PR     | 2                            | Main synthesizer prescaler type in use: PR = X1: modulus 2 prescaler (64/65)<br>PR = X0: modulus 3 prescaler (64/65/72) |

| NF     | 3                            | Main synthesizer fractional-N increment                                                                                 |

| FMOD   | 1                            | Main synthesizer fractional-N modulus selection flag:<br>1 = modulo 8<br>0 = modulo 5                                   |

| CN     | 8                            | Current setting factor for main charge pumps                                                                            |

| CL     | 2                            | Acceleration factor for proportional charge pump current                                                                |

| CK     | 4                            | Acceleration factor for integral charge pump current                                                                    |

| EM     | 1                            | Main divider enable flag (see Table 11)                                                                                 |

| EA     | 1                            | Auxiliary divider enable flag (see Table 11)                                                                            |

| RSM    | 2                            | Reference select for main phase detector                                                                                |

| RSA    | 2                            | Reference select for auxiliary phase detector                                                                           |

| NR     | 12                           | Reference divider ratio                                                                                                 |

| NA     | 13                           | Auxiliary divider ratio                                                                                                 |

| Ν      | 2                            | TXIF synthesizer divider ratio, +N, N = 6, 7, 8, 9 (see Note 6)                                                         |

| PC     | 7                            | Variable gain amplifier (VGA) power control function (see Table 14)                                                     |

| SE     | 1                            | TXIF synthesizer on/off. SE=1, TXIF synthesizer on; SE=0, TXIF synthesizer off                                          |

| SM     | 1                            | Sleep mode bit; SM bit shuts down the synthesizers and the modulator section (see Table 3)                              |

| MODE   | 1                            | Mode control: MODE=1, digital (DAMPS); MODE=0, analog (AMPS) (see Note 7)                                               |

| ALT    | 1                            | Alternate programming bit; ALT=0, standard (STD) mode; ALT=1, enhanced (ALT) mode (see Note 8)                          |

| Т      | 19                           | Test mode connection of internal signals to lock pin: see test modes section                                            |

<sup>†</sup> Not including reset cycles and fractional-N effects. R1 = 64, R2 = 65, R3 = 72.

NOTES: 4. Data bits are shifted in on the leading clock edge, with the least significant bit (LSB) first in and the most significant bit (MSB) last.

5. On the rising edge of the strobe and with the address decoder output = 1, the contents of the input shift register are transferred to the working registers. The strobe rising edge comes one-half clock period after the clock edge on which the MSB of a word is shifted in.

6. Field bits setting for the TXIF synthesizer divider ratio

| FIELD BIT |    | ÷N  |  |

|-----------|----|-----|--|

| N1        | N0 | ÷ N |  |

| 0         | 0  | 6   |  |

| 0         | 1  | 7   |  |

| 1         | 0  | 8   |  |

| 1         | 1  | 9   |  |

- 7. The MODE bit allows a reduction in current for the DUALTX output driver while in AMPS mode.

- 8. The ALT programming bit allows the user to specify an enhanced programming scheme which allows for a fully programmable fractional modulus of 1 to 16 for the main synthesizer.

SLWS057 - AUGUST 1999

Figure 5. Serial Input Word Format (Alternate Programming, ALT = 1)

SLWS057 - AUGUST 1999

## PRINCIPLES OF OPERATION

#### Table 5. Alternate Programming (ALT = 1) Function Table

| SYMBOL | BITS | FUNCTION                                                                                   |

|--------|------|--------------------------------------------------------------------------------------------|

| NF     | 4    | Main synthesizer fractional-N increment                                                    |

| NM     | 18   | Overall main divider integer division ratio                                                |

| CN     | 8    | Binary current-setting factor for main charge pumps                                        |

| G      | 4    | Speed-up mode duration (number of reference divider cycles)                                |

| СК     | 4    | Binary acceleration factor for integral charge pump current                                |

| CL     | 2    | Binary acceleration factor for proportional charge pump current                            |

| MCP    | 1    | Main charge pump polarity                                                                  |

| ACP    | 1    | Auxiliary charge polarity                                                                  |

| NA     | 13   | Auxiliary charge ratio                                                                     |

| FMOD   | 5    | Fraction accumulator modulus                                                               |

| NR     | 12   | Reference divider ratio                                                                    |

| RSM    | 2    | Reference select for main phase detector                                                   |

| EM     | 1    | Main divider enable flag (see Table 11)                                                    |

| RSA    | 2    | Reference select for auxiliary phase detector                                              |

| EA     | 1    | Auxiliary divider enable flag (see Table 11)                                               |

| Ν      | 2    | TXIF synthesizer divider ratio, +N, N = 6, 7, 8, 9                                         |

| PC     | 7    | Variable gain amplifier (VGA) power control function (see Table 14)                        |

| SE     | 1    | TXIF synthesizer on/off. SE=1, TXIF synthesizer on; SE=0, TXIF synthesizer off             |

| SM     | 1    | Sleep mode bit: SM bit shuts down the synthesizers and the modulator section (see Table 3) |

| MODE   | 1    | Mode control: mode=1, digital (DAMPS); mode=0, analog (AMPS)                               |

| ALT    | 1    | Alternate programming bit: ALT=0, standard (STD) mode; ALT=1, enhanced (ALT) mode          |

| Т      | 19   | Test mode connection of internal signals to LOCK pin (see test modes section)              |

Figure 6. Serial Input Timing Sequence

SLWS057 - AUGUST 1999

#### PRINCIPLES OF OPERATION

#### reference variable divider

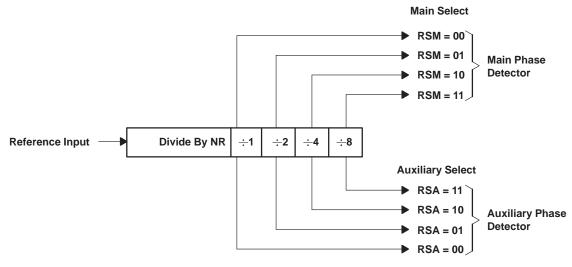

The internal reference signal INR, which is generated by the external crystal oscillator, is amplified to logic level by a single-ended input buffer. The OR function of the serial input bits EM an EA enables this input buffer. Subsequently, the output of the input buffer feeds the reference divider which consists of a 12-bit programmable divide-by-NR (NR = 4 to 4095) and a four-section postscaler. The main and auxiliary synthesizer sections can individually select a reference postscaler division of 1, 2, 4, or 8 by selecting RSM and RSA, respectively, as shown in Figure 7.

Figure 7. Reference Variable Divider

#### auxiliary variable divider

The input signal on INA is amplified to logic level by a single-ended input buffer, which has sufficient sensitivity for direct connection to a typical VCO (200 mVpp at 200 MHz). The input stage is enabled when the serial control bit EA = 1. The auxiliary divider consists of a 13-bit programmable divider with a 8/9 dual-modulus prescaler. The 13-bit field divider is composed of two separate counters: a 3-bit NA2 counter and a 10-bit NA1 counter. The total divider ratio value can be expressed as:  $NA = 8 \times (NA1 - NA2) + 9 \times NA2$ , where  $7 \le NA1 \le 1023$ , and  $0 \le NA2 \le 7$ . This results in a continuous integral divide range of 56 to 8191. The detail of the 13-bit field of the auxiliary divider is shown in Figure 8.

SLWS057 - AUGUST 1999

#### PRINCIPLES OF OPERATION

#### main variable divider - general

The input signal on RXLO is amplified to a logic level by a differential-input comparator giving a common mode rejection. The input stage is enabled by serial control bit EM = 1. Disabling means that all currents in the comparator are switched off. The main variable divider is programmed using two different schemes: standard and alternate.

The standard programming scheme (ALT=0) is referenced to a main divider section that implements a dual/triple-modulus prescaler [(64/65)/(64/65/72)] design. The dual/triple modulus prescaler is actually synthesized using a 32/33 dual-modulus prescaler with conversions that occur within the TRF3040 and are transparent to the user.

Depending on the value of the prescaler select PR, the bit capacity for NM1, NM2, and NM3 is defined, as listed in Table 6 (see also Figure 4).

|    | BIT CAPACITY |     |     |

|----|--------------|-----|-----|

| PR | NM1          | NM2 | NM3 |

| 00 | 12           | 8   | 0   |

| 01 | 12           | 8   | 0   |

| 10 | 12           | 4   | 4   |

| 11 | 12           | 4   | 4   |

Table 6. Main Variable Divider Bit Capacity

The total N-division ratio, as a function of the 64/65 dual-modulus and the 64/65/72 triple-modulus prescaler can be expressed as:

- N<sub>total</sub> = 64(NM1 + 2) + 65(NM2), where PR = 0X,

- N<sub>total</sub> = 64(NM1 + 2) + 65(NM2) + 72(NM3 + 1), where PR = 1X.

For contiguous channels, the values of NM1, NM2, and NM3 are defined:

- For PR = 0X: 61 ≤ NMI ≤ 4095 and 0 ≤ NM2 ≤ 63, which yields minimum and maximum divide ratios of 4032 and 266303, respectively.

- For PR = 1X:  $14 \le NMI \le 4095$  and  $0 \le NM2 \le 15$  and  $0 \le NM3 \le 15$ , which yields minimum and maximum divide ratios of 1096 and 264335, respectively.

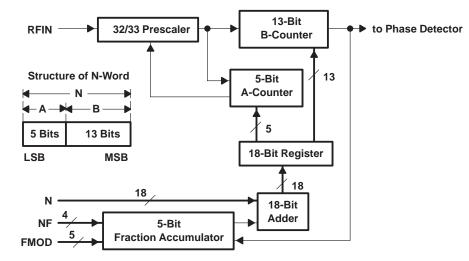

The alternate programming scheme (ALT=1) is provided for ease of use. The 32/33 dual modulus prescaler is the reference of the alternate programming scheme. Referring to the A-word of Figure 4 shown previously, the main divider consists of 18-bit NM-field counters. The NM-field counter section is composed of two separate counters: a 5-bit A-counter and a 13-bit B-counter, as shown in Figure 9. The prescaler divides by 33 until the A-counter reaches terminal count and then divides by 32 until the B-counter reaches terminal count where upon both counters reset and the cycle repeats.

The total NM division is defined as:

$NM_{Total} = 32(B - A) + 33(A)$ , where  $0 \le A \le 31$  and  $31 \le B \le 8191$ .

This results in a continuous integral divide range of 992 to 262143. If B < 31, the synthesizer no longer provides contiguous channels. It is important to note that the value assigned to A is never greater than the value assigned to B.

SLWS057 - AUGUST 1999

#### PRINCIPLES OF OPERATION

main variable divider – general (continued)

Figure 9. Main Divider Organization

#### main variable divider - synchronization

The A-word is loaded into working registers only when a main divider synchronization signal is active in order to avoid phase jumps when reprogramming the main divider. The synchronization signal is generated by the main divider and is active when the main divider reaches its terminal count; also at this time, a main divider output pulse is sent to the main phase detector. The new A-word is correctly loaded provided that the STROBE signal is at an active high.

#### main variable divider - fractional accumulator

The TRF3040 main synthesizer loop can operate as a traditional integer-N feedback phase-locked loop or as a fractional-N feedback phase-locked loop. The integer-N feedback loop divides the VCO frequency by integer values of N that result in phase detector reference comparisons at the desired channel spacing. A fractional-N feedback loop divides the VCO frequency by an integer term plus a fractional term that results in phase detector reference comparisons at the desired channel spacing.

Integer-N division: VCO frequency  $\div$  N = Phase detector reference frequency = channel spacing

Fractional-N division: VCO frequency  $\div$  (N + NF/FMOD) = Phase detector reference frequency = FMOD × channel spacing

where  $0 \le NF < FMOD$  and  $1 \le FMOD \le 16$ .

Because the programmable main counter and prescaler can not divide by a fraction of an integer, fractional-N division is accomplished by averaging main divider cycles of division by N and N+1. A fractional accumulator that is programmed with values of NF and FMOD is responsible for causing the main counter and prescaler sections to divide by N or N+1.

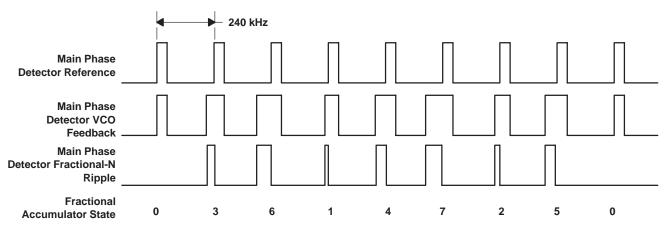

The fractional accumulator operates modulo-FMOD and is incremented by NF at the completion of each main divider cycle. When the fractional accumulator overflows, division by N+1 occurs. Otherwise, the main counters and prescaler divide by N; division by N+1 is transparent to the user. Table 7 shows the contents of the fractional accumulator and the resulting N or N+1 division for two fractional division ratios.

SLWS057 – AUGUST 1999

#### PRINCIPLES OF OPERATION

| NF = 3, FMOD = 8         |                   |  |  |

|--------------------------|-------------------|--|--|

| ACCUMULATOR<br>NUMERATOR | STATE             |  |  |

| 3                        | ÷N                |  |  |

| 6                        | ÷N                |  |  |

| 1                        | ÷ N + 1, overflow |  |  |

| 4                        | ÷N                |  |  |

| 7                        | ÷N                |  |  |

| 2                        | ÷ N + 1, overflow |  |  |

| 5                        | ÷N                |  |  |

| 0                        | ÷ N + 1, overflow |  |  |

| NF = 6, FMOD = 8         |                   |  |

|--------------------------|-------------------|--|

| ACCUMULATOR<br>NUMERATOR | STATE             |  |

| 6                        | ÷N                |  |

| 4                        | ÷ N + 1, overflow |  |

| 2                        | ÷ N + 1, overflow |  |

| 0                        | ÷ N + 1, overflow |  |

| 6                        | ÷N                |  |

| 4                        | ÷ N + 1, overflow |  |

| 2                        | ÷ N + 1, overflow |  |

| 0                        | ÷ N + 1, overflow |  |

#### **Table 7. Fractional Accumulator Operation**

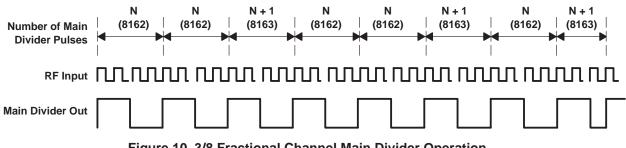

For example, suppose that the main synthesizer input frequency is 1958.97 MHz, the main phase detector reference frequency is 240 kHz, and a channel spacing of 30 kHz is realized. The value of FMOD = 8 would be selected because 240 kHz/30 kHz = 8. Dividing the main synthesizer input frequency by the reference frequency results in 1958.97  $\div$  0.24 = 8162.375 = 8162 + 3/8. As a result, the fractional accumulator overflow cycle of this particular frequency is described with NF=3 and FMOD=8 (see Table 7). Figure 10 illustrates the division by N and N+1 for this 3/8 fractional channel example.

Figure 10. 3/8 Fractional Channel Main Divider Operation

The mean division over the complete fractional accumulator cycle as shown in Figure 9 is:

$$N_{\text{MEAN}} = \frac{8162 + 8162 + 8163 + 8162 + 8162 + 8163 + 8162 + 8163}{8} = 8162.375$$

$$= 8162 + 3/8.$$

Therefore, fractional channels are available every 30 kHz or 240 kHz  $\frac{1}{FMOD} = \frac{240 \text{ kHz}}{8}$ .

#### main divider - integer channels

In the case where NF = 0, only division by N occurs and the fractional accumulator essentially is steady state with a numerator of 0 and never increments or overflows. A channel that requires NF = 0 is a pure integer channel because the fractional term of  $\frac{NF}{FMOD}$  is zero.

SLWS057 - AUGUST 1999

## PRINCIPLES OF OPERATION

#### main divider – fractional-N sidebands and compensation

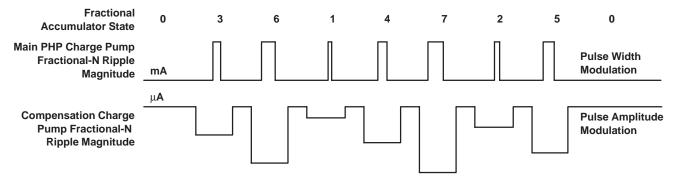

Programming a fractional-N channel means the main divider and prescaler divide by N or N + 1 as dictated by the operation of the fractional accumulator. Because the main divider operation is integer in nature and the desired VCO frequency is not, the output of the main phase detector is modulated with a resultant fractional-N phase ripple that, if left uncompensated, produces sideband energy. This phase ripple is proportional and synchronized to the contents of the fractional accumulator that is used to control fractional-N sideband energy. The fractional-N sideband energy. The fractional-N sidebands appear at offset frequencies from the VCO fundamental tone, which are multiples of NF/FMOD. Figure 11 shows the fractional-N phase detector ripple for a 3/8 fractional channel.

Figure 11. Fractional-N Phase Detector Ripple for 3/8 Fractional Channel

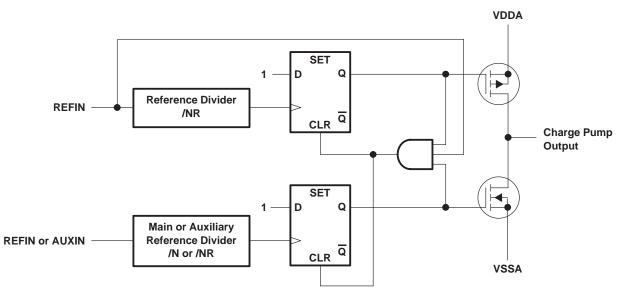

The TRF3040 has internal circuitry that provides a means to compensate for the phase detector fractional-N phase ripple thereby significantly reducing the magnitude of the fractional-N sidebands. Because the current waveform output of the main phase-locked loop (PLL) proportional charge pumps is modulated with the phase detector fractional-N phase ripple, a fractional-N compensation charge pump output is summed with the main PLL proportional charge pump.

Figure 12 shows the fractional-N ripple magnitude on the main PHP charge pump output. The magnitude is essentially constant and the pulse width is modulated with the contents of the fractional accumulator. The area under the Main PHP charge pump curve represents the amount of charge delivered to the system loop filter network. In order to minimize fractional-N sidebands in the VCO spectrum, the compensation current waveform is generated to have *equal* and *opposite* sign magnitude *areas* as the main PHP charge pump.

Figure 12. Main PHP and Compensation Charge Pump Fractional-N Waveforms for 3/8 Fractional Channel

SLWS057 – AUGUST 1999

#### PRINCIPLES OF OPERATION

#### main divider - fractional-N sidebands and compensation (continued)

The compensation waveform is pulse-amplitude modulated with the contents of the fractional accumulator. The main PHP pulse magnitude is much larger than the compensation pulse magnitude, but the compensation pulse has a much longer duration than that of the main PHP pulse. The compensation pulse is optimally centered about the main PHP charge pump pulse in order to avoid additional sideband energy due to phase-offset between the main and compensation pulses.

The following step illustrates a method for determining correct values for RN, RF, and CN for minimal fractional-N sidebands based on VCO frequency and reference frequency.

#### Assumptions: