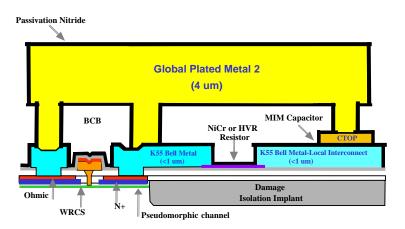

### **Process Cross Section Diagram**

#### **Updated Process Diagram**

#### **Features**

- D-Mode, -1.0 V Vp

- InGaAs Active Layer pHEMT Process

- 0.15 µm Low Cost Optical Lithography Gates

- High Density Interconnects:

- 1 Global

- 1 Local

- High-Q Passives

- Thin Film Resistors

- High Value Capacitors (620 pF/mm<sup>2</sup>

- Backside Vias Optional

- Based on Production TQP13 Processes

### **Process Description**

TriQuint's TQP15 process is based on our production-released TQP13 processes. TQP15 is a breakthrough technology offering both high breakdown voltage and high frequency/ gain capability all within an optical process technology that enables commercialization of mmw markets. TQP15 is targeted at the emergent Ka-band segment and is ideal for the VSAT, satellite communications, and point-to-point radio markets. The two metal interconnecting layers are encapsulated in a high performance dielectric that allows wiring flexibility, optimized die size and plastic packaging simplicity. Precision NiCr resistors and high value MIM capacitors are included allowing higher levels of integration, while maintaining smaller, cost-effective die sizes.

### **Applications**

- Medium Power, D-Mode Applications

- Point-to-Point Radio

- Converters

- VSAT

- Ka-band Power Amplifiers

- 1 of 7 -

# Process Details

# **Absolute Maximum Ratings**

| Storage Temperature Range   | -65 to +150 | Deg C |

|-----------------------------|-------------|-------|

| Operating Temperature Range | -55 to +150 | Deg C |

| Capacitor                   | 40          | V     |

### **Process Details**

| Transistor Details @ Vds = 3.0V |                |         |              |  |

|---------------------------------|----------------|---------|--------------|--|

| Element                         | Parameter      | Typical | Units        |  |

| D-Mode pHEMT                    | Vp (1uA/um)    | -1.0    | V            |  |

|                                 | Idss           | 380     | mA/mm        |  |

|                                 | Imax           | 580     | mA/mm        |  |

|                                 | Breakdown, Vdg | 14      | V            |  |

|                                 | Ft (peak)      | 80      | GHz          |  |

|                                 | Gm @ Idss      | 550     | mS/mm        |  |

| Common Process Element Details  |                |         |              |  |

| Gate Length                     | D-Mode         | 0.15    | μm           |  |

| Interconnect                    |                | 2       | Metal Layers |  |

| MIM Caps                        | Value          | 620     | pF/mm2       |  |

| Resistors                       | NiCr           | 50      | Ohms/sq      |  |

|                                 | Bulk           | 120     | Ohms/sq      |  |

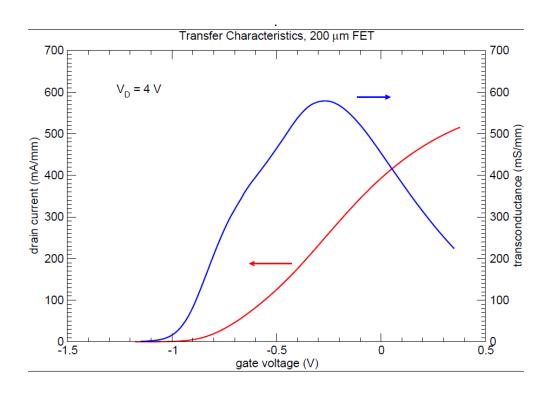

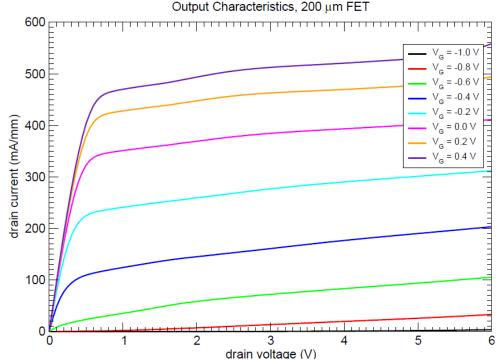

## **Performance Details**

Unless otherwise noted; models and graphs in this process data sheet are for devices on a full thickness substrate.

-3 of 7 -

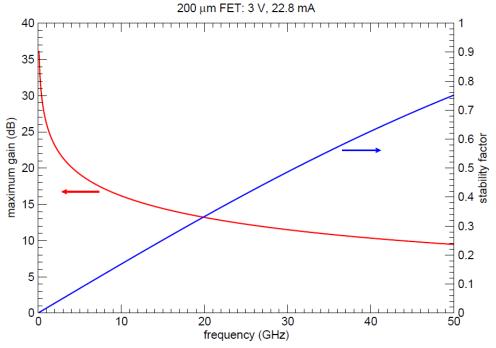

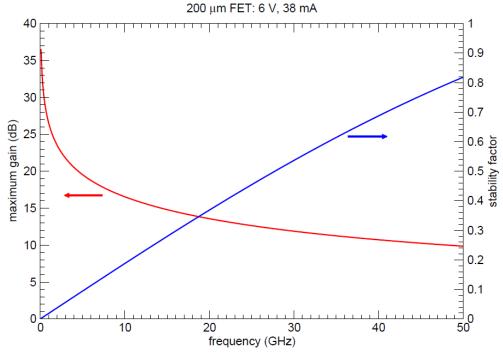

#### Maximum Available Gain/Stable Gain (MAG/MSG)

#### Maximum Available Gain/Stable Gain (MAG/MSG)

Unless otherwise noted; models and graphs in this process data sheet are for devices on a full thickness substrate.

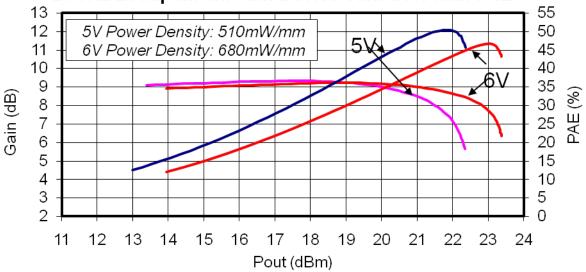

### 24GHz Loadpull: 4x75um Device Tuned for Max PAE

Devices used on a 100-um thick substrate.

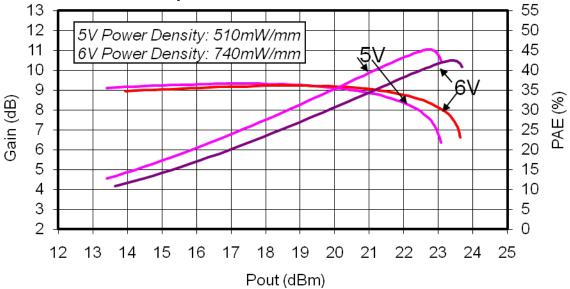

# 24GHz Loadpull: 4x75um Device Tuned for Po Max

Devices used on a 100-um thick substrate.

## **Prototyping and Development**

- Prototype Development Quick Turn (PDQ):

- o Shared mask set

- o Hot Lot cycle time

- Prototype Wafer Option (PWO):

- o Customer-specific masks; Customer schedule

- o 2 wafers delivered

- o With thinning and sawing; optional backside vias

## **Design Tool Status**

- Complete Design Manual

- Device Library of circuit elements: FETs, diodes, thin film resistors, capacitors, inductors

- · Design Kit for Agilent's ADS design environment

- Design Kit for AWR Microwave Office

- · Layout Library in GDS II format

- Cadence Development Kit with PCells

- · Layout Rule Sets for Design Rule Check for ICED, Cadence

#### **Process Qualification Status**

- Process fully released to production

- Full 150mm wafer Process Qualification complete

- For more information on Quality and Reliability, contact TriQuint or visit: www.triquint.com/manufacturing/QR/

# **Applications Support Services**

- Tiling of GDSII stream files including PCM

- Design Rule Check services

- · Layout Versus Schematic check services

- Test Development Engineering:

- o On-wafer

- Thermal Analysis Engineering

- Yield Enhancement Engineering

- Failure Analysis

# Manufacturing Services

- Mask making

- Production 150-mm wafer fab

- Wafer Thinning

- Wafer Sawing

- Substrate Vias

- DC Diesort Testing

- RF On-wafer testing

Process Data Sheet: Rev 9/14/2010 © 2009 TriQuint Semiconductor, Inc.

- 6 of 7 - Disclaimer: Subject to change without notice

Connecting the Digital World to the Global Network

# **TQP15**

#### 0.15 um D-mode pHEMT Foundry Service

### **Training**

For Training & PDQ Schedules, please visit: <a href="www.triquint.com/foundry/">www.triquint.com/foundry/</a>

#### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

Web: <u>www.triquint.com</u> Tel: +1.503.615.9000 Email: <u>Foundry\_Marketing@tqs.com</u> Fax: +1.503.615.8902

For technical questions and application information:

Email: Foundry Marketing@tgs.com

# **Important Notice**

The information contained herein is believed to be reliable. TriQuint makes no warranties regarding the information contained herein. TriQuint assumes no responsibility or liability whatsoever for any of the information contained herein. TriQuint assumes no responsibility or liability whatsoever for the use of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for TriQuint products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

TriQuint products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.