### **Applications**

- 3G / 4G Wireless Infrastructure

- CDMA, TD-CDMA, WCDMA, LTE

- Repeaters

- PTP Radio IF Chains

28-pin 6x6mm leadless SMT package

### **Product Features**

- 1.8-2.7 GHz Frequency Range

- 31 dB Maximum Gain at 2 GHz

- 31.5 dB Gain Range in 0.5 dB Steps

- +41.3 dBm Output IP3

- +25.4 dBm Output P1dB

- 1.5 dB Noise Figure

- Fully Internally Matched Module

- Integrated Blocking Capacitors, Bias Inductors

- 3-wire SPI Control Programming

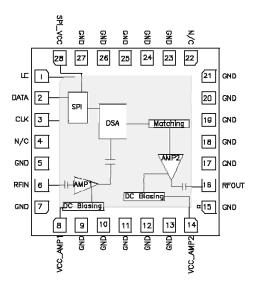

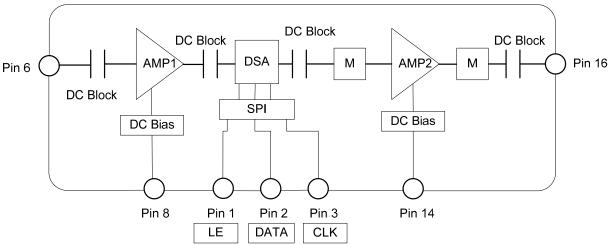

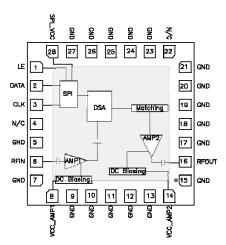

### **Functional Block Diagram**

### **General Description**

The TQM879006 is a digital variable gain amplifier (DVGA) featuring high linearity over the entire gain control range. The amplifier module features the integration of a low noise amplifier gain block, a digital-step attenuator (DSA), along with a high linearity ½W amplifier. The module has the added features of integrating all matching components with bias chokes and blocking capacitors. The internal DSA offers 0.5 dB step, 6-bit, and 31.5 dB range and is controlled with a serial periphery interface (SPI<sup>TM</sup>).

The TQM879006 features variable gain from -0.5 to 31dB at 2 GHz, has +41.3 dBm Output IP3, and +25.4 dBm P1dB. The amplifier also has a very low 1.5 dB Noise Figure (at maximum gain) allowing it to be an ideal DVGA for both receiver and transmitter applications. The amplifier operates from a single +5V supply and is available in a compact 28-pin 6x6 mm leadless SMT package.

## **Pin Configuration**

| 1 LE 2 DATA 3 CLK 4, 22 NC 6 RFIN 8 VCC AMP1 14 VCC AMP2 16 RFOUT 28 VCC SPI                                                    | Pin #          | Symbol   |

|---------------------------------------------------------------------------------------------------------------------------------|----------------|----------|

| 3 CLK 4, 22 NC 6 RFIN 8 VCC AMP1 14 VCC AMP2 16 RFOUT                                                                           | 1              | LE       |

| 4, 22         NC           6         RFIN           8         VCC AMP1           14         VCC AMP2           16         RFOUT | 2              | DATA     |

| 4, 22         NC           6         RFIN           8         VCC AMP1           14         VCC AMP2           16         RFOUT | 3              | CLK      |

| 8 VCC AMP1 14 VCC AMP2 16 RFOUT                                                                                                 | 4, 22          | NC       |

| 14 VCC AMP2<br>16 RFOUT                                                                                                         | 6              | RFIN     |

| 16 RFOUT                                                                                                                        | 8              | VCC_AMP1 |

|                                                                                                                                 | 14             | VCC_AMP2 |

| VCC SPI                                                                                                                         | 16             | RFOUT    |

| VCC_SIT                                                                                                                         | 28             | VCC_SPI  |

| All Other Pins GND                                                                                                              | All Other Pins | GND      |

## **Ordering Information**

| Part No.      | Description                                                    |

|---------------|----------------------------------------------------------------|

| TQM879006     | 1.8-2.7GHz Digital Variable Gain Amp                           |

| TQM879006-PCB | Fully Assembled Evaluation Board<br>Includes USB control board |

Standard T/R size = 1000 pieces on a 7" reel.

- 1 of 11 - Disclaimer: Subject to change without notice

Data Sheet: Rev J 12/14/10

### **Specifications**

### **Absolute Maximum Ratings**

| Parameter                                 | Rating        |

|-------------------------------------------|---------------|

| Storage Temperature                       | -55 to 150 °C |

| RF Input Power, CW, $50\Omega$ , T = 25°C | +23 dBm       |

| Vcc (pins 8, 14, 28)                      | +5.5 V        |

| Junction Temperature, T <sub>J</sub>      | +170 °C       |

Operation of this device outside the parameter ranges given above may cause permanent damage.

### **Recommended Operating Conditions**

| Parameter            | Min  | Тур | Max  | Units |

|----------------------|------|-----|------|-------|

| Vcc (pins 8, 14, 28) | 4.75 | 5   | 5.25 | V     |

| Case Temperature     | -40  |     | 85   | °C    |

Electrical specifications are measured at specified test conditions. Specifications are not guaranteed over all recommended operating conditions.

## **Electrical Specifications**

Test conditions unless otherwise noted: 25°C, +5Vcc, Maximum Gain State.

| Parameter                         | Conditions                                        | Min                        | Тур            | Max        | Units |

|-----------------------------------|---------------------------------------------------|----------------------------|----------------|------------|-------|

| Operational Freq Range            |                                                   | 1800                       |                | 2700       | MHz   |

| Test Frequency                    |                                                   |                            | 2000           |            | MHz   |

| Gain                              |                                                   | 27.5                       | 31             |            | dB    |

| Gain Control Range                | 0.5 dB Step Size                                  |                            | 31.5           |            | dB    |

| Accuracy Error                    | All States, 3 wire SPI, 6 states                  | $\pm (0.3+5\% \text{ of }$ | Attenuation se | tting) Max | dB    |

| Control Interface                 | 3-wire serial interface                           |                            | 6              |            | Bit   |

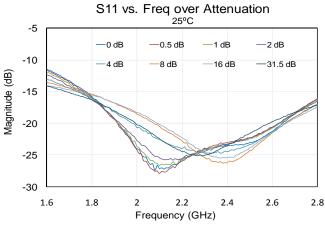

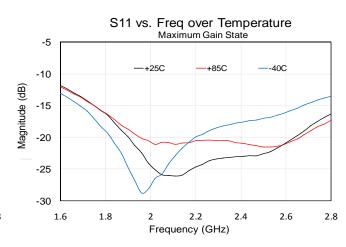

| Input Return Loss                 |                                                   |                            | 24             |            | dB    |

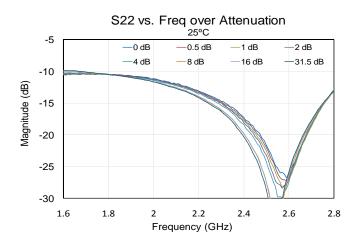

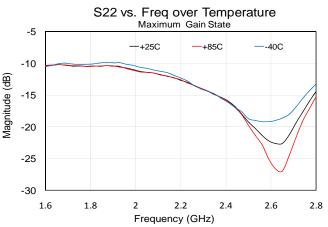

| Output Return Loss                |                                                   |                            | 11             |            | dB    |

| Output P1dB                       |                                                   |                            | +25.4          |            | dBm   |

| Output IP3                        | Pout = $+11$ dBm/tone, $\Delta f = 1$ MHz Spacing | +38                        | +41.3          |            | dBm   |

| Noise Figure                      |                                                   |                            | 1.5            |            | dB    |

| I/O Impedance                     |                                                   |                            | 50             |            | Ohm   |

| Supply Voltage                    |                                                   |                            | +5             |            | V     |

| Supply Current                    |                                                   |                            | 200            | 240        | mA    |

| Thermal Resistance, $\theta_{ic}$ | Module (junction to case)                         |                            |                | 45         | °C/W  |

Data Sheet: Rev J 12/14/10 © 2010 TriQuint Semiconductor, Inc.

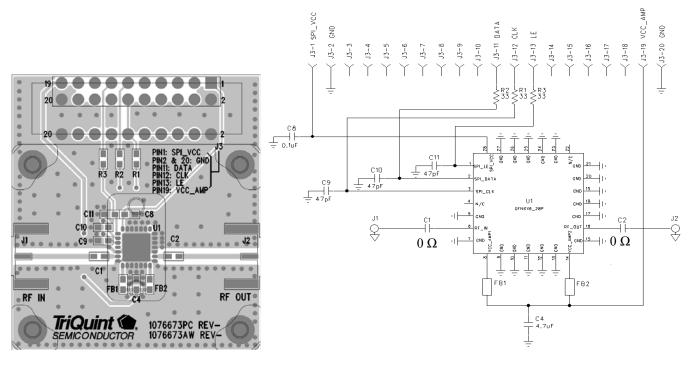

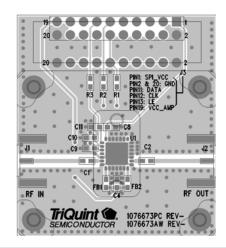

### **Application Circuit (TQM879006-PCB)**

#### Notes:

- 1. For PCB Board Layout, see page 6 for more information.

- 2. All Components are of 0603 size unless stated otherwise.

- 3. For SPI Timing Diagram, see page 5.

- 4. Input and Output DC blocks (C1, C2) may be replaced by 0 Ω jumpers since module is DC blocked internally.

- 5.  $0 \Omega$  jumpers may be replaced with copper traces in the target application layout.

- 6. R1, R2 and R3 are used as termination for digital noise or any noise reflection.

- 7. Different ground pins are used for SPI (digital) and analog supply voltages.

- 8. The primary RF microstrip characteristic line impedance is 50  $\Omega$ .

- 9. The single power supply is used to provide supply voltage to AMP1 and AMP2.

- 10. Ferrite Bead FB1 eliminates bypass line resonances between internal bypass capacitor and C4. Steward MI0603K300R-10.

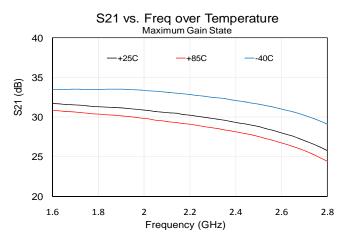

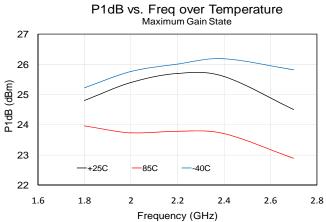

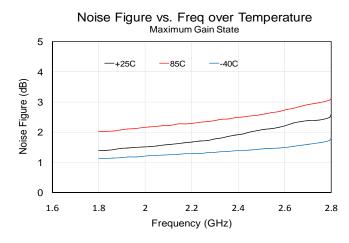

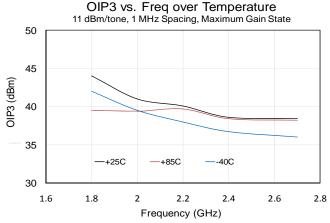

## **Typical Performance, Maximum Gain State**

| Frequency                                           | GHz | 1.8   | 2.0   | 2.14  | 2.35  | 2.6   |

|-----------------------------------------------------|-----|-------|-------|-------|-------|-------|

| Gain                                                | dB  | 31.4  | 31    | 30.6  | 30    | 28    |

| Input Return Loss                                   | dB  | 16    | 24.5  | 26    | 23.5  | 21    |

| Output Return Loss                                  | dB  | 10.5  | 11    | 12    | 15    | 22.4  |

| Output P1dB                                         | dBm | +24.8 | +25.4 | +25.5 | +25.7 | +24.8 |

| Output IP3 @ Pout = 11 dBm/tone, $\Delta f = 1$ MHz | dBm | +44   | +41.3 | +40   | +38.6 | +38.4 |

| Noise Figure                                        | dB  | 1.4   | 1.5   | 1.5   | 1.7   | 1.9   |

| Supply Voltage                                      | V   |       |       | +5    |       |       |

| Supply Current                                      | mA  |       |       | 200   |       |       |

#### Note:

1. The evaluation board can be used with TriQuint's USB interface board. Refer to TriQuint's website for more information.

Data Sheet: Rev J 12/14/10 - 3 of 11 - Disclaimer: Subject to change without notice

Connecting the Digital World to the Global Network®

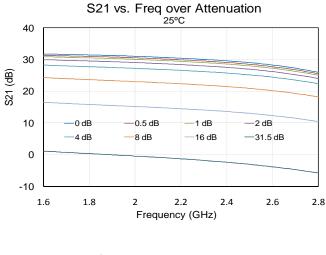

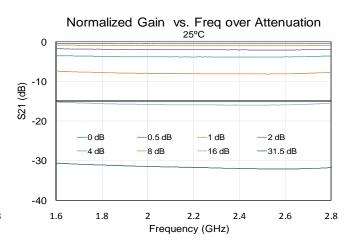

# **Typical Performance Plots**

# **Typical Performance Plots**

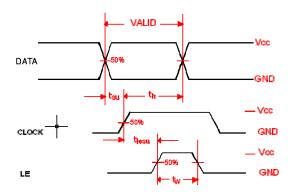

# **Serial Interface Timing Diagram**

| Symbol                | Parameter                                               | Conditions                  | Limits | Units |

|-----------------------|---------------------------------------------------------|-----------------------------|--------|-------|

| fmax                  | Maximum Operating frequency, Clock                      | $C_L$ =45pF                 | 30     | MHz   |

| $V_{IH, min}$         | Minimum HIGH Level Input Voltage                        |                             | 3.3    | V     |

| V <sub>IL, max</sub>  | Maximum LOW Level Input Voltage                         |                             | 0.8    | v     |

| $t_{su}$              | Minimum Set-up time from Data to Clock                  |                             | 20     |       |

| $t_{\rm h}$           | Minimum Hold time from Clock to Data                    |                             | 20     |       |

| $t_{lesu}$            | Minimum Set-up time from Clock to LE                    | $R_L=1k\Omega$ ,            | 5      |       |

| $t_{\rm w}$           | Minimum LE Pulse Width                                  | $R_L=1k\Omega$ , $C_L=45pF$ | 20     |       |

| $t_{R}$ , $t_{F}$     | Maximum Input Rise and Fall Time, Clock                 |                             | 15     | ns    |

| $t_{THL}$ , $t_{TLH}$ | Maximum Output Rise and Fall Time (Parallel Data        | =                           | 15     |       |

|                       | Outputs)                                                |                             | 13     |       |

|                       | Maximum Output Rise and Fall Time (Serial Data Outputs) |                             | 19     |       |

### 6-bit Attenuator Serial Programming Register Map

| 6-Bit A    | Attenuator | · Serial Pr | ogrammir | ig Registe | r Map     |

|------------|------------|-------------|----------|------------|-----------|

| B5         | B4         | В3          | B2       | B1         | В0        |

| A5         | A4         | A3          | A2       | A1         | A0        |

| <b>↑</b>   |            |             |          |            | <b>†</b>  |

| MSB        |            |             |          |            | LSB       |

| (first in) |            |             |          |            | (last in) |

### **Truth Table**

| Attenuation State | A5 | A4 | A3 | A2 | A1 | A0 |

|-------------------|----|----|----|----|----|----|

| Reference Loss    | Н  | Н  | Н  | Н  | Н  | Н  |

| 0.5 dB            | Н  | Н  | Н  | Н  | Н  | L  |

| 1 dB              | Н  | Н  | Н  | Н  | L  | Н  |

| 2 dB              | Н  | Н  | Н  | L  | Н  | Н  |

| 4 dB              | Н  | Н  | L  | Н  | Н  | Н  |

| 8 dB              | Н  | L  | Н  | Н  | Н  | Н  |

| 16 dB             | L  | Н  | Н  | Н  | Н  | Н  |

| 31.5 dB           | L  | L  | L  | L  | L  | L  |

Note: Not all 64 possible combinations of A0-A5 are shown in this table.

Data Sheet: Rev J 12/14/10 - 6 of 11 - Disclaimer: Subject to change without notice

### **Detailed Device Description**

The TQM879006 is a 50  $\Omega$  internally matched digital variable gain amplifier (DVGA) featuring high linearity over the entire gain control range. The amplifier module features the integration of a low noise amplifier gain block, a digital-step attenuator (DSA), along with a high linearity  $\frac{1}{4}$ W amplifier as shown in the functional diagram below. The module is unconditionally stable. Internal blocking capacitors and bias structures keep external parts count to a minimum. The DVGA has an operational frequency range from 1800-2700 MHz.

For any further technical questions, please email to **sicapplications.engineering@tqs.com**.

### **Functional Schematic Diagram**

Where M = Matching Network.

## **Chain Analysis Table**

The chain analysis of DVGA module is shown below in the table. This table provides the typical performance of individual stages in the module as well as overall module performance.

|            | Overall |      |      |             |

|------------|---------|------|------|-------------|

| Function   | AMP1    | DSA  | AMP2 | Performance |

| Gain (dB)  | 19      | -1.8 | 14   | 31          |

| NF (dB)    | 1.3     | 1.8  | 4.5  | 1.5         |

| OIP3 (dBm) | 37      | 55   | 41   | 41          |

| P1dB (dBm) | 19.5    | 26   | 25.4 | 25.4        |

| Icc (mA)   | 85      | 0    | 115  | 200         |

### **Detailed Device Description**

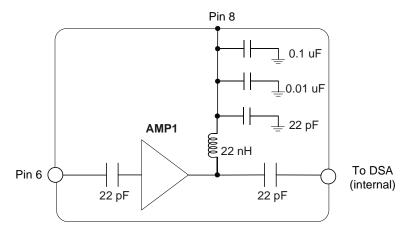

### AMP1

AMP1 is a wide band low noise amplifier gain block in DVGA module. The amplifier provides 19 dB gain, 1.3 dB noise figure, +37 dBm OIP3 at 1.9 GHz while only drawing 85 mA current. External DC blocks and biasing is not required. AMP1 is DC blocked internally and is connected internally to three bypass capacitors (22 pF, 0.01 uF, 0.1 uF) followed by 22 nH inductor inside the module as shown in the figure below.

### **DSA (Digital Step Attenuator)**

DVGA has a serial digital step attenuator that is controlled with 6-bit serial periphery interface (SPI<sup>TM</sup>) and has 0.5 dB step size with 31.5 dB attenuation range. This 50-ohm RF DSA maintains high attenuation accuracy over frequency and temperature. "000000" represents maximum attenuation state. External bypass capacitors are needed to compensate the inductance effect associated with long transmission lines on the evaluation board.

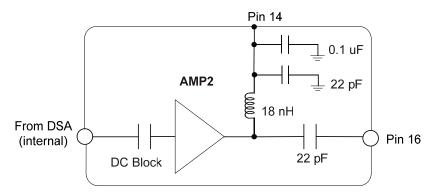

#### AMP2

AMP2 is high linearity ¼-W amplifier in DVGA module. The amplifier provides 14 dB gain, +25.4 dBm P1dB, +41 dBm OIP3 at 2.14 GHz while only drawing 115 mA current. The amplifier is tuned over 1800 -2700 MHz bandwidth using internal matching components. AMP2 is DC blocked internally and is connected internally to two bypass capacitors (22 pF, 0.1 uF) followed by an 18 nH inductor inside the module as shown in the figure below. External DC blocks and biasing is not required.

-8 of 11 -

Data Sheet: Rev J 12/14/10

© 2010 TriQuint Semiconductor, Inc.

Disclaimer: Subject to change without notice

Connecting the Digital World to the Global Network®

### **Pin Configuration and Description**

| Pin            | Symbol   | Description                                                                                                                                           |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | LE       | Serial Latch Enable Input. When LE is high, latch is clear and content of SPI control the attenuator. When LE is low, data in SPI is latched.         |

| 2              | DATA     | Serial data input. The data and clock pins allow the data to be entered serially into SPI and is independent of Latch state.                          |

| 3              | CLK      | Serial clock input.                                                                                                                                   |

| 4, 22          | N/C      | No connect or open. This pin is not connected in this module                                                                                          |

| 6              | RFIN     | Input, matched to 50 ohms between 1800 and 2700 MHz. Internally DC blocked.                                                                           |

| 8              | VCC_AMP1 | Supply Voltage to AMP1. This pin is connected internally to 3 bypass capacitors (22pF, 0.01uF, 0.1uF) followed by a 22 nH inductor inside the module. |

| 14             | VCC_AMP2 | Supply Voltage to AMP2. This pin is connected internally to 2 bypass capacitors (22pF, 0.1uF) followed by an 18 nH inductor inside the module.        |

| 16             | RFOUT    | Output, matched to 50 ohms between 1800 and 2700 MHz. Internally DC blocked.                                                                          |

| 28             | VCC_SPI  | Supply voltage for SPI and DSA chip. This pin is connected to 1000 pF bypass capacitor internally.                                                    |

| All other Pins | GND      | RF/DC Ground Connection                                                                                                                               |

### **Applications Information**

## **PC Board Layout**

Top RF layer is .014" NELCO N4000-13 material,  $\epsilon_r = 3.9$ , 4 total layers (0.062" thick) for mechanical rigidity. Metal layers are 1-oz copper. Microstrip line details: width = .030", spacing = .036".

The pad pattern shown has been developed and tested for optimized assembly at TriQuint Semiconductor. The PCB land pattern has been developed to accommodate lead and package tolerances. Since surface mount processes vary from supplier to supplier, careful process development is recommended.

For further technical information, Refer to www.TriQuint.com

Data Sheet: Rev J 12/14/10 © 2010 TriQuint Semiconductor, Inc.

- 9 of 11 - Disclaimer: Subject to change without notice

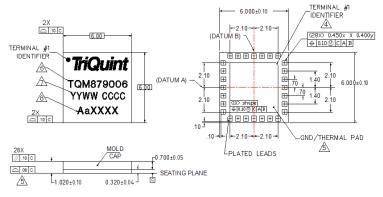

### **Mechanical Information**

### **Package Information and Dimensions**

This package is RoHS-compliant. The package bottom finish is electrolytic plated Au over Ni. It is compatible with both lead-free (maximum 260 °C reflow temperature) and lead (maximum 245 °C reflow temperature) soldering processes. Also recommend adding active fluxes of 2% during solder reflow.

The component will be laser marked with "TQM879006" product label with an alphanumeric lot code on the top surface of the package.

#### NOTES:

- EXCEPT WHERE NOTED, THIS PART OUTLINE CONFORMS TO JEDEC STANDARD MO-220, ISSUE E (VARIATION VJJC) FOR THERMALLY ENHANCED PLASTIC VERY THIN FINEPITCH QUAD FLAT NO LEAD PACKAGE (QFN).

- 2. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.4M-1994

- 3. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION CONFORM TO JESD 95-1 SPP-012.

- $\underline{\&}$  coplanarity applies to the exposed ground/thermal pad as well as the terminals.

- A PRODUCT CODE.

- ALPHA-NUMERIC LOT CODE.

- NENDOR CODE AND TRIQUINT LOT NUMBER

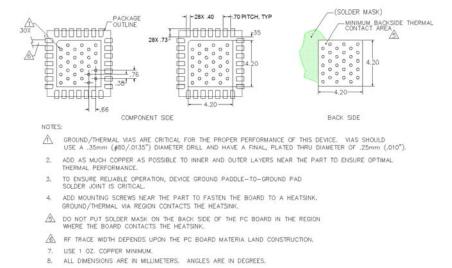

### **Mounting Configuration**

All dimensions are in millimeters (inches). Angles are in degrees.

#### Notes:

- 1. Ground / thermal vias are critical for the proper performance of this device. Vias should use a .35mm (#80 / .0135") diameter drill and have a final plated thru diameter of .25 mm (.010").

- 2. Add as much copper as possible to inner and outer layers near the part to ensure optimal thermal performance.

Data Sheet: Rev J 12/14/10 © 2010 TriQuint Semiconductor, Inc.

- 10 of 11 Disclaimer: Subject to change without notice

# TQM879006

### 1.8-2.7GHz Digital Variable Gain Amplifier

# **Product Compliance Information**

### **ESD Information**

### **Caution! ESD-Sensitive Device**

ESD Rating: Class 1B

Value: Passes ≥ 500 V min.

Test: Human Body Model (HBM)

Standard: JEDEC Standard JESD22-A114

ESD Rating: Class IV

Value: Passes  $\geq 1000 \text{ V min.}$

Test: Charged Device Model (CDM)

Standard: JEDEC Standard JESD22-C101

### **MSL Rating**

Level 3 at +260 °C convection reflow The part is rated Moisture Sensitivity Level 3 at 260°C per JEDEC standard IPC/JEDEC J-STD-020.

### **Solderability**

Compatible with the latest version of J-STD-020, Lead free solder, 260°

This part is compliant with EU 2002/95/EC RoHS directive (Restrictions on the Use of Certain Hazardous Substances in Electrical and Electronic Equipment).

Connecting the Digital World to the Global Network®

This product also has the following attributes:

- Halogen Free (Chlorine, Bromine)

- Antimony Free

- TBBP-A  $(C_{15}H_{12}Br_4O_2)$  Free

- PFOS FreeSVHC Free

### **Contact Information**

For the latest specifications, additional product information, worldwide sales and distribution locations, and information about TriQuint:

Web: <u>www.triquint.com</u> Tel: +1.503.615.9000 Email: <u>info-sales@tqs.com</u> Fax: +1.503.615.8902

For technical questions and application information:

Email: sicapplications.engineering@tqs.com

### **Important Notice**

The information contained herein is believed to be reliable. TriQuint makes no warranties regarding the information contained herein. TriQuint assumes no responsibility or liability whatsoever for any of the information contained herein. TriQuint assumes no responsibility or liability whatsoever for the use of the information contained herein. The information contained herein is provided "AS IS, WHERE IS" and with all faults, and the entire risk associated with such information is entirely with the user. All information contained herein is subject to change without notice. Customers should obtain and verify the latest relevant information before placing orders for TriQuint products. The information contained herein or any use of such information does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other intellectual property rights, whether with regard to such information itself or anything described by such information.

TriQuint products are not warranted or authorized for use as critical components in medical, life-saving, or life-sustaining applications, or other applications where a failure would reasonably be expected to cause severe personal injury or death.

Data Sheet: Rev J 12/14/10 -11 of 11 Disclaimer: Subject to change without notice