Sample &

Buy

SLIS155A-OCTOBER 2014-REVISED MARCH 2015

Support &

Community

**.**...

# **TPS99110-Q1 System-Basis Chip for Automotive Applications**

Technical

Documents

#### Features 1

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device HBM ESD Classification Level 2

- Device CDM ESD Classification Level C4B

- Operating Case Temperature: -40°C to 150°C

- Ambient Temperature: -40°C to 125°C

- Absolute Maximum Junction Temperature: -40°C to 175°C

- Absolute Maximum VBAT: -0.3 to 40 V

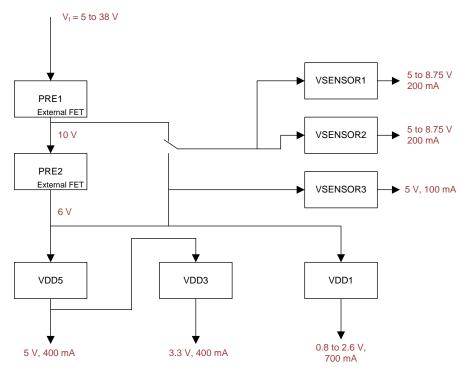

- Multi-Rail Power Supply

- Two Pre-regulating LDO Controllers: 6-V and 10-V Outputs

- Linear Regulator Controller With External FET: Adjustable Output From 0.8 to 2.6 V (VDD1)

- 5-V Output Linear Regulator With Internal FET: 400 mA Maximum (VDD5)

- 3.3-V Output Linear Regulator With Internal FET: 400 mA Maximum (VDD3), Generated From VDD5

- Voltage Monitoring on VDD1, VDD3, and VDD5

- 5-V Sensor Supply Output Tracking to VDD5, 100-mA Maximum, Protection Against Short to Battery and GND

- Two Adjustable Sensor Supplies, 200-mA Maximum With Protection Against Short to Battery and GND

- Switched Battery Output Provides VBAT Input With Low Drop

- Analog Features:

- Two Operational Amplifiers for Signal Conditioning

- Thee Independent Current Loop Interfaces With Current Sense Input and Digital Output

- Microcontroller Interface

- 3.3-V and 5-V Compatible 32-Bit, 2-Mbps SPI

- MCU Monitoring With SPI Q&A Watchdog

- Dual Polarity Enable-Drive Outputs for Disabling Safing-Path or External Power Stages on Any **Detected System Failure**

- One HS-CAN Transceiver With Bus Wakeup

- One KLINE/LIN Transceiver

# 2 Applications

- Transmission Control Unit

- **Engine Control Unit**

Tools &

Software

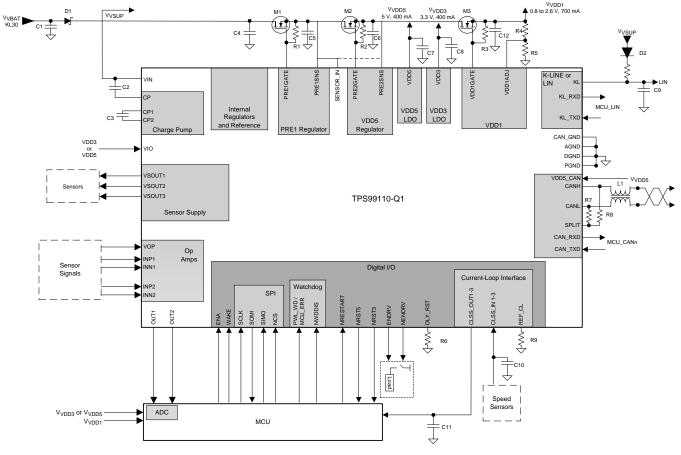

# 3 Description

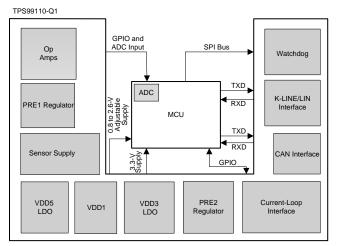

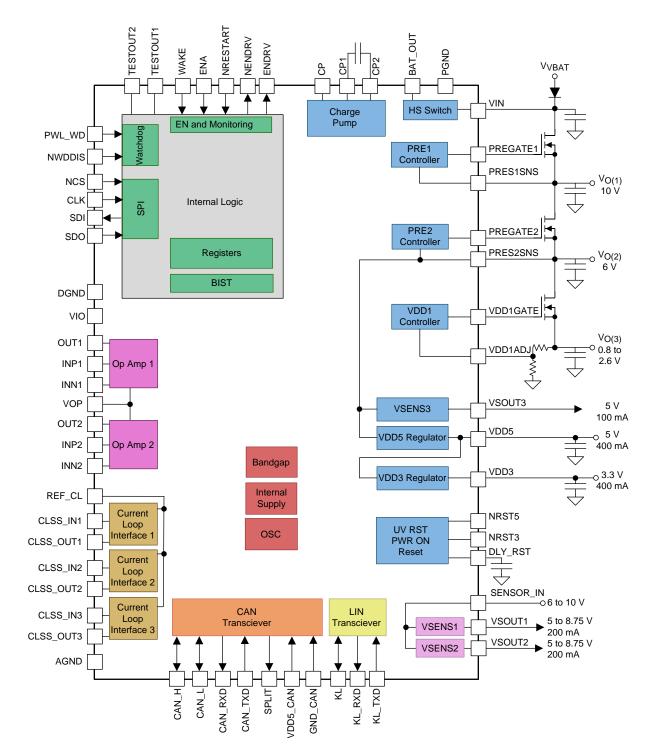

The TPS99110-Q1 device is a system-basis chip (SBC) offering a highly integrated solution for the typical requirements of transmission and engine electrical control units (ECU) in the automotive space. The integrated multi-rail power supply is designed to power microcontroller units (MCUs) and other circuits in ECUs. The device is designed to support rugged, high-temperature conditions and incorporates three low-dropout (LDO) regulators along with three sensor supplies. The integrated HS-CAN with bus wakeup KLINE/LIN transceivers help reduce and the component count on the board. The TPS99110-Q1 functional architecture features undervoltage and overvoltage monitoring, current limits, temperature warning flags, and overtemperature shutdown on all regulator outputs. Additional features include a window watchdog and SPI Q&A watchdog for MCUmonitorina.

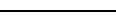

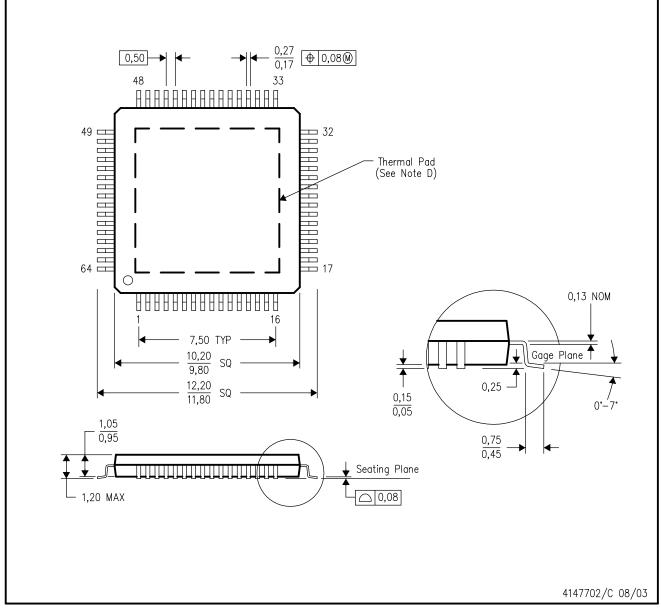

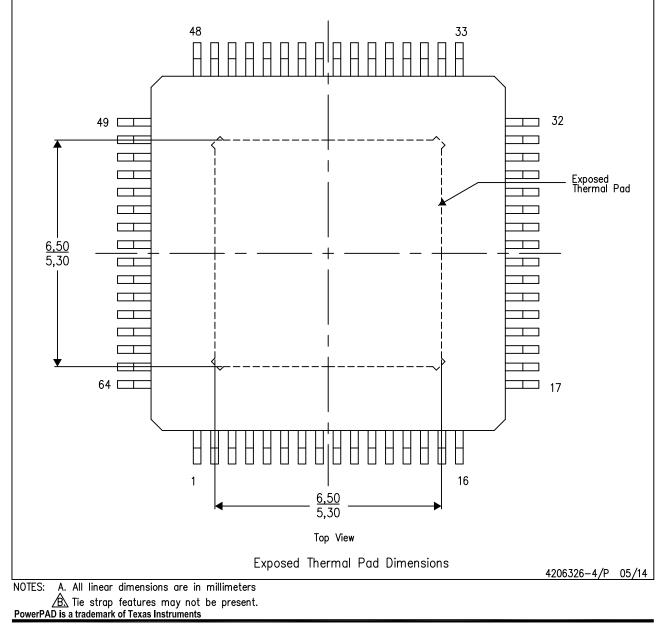

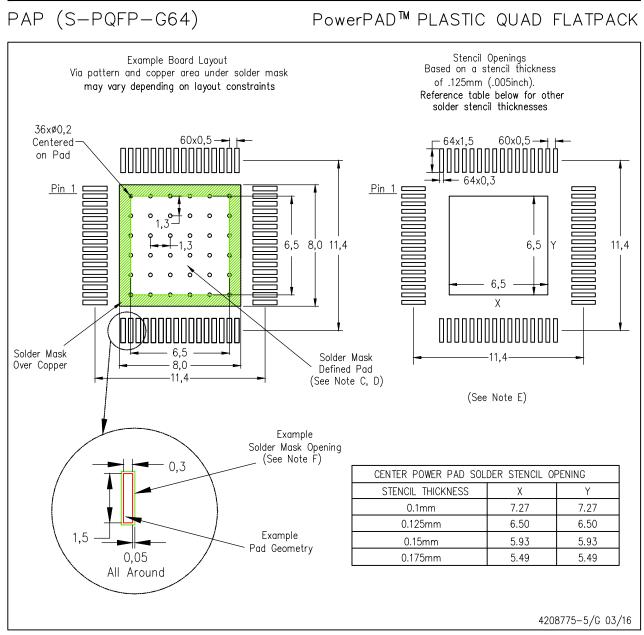

The device is available in a 64-pin HTQFP (PAP) PowerPAD<sup>™</sup> integrated circuit package.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)     |

|-------------|------------|---------------------|

| TPS99110-Q1 | HTQFP (64) | 10.00 mm × 10.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### Simplified Schematic of Typical Application

# **Table of Contents**

| 1 | Feat  | ures 1                                      |

|---|-------|---------------------------------------------|

| 2 | App   | lications1                                  |

| 3 | Desc  | cription1                                   |

| 4 | Revi  | sion History 2                              |

| 5 | Pin ( | Configuration and Functions 3               |

| 6 | Spec  | cifications                                 |

|   | 6.1   | Absolute Maximum Ratings 6                  |

|   | 6.2   | ESD Ratings 6                               |

|   | 6.3   | Recommended Operating Conditions7           |

|   | 6.4   | Thermal Information7                        |

|   | 6.5   | Range of Functionality 7                    |

|   | 6.6   | Enable Operation Electrical Characteristics |

|   | 6.7   | Preregulator Characteristics                |

|   | 6.8   | VDD5 Voltage Regulator Characteristics 9    |

|   | 6.9   | VDD3 Voltage Regulator Characteristics 10   |

|   | 6.10  | VDD1 Voltage Regulator Characteristics 10   |

|   | 6.11  | VSOUT1, VSOUT2, and VSOUT3 Sensor-Supply    |

|   |       | Output Characteristics 11                   |

|   | 6.12  | NRST5 Electrical Characteristics            |

|   | 6.13  | NRST3 Electrical Characteristics            |

|   | 6.14  | SPI Characteristics                         |

|   | 6.15  | NENDRV and ENDRV Output Characteristics 13  |

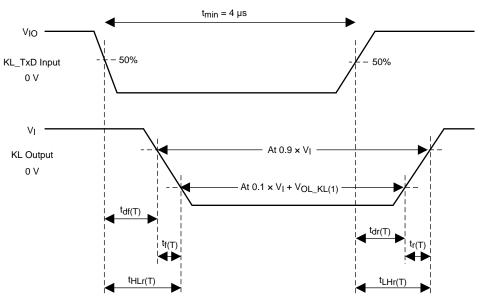

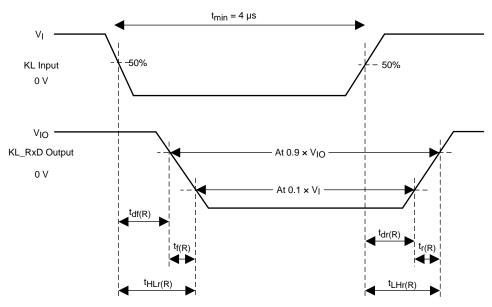

|   | 6.16  | K-Line and LIN Driver Characteristics       |

|   | 6.17  | CAN Transceiver Characteristics             |

|   | 6.18  | Current-Loop Interface Characteristics 16   |

|    | 6.19 | Operational Amplifier Characteristics | 16   |

|----|------|---------------------------------------|------|

|    | 6.20 | Switched Battery Characteristics      | 17   |

|    | 6.21 | Charge Pump Characteristics           | 17   |

|    | 6.22 |                                       |      |

| 7  | Deta | iled Description                      | . 19 |

|    | 7.1  | Overview                              | 19   |

|    | 7.2  | Functional Block Diagram              | 20   |

|    | 7.3  | Feature Description                   | 21   |

|    | 7.4  | Device Functional Modes               | 34   |

|    | 7.5  | Programming                           | 34   |

|    | 7.6  | Register Maps                         | 36   |

| 8  | App  | lication and Implementation           | . 56 |

|    | 8.1  | Application Information               | 56   |

|    | 8.2  | Typical Application                   | 56   |

| 9  |      | er Supply Recommendations             |      |

| 10 |      | out                                   |      |

|    | 10.1 |                                       |      |

|    | 10.2 | Layout Example                        | 61   |

| 11 | Dev  | ice and Documentation Support         | . 62 |

|    | 11.1 |                                       |      |

|    | 11.2 | Trademarks                            | 62   |

|    | 11.3 |                                       |      |

|    | 11.4 |                                       |      |

| 12 | Mec  | hanical, Packaging, and Orderable     |      |

|    |      | rmation                               | . 62 |

|    |      |                                       |      |

# 4 Revision History

Changes from Original (October 2014) to Revision A

| Released the full version of the data sheet | 1 |

|---------------------------------------------|---|

|---------------------------------------------|---|

Product Folder Links: TPS99110-Q1

Page

www.ti.com

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN     |     | TYPE | DESCRIPTION               |  |  |

|---------|-----|------|---------------------------|--|--|

| NAME    | NO. | TYPE | DESCRIPTION               |  |  |

| BAT_OUT | 18  | 0    | Switched battery output   |  |  |

| CAN_H   | 40  | I/O  | CAN high input and output |  |  |

| CAN_L   | 41  | I/O  | CAN low input and output  |  |  |

Copyright © 2014–2015, Texas Instruments Incorporated

TPS99110-Q1 SLIS155A – OCTOBER 2014–REVISED MARCH 2015

www.ti.com

NSTRUMENTS

**EXAS**

# Pin Functions (continued)

| PIN TYPE DESCRIPTION |     |      |                                                                                                  |

|----------------------|-----|------|--------------------------------------------------------------------------------------------------|

| NAME                 | NO. | TYPE | DESCRIPTION                                                                                      |

| CAN_RXD              | 46  | 0    | Asynchronous receive data line of the CAN interface                                              |

| CAN_TXD              | 44  | I    | Asynchronous transmission data line of the CAN interface                                         |

| CLK                  | 36  | I    | SPI clock                                                                                        |

| CLSS_IN1             | 62  | I    | Input of the current-loop speed-sensor interface 1                                               |

| CLSS_IN2             | 63  | I    | Input of the current-loop speed-sensor interface 2                                               |

| CLSS_IN3             | 64  | I    | Input of the current-loop speed-sensor interface 3                                               |

| CLSS_OUT1            | 2   | 0    | Output of the current-loop speed-sensor interface 1                                              |

| CLSS_OUT2            | 3   | 0    | Output of the current-loop speed-sensor interface 2                                              |

| CLSS_OUT3            | 4   | 0    | Output of the current-loop speed-sensor interface 3                                              |

| CP                   | 14  | 0    | Pin to the external charge-pump tank capacitor                                                   |

| CP1                  | 16  | 0    |                                                                                                  |

| CP2                  | 15  | 0    | Pin to the external charge-pump fly capacitor                                                    |

| DLY_RST              | 52  | I    | This pin adjusts the reset delay with an external resistor.                                      |

| ENA                  | 61  | I    | Ignition enable input                                                                            |

| ENDRV                | 26  | 0    | Enable output to switch on external drivers                                                      |

|                      | 5   |      |                                                                                                  |

|                      | 13  |      |                                                                                                  |

|                      | 27  | 1    |                                                                                                  |

| GND                  | 37  | GND  | Ground                                                                                           |

|                      | 50  | -    |                                                                                                  |

|                      | 60  | -    |                                                                                                  |

| GND_CAN              | 42  | GND  | GND supply input for the CAN driver                                                              |

| INN1                 | 7   | I    | Comparator 1 negative input                                                                      |

| INN2                 | 10  | I    | Comparator 2 negative input                                                                      |

| INP1                 | 8   | I    | Comparator 1 positive input                                                                      |

| INP2                 | 9   | I    | Comparator 2 positive input                                                                      |

| KL                   | 49  | I/O  | K-line/LIN driver input and output                                                               |

| KL_RXD               | 47  | 0    | Asynchronous receive-data line of K-line (LIN)                                                   |

| KL_TXD               | 48  | I    | Asynchronous transmission-data line of K-line (LIN)                                              |

| nCS                  | 33  | I    | SPI chip select                                                                                  |

| NENDRV               | 25  | 0    | Enable output to switch on the external drivers                                                  |

| NRESTART             | 45  | I    | Restart internal logic. A static-low disables the ENDRV and NENDRV pins.                         |

| NRST3                | 53  | 0    | Reset output for the VDD3 and VDD1 supplies                                                      |

| NRST5                | 51  | 0    | Reset output for the VDD5 supply                                                                 |

| NWDDIS               | 54  | 1    | Disable watchdog for debug purposes                                                              |

| OUT1                 | 6   | 0    | Comparator 1 digital output                                                                      |

| OUT2                 | 11  | 0    | Comparator 2 digital output                                                                      |

| PRE1GATE             | 21  | 0    | External linear power-device control for presupply 1                                             |

| PRE1SNS              | 20  | 1    | Voltage feedback input for presupply 1 regulation                                                |

| PRE2GATE             | 23  | 0    | External linear power device control for presupply 2                                             |

| PRE2SNS              | 22  | 1    | Voltage feedback input for presupply 2 regulation                                                |

| PWL_WD               | 30  | 1    | Logic-level enable and watchdog trigger                                                          |

| REF_CL               | 1   | 0    | Reference resistor for current loop interfaces                                                   |

| SDI                  | 34  |      | SPI data in                                                                                      |

| SDO                  | 35  | 0    | SPI data out                                                                                     |

|                      |     |      | Supply input for sensor and tracker control 1 and 2. Connect this pin externally with PRE1SNS or |

| SENSOR_IN            | 55  | Р    | PRE2SNS.                                                                                         |

4

# Pin Functions (continued)

| PIN      |     | TVDE | DESCRIPTION                                                                     |  |

|----------|-----|------|---------------------------------------------------------------------------------|--|

| NAME     | NO. | TYPE | DESCRIPTION                                                                     |  |

| SPLIT    | 39  | 0    | 2.5-V split output                                                              |  |

| TEST1    | 56  | 0    | For internal TI testing purposes. Connect this pin to ground in an application. |  |

| TEST2    | 19  | 0    | For internal TI testing purposes. Connect this pin to ground in an application. |  |

| VDD1ADJ  | 31  | I    | Voltage feedback input for VDD1 regulation                                      |  |

| VDD1GATE | 32  | 0    | External linear power device control for VDD1                                   |  |

| VDD3     | 29  | 0    | 3.3-V output                                                                    |  |

| VDD5     | 24  | 0    | 5-V output                                                                      |  |

| VDD5_CAN | 43  | Р    | 5-V supply input for CAN driver                                                 |  |

| VIN      | 17  | Р    | Power supply input and battery voltage                                          |  |

| VIO      | 28  | Р    | Supply input for digital outputs                                                |  |

| VOP      | 12  | Р    | Supply voltage for the operation amplifiers (op amps)                           |  |

| VSOUT1   | 57  | 0    | Sensor-supply output 1                                                          |  |

| VSOUT2   | 58  | 0    | Sensor-supply output 2                                                          |  |

| VSOUT3   | 59  | 0    | Sensor-supply output 3                                                          |  |

| WAKE     | 38  | I    | Wake input                                                                      |  |

TEXAS INSTRUMENTS

www.ti.com

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                    |                                                                                               | MIN  | MAX                    | UNIT |  |

|--------------------|-----------------------------------------------------------------------------------------------|------|------------------------|------|--|

|                    | PWL_WD, DLY_RST, NWDDIS, VIO, SDI, CLK, NCS, NRESTART, CAN_TXD, VDD5_CAN, KL_TXD, and VDD1ADJ | -0.3 | 7                      |      |  |

|                    | PRE2SNS                                                                                       | -0.3 | 12                     | V    |  |

| Input voltage      | VOP                                                                                           | -0.3 | 13.2                   |      |  |

|                    | VIN, SENSOR_IN, ENA, PRE1SNS, and WAKE                                                        | -0.3 | 40                     |      |  |

|                    | INPx/INNx                                                                                     | -0.3 | V <sub>VOP</sub> + 0.3 |      |  |

|                    | CLSS_INx                                                                                      | -2   | 40                     |      |  |

|                    | VDD5, VDD3, NRSTx, SDO, NENDRV, ENDRV, CAN_RXD, CLSS_OUTx, REF_CL, and KL_RXD                 | -0.3 | 7                      |      |  |

|                    | VDD1GATE                                                                                      | -0.3 | 8                      | 1    |  |

|                    | PRE2GATE                                                                                      | -0.3 | 19                     | V    |  |

| Output voltage     | VSOUTx, PRE1GATE, CP2, and BAT_OUT                                                            | -0.3 | 40                     |      |  |

|                    | CP and CP1                                                                                    | -0.3 | 50                     |      |  |

|                    | OUTx                                                                                          | -0.3 | V <sub>VOP</sub> + 0.3 |      |  |

|                    | CAN_H, CAN_L, and KL_TXD                                                                      | -27  | 40                     |      |  |

|                    | NRSTx, ENDRV/NENDRV, CLSS_OUTx, and OUTx                                                      | -20  | 20                     |      |  |

| Course ourset      | BAT_OUT                                                                                       | -50  | 20                     |      |  |

| Source current     | VDD5 and VDD3                                                                                 |      | 400                    | mA   |  |

|                    | VSOUTx                                                                                        |      | 700                    |      |  |

|                    | SENSOR_IN and VIN                                                                             | -10  |                        |      |  |

| Sink current       | ENA, PWL_WD, DLY_RST, NWDDIS, WAKE, INP/Nx, KL_TXD, and KL_RXD                                | -20  | 20                     | mA   |  |

|                    | VDD1ADJ                                                                                       |      | 20                     |      |  |

| Ground current, IG | ND                                                                                            |      | 100                    | mA   |  |

| Power-supply powe  | er dissipation, P <sub>D</sub>                                                                |      | 3.5                    | W    |  |

| Operating junction | temperature, TJ                                                                               | -40  | 175                    | °C   |  |

| Storage temperatu  | re, T <sub>sta</sub>                                                                          | -55  | 150                    | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |               |                                                         |                                                    | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------|----------------------------------------------------|-------|------|

|                    |               |                                                         | All pins except CANH, CANL, SPLIT, and global pins | ±2000 |      |

|                    | Electrostatic | Human body model (HBM), per AEC Q100–002 <sup>(1)</sup> | $CANH^{(2)}$ , CANL, and SPLIT pins^{(3)}          | ±8000 |      |

| V <sub>(ESD)</sub> | discharge     | scharge                                                 | Global pins <sup>(3)(4)</sup>                      | ±4000 | V    |

|                    |               |                                                         | All pins                                           | ±500  |      |

|                    |               | Charged device model (CDM), per AEC<br>Q100–011         | Corner pins (1, 16, 17, 32, 33, 48, 49, and 64)    | ±750  |      |

(1) AEC Q100–002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS–001 specification.

(2) The CANH pin has 2kV HBM capability, verified to pass up to 8kV with IEC HV ESD testing conditions.

(3) CANH, CANL, SPLIT, and all Global pins rating is met with respect to GND.

(4) Global pins are VIN, ENA, WAKE, VSOUTx, PRE1SNS, KL, CLSS\_INx

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                       |                                                                                      | MIN | NOM MAX | UNIT |

|------------------|-----------------------|--------------------------------------------------------------------------------------|-----|---------|------|

| V <sub>VIN</sub> | Input supply voltage  | Full functionality, wakeup from standby mode requires 5.5-V V <sub>VIN</sub> minimum | 5.2 | 38.5    | V    |

| V <sub>VIO</sub> | VIO pin Input voltage |                                                                                      | 3   | 5.5     | V    |

#### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | PAP (HTQFP)<br>64 PINS | UNIT |

|-----------------------|----------------------------------------------|------------------------|------|

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 24.2                   |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 9.1                    |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 7.5                    | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.2                    | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 7.4                    |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.3                    |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### 6.5 Range of Functionality

Functionality remains the same for all functional blocks including the block affected by a short- circuit or test pulse event. These affected blocks can be: K/LIN and CAN transceivers, current-loop interface, operational amplifier, sensor supplies.  $T_C = -40^{\circ}$ C to  $150^{\circ}$ C,  $T_J = -40^{\circ}$ C to  $175^{\circ}$ C unless otherwise noted.

|                          | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                                                                                               | MIN             | TYP N | MAX  | UNIT |

|--------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|------|------|

|                          |                                                                                             | All functions are operational in this voltage range. Wakeup from standby mode requires VIN minimum of 5.5 V $$                                                                                | 5.2             | 3     | 88.5 |      |

| V <sub>VIN</sub>         | Input voltage, VIN                                                                          | NRST5 might output a low level, but NRST3 outputs a<br>high level, VDD5 must be above 3.3 V, ENDRV or<br>NENDRV must be inactive<br>Wakeup from standby mode requires VIN minimum of<br>5.5 V | 4               |       | 5.2  | V    |

|                          | Quiescent current in standby modes, ENA,                                                    | $V_{IN}$ = 16 V and T <sub>J</sub> < 70°C                                                                                                                                                     |                 |       | 50   | μA   |

| I <sub>Q(STBY)</sub>     | $PWL_WD = Low^{(1)}$                                                                        | $V_{\rm IN}$ = 28 V and $T_{\rm J}$ < 175°C                                                                                                                                                   |                 |       | 400  | μA   |

| I <sub>IN_IDLE</sub>     | Input current in enabled mode                                                               | No external current consumption                                                                                                                                                               |                 |       | 15   | mA   |

| V <sub>VIO</sub>         | VIO voltage range                                                                           |                                                                                                                                                                                               | 3               |       | 5.5  | V    |

| V <sub>DIGIN_HIGH</sub>  | Digital input high threshold,KL_TXD,<br>CAN_TXD, SDI, CLK, NCS, PWL_WD,<br>NRESTART, NWDDIS |                                                                                                                                                                                               | 2               |       |      | V    |

| V <sub>DIGIN_LOW</sub>   | Digital input low threshold, KL_TXD,<br>CAN_TXD, SDI, CLK, NCS, PWL_WD,<br>NRESTART, NWDDIS |                                                                                                                                                                                               |                 |       | 0.8  | V    |

| V <sub>DIGIN_HYST</sub>  | Digital input Hysteresis, KL_TXD,<br>CAN_TXD, SDI, CLK, NCS, PWL_WD,<br>NRESTART, NWDDIS    |                                                                                                                                                                                               | 0.1             |       |      | V    |

| I <sub>DIG_LEAK</sub>    | Digital input leakage current, CAN_TXD,<br>SDI, CLK, NCS, PWL_WD, NRESTART,<br>NWDDIS       | $0 \text{ V} < \text{V}_{\text{LEAK}} \leq 5.5 \text{ V}$                                                                                                                                     | -60             |       | 60   | μA   |

| I <sub>KL_TXD_LEAK</sub> | KL_TXD leakage current                                                                      | 0 V < V <sub>LEAK</sub> ≤ 5.5 V                                                                                                                                                               | -300            |       | 300  | μΑ   |

| V <sub>DIGOUT_HIGH</sub> | Digital output high level, KL_RXD,<br>CAN_RXD, SDO, CLSS_OUTx                               | I <sub>OUT</sub> = -2 mA                                                                                                                                                                      | $V_{VIO} - 0.2$ |       |      | V    |

| V <sub>DIGOUT_LOW</sub>  | Digital output low level, KL_RXD,<br>CAN_RXD, SDO, CLSS_OUTx                                | I <sub>OUT</sub> = 2 mA                                                                                                                                                                       |                 |       | 0.2  | V    |

| V <sub>SENSOR_IN</sub>   | Forced voltage at SENSOR_IN pin                                                             |                                                                                                                                                                                               |                 |       | 40   | V    |

|                          | Leakage current, WAKE pin                                                                   | $V_{VIN}$ = 16 V and T <sub>J</sub> < 70°C                                                                                                                                                    |                 |       | 1.5  |      |

| I <sub>WAKE_LEAK</sub>   | Leanage cullent, WARE pill                                                                  | $V_{VIN}$ = 28 V and T <sub>J</sub> < 175°C                                                                                                                                                   |                 |       | 15   | μA   |

| I <sub>REV_ENA</sub>     | Digital output high level, KL_RXD,<br>CAN_RXD, SDO, CLSS_OUTx                               | Functionality remains the same for all functional blocks:                                                                                                                                     | -5              |       | 5    | mA   |

(1) Sum of current into VIN and WAKE.

TEXAS INSTRUMENTS

www.ti.com

# 6.6 Enable Operation Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                   | TEST CONDITIONS                                                    | MIN | ТҮР | MAX | UNIT |

|-------------------------|-----------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>ENA_HIGH</sub>   | Enable input threshold high | ENA is connected to ignition line through a minimum of 1 $k\Omega$ |     |     | 3.8 | V    |

| V <sub>ENA_LOW</sub>    | Enable input threshold low  | ENA is connected to ignition line through a minimum of 1 $k\Omega$ | 2   |     |     | V    |

| V <sub>ENA_HYST</sub>   | Enable input hysteresis     | If no connection to ENA pin, the default state must be OFF         | 440 |     |     | mV   |

| R <sub>ENA</sub>        | ENA resistor to ground      | V <sub>ENA</sub> = 2 V                                             | 0.4 |     | 2   | MΩ   |

| V <sub>VIN_TH_L</sub>   | VIN undervoltage switch-off |                                                                    | 3.7 |     | 3.9 | V    |

| V <sub>VIN_TH_H</sub>   | VIN undervoltage switch-on  |                                                                    | 5   |     | 5.4 | V    |

| V <sub>VIN_TH_HYS</sub> | VIN undervoltage hysteresis |                                                                    | 1   |     | 1.5 | V    |

| V <sub>WAKE_HIGH</sub>  | WAKE input threshold high   | WAKE pin is connected to VIN through a minimum of 1 $k\Omega$      |     |     | 3.8 | V    |

| V <sub>WAKE_LOW</sub>   | WAKE input threshold low    | WAKE pin is connected to VIN through a minimum of 1 $k\Omega$      | 2   |     |     | V    |

| V <sub>WAKE_HYST</sub>  | WAKE input hysteresis       | If no connection to WAKE pin, the default state must be OFF.       | 0.1 |     |     | V    |

| IWAKE                   | WAKE sink current to GND    | V <sub>WAKE</sub> > 2 V                                            |     |     | 1   | μA   |

### 6.7 Preregulator Characteristics

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                               | TEST CONDITIONS                                                              | MIN | ТҮР | MAX  | UNIT |

|---------------------------|-----------------------------------------|------------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>GS(th)</sub>       | Gate threshold voltage                  | $I_D = 1 \text{ mA and } T_J = -40^{\circ}\text{C to } 175^{\circ}\text{C}$  | 0.3 |     | 3    | V    |

| C <sub>ISS</sub>          | Maximum input capacitance               | V <sub>GS</sub> = 0 V                                                        |     |     | 5000 | pF   |

| Q <sub>GATE</sub>         | Maximum gate charge                     | $V_{GS} = 0 V$ to 10 V                                                       |     |     | 190  | nC   |

| 9 <sub>FS</sub>           | Minimum forward transconductance        | $I_D = 50 \text{ mA}$                                                        | 0.4 |     |      | S    |

| C <sub>PRExSNS</sub>      | Value of the output ceramic capacitor   | $0 \text{ m}\Omega \leq \text{ESR} \leq 250 \text{ m}\Omega$ , see Figure 37 | 0.5 | 1   | 15   | μF   |

| V <sub>PRE1SNS</sub>      | Regulated voltage to PRE1SNS pin        | $10 \text{ V} \leq \text{V}_{IN} \leq 38.5 \text{ V}$                        | 9   | 10  | 11   | V    |

| V <sub>PRE1GATE</sub>     | External device voltage at PRE1GATE pin | $I_{Load} = -20 \ \mu A$ at the PRE1GATE pin                                 | 14  |     |      | V    |

| V <sub>PRE1_GS</sub>      | External PRE1 FET Gate to Source        | $4 \text{ V} \leq \text{V}_{\text{VIN}} \leq 6 \text{ V}$                    | 2.5 |     | 4.5  | V    |

|                           | voltage                                 | V <sub>VIN</sub> > 6 V                                                       | 4.5 |     |      |      |

| V <sub>PRE1GATE_OFF</sub> | External device voltage at PRE1GATE pin | Off condition, $I_{Load} = 20 \ \mu A$ at PRE1GATE pin                       |     |     | 1    | V    |

| M                         |                                         | V <sub>PRE1GATE</sub> – V <sub>PRE1SNS</sub> , internal Zener diode          | 10  |     | 15   | V    |

| V <sub>CLAMP1</sub>       | External FET V <sub>GS</sub> clamp      | V <sub>PRE1SNS</sub> – V <sub>PRE1GATE</sub> , internal Zener diode          | 10  |     | 15   | v    |

| V <sub>PRE2SNS</sub>      | Regulated voltage to PRE2SNS pin        |                                                                              | 5.5 | 6   | 6.5  | V    |

| V <sub>PRE2GATE</sub>     | External device voltage at PRE2GATE pin | Load = -20 µA at PRE2GATE pin                                                | 11  |     |      | V    |

|                           | External PRE2 FET Gate to Source        | $4 \vee \leq V_{\rm IN} \leq 4.5 \vee$                                       | 2.5 |     | 3    | N/   |

| V <sub>PRE2_GS</sub>      | voltage                                 | 4.5 V < V <sub>IN</sub>                                                      | 3.5 |     |      | V    |

| V <sub>PRE2GATE_OFF</sub> | External device voltage at PRE2GATE pin | Off condition, load = 20 µA at PRE2GATE pin                                  |     |     | 0.3  | V    |

|                           |                                         | V <sub>PRE2GATE</sub> – V <sub>PRE2SNS</sub> , internal Zener diode          | 10  |     | 15   | V    |

| V <sub>CLAMP2</sub>       | External device V <sub>GS</sub> clamp   | V <sub>PRE2SNS</sub> – V <sub>PRE2GATE</sub> , internal Zener diode          | 10  |     | 15   |      |

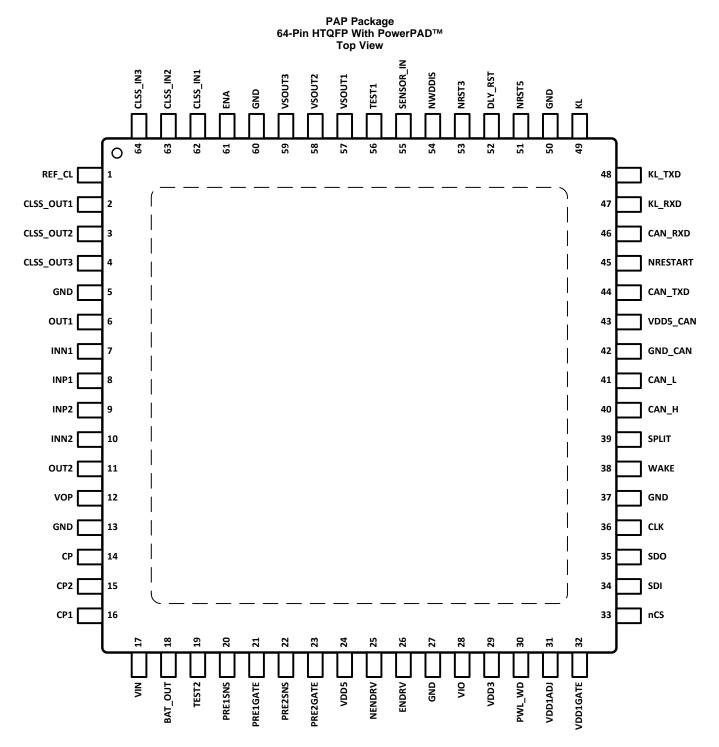

# 6.8 VDD5 Voltage Regulator Characteristics

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                           | TEST CONDITIC                                                                                                                                                                                                      | NS                     | MIN   | TYP | MAX   | UNIT  |

|----------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|-----|-------|-------|

| C <sub>VDD5</sub>    | Value of output ceramic capacitor                                                   | 0 mΩ ≤ ESR ≤ 250 mΩ                                                                                                                                                                                                |                        | 5     | 10  | 40    | μF    |

| P <sub>VDD5</sub>    | Maximum power dissipation                                                           |                                                                                                                                                                                                                    |                        |       |     | 2     | W     |

| I <sub>VDD5</sub>    | VDD5 output current                                                                 |                                                                                                                                                                                                                    |                        | 0     |     | 400   | mA    |

| V <sub>VDD5</sub>    | VDD5 output voltage                                                                 | $0 \le I_{VDD5} \le 400 \text{ mA}^{(1)}$                                                                                                                                                                          |                        | 4.9   | 5   | 5.1   | V     |

| $V_{VDD5\_dyn}$      | VDD5 output voltage dynamic<br>Go-no-go test for RESET<br>behavior                  | Square wave on VDD5<br>f = 50 kHz to 50 Hz<br>Duty cycle = 50%<br><sub>VDD5</sub> = 10% to 90% I <sub>max</sub>                                                                                                    |                        | 4.8   | 5   | 5.151 | V     |

| $V_{VDD5\_max}$      | Maximum VDD5 output voltage<br>during VIN step from 5.1 V to<br>13.5 V within 10 μs | $C_{VDD5} = 6 \ \mu F$<br>$I_{VDD5} < 400 \ mA$                                                                                                                                                                    |                        |       |     | 5.5   | V     |

|                      |                                                                                     |                                                                                                                                                                                                                    | $T_J = -40^{\circ}C$   |       |     | 0.25  |       |

| V <sub>Vdr5</sub>    | VDD5 output dropout voltage<br>Vdr5 = (VPRE2 – VDD5)                                | $0 \text{ mA} \le I_{\text{VDD5}} \le 400 \text{ mA}$                                                                                                                                                              | $T_J = 25^{\circ}C$    |       |     | 0.29  | V     |

|                      |                                                                                     |                                                                                                                                                                                                                    | T <sub>J</sub> = 175°C |       |     | 0.32  |       |

| PSRR <sub>VDD5</sub> | Power supply rejection ratio VIN                                                    | 50 Hz $\leq f \leq$ 20 kHz<br>U = 4 V <sub>PP</sub><br>V <sub>IN</sub> > 9 V mean value<br>0 $\leq$ I <sub>VDD5</sub> $\leq$ 400mA                                                                                 |                        | 40    |     |       | dB    |

| LiR <sub>VDD5</sub>  | Line regulation (I <sub>VDD5</sub> is constant during test)                         | $0 \le I_{VDD5} \le 400 \text{ mA}, 8 \text{ V} \le \text{V}_{IN}$                                                                                                                                                 | ≤ 19 V                 | -25   | 0   | 25    | mV    |

| LoR <sub>VDD5</sub>  | Load regulation (VPRE2 is<br>constant during test)                                  | $0 \le I_{VDD5} \le 400 \text{ mA}, 8 \text{ V} \le \text{V}_{IN}$                                                                                                                                                 | ≤ 19 V                 | -25   | 0   | 25    | mV    |

| Tmp <sub>VDD5</sub>  | Temperature drift                                                                   | Compared to 25°C value                                                                                                                                                                                             |                        | -100  | 0   | 100   | ppm/K |

| D <sub>VDD5</sub>    | Long-term drift                                                                     |                                                                                                                                                                                                                    |                        | -0.8% | 0   | 0.8%  |       |

| C <sub>VDD5</sub>    | Regulator output with ripple on<br>VIN input                                        | Square wave on VIN, 8 V to 1<br>kHz; dV/dt = 5 V/µs                                                                                                                                                                | 6 V; F0 = 10           | 4.8   |     | 5.2   | V     |

| dVDD5/dt             | dV/dt at VDD5                                                                       | For MCU supply $C_{VDD5} = 10 \mu$<br>Slope from 0.5 V to 1 V and s<br>90% of VDD5 <sup>(2)</sup><br>$C_{VDD5} = 10 \mu$ F<br>0 ≤ $I_{VDD5} \le 400 \text{ mA}$<br>PRE1 and PRE2 used<br>SENSORIN connected to PRE | ope from 1 V to        | 5     |     | 50    | V/ms  |

(1) Including line regulation, loads regulation, temperature drift and long-term drift.

(2) if current limitation is reached, the slope will be controlled by the current limitation and output capacitor

SLIS155A-OCTOBER 2014-REVISED MARCH 2015

TEXAS INSTRUMENTS

www.ti.com

# 6.9 VDD3 Voltage Regulator Characteristics

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                           | TEST CONDITION                                                                                                                                                                                                       | S                    | MIN   | TYP | MAX   | UNIT  |  |

|----------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-----|-------|-------|--|

| C <sub>VDD3</sub>    | Value of output ceramic<br>capacitor                                                | 0 mΩ ≤ ESR ≤ 250 mΩ                                                                                                                                                                                                  |                      | 5     | 10  | 40    | μF    |  |

| P <sub>VDD3</sub>    | Maximum power dissipation                                                           |                                                                                                                                                                                                                      |                      |       |     | 1.75  | W     |  |

| I <sub>VDD3</sub>    | VDD3 output current                                                                 |                                                                                                                                                                                                                      |                      | 0     |     | 400   | mA    |  |

| V <sub>VDD3</sub>    | VDD3 output voltage                                                                 | $0 \le I_{VDD3} \le 400 \text{ mA}^{(1)}$                                                                                                                                                                            |                      | 3.234 | 3.3 | 3.366 | V     |  |

| $V_{VDD3\_dyn}$      | VDD3 output voltage dynamic                                                         | Square wave on VDD3<br>f = 50  kHz to 50 Hz<br>Duty cycle = 50%<br>I <sub>VDD3</sub> = 10% to 90% I <sub>max</sub>                                                                                                   |                      | 3.17  | 3.3 | 3.43  | V     |  |

| $V_{VDD5\_max}$      | Maximum VDD3 output voltage<br>during VIN step from 5.1 V to<br>13.5 V within 10 µs | $C_{VDD3} = 6 \ \mu F$<br>$I_{VDD3} < 400 \ mA$<br>PRE1 and PRE2 used                                                                                                                                                |                      |       |     | 3.6   | V     |  |

|                      |                                                                                     |                                                                                                                                                                                                                      | $T_J = -40^{\circ}C$ |       |     | 0.25  |       |  |

| V <sub>Vdr3</sub>    | VDD5 output dropout voltage<br>Vdr5 = (VDD5 – VDD3)                                 | 0 mA ≤ I <sub>VDD3</sub> ≤ 400 mA                                                                                                                                                                                    | $T_J = 25^{\circ}C$  |       |     | 0.29  | V     |  |

|                      |                                                                                     |                                                                                                                                                                                                                      | $T_J = 175^{\circ}C$ |       |     | 0.32  |       |  |

| PSRR <sub>VDD3</sub> | Power supply rejection ratio VIN                                                    | 50 Hz $\leq f \leq$ 20 kHz<br>U = 4 V <sub>PP</sub><br>V <sub>IN</sub> > 9 V mean value<br>C <sub>VDD3</sub> = 10 µF<br>0 $\leq$ I <sub>VDD3</sub> $\leq$ 400 mA<br>PRE1 and PRE2 used<br>SENSORIN connected to PRE1 |                      | 40    |     |       | dB    |  |

| LiR <sub>VDD3</sub>  | Line regulation (I <sub>VDD3</sub> is constant during test)                         | $0 \le I_{VDD3} \le 400 \text{ mA}, 8 \text{ V} \le \text{V}_{IN} \le$                                                                                                                                               | 19 V                 | -25   | 0   | 25    | mV    |  |

| LoR <sub>VDD3</sub>  | Load regulation (VPRE2 is<br>constant during test)                                  | $0 \le I_{VDD3} \le 400 \text{ mA}, 8 \text{ V} \le \text{V}_{IN} \le$                                                                                                                                               | 19 V                 | -25   | 0   | 25    | mV    |  |

| Tmp <sub>VDD3</sub>  | Temperature drift                                                                   | Compared to 25°C value                                                                                                                                                                                               |                      | -100  | 0   | 100   | ppm/K |  |

| D <sub>VDD3</sub>    | Long-term drift                                                                     |                                                                                                                                                                                                                      |                      | -0.8% | 0   | 0.8%  |       |  |

| C <sub>VDD3</sub>    | Regulator output with ripple on VIN input                                           | Square wave on VIN, 8 V to 16<br>kHz; dV/dt = 5 V/µs                                                                                                                                                                 | V; F0 = 10           | 3.2   |     | 3.4   | V     |  |

| dVDD3/dt             | dV/dt at VDD3                                                                       | For MCU supply:<br>$C_{VDD3} = 10 \ \mu F$<br>$I_{VDD3} = 0 \ mA$<br>Slope from 0.5 V to 1 V and slop<br>90% of VDD3 <sup>(2)</sup>                                                                                  | be from 1 V to       | 5     |     | 50    | V/ms  |  |

(1) Including line regulation, load regulation, temperature drift, and long-term drift.

(2) if current limitation is reached, the slope will be controlled by the current limitation and output capacitor

# 6.10 VDD1 Voltage Regulator Characteristics

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                             | TEST CONDITIONS                                                              | MIN   | ТҮР | MAX   | UNIT |

|---------------------------|---------------------------------------|------------------------------------------------------------------------------|-------|-----|-------|------|

| V <sub>GS(th)</sub>       | Gate threshold voltage                | I <sub>D</sub> = 1 mA                                                        | 0.3   |     | 3     | V    |

| CISS                      | Maximum input capacitance             | V <sub>GS</sub> = 0 V                                                        |       |     | 3200  | pF   |

| Q <sub>GATE</sub>         | Maximum gate charge                   | $V_{GS} = 0 V$ to 10 V                                                       |       |     | 70    | nC   |

| <b>g</b> <sub>FS</sub>    | Minimum forward transconductance      | I <sub>D</sub> = 50 mA                                                       | 0.4   |     |       | S    |

| C <sub>VDD1</sub>         | Value of the output ceramic capacitor | $0 \text{ m}\Omega \leq \text{ESR} \leq 250 \text{ m}\Omega$ , see Figure 37 | 5     | 10  | 40    | μF   |

| V <sub>VDD1</sub>         | VDD1 programmable output              | Dependent on external resistive divider                                      | 0.8   |     | 2.6   | V    |

| I <sub>VDD1</sub>         | VDD1 output current                   |                                                                              | 10    |     | 700   | mA   |

| V <sub>ref(VDD1ADJ)</sub> | VDD1ADJ reference voltage             | $10 \text{ mA} \le I_{\text{VDD1}} \le 700 \text{ mA}^{(1)}$                 | 0.784 | 0.8 | 0.816 | V    |

(1) Including line regulation, loads regulation, temperature drift and long-term drift.

### VDD1 Voltage Regulator Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                                                                             | TEST CONDITIONS                                                                                                                                                                                                            | MIN   | TYP | MAX                            | UNIT  |

|---------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--------------------------------|-------|

| V <sub>dref</sub> (VDD1ADJ<br>) | VDD1ADJ reference voltage dynamic, go-no-go test for RESET behavior                   | 10 mA $\leq I_{VDD1} \leq$ 700 mA<br>Square wave on VDD1<br>$I_{VDD1} = 10\%$ to 90% $I_{max}$<br>f = 50 kHz to 50 Hz<br>Duty cycle = 50%<br>$C_{VDD1} > 30 \ \mu F$<br>ESR < 50 m $\Omega$<br>No reset allowed            | 0.753 | 0.8 | 0.835                          | V     |

|                                 |                                                                                       |                                                                                                                                                                                                                            | 7     |     | 15                             |       |

| $V_{VDD1\_GATE}$                | VDD1_GATE output voltage                                                              | $4 V \le V_{IN} \le 4.5 V$<br>T <sub>J</sub> > 70°C                                                                                                                                                                        | 6.55  |     | 15                             | V     |

| V <sub>VDD1ADJmax</sub>         | Maximum VDD1ADJ voltage at switch-on                                                  | $C_{VDD1} > 6 \ \mu F$<br>$I_{VDD1} < 700 \ mA$<br>Internal soft-start function                                                                                                                                            |       |     | V <sub>VDD1ADJ</sub> ×<br>1.03 | V     |

| C <sub>VDD1ADJ</sub>            | Regulator output with ripple on VIN input                                             | Square wave on VIN 8 V to 16 V<br>F0 = 10 kHz<br>dV/dt = 5 V/µs                                                                                                                                                            | 0.773 | 0.8 | 0.827                          | V     |

| V <sub>O(VDD1ADJm</sub><br>ax)  | Maximum VDD1ADJ output voltage during VIN step from 5.1 V to 13.5 V within 10 $\mu s$ | $C_{VDD1} = 6 \ \mu F$<br>$I_{VDD1} < 700 \ mA$                                                                                                                                                                            |       |     | 0.88                           | V     |

| dVDD1ADJ/<br>dt                 | Rate at which VDD1 powers up                                                          | $C_{VDD1} = 10 \ \mu F$<br>$I_{VDD1} = 10 \ mA$                                                                                                                                                                            | 0.8   |     | 8                              | V/ms  |

| LiR <sub>VDD1ADJ</sub>          | Line regulation (IVDD1 is constant during test)                                       | $0 \le I_{VDD1} \le 700 \text{ mA}$<br>8.0 V $\le$ VIN $\le$ 19 V                                                                                                                                                          | -7    | 0   | 7                              | mV    |

| LoR <sub>VDD1ADJ</sub>          | Load regulation (VIN is constant during test)                                         | 0 ≤ I <sub>VDD1</sub> ≤ 700 mA<br>8 V ≤ VIN ≤ 19 V                                                                                                                                                                         | -7    | 0   | 7                              | mV    |

| PSRR <sub>VDD1</sub>            | Power supply rejection ratio VIN                                                      | $\begin{array}{l} 50 \text{ Hz} \leq f \leq 20 \text{ kHz} \\ C_{VDD1} > 10 \ \mu\text{F} \ 10 \text{ mA} \leq I_{VDD1} \leq 700 \text{ mA} \\ \text{PRE1 and PRE2 used} \\ \text{SENSORIN connected to PRE1} \end{array}$ | 40    |     |                                | dB    |

| Tmp <sub>VDD1ADJ</sub>          | Temperature drift                                                                     |                                                                                                                                                                                                                            | -100  | 0   | 100                            | ppm/K |

| D <sub>VDD1</sub>               | Long-term drift                                                                       |                                                                                                                                                                                                                            | -0.8% | 0   | 0.8%                           |       |

# 6.11 VSOUT1, VSOUT2, and VSOUT3 Sensor-Supply Output Characteristics

Other functions must not be interfered by VSOUTx an output shorted to GND or battery voltage or other VSOUT outputs. Over operating free-air temperature range (unless otherwise noted)

| P                        | PARAMETER                                          | TEST CON                                                                       | DITIONS                  | MIN                          | TYP | MAX                          | UNIT |

|--------------------------|----------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|------------------------------|-----|------------------------------|------|

| C <sub>VSOUT</sub>       | Value of output capacitor                          | ESR range 0 m $\Omega$ to 250                                                  | mΩ                       | 0.5                          | 1   | 15                           | μF   |

| P <sub>VSOUT1/2</sub>    | Maximum power<br>dissipation, VSOUT1<br>and VSOUT2 | Single use power dissipa<br>VSOUT1 + VSOUT2                                    | ation or sum dissipation |                              |     | 1                            | W    |

| P <sub>VSOUT3</sub>      | Maximum power<br>dissipation, SOUT3                |                                                                                |                          |                              |     | 0.1                          | W    |

| I <sub>VSOUT1/2</sub>    | Output current                                     | VSOUT1 and VSOUT2 of                                                           | only                     | 0                            |     | 200                          | mA   |

| I <sub>VSOUT3</sub>      | Output current                                     | VSOUT3 only                                                                    |                          | 0                            |     | 100                          | mA   |

| V <sub>VSOUTx_UV</sub>   | Under voltage detection threshold, VSOUTx          |                                                                                |                          | 0.9 ×<br>V <sub>VSOUT</sub>  |     | 0.96 ×<br>V <sub>VSOUT</sub> | V    |

| V <sub>VSOUTx_OV</sub>   | Overvoltage detection threshold, VSOUTx            |                                                                                |                          | 1.04 ×<br>V <sub>VSOUT</sub> |     | 1.1 ×<br>V <sub>VSOUT</sub>  | V    |

|                          | VSOUT dropout                                      | SENSOR IN < VDD5                                                               | $T_J = -40^{\circ}C$     |                              |     | 0.24                         |      |

| Vdrtx                    | voltage, Vdrtx =<br>(SENSOR_IN-                    | $0 \text{ mA} \le I_{VSOUT} \le$                                               | $T_J = 25^{\circ}C$      |                              |     | 0.275                        | V    |

|                          | VVSOUT)                                            | I <sub>VSOUT_Max</sub>                                                         | T <sub>J</sub> = 175°C   |                              |     | 0.44                         |      |

| -I <sub>VSOUTX_REV</sub> | Output reverse current (limited by the regulator)  | VVSOUT = 38.5 V<br>Only one Sensor supply tested at a time, others<br>disabled |                          |                              |     | 15                           | mA   |

| I <sub>VSOUT_LIM</sub>   | Output current limit                               | $-2 V \le V_{VSOUT} \le VDD5$                                                  |                          | 200                          |     | 700                          | mA   |

Copyright © 2014–2015, Texas Instruments Incorporated

# VSOUT1, VSOUT2, and VSOUT3 Sensor-Supply Output Characteristics (continued)

Other functions must not be interfered by VSOUTx an output shorted to GND or battery voltage or other VSOUT outputs. Over operating free-air temperature range (unless otherwise noted)

| VVSOUT_SH VOL          | atput short circuit<br>Itage range<br>ad step behavior<br>REGISTER FOR VSO | No effect on other functions.<br>$-0.3 V \le V_{VIN} \le 38.5 V$<br>Square wave on VSOUTx<br>$I_{VSOUTx} = 10\%$ to 90% $I_{max}$ ;<br>f = 50 Hz to 50 kHz; duty cycle = 50%<br>No undervoltage or overvoltage detection<br>allowed<br><b>UT1/2 = 0000) AND VSOUT3</b><br>Within $I_{VSOUT}$ limits <sup>(1)</sup> | -2<br>pa | ss or fail | 38.5 | V  |

|------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|------|----|

|                        | REGISTER FOR VSO                                                           | $I_{VSOUTx} = 10\%$ to 90% $I_{max}$ ;<br>f = 50 Hz to 50 kHz; duty cycle = 50%<br>No undervoltage or overvoltage detection<br>allowed<br>UT1/2 = 0000) AND VSOUT3                                                                                                                                                 | pa       | ss or fail |      |    |

| TRACKING MODE (SPI     |                                                                            | -                                                                                                                                                                                                                                                                                                                  |          |            |      |    |

|                        | atching output error                                                       | Within I <sub>VSOUT</sub> limits <sup>(1)</sup>                                                                                                                                                                                                                                                                    |          |            |      |    |

| Ma                     | atoming output cirol                                                       | $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 140^{\circ}\text{C}$                                                                                                                                                                                                                                                  | -15      | 0          | 15   |    |

|                        | MV <sub>VSOUT</sub> = (VDD5 –                                              | 140°C < T <sub>J</sub> < 150°C                                                                                                                                                                                                                                                                                     | -20      |            | 20   | mV |

|                        | SOUT)                                                                      | 150°C < T <sub>J</sub> < 160°C                                                                                                                                                                                                                                                                                     | -25      |            | 25   |    |

|                        |                                                                            | 160°C < T <sub>J</sub>                                                                                                                                                                                                                                                                                             | -30      |            | 30   |    |

|                        |                                                                            | SPI register VSOUTx = 0001                                                                                                                                                                                                                                                                                         | -3%      | 5.25       | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 0010                                                                                                                                                                                                                                                                                         | -3%      | 5.5        | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 0011                                                                                                                                                                                                                                                                                         | -3%      | 5.75       | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 0100                                                                                                                                                                                                                                                                                         | -3%      | 6          | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 0101                                                                                                                                                                                                                                                                                         | -3%      | 6.25       | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 0110                                                                                                                                                                                                                                                                                         | -3%      | 6.5        | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 0111                                                                                                                                                                                                                                                                                         | -3%      | 6.75       | 3%   |    |

| V <sub>VSOUTx</sub> Ou | utput voltage                                                              | SPI register VSOUTx = 1000                                                                                                                                                                                                                                                                                         | -3%      | 7          | 3%   | V  |

|                        |                                                                            | SPI register VSOUTx = 1001                                                                                                                                                                                                                                                                                         | -3%      | 7.25       | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 1010                                                                                                                                                                                                                                                                                         | -3%      | 7.5        | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 1011                                                                                                                                                                                                                                                                                         | -3%      | 7.75       | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 1100                                                                                                                                                                                                                                                                                         | -3%      | 8          | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 1101                                                                                                                                                                                                                                                                                         | -3%      | 8.25       | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 1110                                                                                                                                                                                                                                                                                         | -3%      | 8.5        | 3%   |    |

|                        |                                                                            | SPI register VSOUTx = 1111                                                                                                                                                                                                                                                                                         | -3%      | 8.75       | 3%   |    |

(1) Referenced to VDD5 output, including long-term drift and temperature drift

# 6.12 NRST5 Electrical Characteristics

Reset function remains operational for voltages as low as VDD5 = 1 V. Over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                             | TEST CONDITIONS                                       | MIN                       | TYP  | MAX                       | UNIT |

|------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|---------------------------|------|---------------------------|------|

| V <sub>DLY_RST</sub>   | Voltage capability of external resistor at pin DLY_RST <sup>(1)</sup> |                                                       | 2                         |      |                           | V    |

| V <sub>VDD5_UV</sub>   | VDD5 under voltage threshold                                          |                                                       | 4.5                       | 4.65 | 4.8                       | V    |

| V <sub>VDD5_HEAD</sub> | VDD5 headroom                                                         |                                                       | 200                       |      |                           | mV   |

| V <sub>RST_I</sub>     | Reset output low level (on)                                           | $1 V = V_{VDD5}^{(2)}$                                |                           |      | 0.4                       | V    |

| V <sub>RST_h</sub>     | Reset output high level (off)                                         |                                                       | V <sub>VDD5</sub> –<br>50 |      | V <sub>VDD5</sub> +<br>50 | mV   |

| R <sub>DLY_RST</sub>   | Value of reset delay resistor                                         | Nominal value is 22 k $\Omega$ ; Can be open or short | 0                         | 22   | ∞                         | kΩ   |

(1) The external resistors to GND must be selected according these limits.

(2) An external pullup of 2 k $\Omega$  to VDD5 output is added.

# 6.13 NRST3 Electrical Characteristics

Reset function remains operational for voltages as low as VDD3 = 0 V. Over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                                    | TEST CONDITIONS                                                       | MIN                       | TYP   | MAX                      | UNIT |

|-------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|-------|--------------------------|------|

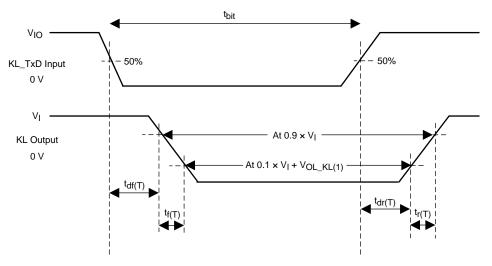

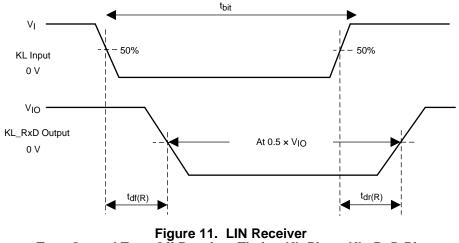

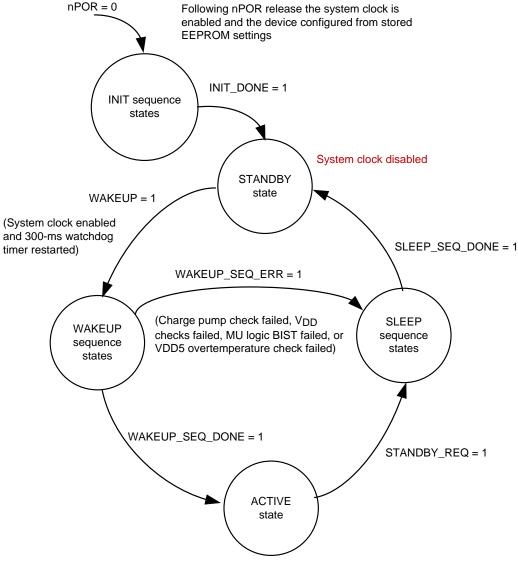

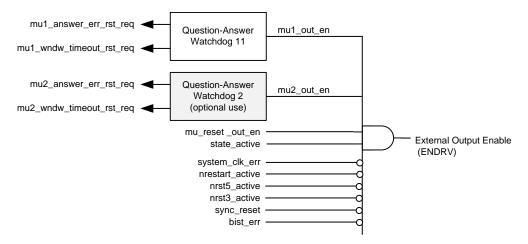

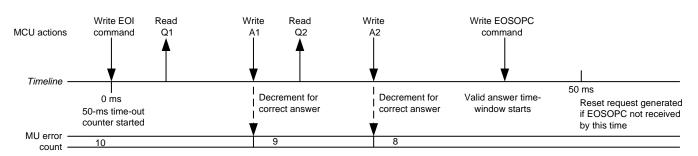

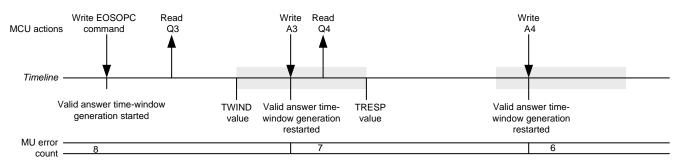

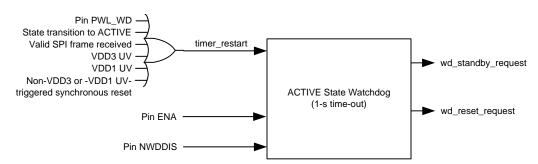

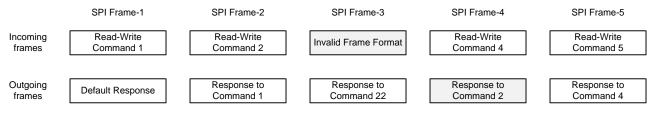

| V <sub>DLY_RST</sub>    | Voltage capability of<br>external resistor at pin<br>DLY_RST | The external resistor to GND must be selected according these limits. | 2                         |       |                          | V    |