SGLS231A - FEBRUARY 2004 - JUNE 2008

- Qualified for Automotive Applications

- Dual Output Voltages for Split-Supply Applications

- Output Current Range of 0 mA to 1.0 A Per Regulator

- 3.3-V/2.5-V, 3.3-V/1.8-V, and 3.3-V/Adjustable Output

- Fast-Transient Response

- 2% Tolerance Over Load and Temperature

- Dropout Voltage Typically 350 mV at 1 A

- Ultra Low 85 μA Typical Quiescent Current

- 1 µA Quiescent Current During Shutdown

- Dual Open Drain Power-On Reset With 200-ms Delay for Each Regulator

- 28-Pin PowerPAD<sup>™</sup> TSSOP Package

- Thermal Shutdown Protection for Each Regulator

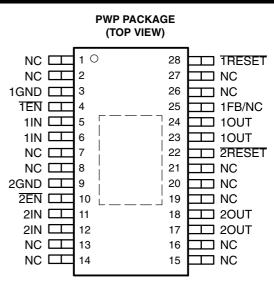

NC - No internal connection

#### description

The TPS767D3xx family of dual voltage regulators offers fast transient response, low dropout voltages and dual outputs in a compact package and incorporating stability with 10-μF low ESR output capacitors.

The TPS767D3xx family of dual voltage regulators is designed primarily for DSP applications. These devices can be used in any mixed-output voltage application, with each regulator supporting up to 1 A. Dual active-low reset signals allow resetting of core-logic and I/O separately.

| Т <sub>Ј</sub> | REGULATOR 1<br>V <sub>O</sub> (V) | REGULATOR 2<br>V <sub>O</sub> (V) | TSSOP<br>(PWP)    |

|----------------|-----------------------------------|-----------------------------------|-------------------|

|                | Adj (1.5 – 5.5 V)                 | 3.3 V                             | TPS767D301QPWPRQ1 |

| -40°C to 125°C | 1.8 V                             | 3.3 V                             | TPS767D318QPWPRQ1 |

|                | 2.5 V                             | 3.3 V                             | TPS767D325QPWPRQ1 |

#### AVAILABLE OPTIONS<sup>†‡</sup>

<sup>†</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at http://www.ti.com.

<sup>‡</sup> Package drawings, thermal data, and symbolization are available at http://www.ti.com/packaging.

The TPS767D301 is adjustable using an external resistor divider (see application information). The PWP packages are taped and reeled as indicated by the R suffix on the device type (e.g., TPS767D301QPWPRQ1).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2008 Texas Instruments Incorporated

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### description (continued)

Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 350 mV at an output current of 1 A for the TPS767D325) and is directly proportional to the output current. Additionally, since the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent of output loading (typically 85  $\mu$ A over the full range of output current, 0 mA to 1 A). These two key specifications yield a significant improvement in operating life for battery-powered systems. This LDO family also features a sleep mode; applying a TTL high signal to  $\overline{EN}$  (enable) shuts down the regulator, reducing the quiescent current to 1  $\mu$ A at T<sub>J</sub> = 25°C.

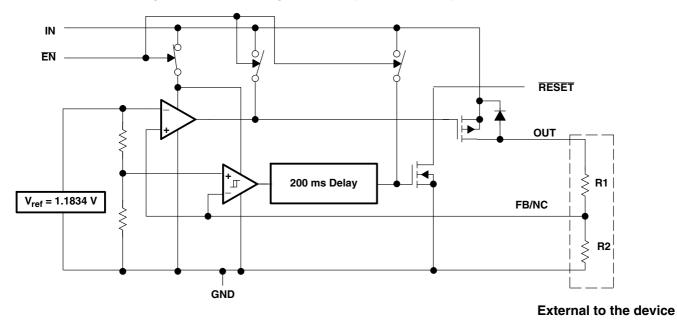

The RESET output of the TPS767D3xx initiates a reset in microcomputer and microprocessor systems in the event of an undervoltage condition. An internal comparator in the TPS767D3xx monitors the output voltage of the regulator to detect an undervoltage condition on the regulated output voltage.

The TPS767D3xx is offered in 1.8-V, 2.5-V, and 3.3-V fixed-voltage versions and in an adjustable version (programmable over the range of 1.5 V to 5.5 V). Output voltage tolerance is specified as a maximum of 2% over line, load, and temperature ranges. The TPS767D3xx family is available in 28 pin PWP TSSOP package. They operate over a junction temperature range of  $-40^{\circ}$ C to  $125^{\circ}$ C.

SGLS231A - FEBRUARY 2004 - JUNE 2008

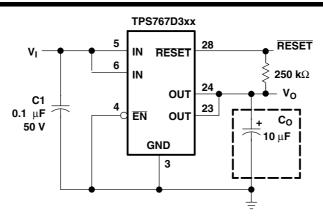

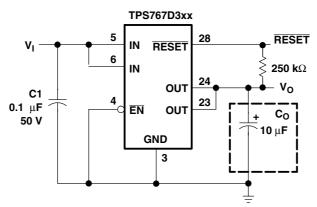

Figure 1. Typical Application Circuit (Fixed Versions) for Single Channel

SGLS231A - FEBRUARY 2004 - JUNE 2008

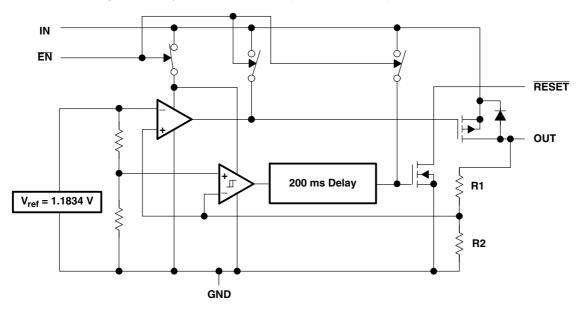

#### functional block diagram—adjustable version (for each LDO)

functional block diagram—fixed-voltage version (for each LDO)

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### **Terminal Functions**

| TE            | RMINAL                                      |     |                                                                                     |

|---------------|---------------------------------------------|-----|-------------------------------------------------------------------------------------|

| NAME          | NO.                                         | I/O | DESCRIPTION                                                                         |

| 1GND          | 3                                           |     | Regulator #1 ground                                                                 |

| 1EN           | 4                                           | Ι   | Regulator #1 enable                                                                 |

| 1IN           | 5, 6                                        | Ι   | Regulator #1 input supply voltage                                                   |

| 2GND          | 9                                           |     | Regulator #2 ground                                                                 |

| 2EN           | 10                                          | Ι   | Regulator #2 enable                                                                 |

| 2IN           | 11, 12                                      | Ι   | Regulator #2 input supply voltage                                                   |

| 2OUT          | 17, 18                                      | 0   | Regulator #2 output voltage                                                         |

| 2RESET        | 22                                          | 0   | Regulator #2 reset signal                                                           |

| 10UT          | 23, 24                                      | 0   | Regulator #1 output voltage                                                         |

| 1FB/NC        | 25                                          | Ι   | Regulator #1 output voltage feedback for adjustable and no connect for fixed output |

| <b>1RESET</b> | 28                                          | 0   | Regulator #1 reset signal                                                           |

| NC            | 1, 2, 7, 8,<br>13–16, 19, 20,<br>21, 26, 27 |     | No connection                                                                       |

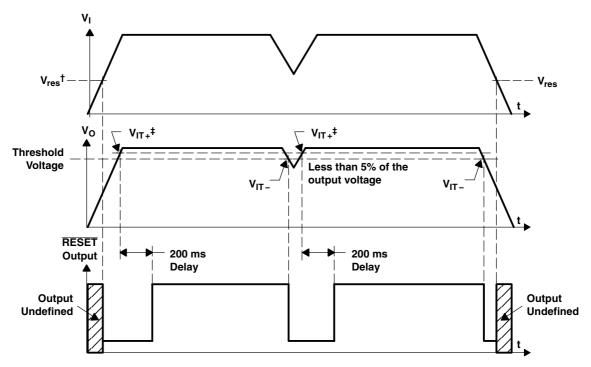

#### timing diagram

<sup>†</sup> V<sub>res</sub> is the minimum input voltage for a valid RESET. The symbol V<sub>res</sub> is not currently listed within EIA or JEDEC standards for semiconductor symbology.

$^{\ddagger}$  VIT –Trip voltage is typically 5% lower than the output voltage (95%V<sub>O</sub>)

#### SGLS231A - FEBRUARY 2004 - JUNE 2008

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Input voltage range <sup>‡</sup> , V <sub>I</sub>            |                               |

|--------------------------------------------------------------|-------------------------------|

| Output voltage, $V_{\Omega}$ (10UT, 20UT)                    |                               |

| Output voltage, V <sub>O</sub> (RESET)                       |                               |

| Peak output current                                          | Internally limited            |

| ESD rating, HBM                                              |                               |

| Continuous total power dissipation                           | See dissipation rating tables |

| Operating virtual junction temperature range, T <sub>1</sub> | –40°C to 150°C                |

| Storage temperature range, T <sub>stg</sub>                  | −65°C to 150°C                |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>‡</sup> All voltage values are with respect to network terminal ground.

|                                                        | DISSIPATION RATING TABLE |        |            |        |        |  |  |  |  |  |  |

|--------------------------------------------------------|--------------------------|--------|------------|--------|--------|--|--|--|--|--|--|

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |                          |        |            |        |        |  |  |  |  |  |  |

| DIMOS                                                  | 0                        | 3.58 W | 35.8 mW/°C | 1.97 W | 1.43 W |  |  |  |  |  |  |

| PWP§                                                   | 250                      | 5.07 W | 50.7 mW/°C | 2.79 W | 2.03 W |  |  |  |  |  |  |

This parameter is measured with the recommended copper heat sink pattern on a 4–layer PCB, 1 oz. copper on 4–in x 4–in ground layer. For more information, refer to TI technical brief literature number SLMA002.

#### recommended operating conditions

|                                                        | MIN | MAX | UNIT |

|--------------------------------------------------------|-----|-----|------|

| Input voltage, VI <sup>¶</sup> (1IN, 2IN)              | 2.7 | 10  | V    |

| Output current for each LDO, I <sub>O</sub> (Note 1)   | 0   | 1.0 | А    |

| Output voltage range, V <sub>O</sub> (1OUT, 2OUT)      | 1.5 | 5.5 | V    |

| Operating virtual junction temperature, T <sub>J</sub> | -40 | 125 | °C   |

<sup>¶</sup> To calculate the minimum input voltage for your maximum output current, use the following equation:  $V_{I(min)} = V_{O(max)} + V_{DO(max load)}$ .

NOTE 1: Continuous current and operating junction temperature are limited by internal protection circuitry, but it is not recommended that the device operate under conditions beyond those specified in this table for extended periods of time.

SGLS231A - FEBRUARY 2004 - JUNE 2008

|                        |                                                      |                    | (                                                            |                                        |                    |      |                    |                 |

|------------------------|------------------------------------------------------|--------------------|--------------------------------------------------------------|----------------------------------------|--------------------|------|--------------------|-----------------|

|                        | PARAMETER                                            |                    | TEST CO                                                      | NDITIONS                               | MIN                | TYP  | MAX                | UNIT            |

|                        |                                                      | A diversity in the | $1.5 \text{ V} \le \text{V}_{\text{O}} \le 5.5 \text{ V},$   | $T_J = 25^{\circ}C$                    |                    | Vo   |                    |                 |

|                        |                                                      | Adjustable         | 10 μA < I <sub>O</sub> < 1 A                                 | $T_J = -40^{\circ}C$ to $125^{\circ}C$ | 0.98V <sub>O</sub> |      | 1.02V <sub>O</sub> |                 |

|                        |                                                      | 1.0.) Oursuit      | 2.8 V < V <sub>I</sub> < 10 V,                               | $T_J = 25^{\circ}C$                    |                    | 1.8  | v                  |                 |

|                        | $ t_{2}, t_{2}\rangle$ (222 Note 2)                  | 1.8 V Ouput        | 10 μA < I <sub>O</sub> < 1 A                                 | $T_J = -40^{\circ}C$ to $125^{\circ}C$ | 1.764              |      | 1.836              | v               |

| Output vo              | ltage (V <sub>O</sub> ) (see Note 2)                 | 2.5 V Output       | 3.5 V < V <sub>I</sub> < 10 V,                               | $T_J = 25^{\circ}C$                    |                    | 2.5  |                    |                 |

|                        |                                                      | 2.5 V Output       | 10 μA < I <sub>O</sub> < 1 A                                 | $T_J = -40^{\circ}C$ to $125^{\circ}C$ | 2.45               |      | 2.55               |                 |

|                        |                                                      | 3.3 V Output       | 4.3 V < V <sub>I</sub> < 10 V,                               | $T_J = 25^{\circ}C$                    |                    | 3.3  |                    | v               |

|                        |                                                      |                    | 10 μA < I <sub>O</sub> < 1 A                                 | $T_J = -40^{\circ}C$ to $125^{\circ}C$ | 3.234              |      | 3.366              | v               |

| Quiescent<br>(see Note | t current (GND current) for e                        | each LDO           | 10 $\mu$ A < I <sub>O</sub> < 1 A,                           | $T_J = 25^{\circ}C$                    |                    | 85   |                    | A               |

| (See Note              | <u>~)</u>                                            |                    | I <sub>O</sub> = 1 A,                                        | $T_J = -40^{\circ}C$ to $125^{\circ}C$ |                    |      | 125                | μA              |

| •                      | Itage line regulation for eac<br>(see Notes 2 and 3) | h LDO              | $V_{O} + 1 V < V_{I} \le 10 V,$                              | $T_{\rm J}=25^{\circ}C$                |                    | 0.01 |                    | %/V             |

| Output no              | ise voltage                                          |                    | BW = 200 Hz to 100 kH $I_{C}$ = 1 A, $C_{O}$ = 10 $\mu$ F,   |                                        |                    | 55   |                    | μVrms           |

| Output cu              | rrent limit for each LDO                             |                    | V <sub>O</sub> = 0 V                                         |                                        |                    | 1.7  | 2                  | А               |

| Thermal s              | hutdown juction temperatur                           | e                  |                                                              |                                        |                    | 150  |                    | °C              |

| <b>.</b>               |                                                      |                    | $2.7 < V_I < 10V,$<br>$T_J = 25^{\circ}C,$                   | $\overline{EN} = V_{I,I}$              |                    | 1    |                    | μA              |

| Standby c              | urrent for each LDO                                  |                    | $2.7 < V_I < 10V,$<br>$T_J = -40^{\circ}C$ to $125^{\circ}C$ | $\overline{EN} = V_{I,I}$              |                    |      | 10                 | μA              |

| FB input o             | current                                              | Adjustable         | FB = 1.5 V                                                   |                                        |                    | 2    |                    | nA              |

| High level             | enable input voltage                                 |                    |                                                              |                                        | 2.0                |      |                    | V               |

| Low level              | enable input voltage                                 |                    |                                                              |                                        |                    |      | 0.8                | V               |

| Power sup              | oply ripple rejection (see No                        | ote 2)             | $f = 1 \text{ KHz}, T_J = 25^{\circ}\text{C},$               | $C_O = 10 \ \mu F$                     |                    | 60   |                    | dB              |

|                        | Minimum input voltage                                | or valid RESET     | $I_{O(RESET)} = 300 \ \mu A$                                 |                                        |                    | 1.1  |                    | V               |

|                        | Trip threshold voltage                               |                    | V <sub>O</sub> decreasing                                    |                                        | 92                 |      | 98                 | %V <sub>O</sub> |

| Deest                  | Hysteresis voltage                                   |                    | Measured at V <sub>O</sub>                                   |                                        |                    | 0.5  |                    | %V <sub>O</sub> |

| Reset                  | Output low voltage                                   |                    | V <sub>I</sub> = 2.7 V,                                      | I <sub>O(RESET)</sub> = 1 mA           |                    | 0.15 | 0.4                | V               |

|                        | Leakage current                                      |                    | V <sub>(RESET)</sub> = 7 V                                   |                                        |                    |      | 1                  | μA              |

|                        | RESET time-out delay                                 |                    |                                                              |                                        |                    | 200  |                    | mA              |

# electrical characteristics, $V_i = V_{O(nom)} + 1$ V, $I_O = 1$ mA, $\overline{EN} = 0$ , $C_O = 10 \ \mu$ F (unless otherwise noted)

NOTES: 2. Minimum IN operating voltage is 2.7 V or  $V_{O(typ)}$  + 1 V, whichever is greater. maximum IN voltage 10V. 3. If VO  $\leq$  1.8 V, V<sub>Imin</sub> = 2.7 V, and V<sub>Imax</sub> = 10 V:

Line Reg. (mV) =

$$(\%/V) \times \frac{V_O(V_{Imax} - 2.7 V)}{100} \times 1000$$

If VO  $\geq$  2.5 V, V<sub>Imin</sub> = Vo + 1 V, and V<sub>Imax</sub> = 10 V:

Line Reg. (mV) =

$$(\%/V) \times \frac{V_O(V_{Imax} - (V_O + 1 V))}{100} \times 1000$$

SGLS231A - FEBRUARY 2004 - JUNE 2008

# electrical characteristics, $V_i$ = $V_{O(nom)}$ + 1 V, $I_O$ = 1 mA, $\overline{EN}$ = 0, $C_O$ = 10 $\mu F$ (unless otherwise noted) (continued)

| PARAMETER                    | TEST CO                      | NDITIONS                               | MIN | ТҮР | MAX | UNIT |  |

|------------------------------|------------------------------|----------------------------------------|-----|-----|-----|------|--|

|                              | <u>EN</u> = 0 V              |                                        | –1  | 0   | 1   |      |  |

| Input current (EN)           | $\overline{EN} = V_1$        | -1                                     |     | 1   | μA  |      |  |

| Load regulation              |                              |                                        |     | 3   |     | mV   |  |

|                              |                              | T <sub>J</sub> = 25°C                  |     | 350 |     |      |  |

| Dropout voltage (see Note 4) | $V_{O} = 3.3 V, I_{O} = 1 A$ | $T_J = -40^{\circ}C$ to $125^{\circ}C$ |     |     | 575 | mV   |  |

NOTE 4: IN voltage equals Vo(Typ) – 100mV; Adjustable output voltage set to 3.3V nominal with external resistor divider. 1.8V, and 2.5V dropout voltage is limited by input voltage range limitations.

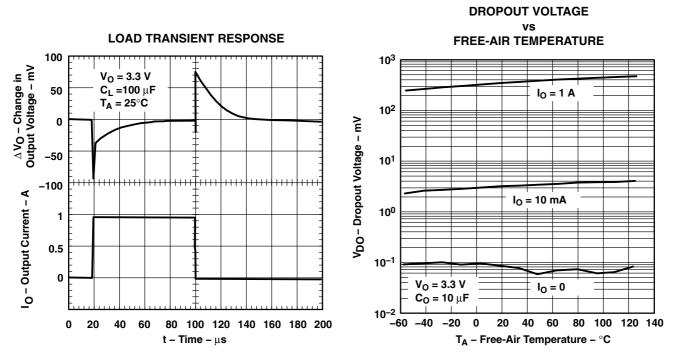

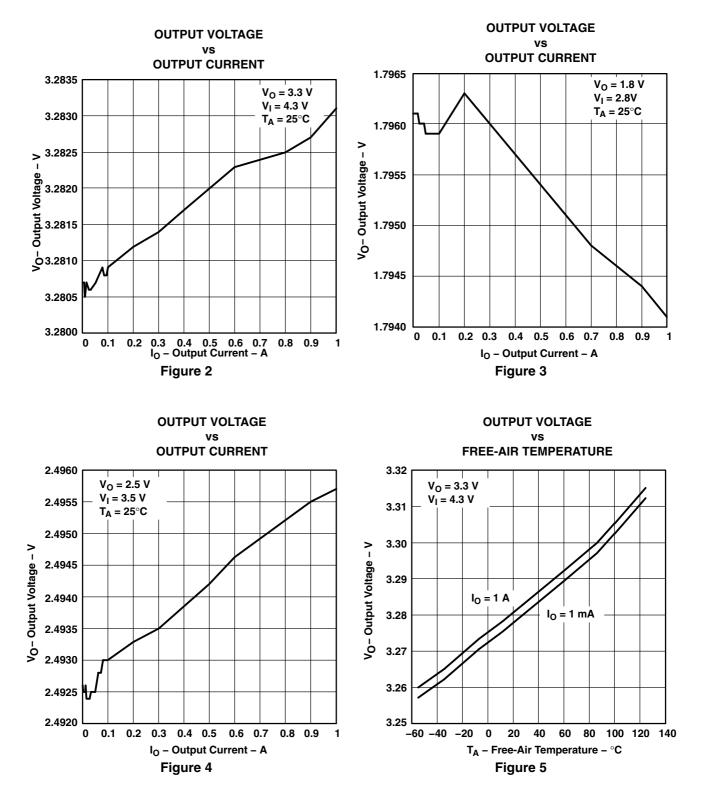

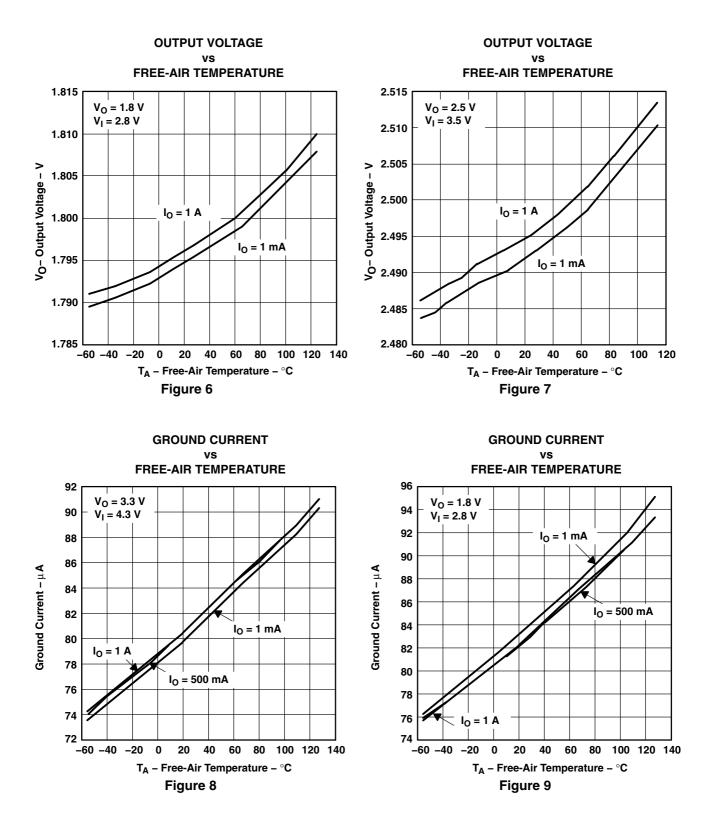

### **TYPICAL CHARACTERISTICS**

#### Table of Graphs

|                                                                                                                                                                                                                                                                  |                                           | FIGURE  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------|

| 0 · · · ·                                                                                                                                                                                                                                                        | vs Output current                         | 2, 3, 4 |

| Output voltage   Ground current   Power supply ripple rejection   Output spectral noise density   Output impedance   Dropout voltage   Line transient response   Load transient response   Output voltage   Dropout voltage   Equivalent series resistance (ESR) | vs Free-air temperature                   | 5, 6, 7 |

| Ground current                                                                                                                                                                                                                                                   | vs Free-air temperature                   | 8, 9    |

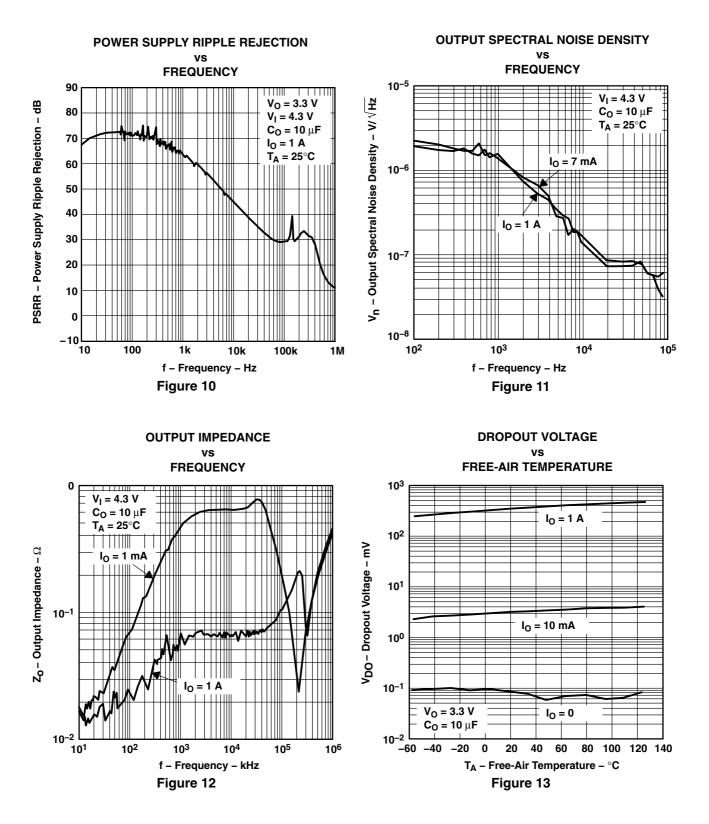

| Power supply ripple rejection                                                                                                                                                                                                                                    | vs Frequency                              | 10      |

| Output spectral noise density                                                                                                                                                                                                                                    | vs Frequency                              | 11      |

| Output impedance                                                                                                                                                                                                                                                 | vs Frequency                              | 12      |

| Dropout voltage                                                                                                                                                                                                                                                  | vs Free-air temperature                   | 13      |

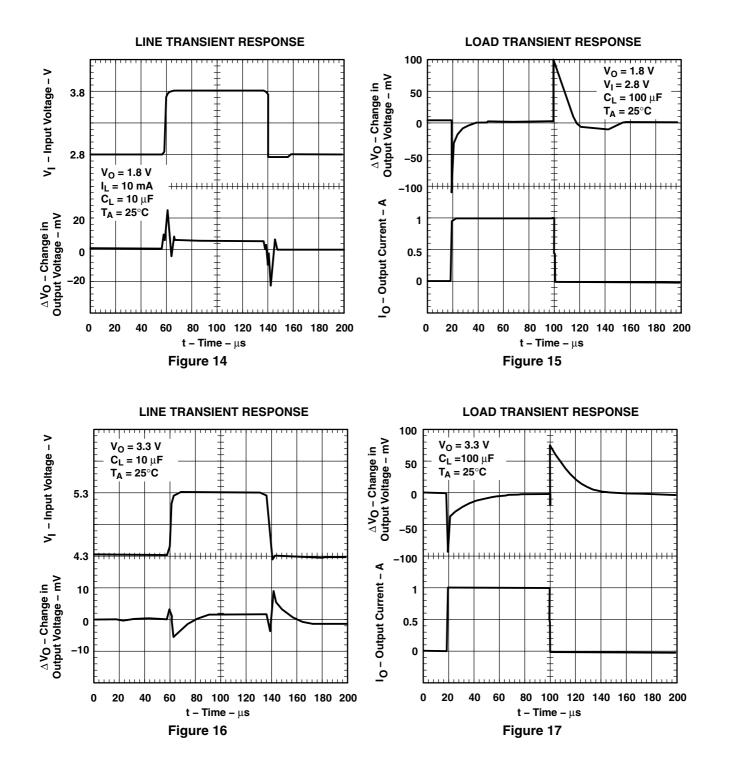

| Line transient response                                                                                                                                                                                                                                          |                                           | 14, 16  |

| Load transient response                                                                                                                                                                                                                                          |                                           | 15, 17  |

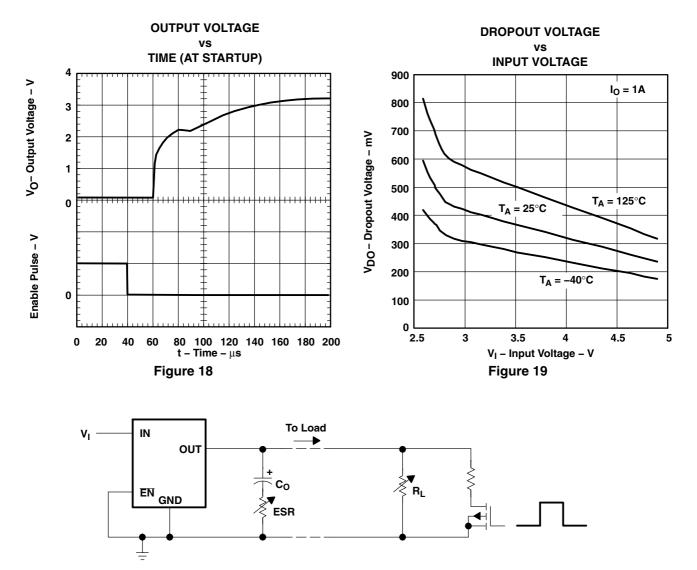

| Output voltage                                                                                                                                                                                                                                                   | vs Time                                   | 18      |

| Dropout voltage                                                                                                                                                                                                                                                  | vs Input voltage                          | 19      |

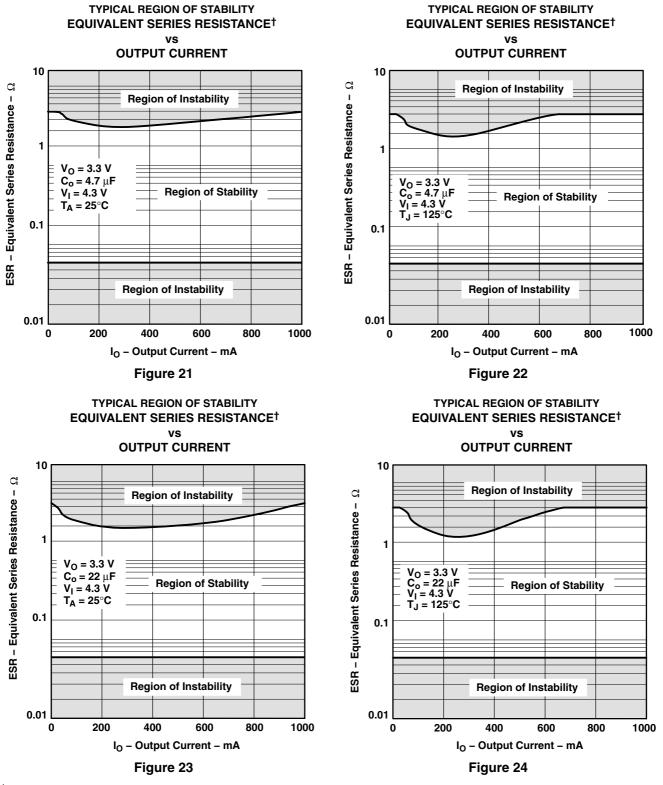

|                                                                                                                                                                                                                                                                  | vs Output current, $T_A = 25^{\circ}C$    | 21      |

|                                                                                                                                                                                                                                                                  | vs Output current, T <sub>J</sub> = 125°C | 22      |

| Equivalent series resistance (ESR)                                                                                                                                                                                                                               | vs Output Current, $T_A = 25^{\circ}C$    | 23      |

|                                                                                                                                                                                                                                                                  | vs Output current, $T_J = 125^{\circ}C$   | 24      |

SGLS231A - FEBRUARY 2004 - JUNE 2008

SGLS231A - FEBRUARY 2004 - JUNE 2008

SGLS231A - FEBRUARY 2004 - JUNE 2008

SGLS231A - FEBRUARY 2004 - JUNE 2008

SGLS231A - FEBRUARY 2004 - JUNE 2008

Figure 20. Test Circuit for Typical Regions of Stability (Figures 21 through 24) (fixed output options)

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### TYPICAL CHARACTERISTICS

<sup>+</sup> Equivalent series resistance (ESR) refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to C<sub>O</sub>.

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### **APPLICATION INFORMATION**

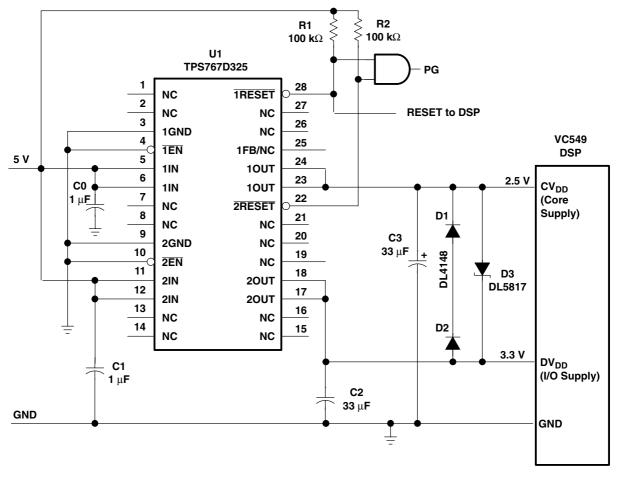

The features of the TPS767D3xx family (low-dropout voltage, ultra low quiescent current, power-saving shutdown mode, and a supply-voltage supervisor) and the power-dissipation properties of the TSSOP PowerPAD package have enabled the integration of the dual LDO regulator with high output current for use in DSP and other multiple voltage applications. Figure 25 shows a typical dual-voltage DSP application.

Figure 25. Dual-Voltage DSP Application

DSP power requirements include very high transient currents that must be considered in the initial design. This design uses higher-valued output capacitors to handle the large transient currents.

#### device operation

The TPS767D3xx features very low quiescent current, which remain virtually constant even with varying loads. Conventional LDO regulators use a pnp pass element, the base current of which is directly proportional to the load current through the regulator ( $I_B = I_C/\beta$ ). Close examination of the data sheets reveals that these devices are typically specified under near no-load conditions; actual operating currents are much higher as evidenced by typical quiescent current versus load current curves. The TPS767D3xx uses a PMOS transistor to pass current; because the gate of the PMOS is voltage driven, operating current is low and invariable over the full load range. The TPS767D3xx specifications reflect actual performance under load condition.

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### device operation (continued)

Another pitfall associated with the pnp-pass element is its tendency to saturate when the device goes into dropout. The resulting drop in  $\beta$  forces an increase in I<sub>B</sub> to maintain the load. During power up, this translates to large start-up currents. Systems with limited supply current may fail to start up. In battery-powered systems, it means rapid battery discharge when the voltage decays below the minimum required for regulation. The TPS767D3xx quiescent current remains low even when the regulator drops out, eliminating both problems.

The TPS767D3xx family also features a shutdown mode that places the output in the high-impedance state (essentially equal to the feedback-divider resistance) and reduces quiescent current to under 2  $\mu$ A. If the shutdown feature is not used,  $\overline{EN}$  should be tied to ground. Response to an enable transition is quick; regulated output voltage is typically reestablished in 120  $\mu$ s.

#### minimum load requirements

The TPS767D3xx family is stable even at zero load; no minimum load is required for operation.

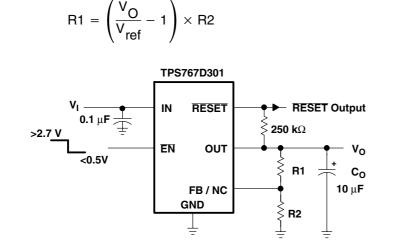

#### FB - pin connection (adjustable version only)

The FB pin is an input pin to sense the output voltage and close the loop for the adjustable option. The output voltage is sensed through a resistor divider network as is shown in Figure 27 to close the loop. Normally, this connection should be as short as possible; however, the connection can be made near a critical circuit to improve performance at that point. Internally, FB connects to a high-impedance wide-bandwidth amplifier and noise pickup feeds through to the regulator output. Routing the FB connection to minimize/avoid noise pickup is essential. In fixed output options this pin is a no connect.

#### external capacitor requirements

An input capacitor is not required; however, a ceramic bypass capacitor (0.047 pF to 0.1  $\mu$ F) improves load transient response and noise rejection when the TPS767D3xx is located more than a few inches from the power supply. A higher-capacitance electrolytic capacitor may be necessary if large (hundreds of milliamps) load transients with fast rise times are anticipated.

Like all low dropout regulators, the TPS767D3xx requires an output capacitor connected between OUT and GND to stabilize the internal control loop. The minimum recommended capacitance value is 10  $\mu$ F and the ESR (equivalent series resistance) must be between 60 m $\Omega$  and 1.5  $\Omega$ . Capacitor values 10  $\mu$ F or larger are acceptable, provided the ESR is less than 1.5  $\Omega$ . Solid tantalum electrolytic, aluminum electrolytic, and multilayer ceramic capacitors are all suitable, provided they meet the requirements described previously.

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### external capacitor requirements (continued)

When necessary to achieve low height requirements along with high output current and/or high ceramic load capacitance, several higher ESR capacitors can be used in parallel to meet the previous guidelines.

Figure 26. Typical Application Circuit (Fixed Versions) for Single Channel

#### programming the TPS767D301 adjustable LDO regulator

The output voltage of the TPS767D301 adjustable regulator is programmed using an external resistor divider as shown in Figure 27. The output voltage is calculated using:

$$V_{O} = V_{ref} \times \left(1 + \frac{R1}{R2}\right)$$

(1)

where:

V<sub>ref</sub> = 1.1834 V typ (the internal reference voltage)

Resistors R1 and R2 should be chosen for approximately 50- $\mu$ A divider current. Lower value resistors can be used but offer no inherent advantage and waste more power. Higher values should be avoided as leakage currents at FB increase the output voltage error. The recommended design procedure is to choose R2 = 30.1 k $\Omega$  to set the divider current at 50  $\mu$ A and then calculate R1 using:

OUTPUT VOLTAGE PROGRAMMING GUIDE

| OUTPUT<br>VOLTAGE | R1   | R2   | UNIT |

|-------------------|------|------|------|

| 2.5 V             | 33.2 | 30.1 | kΩ   |

| 3.3 V             | 53.6 | 30.1 | kΩ   |

| 3.6 V             | 61.9 | 30.1 | kΩ   |

| 4 75V             | 90.8 | 30.1 | kΩ   |

Figure 27. TPS767D301 Adjustable LDO Regulator Programming

(2)

SGLS231A - FEBRUARY 2004 - JUNE 2008

#### **Reset indicator**

The TPS767D3xx features a RESET output that can be used to monitor the status of the regulator. The internal comparator monitors the output voltage: when the output drops to 95% (typical) of its regulated value, the RESET output transistor turns on, taking the signal low. The open-drain output requires a pullup resistor. If not used, it can be left floating. RESET can be used to drive power-on reset circuitry or as a low-battery indicator.

#### regulator protection

The TPS767D3xx PMOS-pass transistor has a built-in back-gate diode that safely conducts reverse currents when the input voltage drops below the output voltage (e.g., during power down). Current is conducted from the output to the input and is not internally limited. When extended reverse voltage is anticipated, external limiting may be appropriate.

The TPS767D3xx also features internal current limiting and thermal protection. During normal operation, the TPS767D3xx limits output current to approximately 1.7 A. When current limiting engages, the output voltage scales back linearly until the overcurrent condition ends. While current limiting is designed to prevent gross device failure, care should be taken not to exceed the power dissipation ratings of the package. If the temperature of the device exceeds  $150^{\circ}C(typ)$ , thermal-protection circuitry shuts it down. Once the device has cooled below  $130^{\circ}C(typ)$ , regulator operation resumes.

#### power dissipation and junction temperature

Specified regulator operation is assured to a junction temperature of 125°C; the maximum junction temperature should be restricted to 125°C under normal operating conditions. This restriction limits the power dissipation the regulator can handle in any given application. To ensure the junction temperature is within acceptable limits, calculate the maximum allowable dissipation,  $P_{D(max)}$ , and the actual dissipation,  $P_D$ , which must be less than or equal to  $P_{D(max)}$ .

The maximum-power-dissipation limit is determined using the following equation:

$$P_{D(max)} = \frac{T_J max - T_A}{R_{\theta JA}}$$

where:

T<sub>J</sub>max is the maximum allowable junction temperature

$R_{\theta JA}$  is the thermal resistance junction-to-ambient for the package, i.e., 27.9°C/W for the 28-terminal PWP with no airflow.

T<sub>A</sub> is the ambient temperature.

The regulator dissipation is calculated using:

$$\mathsf{P}_{\mathsf{D}} = \left(\mathsf{V}_{\mathsf{I}} - \mathsf{V}_{\mathsf{O}}\right) \times \mathsf{I}_{\mathsf{O}}$$

Power dissipation resulting from quiescent current is negligible. Excessive power dissipation will trigger the thermal protection circuit.

15-Oct-2015

## PACKAGING INFORMATION

| Orderable Device  | Status | Package Type | •       | Pins | •    | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|-------------------|--------|--------------|---------|------|------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                   | (1)    |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| TPS767D301QPWPRQ1 | ACTIVE | HTSSOP       | PWP     | 28   | 2000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 125   | 767D301Q1      | Samples |

| TPS767D318QPWPRQ1 | ACTIVE | HTSSOP       | PWP     | 28   | 2000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 125   | 767D318Q1      | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# PACKAGE OPTION ADDENDUM

15-Oct-2015

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPS767D301-Q1, TPS767D318-Q1, TPS767D325-Q1 :

• Catalog: TPS767D301, TPS767D318, TPS767D325

• Enhanced Product: TPS767D301-EP

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Enhanced Product Supports Defense, Aerospace and Medical Applications

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

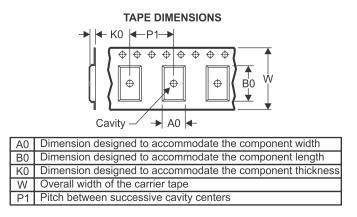

#### TAPE AND REEL INFORMATION

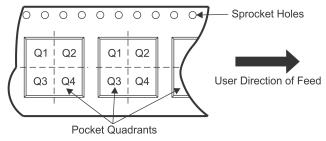

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS767D301QPWPRQ1           | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

| TPS767D318QPWPRQ1           | HTSSOP          | PWP                | 28 | 2000 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

TEXAS INSTRUMENTS

www.ti.com

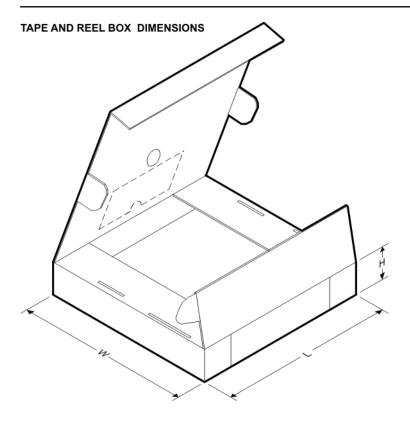

# PACKAGE MATERIALS INFORMATION

5-Jul-2019

\*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS767D301QPWPRQ1 | HTSSOP       | PWP             | 28   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS767D318QPWPRQ1 | HTSSOP       | PWP             | 28   | 2000 | 350.0       | 350.0      | 43.0        |

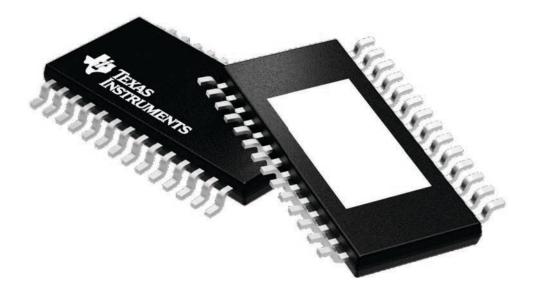

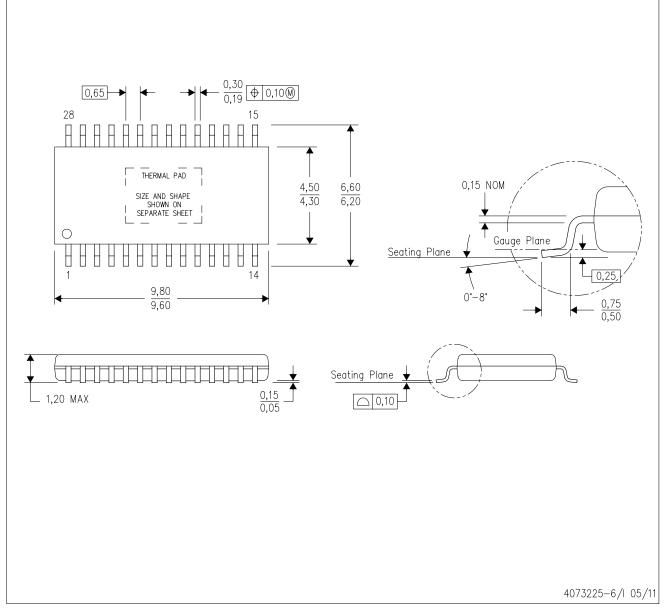

# **PWP 28**

4.4 x 9.7, 0.65 mm pitch

# **GENERIC PACKAGE VIEW**

PowerPAD<sup>™</sup> TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

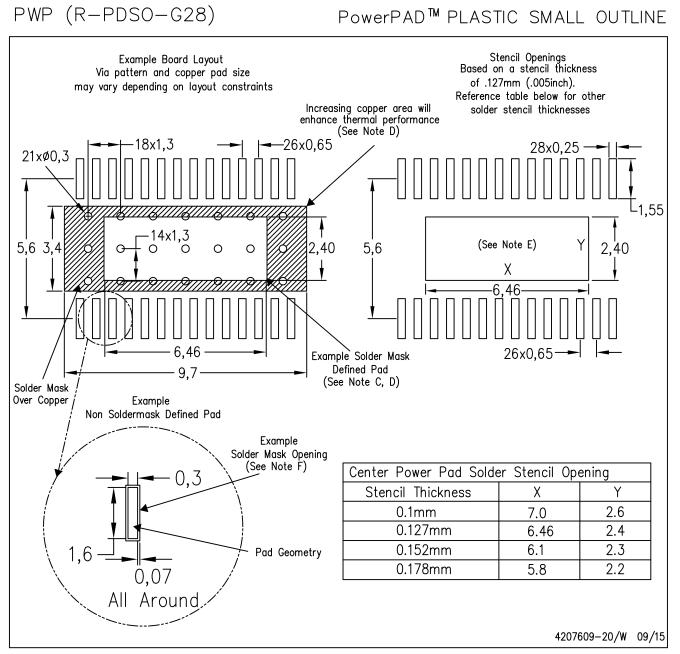

PWP (R-PDSO-G28)

PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

All linear dimensions are in millimeters. NOTES: Α.

- Β. This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D.

- Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions. E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

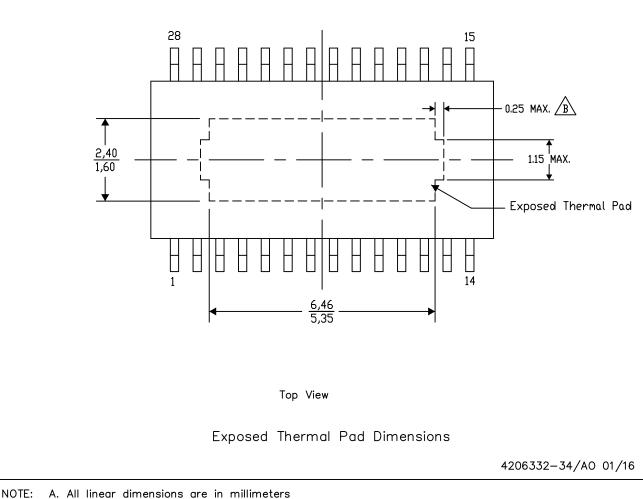

# PWP (R-PDSO-G28) PowerPAD<sup>™</sup> SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

B. Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

NOTES:

Α.

B. This drawing is subject to change without notice.

All linear dimensions are in millimeters.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated