Sample &

Buv

TPS61280, TPS61281, TPS61282

SLVSBI1A-OCTOBER 2013-REVISED SEPTEMBER 2014

# TPS6128x Low-, Wide- Voltage Battery Front-End DC/DC Converter Single-Cell Li-Ion, Ni-Rich, Si-Anode Applications

Technical

Documents

## 1 Features

- 95% Efficiency at 2.3MHz Operation

- $2\mu A$  Quiescent Current in Low I<sub>Q</sub> Pass-Through Mode

- Wide  $V_{IN}$  Range From 2.3V to 4.8V

- $I_{OUT} \ge 4A$  (Peak) at  $V_{OUT} = 3.35V$ ,  $V_{IN} \ge 2.65V$

- Integrated Pass-Through Mode (35mΩ)

- Programmable Valley Inductor Current Limit and Output Voltage

- Programmable Average Input Current Limit and Output Voltage

- True Pass-Through Mode During Shutdown

- Best-in-Class Line and Load Transient

- Low-Ripple Light-Load PFM Mode

- In-Situ Customization with On-Chip E<sup>2</sup>PROM (Write Protect)

- Two Interface Options:

- I<sup>2</sup>C Compatible I/F up to 3.4Mbps (TPS61280)

- Simple I/O Logic Control Interface (TPS6128x)

- Thermal Shutdown and Overload Protection

- Total Solution Size <20mm<sup>2</sup>, Sub 1-mm Profile

## 2 Applications

- Single-Cell Ni-Rich, Si-Anode, Li-Ion, LiFePO4 Smart-Phones or Tablet PCs

- 2.5G/3G/4G Mini-Module Data Cards

- Current Limited Applications Featuring High Peak

Power Loads

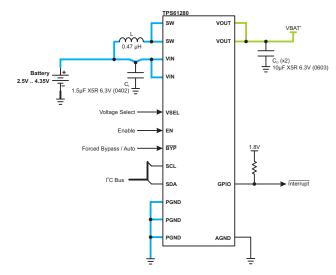

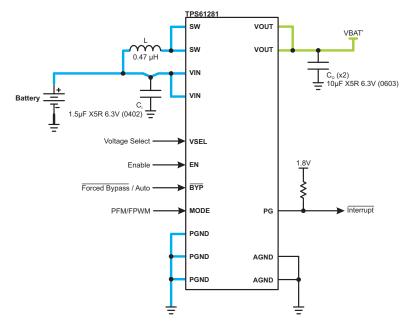

## 4 Simplified Schematic

## 3 Description

The TPS6128x device provides a power supply solution for products powered by either by a Li-Ion, Nickel-Rich, Silicon Anode, Li-Ion or LiFePO4 battery. The voltage range is optimized for single-cell portable applications like in smart-phones or tablet PCs.

Used as a high-power pre-regulator, the TPS6128x extends the battery run-time and overcomes input current- and voltage limitations of the powered system.

While in shutdown, the TPS6128x operates in a true pass-through mode with only  $2\mu A$  quiescent consumption for longest battery shelf life.

During operation, when the battery is at a good stateof-charge, a low-ohmic, high-efficient integrated passthrough path connects the battery to the powered system.

If the battery gets to a lower state of charge and its voltage becomes lower than the desired minimum system voltage, the device seamlessly transits into boost mode to utilize the full battery capacity.

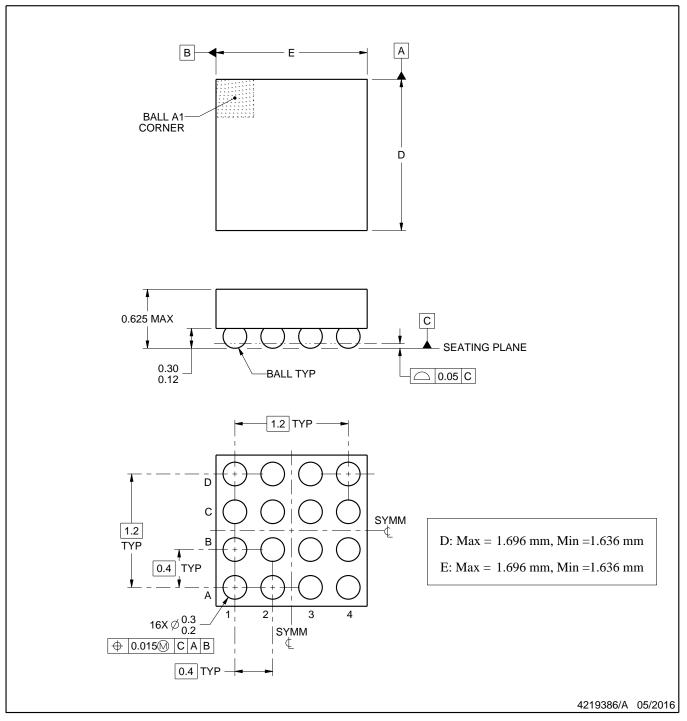

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TPS61280    |            |                   |

| TPS61281    | DSBGA (16) | 1.66 mm x 1.66 mm |

| TPS61282    |            |                   |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

Features ..... 1

Applications ..... 1

Description ..... 1

Simplified Schematic..... 1

Revision History..... 2

Device Comparison Table...... 3

Pin Configuration and Functions ...... 4

9.2 Handling Ratings...... 6

9.4 Thermal Information ...... 7

9.8 Typical Characteristics ..... 12

10.2 Functional Block Diagram ...... 15

10 Detailed Description ...... 14

Absolute Maximum Ratings ...... 6

Recommended Operating Conditions ...... 6

Electrical Characteristics......7

1

2

3

4

5

6

7

8

9

9.1

9.3

9.5

## **Table of Contents**

40.0

|                      | 10.3 | Feature Description               | 1 <mark>6</mark> |

|----------------------|------|-----------------------------------|------------------|

|                      | 10.4 | Device Functional Modes           | 18               |

|                      | 10.5 | Programming                       | 23               |

|                      | 10.6 | Register Maps                     | 26               |

| 11                   | Appl | lication and Implementation       | 34               |

|                      | 11.1 | Application Information           |                  |

|                      | 11.2 | Typical Application               | 34               |

| 12                   | Pow  | er Supply Recommendations         | 46               |

| 13                   |      | out                               |                  |

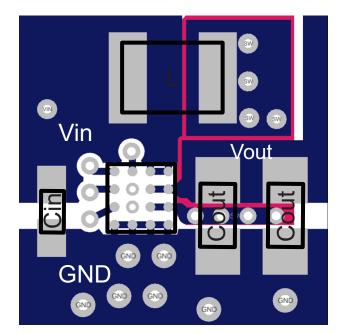

|                      | 13.1 | Layout Guidelines                 | 46               |

|                      | 13.2 | Layout Example                    | 46               |

|                      | 13.3 | Thermal Consideration             | 47               |

| 14                   | Devi | ce and Documentation Support      | 48               |

|                      | 14.1 | Device Support                    | 48               |

|                      | 14.2 | Related Links                     | 48               |

|                      | 14.3 | Trademarks                        | 48               |

|                      | 14.4 | Electrostatic Discharge Caution   | 48               |

|                      | 14.5 | Glossary                          |                  |

| 12<br>13<br>14<br>15 | Mecl | hanical, Packaging, and Orderable |                  |

|                      |      | mation                            | 49               |

|                      | 15.1 | Package Summary                   | 49               |

## 5 Revision History

#### Changes from Original (October 2013) to Revision A

#### Page

| 1           |

|-------------|

| 1           |

| in<br>4     |

| 6           |

| 12          |

| 21          |

| -<br>-<br>- |

2

www.ti.com

## 6 Description (continued)

TPS6128x device supports more than 4A pulsed load current even from a deeply discharged battery. In this mode of operation, the TPS6128x enables the utilization of the full battery capacity: A high battery-cut-off voltage originated by powered components with a high minimum input voltage is overcome; new battery chemistries can be fully discharged; high current pulses forcing the system into shutdown are buffered by the device seamlessly transitioning between boost and by-pass mode back and forth.

This has significant impact on the battery on-time and translates into either a longer use-time and better userexperience at an equal battery capacity or into reduced battery costs at similar use-times.

The TPS6128x operates in synchronous, 2.3MHz boost mode and enters power-save mode operation (PFM) at light load currents to maintain high efficiency over the entire load current range.

The TPS6128x offers a small solution size (<20mm<sup>2</sup>) due to minimum amount of external components, enabling the use of small inductors and input capacitors, available as a 16-pin chip-scale package (CSP).

## 7 Device Comparison Table

| PART NUMBER |                                                                               | DEVICE<br>SPECIFIC FEATURES                       |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

|             |                                                                               | DC/DC boost / bypass threshold = 3.15V (Vsel = L) |  |  |  |  |  |

| TPS61280    | I <sup>2</sup> C Control Interface<br>User Prog. E <sup>2</sup> PROM Settings | DC/DC boost / bypass threshold = 3.35V (Vsel = H) |  |  |  |  |  |

|             |                                                                               | Valley inductor current limit = 3A                |  |  |  |  |  |

|             |                                                                               | DC/DC boost / bypass threshold = 3.15V (Vsel = L) |  |  |  |  |  |

| TPS61281    | Simple Logic Control Interface                                                | DC/DC boost / bypass threshold = 3.35V (Vsel = H) |  |  |  |  |  |

|             |                                                                               | Valley inductor current limit = 3A                |  |  |  |  |  |

|             |                                                                               | DC/DC boost / bypass threshold = 3.3V (Vsel = L)  |  |  |  |  |  |

| TPS61282    | Simple Logic Control Interface                                                | DC/DC boost / bypass threshold = 3.5V (Vsel = H)  |  |  |  |  |  |

|             |                                                                               | Valley inductor current limit = 4A                |  |  |  |  |  |

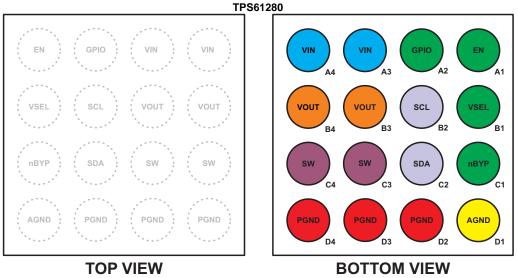

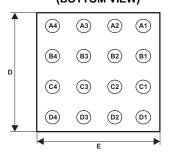

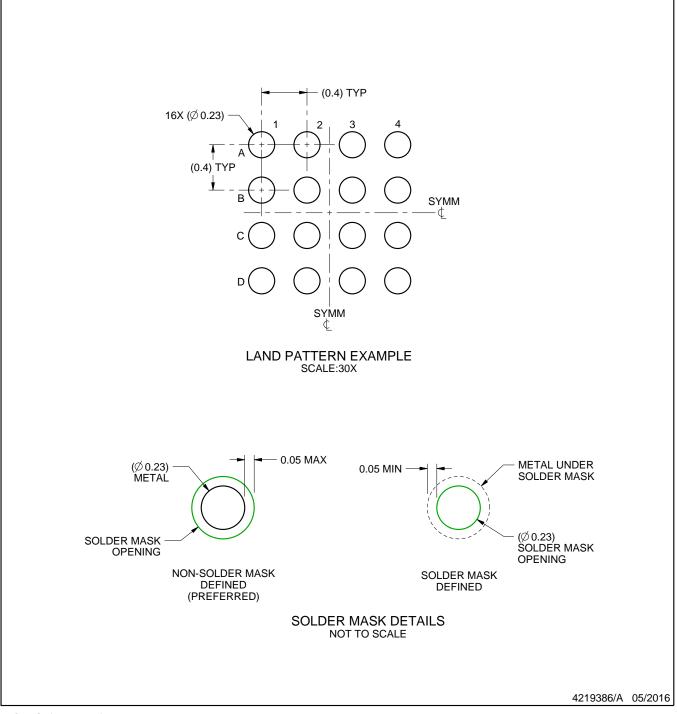

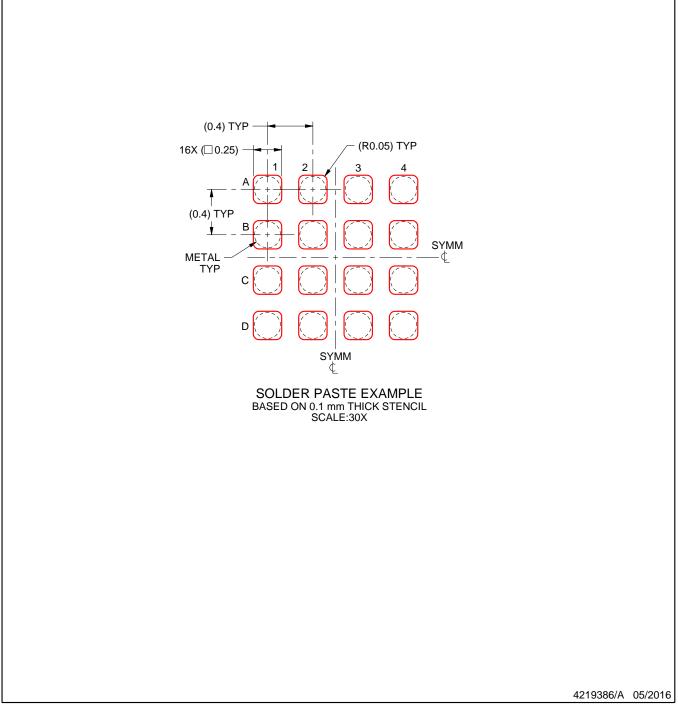

## 8 Pin Configuration and Functions

## **TOP VIEW**

|  |  | U |  |  |

|--|--|---|--|--|

|  |  |   |  |  |

|  |  |   |  |  |

### Pin Functions - TPS61280

|      | PIN        |     | DECODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO.        | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VIN  | A3, A4     | I   | Power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| VOUT | B3, B4     | 0   | Boost converter output.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EN   |            |     | This is the enable pin of the device. On the rising edge of the enable pin, all the registers are reset with their default values. This input must not be left floating and must be terminated.                                                                                                                                                                                                                                            |

|      | A1         | I   | $EN = Low$ : The device is forced into shutdown mode and the I2C control interface is disabled. Depending on the logic level applied to the nBYP input, the converter can either be forced in pass-through mode or it's output can be regulated to a minimum level so as to limit the input-to-output voltage difference to less than 3.6V (typ). The current consumption is reduced to a few $\mu$ A. For more details, refer to Table 2. |

|      |            |     | EN = High: The device is operating normally featuring automatic dc/dc boost, pass-through mode transition. For more details, refer to Table 2.                                                                                                                                                                                                                                                                                             |

|      |            |     | This pin can either be configured as a input (mode selection) or as dual role input/open-drain output (nRST/nFAULT) pin. Per default, the pin is configured as nRST/nFAULT input/output. The input must not be left floating and must be terminated.                                                                                                                                                                                       |

|      |            |     | Manual Reset Input: Drive nRST/nFAULT low to initiate a reset of the converter's output. nRST/nFAULT controls a falling edge-triggered sequence consisting of a discharge phase of the capacitance located at the converter's output followed by a start-up phase.                                                                                                                                                                         |

| GPIO | A2         | I/O | Fault Output (open-drain interrupt signal to host): Indicates that a fault has occurred (e.g. thermal shutdown, output voltage out of limits, current limit triggered, and so on). To signal such an event, the device generates a falling edge-triggered interrupt by driving a negative pulse onto the GPIO line and then releases the line to its inactive state.                                                                       |

|      |            |     | Mode selection input = Low: The device is operating in regulated frequency pulse width modulation mode (PWM) at high-load currents and in pulse frequency modulation mode (PFM) at light load currents.                                                                                                                                                                                                                                    |

|      |            |     | Mode selection input = High: Low-noise mode enabled, regulated frequency PWM operation forced.                                                                                                                                                                                                                                                                                                                                             |

| VSEL | B1         | I   | VSEL signal is primarily used to set the output voltage dc/dc boost, pass-through threshold. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                    |

| nBYP | C1         | I   | A logic low level on the nBYP input forces the device in pass-through mode. For more details, refer to <i>Table 2</i> . This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                         |

| SCL  | B2         | I   | Serial interface clock line. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                                                                                    |

| SDA  | C2         | I/O | Serial interface address/data line. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                                                                             |

| SW   | C3, C4     | I/O | Inductor connection. Drain of the internal power MOSFET. Connect to the switched side of the inductor.                                                                                                                                                                                                                                                                                                                                     |

| PGND | D2, D3, D4 |     | Power ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AGND | D1         |     | Analog ground pin. This is the signal ground reference for the IC.                                                                                                                                                                                                                                                                                                                                                                         |

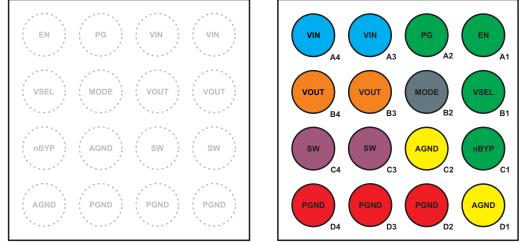

## TPS6128x

## **TOP VIEW**

### Pin Functions - TPS6128x

| PIN  |            |      |                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO.        | I/O  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                   |

| VIN  | A3, A4     | Ι    | Power supply input.                                                                                                                                                                                                                                                                                                                                                                           |

| VOUT | B3, B4     | 0    | Boost converter output.                                                                                                                                                                                                                                                                                                                                                                       |

|      |            |      | This is the enable pin of the device. On the rising edge of the enable pin, all the registers are reset with their default values. This input must not be left floating and must be terminated.                                                                                                                                                                                               |

| EN   | A1         | Ι    | EN = Low: The device is forced into shutdown mode. Depending on the logic level applied to the nBYP input, the converter can either be forced in pass-through mode or it's output can be regulated to a minimum level so as to limit the input-to-output voltage difference to less than 3.6V (typ). The current consumption is reduced to a few $\mu$ A. For more details, refer to Table 2. |

|      |            |      | EN = High: The device is operating normally featuring automatic dc/dc boost, pass-through mode transition. For more details, refer to Table 2.                                                                                                                                                                                                                                                |

| PG   | A2         | 0    | Power-Good Output (open-drain output to host): A logic high on the PG output indicates that the converter's output voltage is within its regulation limits. A logic low indicates a fault has occurred (e.g. thermal shutdown, output voltage out of limits, current limit triggered etc). The PG signal is de-asserted automatically once the IC resumes proper operation.                   |

| VSEL | B1         | Η    | VSEL signal is primarily used to set the output voltage dc/dc boost, pass-through threshold. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                       |

| nBYP | C1         | Ι    | A logic low level on the nBYP input forces the device in pass-through mode. For more details, refer to <i>Table 2</i> . This pin must not be left floating and must be terminated.                                                                                                                                                                                                            |

|      |            |      | This is the mode selection pin of the device. This pin must not be left floating, must be terminated and can be connected to AGND. During start-up this pin must be held low. Once the output voltage settled and PG pin indicates that the converter's output voltage is within its regulation limits the device can be forced in PWM mode operation by applying a high level on this pin.   |

| MODE | B2         | B2 I | MODE = Low: The device is operating in regulated frequency pulse width modulation mode (PWM) at high-load currents and in pulse frequency modulation mode (PFM) at light load currents. This pin must be held low during device start-up.                                                                                                                                                     |

|      |            |      | MODE = High: Low-noise mode enabled, regulated frequency PWM operation forced.                                                                                                                                                                                                                                                                                                                |

| SW   | C3, C4     | I/O  | Inductor connection. Drain of the internal power MOSFET. Connect to the switched side of the inductor.                                                                                                                                                                                                                                                                                        |

| PGND | D2, D3, D4 |      | Power ground pin.                                                                                                                                                                                                                                                                                                                                                                             |

| AGND | C2, D1     |      | Analog ground pin. This is the signal ground reference for the IC.                                                                                                                                                                                                                                                                                                                            |

## 9 Specifications

### 9.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                                                                                                                                         |                                       | MAX       | MIN       | UNIT |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------|-----------|------|

|                   | Voltage at VOUT <sup>(2)</sup>                                                                                                          | DC                                    | -0.3      | 4.7       | V    |

|                   | Voltage at VIN <sup>(2)</sup> , EN <sup>(2)</sup> , VSEL <sup>(2)</sup> , nBYP <sup>(2)</sup> , PG <sup>(2)</sup> , GPIO <sup>(2)</sup> | DC                                    | -0.3      | 5.2       | V    |

| Input voltage     | Voltage at VIN <sup>(2)</sup>                                                                                                           | Transient: 0.01% duty cycle operation | -0.3      | 5.5       | V    |

| input voltage     | Voltage at SCL <sup>(2)</sup> , SDA <sup>(2)</sup> MODE <sup>(2)</sup>                                                                  | DC                                    | -0.3      | 3.6       | V    |

|                   | Voltage at SW <sup>(2)</sup>                                                                                                            | DC                                    | -0.3      | 4.7       | V    |

|                   |                                                                                                                                         | Transient: 2 ns, 2.3 MHz              | -0.3      | 5.5       | V    |

|                   | Differential voltage between VIN and VOUT                                                                                               | DC                                    | -0.3      | 4         | V    |

| Input ourroat     | Continuous average current into SW (3)                                                                                                  |                                       | 1.8       | А         | А    |

| Input current     | Peak current into SW <sup>(4)</sup>                                                                                                     |                                       | 5.5       | А         | Α    |

| Power dissipation | ·                                                                                                                                       |                                       | Internall | y limited |      |

| Tomporature range | Operating temperature range, T <sub>A</sub> <sup>(5)</sup>                                                                              |                                       | -40       | 85        | °C   |

| Temperature range | Operating virtual junction, T <sub>J</sub>                                                                                              |                                       | -40       | 150       | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to network ground terminal.

(3) Limit the junction temperature to 105°C for continuous operation at maximum output power.

(4) Limit the junction temperature to 105°C for 15% duty cycle operation.

(5) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A(max)})$  is dependent on the maximum operating junction temperature  $(T_{J(max)})$ , the maximum power dissipation of the device in the application  $(P_{D(max)})$ , and the junction-to-ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A(max)} = T_{J(max)} - (\theta_{JA} \times P_{D(max)})$ . To achieve optimum performance, it is recommended to operate the device with a maximum junction temperature of 105°C.

### 9.2 Handling Ratings

|                  |                           |                                                                                          | MIN   | MAX  | UNIT |

|------------------|---------------------------|------------------------------------------------------------------------------------------|-------|------|------|

| T <sub>stg</sub> | Storage temperature range |                                                                                          | -65   | 150  | °C   |

|                  |                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | -2000 | 2000 | V    |

| V <sub>ESD</sub> | Electrostatic discharge   | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -1000 | 1000 | V    |

|                  |                           | Machine Model (MM)                                                                       | -200  | 200  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 9.3 Recommended Operating Conditions

|                |                                                                                      | MIN  | NOM | MAX  | UNIT |

|----------------|--------------------------------------------------------------------------------------|------|-----|------|------|

| V              | Input voltage range                                                                  | 2.30 |     | 4.85 | V    |

| VI             | Input voltage range for in-situ customization by E <sup>2</sup> PROM write operation | 3.4  | 3.5 | 3.6  | V    |

| L              | Inductance                                                                           | 200  | 470 | 800  | nH   |

| Co             | Output capacitance                                                                   | 9    | 13  | 100  | μF   |

| ΙL             | Maximum load current during start-up                                                 | 250  |     |      | mA   |

| T <sub>A</sub> | Ambient temperature                                                                  | -40  |     | 85   | °C   |

| TJ             | Operating junction temperature                                                       | -40  |     | 125  | °C   |

## 9.4 Thermal Information

|                     | THERMAL METRIC <sup>(1)</sup>                | TPS6128x      | UNIT |

|---------------------|----------------------------------------------|---------------|------|

|                     |                                              | YFF (16 PINS) | UNIT |

| $R_{\theta JA}$     | Junction-to-ambient thermal resistance       | 78            |      |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 0.6           |      |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 13            | °C/W |

| Ψ <sub>JT</sub>     | Junction-to-top characterization parameter   | 2.4           | °C/w |

| Ψ <sub>JB</sub>     | Junction-to-board characterization parameter | 13            |      |

| $R_{\theta JCbot}$  | Junction-to-case (bottom) thermal resistance | n/a           |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 9.5 Electrical Characteristics

Minimum and maximum values are at  $V_{IN} = 2.3V$  to 4.85V,  $V_{OUT} = 3.4V$  (or  $V_{IN}$ , whichever is higher), EN = 1.8V, VSEL = 1.8V, nBYP = 1.8V, -40°C ≤ T<sub>J</sub> ≤ 125°C; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are at  $V_{IN} = 3.2V$ ,  $V_{OUT} = 3.4V$ , EN = 1.8V,  $T_J = 25°C$  (unless otherwise noted).

| PARAMETER         |                                                     |           | TEST CONDITIONS                                                                            |                                  | MIN | TYP                        | MAX | UNIT |

|-------------------|-----------------------------------------------------|-----------|--------------------------------------------------------------------------------------------|----------------------------------|-----|----------------------------|-----|------|

| SUPPLY            | CURRENT                                             |           |                                                                                            | ι.                               |     | · · ·                      |     |      |

|                   |                                                     |           | DC/DC boost mode. Device not switching, $I_{OUT}$ = 0mA, $V_{IN}$ = 3.2V, $V_{OUT}$ = 3.4V |                                  |     | 47                         | 65  | μA   |

| Iα                | Operating quiescent current into ${\rm V}_{\rm IN}$ | TPS6128x  | Pass-through mode (auto)<br>EN = 1.8V, nBYP = 1.8V,<br>$V_{IN}$ = 3.6V                     |                                  |     | 27                         | 42  | μΑ   |

|                   |                                                     | 12301288  | Pass-through mode (forced)<br>EN = 1.8V, nBYP = AGND,<br>V <sub>OUT</sub> = 3.6V           | –40°C ≤ T <sub>J</sub> ≤<br>85°C |     | 15                         | 25  | μΑ   |

|                   | Operating quiescent current into $V_{\text{OUT}}$   |           | DC/DC boost mode. Device not switching, $I_{OUT}$ = 0mA, $V_{IN}$ = 3.2V, $V_{OUT}$ = 3.4V |                                  |     | 8.5                        | 19  | μΑ   |

|                   | Shutdown current                                    | TPS6128x  | $EN = 0V$ , $nBYP = 0V$ , $V_{IN} = 3.6V$                                                  |                                  |     | 2.6                        | 6   | μA   |

| I <sub>SD</sub>   | Shudown current                                     | 19301200  | $EN = 0V$ , $nBYP = 1.8V$ , $V_{IN} = 3.6V$                                                |                                  |     | 8.5                        | 20  | μA   |

| V                 |                                                     | TD00100v  | Falling                                                                                    |                                  |     | 2.0                        | 2.1 | V    |

| V <sub>UVLO</sub> | Under-voltage lockout threshold                     | TPS6128x  | Hysteresis                                                                                 |                                  |     | 0.1                        |     | V    |

| EN, VSE           | EL, nBYP, MODE, SDA, SCL, GPIO, P                   | G         |                                                                                            |                                  |     |                            |     |      |

| V <sub>IL</sub>   | Low-level input voltage                             | TPS6128x  |                                                                                            |                                  |     |                            | 0.4 | V    |

| V <sub>IH</sub>   | High-level input voltage                            | 11-201208 |                                                                                            |                                  | 1.2 |                            |     | V    |

|                   | Low-level output voltage (SDA)                      | TPS61280  | I <sub>OL</sub> = 8mA                                                                      |                                  |     |                            | 0.3 | V    |

| V <sub>OL</sub>   | Low-level output voltage (GPIO)                     | 1F 301200 | $I_{OL} = 8mA, GPIOCFG = 0$                                                                |                                  |     |                            | 0.3 | V    |

|                   | Low-level output voltage (PG)                       | TPS6128x  | I <sub>OL</sub> = 8mA                                                                      |                                  |     |                            | 0.3 | V    |

| R <sub>PD</sub>   | EN, VSEL, nBYP, pull-down resistance                | TPS6128x  | Input ≤ 0.4 V                                                                              |                                  |     | 300                        |     | kΩ   |

| C <sub>IN</sub>   | EN, VSEL, nBYP, MODE, PG input capacitance          | TPS6128x  | Input connected to AGND or $V_{IN}$                                                        |                                  |     | 9                          |     | pF   |

|                   | SDA, SCL, GPIO input capacitance                    | TPS61280  |                                                                                            |                                  |     | 9                          |     | pF   |

| V <sub>THPG</sub> | Power good threshold                                | TPS6128x  | Rising V <sub>OUT</sub>                                                                    |                                  |     | 0.95 х<br>V <sub>OUT</sub> |     |      |

| ▼ THPG            |                                                     | 11-301208 | Falling V <sub>OUT</sub>                                                                   |                                  |     | 0.9 x<br>V <sub>OUT</sub>  |     |      |

| l <sub>lkg</sub>  | Input leakage current                               | TPS6128x  | Input connected to AGND                                                                    | –40°C ≤ T <sub>J</sub> ≤         |     | 0                          |     | μA   |

|                   | input leakage current                               | 1730128X  | Input connected V <sub>IN</sub>                                                            | 85°C                             |     |                            | 0.5 | μA   |

## **Electrical Characteristics (continued)**

Minimum and maximum values are at  $V_{IN} = 2.3V$  to 4.85V,  $V_{OUT} = 3.4V$  (or  $V_{IN}$ , whichever is higher), EN = 1.8V, VSEL = 1.8V, nBYP = 1.8V, -40°C ≤ T<sub>J</sub> ≤ 125°C; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are at  $V_{IN} = 3.2V$ ,  $V_{OUT} = 3.4V$ , EN = 1.8V,  $T_J = 25°C$  (unless otherwise noted).

| PARAMETER            |                                                         |                      | TEST CONDITIONS                                                                                                                                                   | MIN   | TYP       | MAX   | UNIT |

|----------------------|---------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|------|

| OUTPUT               | г                                                       |                      |                                                                                                                                                                   |       |           |       |      |

| V <sub>OUT(TH)</sub> | Threshold DC voltage accuracy                           | TPS6128x             | No load. Open loop                                                                                                                                                | -1.5% |           | +1.5% |      |

|                      |                                                         | TROOTOOL             | $ \begin{array}{l} 2.65V \leq V_{\text{IN}} \leq V_{\text{OUT\_TH}} \text{ - } 150\text{mV} \\ I_{\text{OUT}} = 0\text{mA} \\ \text{PWM operation.} \end{array} $ | -2%   |           | +2%   |      |

| V <sub>OUT</sub>     | Regulated DC voltage accuracy                           | TPS6128x             | $ \begin{array}{l} 2.65V \leq V_{IN} \leq V_{OUT_TH} \text{ - } 150mV \\ I_{OUT} = 0mA \\ \text{PFM/PWM operation} \end{array} $                                  | -2%   |           | +4%   |      |

| ΔV <sub>OUT</sub>    | Power-save mode<br>output ripple voltage                | TPS6128x             | PFM operation, I <sub>OUT</sub> = 1mA                                                                                                                             |       | 30        |       | mVpk |

|                      | PWM mode output ripple voltage                          |                      | PWM operation, $I_{OUT} = 500$ mA                                                                                                                                 |       | 15        |       | mVpk |

| POWER                | SWITCH                                                  |                      |                                                                                                                                                                   |       |           |       |      |

|                      | Low-side switch MOSFET<br>on resistance                 |                      | V <sub>IN</sub> = 3.2, V <sub>OUT</sub> = 3.5V                                                                                                                    |       | 45        | 80    | mΩ   |

| r <sub>DS(on)</sub>  | High-side rectifier MOSFET<br>on resistance             | TPS6128x             | V <sub>IN</sub> = 3.2V, V <sub>OUT</sub> = 3.5V                                                                                                                   |       | 40        | 70    | mΩ   |

|                      | High-side pass-through MOSFET on resistance             |                      | V <sub>IN</sub> = 3.2V, V <sub>OUT</sub> = 3.5V                                                                                                                   |       | 35        | 60    | mΩ   |

|                      | Reverse leakage current into SW                         |                      | $      EN = AGND, V_{IN} = V_{OUT} = SW = 3.5V \\ -40^\circ C \le T_J \le 85^\circ C $                                                                            |       | 0.1       | 2     | μA   |

| l <sub>lkg</sub>     | Reverse leakage current into VOUT                       | TPS6128x             | $\label{eq:states} \begin{array}{l} EN=nBYP=VIN,V_{IN}=2.9V,V_{OUT}=4.4V,V_{SW}=0V\\ \text{device not switching}\\ -40^\circC\leqT_J\leq85^\circC \end{array}$    |       | 0.11      | 2     | μA   |

| I <sub>SINK</sub>    | VOUT sink capability                                    | TPS6128x             | $EN = AGND, V_{OUT} \le 3.6V, I_{OUT} = -10mA$                                                                                                                    |       | · · · · · | 0.3   | V    |

|                      | Valley inductor current limit                           | TPS61280<br>TPS61281 | $V_{\rm IN}$ = 2.9V, $V_{\rm OUT}$ = 3.5V, –40°C $\leq$ T_J $\leq$ 125°C, auto PFM/PWM                                                                            | 2475  | 3000      | 3525  | mA   |

|                      | Valley inductor current limit                           | TPS61282             | $V_{\rm IN}$ = 2.9V, $V_{OUT}$ = 3.5V, –40°C $\leq$ T_J $\leq$ 125°C, auto PFM/PWM                                                                                | 3300  | 4000      | 4700  | mA   |

|                      | Deep through mode surrent limit                         | TPS6128x             | $EN = nBYP = GND, V_{IN} = 3.2V$                                                                                                                                  |       | 5000      |       | mA   |

|                      | Pass through mode current limit                         | 19301200             | $EN = VIN$ , nBYP = don't care , $V_{IN} = 3.2V$                                                                                                                  | 5600  | 7400      | 9100  | mA   |

|                      | Pre-charge mode current limit<br>(linear mode, phase 1) | TDOOLOG              | V V > 200-V                                                                                                                                                       | 500   | 650       |       | mA   |

|                      | Pre-charge mode current limit<br>(linear mode, phase 2) |                      | V <sub>IN</sub> - V <sub>OUT</sub> ≥ 300mV                                                                                                                        |       | 2000      |       | mA   |

| OSCILL               | ATOR                                                    |                      |                                                                                                                                                                   |       |           |       |      |

| f <sub>osc</sub>     | Oscillator frequency                                    | TPS6128x             | V <sub>IN</sub> = 2.7V, V <sub>OUT</sub> = 3.5                                                                                                                    |       | 2.3       |       | MHz  |

| THERM                | AL SHUTDOWN, HOT DIE DETECTOF                           | R                    |                                                                                                                                                                   |       |           | 1     |      |

|                      | Thermal shutdown <sup>(1)</sup>                         | TPS6128x             |                                                                                                                                                                   | 140   | 160       |       | °C   |

|                      | Hot die detector accuracy <sup>(1)</sup>                | TPS61280             |                                                                                                                                                                   | -10   | 105       | +10   | °C   |

(1) Verified by characterization. Not tested in production.

## 9.6 Timing Requirements

|                               |          |                                                                                                                                                                                                        | MIN | TYP | MAX | UNIT |

|-------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

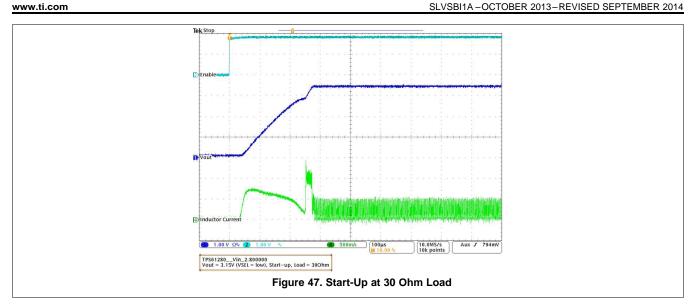

| Start-up time                 | TPS6128x | $ \begin{array}{l} V_{\text{IN}}=3.2V, \ VOUT\_TH=01011\\ (3.4V), \ R_{\text{LOAD}}=50\Omega\\ \\ \text{Time from active } V_{\text{IN}} \ \text{to } V_{\text{OUT}}\\ \\ \text{settled} \end{array} $ |     | 500 |     | μs   |

| GPIO rise time <sup>(1)</sup> | TPS61280 |                                                                                                                                                                                                        |     |     | 200 | ns   |

(1) Specified by characterization. Not tested in production.

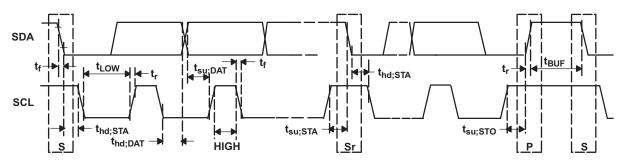

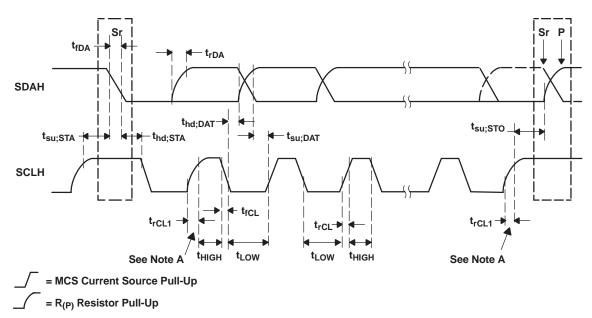

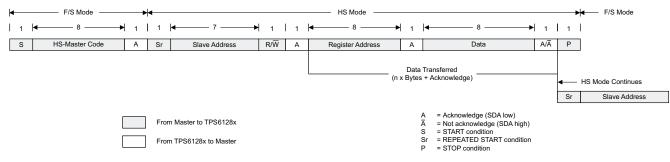

## 9.7 I<sup>2</sup>C Interface Timing Characteristics<sup>(1)</sup>

|                                      | PARAMETER                                        | TEST CONDITIONS                                                | MIN | MAX  | UNIT |

|--------------------------------------|--------------------------------------------------|----------------------------------------------------------------|-----|------|------|

|                                      |                                                  | Standard mode                                                  |     | 100  | kHz  |

| -                                    |                                                  | Fast mode                                                      |     | 400  | kHz  |

|                                      |                                                  | Fast mode plus                                                 |     | 1    | MHz  |

| f <sub>(SCL)</sub>                   | SCL Clock Frequency                              | High-speed mode (write operation), C <sub>B</sub> – 100 pF max |     | 3.4  | MHz  |

|                                      |                                                  | High-speed mode (read operation), C <sub>B</sub> – 100 pF max  |     | 3.4  | MHz  |

|                                      |                                                  | High-speed mode (write operation), C <sub>B</sub> – 400 pF max |     | 1.7  | MHz  |

|                                      |                                                  | High-speed mode (read operation), C <sub>B</sub> – 400 pF max  |     | 1.7  | MHz  |

|                                      |                                                  | Standard mode                                                  | 4.7 |      | μs   |

| t <sub>BUF</sub>                     | Bus Free Time Between a STOP and START Condition | Fast mode                                                      | 1.3 |      | μs   |

|                                      |                                                  | Fast mode plus                                                 | 0.5 |      | μs   |

|                                      |                                                  | Standard mode                                                  | 4   |      | μs   |

|                                      | Hold Time (Repeated) START                       | Fast mode                                                      | 600 |      | ns   |

| t <sub>HD</sub> , t <sub>STA</sub> C | Condition                                        | Fast mode plus                                                 | 260 |      | ns   |

|                                      |                                                  | High-speed mode                                                | 160 |      | ns   |

|                                      | Standard mode                                    | 4.7                                                            |     | μs   |      |

|                                      |                                                  | Fast mode                                                      | 1.3 |      | μs   |

| t <sub>LOW</sub>                     | LOW Period of the SCL Clock                      | Fast mode plus                                                 | 0.5 |      | μs   |

|                                      |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                   | 160 |      | ns   |

|                                      |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                   | 320 |      | ns   |

|                                      |                                                  | Standard mode                                                  | 4   |      | μs   |

|                                      |                                                  | Fast mode                                                      | 600 |      | ns   |

| t <sub>HIGH</sub>                    | HIGH Period of the SCL Clock                     | Fast mode plus                                                 | 260 |      | ns   |

|                                      |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                   | 60  |      | ns   |

|                                      |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                   | 120 |      | ns   |

|                                      |                                                  | Standard mode                                                  | 4.7 |      | μs   |

|                                      | Setup Time for a Repeated START                  | Fast mode                                                      | 600 |      | ns   |

| ISU, ISTA                            | Condition                                        | Fast mode plus                                                 | 260 |      | ns   |

|                                      |                                                  | High-speed mode                                                | 160 |      | ns   |

|                                      |                                                  | Standard mode                                                  | 250 |      | ns   |

|                                      |                                                  | Fast mode                                                      | 100 |      | ns   |

| t <sub>SU</sub> , t <sub>DAT</sub>   | Data Setup Time                                  | Fast mode plus                                                 | 50  |      | ns   |

|                                      |                                                  | High-speed mode                                                | 10  |      | ns   |

|                                      |                                                  | Standard mode                                                  | 0   | 3.45 | μs   |

|                                      |                                                  | Fast mode                                                      | 0   | 0.9  | μs   |

| t <sub>HD</sub> , t <sub>DAT</sub>   | Data Hold Time                                   | Fast mode plus                                                 | 0   |      | μs   |

|                                      |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                   | 0   | 70   | ns   |

|                                      |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                   | 0   | 150  | ns   |

(1) Specified by design. Not tested in production.

### TPS61280, TPS61281, TPS61282 SLVSBI1A-OCTOBER 2013-REVISED SEPTEMBER 2014

www.ti.com

STRUMENTS

ÈXAS

## I<sup>2</sup>C Interface Timing Characteristics<sup>(1)</sup> (continued)

|                                   | PARAMETER                          | TEST CONDITIONS                              | MIN                     | MAX  | UNIT |

|-----------------------------------|------------------------------------|----------------------------------------------|-------------------------|------|------|

|                                   |                                    | Standard mode                                |                         | 1000 | ns   |

|                                   |                                    | Fast mode                                    | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RCL</sub> Rise T           | Rise Time of SCL Signal            | Fast mode plus                               |                         | 120  | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 100 pF max | 10                      | 40   | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 400 pF max | 20                      | 80   | ns   |

|                                   |                                    | Standard mode                                | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

|                                   | Rise Time of SCL Signal After a    | Fast mode                                    | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| RCL1                              | Repeated START Condition and After | Fast mode plus                               |                         | 120  | ns   |

|                                   | an Acknowledge BIT                 | High-speed mode, C <sub>B</sub> – 100 pF max | 10                      | 80   | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 400 pF max | 20                      | 160  | ns   |

|                                   |                                    | Standard mode                                | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

|                                   |                                    | Fast mode                                    |                         | 300  | ns   |

| t <sub>FCL</sub> I                | Fall Time of SCL Signal            | Fast mode plus                               |                         | 120  | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 100 pF max | 10                      | 40   | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 400 pF max | 20                      | 80   | ns   |

|                                   |                                    | Standard mode                                |                         | 1000 | ns   |

|                                   |                                    | Fast mode                                    | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RDA</sub>                  | Rise Time of SDA Signal            | Fast mode plus                               |                         | 120  | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 100 pF max | 10                      | 80   | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 400 pF max | 20                      | 160  | ns   |

|                                   |                                    | Standard mode                                |                         | 300  | ns   |

|                                   |                                    | Fast mode                                    | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| FDA                               | Fall Time of SDA Signal            | Fast mode plus                               |                         | 120  | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 100 pF max | 10                      | 80   | ns   |

|                                   |                                    | High-speed mode, C <sub>B</sub> – 400 pF max | 20                      | 160  | ns   |

|                                   |                                    | Standard mode                                | 4                       |      | μs   |

|                                   |                                    | Fast mode                                    | 600                     |      | ns   |

| t <sub>SU,</sub> t <sub>STO</sub> | Setup Time of STOP Condition       | Fast mode plus                               | 260                     |      | ns   |

|                                   |                                    | High-Speed mode                              | 160                     |      | ns   |

|                                   |                                    | Standard mode                                |                         | 400  | pF   |

| 2                                 |                                    | Fast mode                                    |                         | 400  | pF   |

| CB                                | Capacitive Load for SDA and SCL    | Fast mode plus                               |                         | 550  | pF   |

|                                   |                                    | High-Speed mode                              |                         | 400  | pF   |

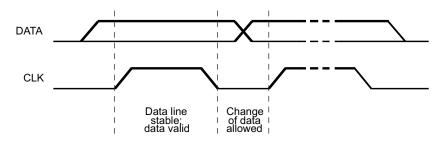

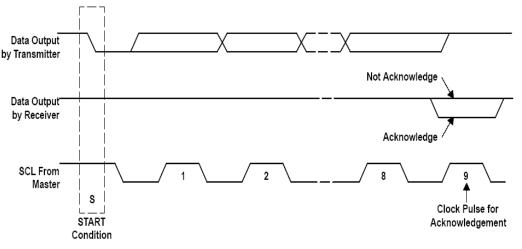

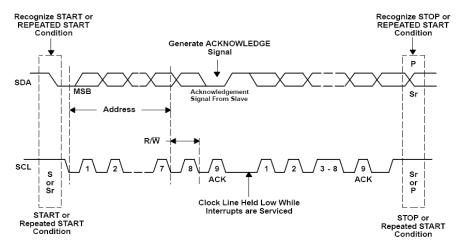

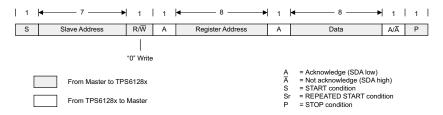

Figure 1. Serial Interface Timing Diagram for Standard-, Fast-, Fast-Mode Plus

Note A: First rising edge of the SCLH signal after Sr and after each acknowledge bit.

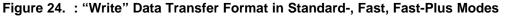

Figure 2. Serial Interface Timing Diagram for H/S-Mode

#### **TPS61280, TPS61281, TPS61282** SLVSBI1A – OCTOBER 2013 – REVISED SEPTEMBER 2014

www.ti.com

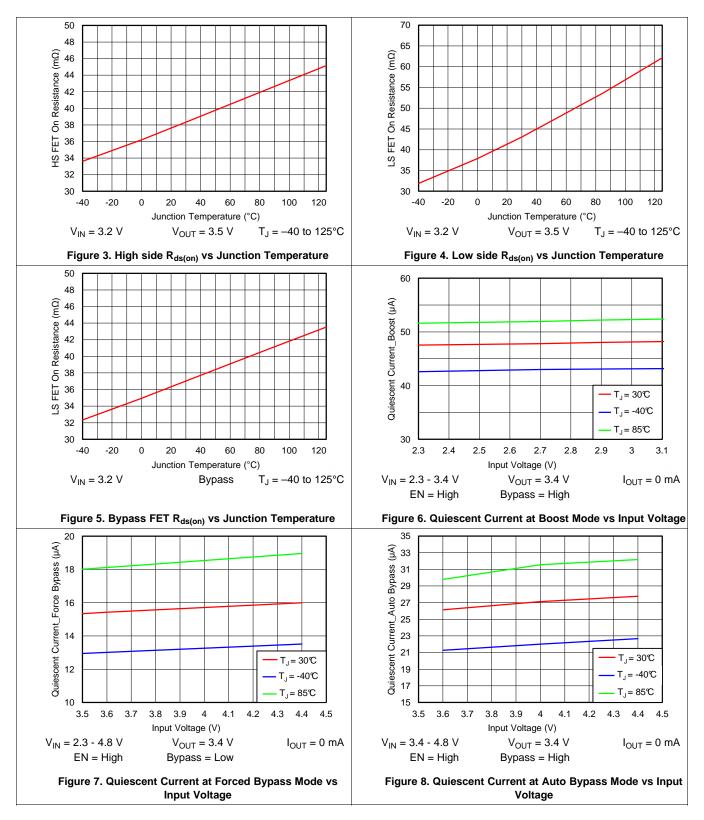

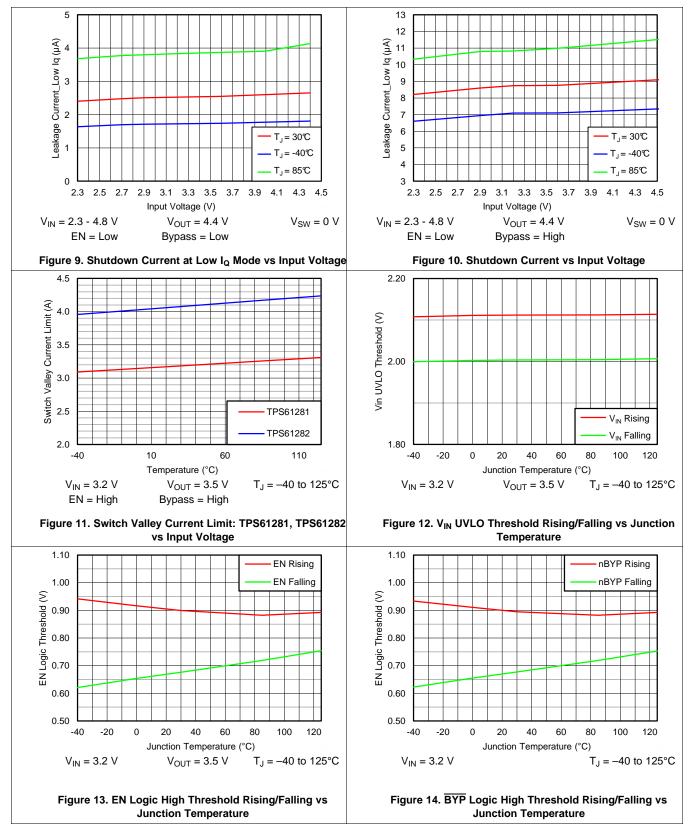

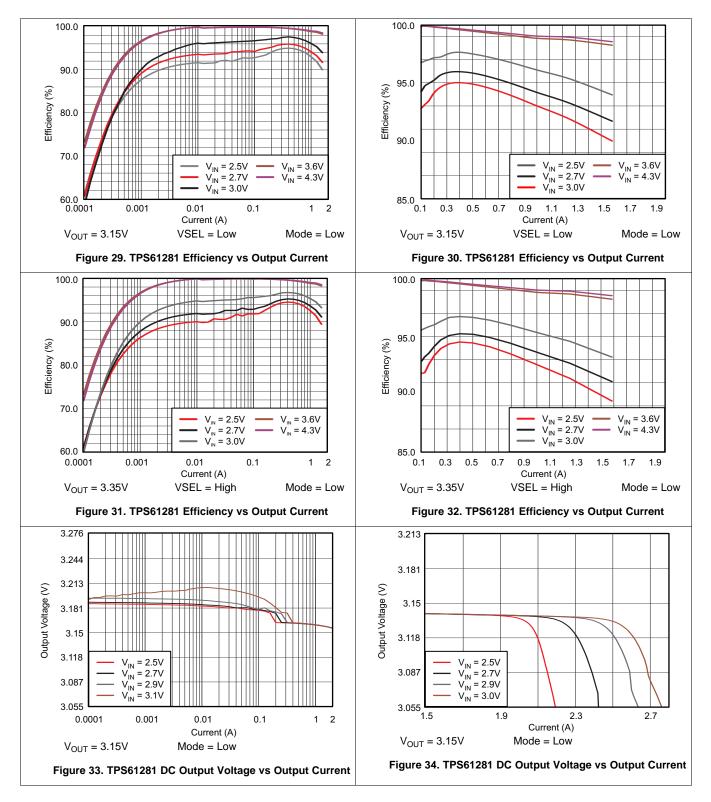

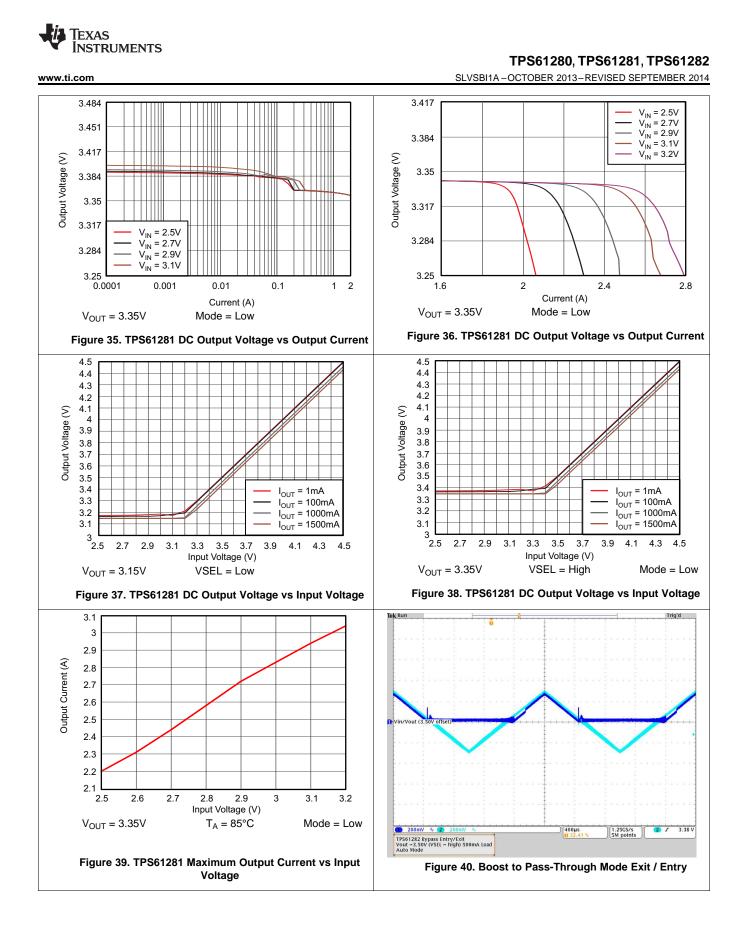

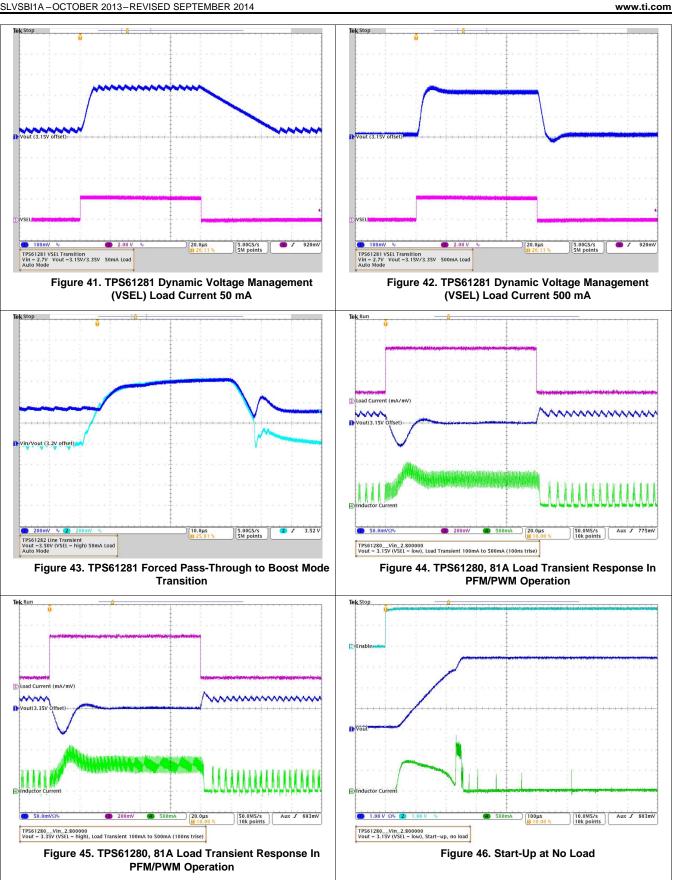

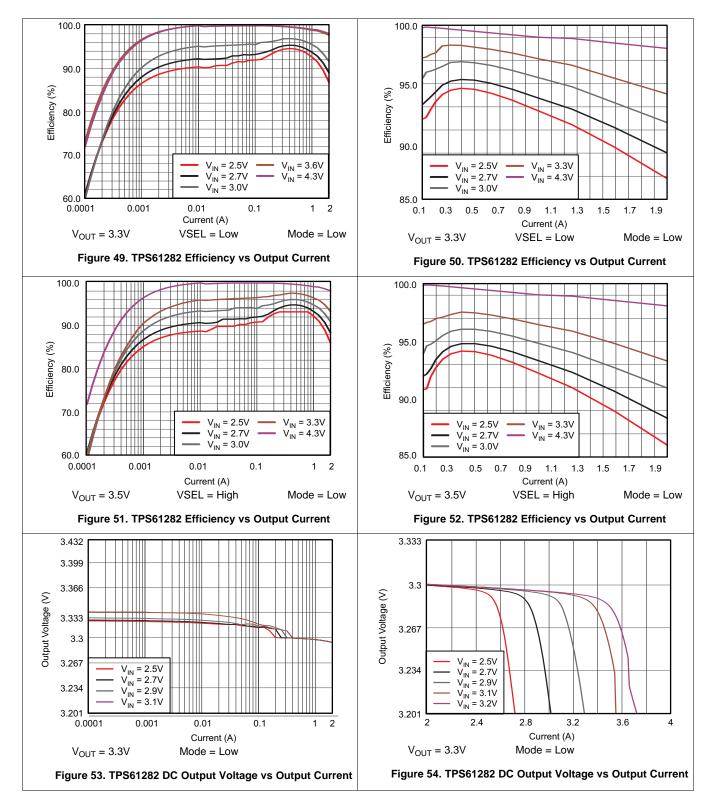

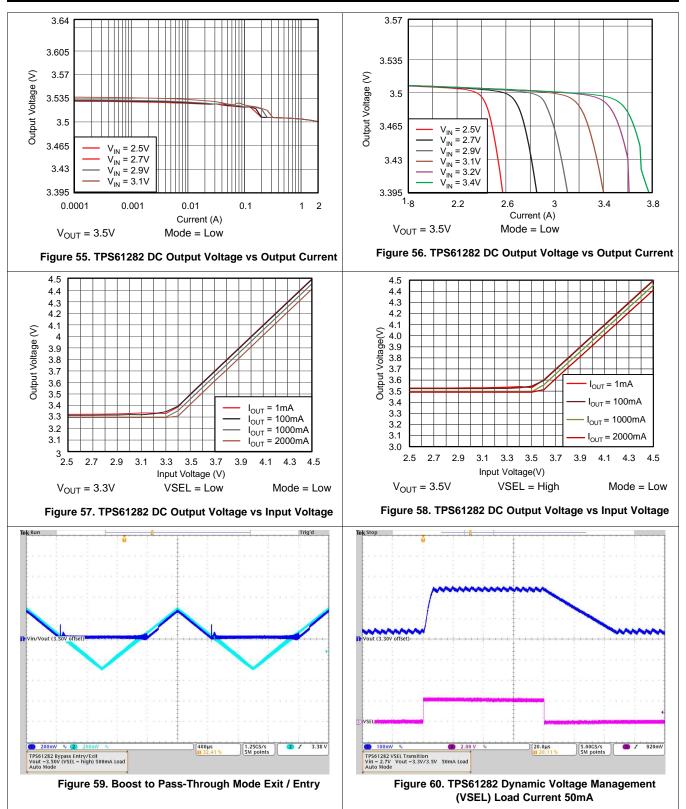

## 9.8 Typical Characteristics

### **Typical Characteristics (continued)**

TEXAS INSTRUMENTS

www.ti.com

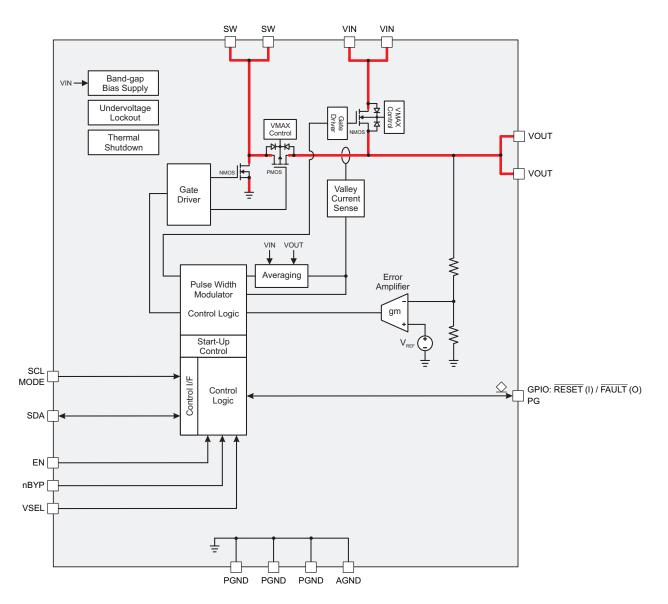

## **10** Detailed Description

### 10.1 Overview

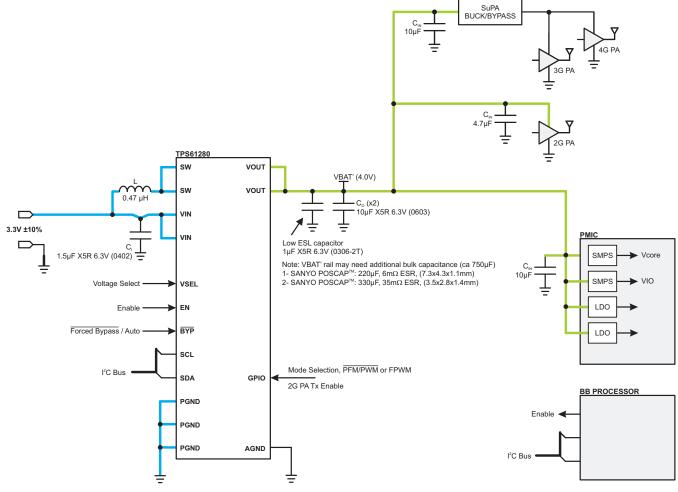

The TPS6128x is a high-efficiency step-up converter featuring pass-through mode optimized to provide low-noise voltage supply for 2G RF power amplifiers (PAs) in mobile phones and/or to pre-regulate voltage for supplying subsystem like eMMC memory, audio codec, LCD bias, antenna switches, RF engine PMIC etc. It is designed to allow the system to operate at maximum efficiency for a wide range of power consumption levels from a low-, wide- voltage battery cell.

The capability of the TPS6128x to step-up the voltage as well as to pass-through the input battery voltage when its level is high enough allow systems to operate at maximum performance over a wide range of battery voltages, thereby extending the battery life between charging. The device also addresses brownouts caused by the peak currents drawn by the APU and GPU which can cause the battery rail to droop momentarily. Using the TPS6128x device as a pre-regulator eliminates system brownout condition while maintaining a stable supply rail for critical sub-system to function properly.

The TPS6128x synchronous step-up converter typically operates at a quasi-constant 2.3-MHz frequency pulse width modulation (PWM) at moderate to heavy load currents. At light load currents, the TPS6128x converter operates in power-save mode with pulse frequency modulation (PFM).

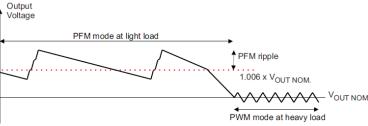

In general, a dc/dc step-up converter can only operate in "true" boost mode, i.e. the output "boosted" by a certain amount above the input voltage. The TPS6128x device operates differently as it can smoothly transition in and out of zero duty cycle operation. Depending upon the input voltage, output voltage threshold and load current, the integrated bypass switch automatically transitions the converter into pass-through mode to maintain low-dropout and high-efficiency. The device exits pass-through mode (0% duty cycle operation) if the total dropout resistance in bypass mode is insufficient to maintain the output voltage at it's nominal level. Refer to the typical characteristics section (DC Output Voltage vs. Input Voltage) for further details.

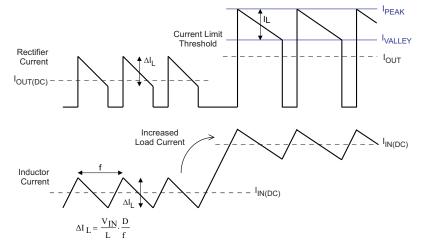

During PWM operation, the converter uses a novel quasi-constant on-time valley current mode control scheme to achieve excellent line/load regulation and allows the use of a small ceramic inductor and capacitors. Based on the  $V_{IN}/V_{OUT}$  ratio, a simple circuit predicts the required on-time. At the beginning of the switching cycle, the low-side N-MOS switch is turned-on and the inductor current ramps up to a peak current that is defined by the on-time and the inductance. In the second phase, once the on-timer has expired, the rectifier is turned-on and the inductor current threshold. Finally, the switching cycle repeats by setting the on timer again and activating the low-side N-MOS switch.

The current mode architecture provides excellent transient load response, requiring minimal output filtering. Internal soft-start and loop compensation simplifies the design process while minimizing the number of external components.

The TPS6128x directly and accurately controls the average input current through intelligent adjustment of the valley current limit, allowing an accuracy of  $\pm 17.5\%$ . Together with an external bulk capacitor, the TPS6268x allows an application to be interfaced directly to its load, without overloading the input source due to appropriate set average input current limit. An open-drain output (PG or GPIO/nFAULT) provides a signal to issue an interrupt to the system if any fault is detected on the device (thermal shutdown, output voltage out-of limits etc ...).

The output voltage can be dynamically adjusted between two values (floor and roof voltages) by toggling a logic control input (VSEL) without the need for external feedback resistors. This features can either be used to raise the output voltage in anticipation of a positive load transient or to dynamically change the PA supply voltage depending on its mode of operation and/or transmitting power.

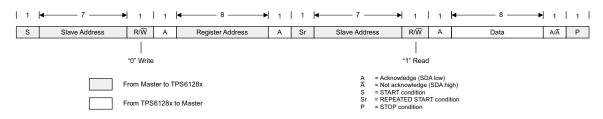

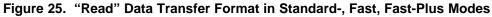

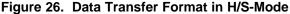

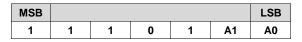

The TPS61280 integrates an I<sup>2</sup>C compatible interface allowing transfers up to 3.4Mbps. This communication interface can be used to set the output voltage threshold at which the converter transitions between boost and pass-through mode, for reprogramming the mode of operation (PFM/PWM or forced PWM), for settings the average input current limit or resetting the output voltage for instance.

Configuration parameters can be changed by writing the desired values to the appropriate  $I^2C$  register(s). The  $I^2C$  registers are volatile and their contents are lost when power is removed from the device. By writing to the *E2PROMCTRL Register*, it is possible to store the active configuration in non-volatile  $E^2PROM$ ; during power-up, the contents of the  $E^2PROM$  are copied into the  $I^2C$  registers and used to configure the device.

## 10.2 Functional Block Diagram

### **10.3 Feature Description**

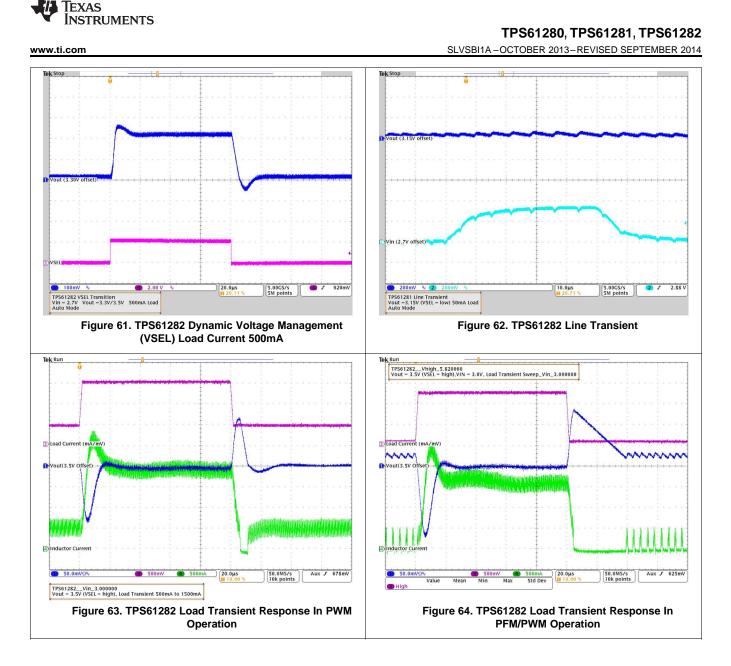

#### 10.3.1 Voltage Scaling Management (VSEL)

In order to maintain a certain minimum output voltage under heavy load transients, the output voltage set point can be dynamically increased by asserting the VSEL input. The functionality also helps to mitigate undershoot during severe line transients, while minimizing the output voltage during more benign operating conditions to save power.

The output voltage ramps up (floor to roof transition) at pre-defined rate defined by the average input current limit setting. The required time to ramp down the voltage (roof to floor transition) largely depends on the amount of capacitance present at the converter's output as well as on the load current. Table 1 shows the ramp rate control when transitioning to a lower voltage.

| Mode Associated with Floor Voltage | Output Voltage Ramp Rate                                                                                                               |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Forced PWM                         | Output capacitance is being discharged at a rate of approx. 50mA (or higher) constant current<br>in addition to the load current drawn |

| PFM                                | Output capacitance is being discharged (solely) by the load current drawn                                                              |

#### Table 1. Ramp Down Rate vs. Target Mode

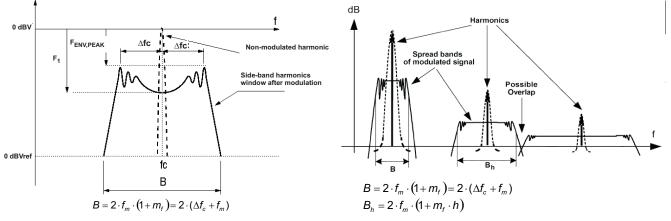

#### 10.3.2 Spread Spectrum, PWM Frequency dithering

The goal is to spread out the emitted RF energy over a larger frequency range so that the resulting EMI is similar to white noise. The end result is a spectrum that is continuous and lower in peak amplitude, making it easier to comply with electromagnetic interference (EMI) standards and with the power supply ripple requirements in cellular and non-cellular wireless applications. Radio receivers are typically susceptible to narrowband noise that is focused on specific frequencies.

Switching regulators can be particularly troublesome in applications where electromagnetic interference (EMI) is a concern. Switching regulators operate on a cycle-by-cycle basis to transfer power to an output. In most cases, the frequency of operation is either fixed or regulated, based on the output load. This method of conversion creates large components of noise at the frequency of operation (fundamental) and multiples of the operating frequency (harmonics).

The spread spectrum architecture varies the switching frequency by ca.  $\pm 15\%$  of the nominal switching frequency thereby significantly reducing the peak radiated and conducting noise on both the input and output supplies. The frequency dithering scheme is modulated with a triangle profile and a modulation frequency f<sub>m</sub>.

The above figures show that after modulation the sideband harmonic is attenuated compared to the nonmodulated harmonic, and the harmonic energy is spread into a certain frequency band. The higher the modulation index (*mf*) the larger the attenuation.

Spectrum illustrations and formulae (Figure 15 and Figure 16) copyright IEEE TRANSACTIONS ON ELECTROMAGNETIC COMPATIBILITY, VOL. 47, NO.3, AUGUST 2005.

(1)

$$m_f = \frac{\delta \times f_c}{f_m}$$

where

- $f_c$  is the carrier frequency (approx. 2.3MHz)

- $f_m$  is the modulating frequency (approx. 40kHz)

- $\delta$  is the modulation ratio (approx 0.15)

$$\delta = \frac{\Delta f_{\rm c}}{f_{\rm c}} \tag{2}$$

The maximum switching frequency  $f_c$  is limited by the process and finally the parameter modulation ratio ( $\delta$ ), together with  $f_m$ , which is the side-band harmonics bandwidth around the carrier frequency  $f_c$ . The bandwidth of a frequency modulated waveform is approximately given by the Carson's rule and can be summarized as:

$$\mathsf{B} = 2 \times f_{\mathsf{m}} \times (1 + \mathsf{m}_{f}) = 2 \times (\Delta f_{\mathsf{c}} + f_{\mathsf{m}})$$

(3)

$f_m$  < RBW: The receiver is not able to distinguish individual side-band harmonics, so, several harmonics are added in the input filter and the measured value is higher than expected in theoretical calculations.

$f_m$  > RBW: The receiver is able to properly measure each individual side-band harmonic separately, so the measurements match with the theoretical calculations.

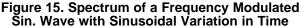

Figure 17. Power-Save Mode Ripple

## 10.4.2 Pass-Through Mode

The TPS6128xA contains an internal switch for bypassing the dc/dc boost converter during pass-through mode. When the input voltage is larger than the preset output voltage, the converter seamlessly transitions into 0% duty cycle operation and the bypass FET is fully enhanced. Entry in pass-through mode is triggered by condition where VOUT > VOUT\_NORM and no switching has occurred during past 16 $\mu$ s.

In this mode of operation, the load (2G RF PA for instance) is directly supplied from the battery for maximum RF output power, highest efficiency and lowest possible input-to-output voltage difference. The device consumes only a standby current of 15µA (typ). In pass-through mode, the device is short-circuit protected by a very fast current limit detection scheme.

During this operation, the output voltage follows the input voltage and will not fall below the programmed output voltage threshold as the input voltage decreases. The output voltage drop during pass-through mode depends on the load current and input voltage, the resulting output voltage is calculated as:

$$V_{OUT} = V_{IN} - (R_{DSON(BP)} \times I_{OUT})$$

Conversely, the efficiency in pass-through mode is defined as:

$$\eta = 1 - R_{\text{DSON(BP)}} \frac{I_{\text{OUT}}}{V_{\text{IN}}}$$

(5)

in which R<sub>DSON(BP)</sub> is the typical on-resistance of the bypass FET

10.4 Device Functional Modes

10.4.1 Power-Save Mode

PFM mode.

(4)

Copyright © 2013-2014, Texas Instruments Incorporated

The TPS6128x integrates a power-save mode to improve efficiency at light load. In power save mode the converter only operates when the output voltage trips below a set threshold voltage. It ramps up the output voltage with several pulses and goes into power save mode once the output voltage exceeds the set threshold voltage. The PFM mode is left and PWM mode entered in case the output current can not longer be supported in

#### TPS61280, TPS61281, TPS61282 SLVSBI1A – OCTOBER 2013 – REVISED SEPTEMBER 2014

## **Device Functional Modes (continued)**

Figure 18. DC Output Voltage vs. Input Voltage

Pass-through mode exit is triggered when the output voltage reaches the pre-defined threshold (e.g. 3.4V).

During pass-through mode, the TPS6128x device is short-circuit protected by a very fast current limit detection scheme. If the current in the pass-through FET exceeds approximately 7.3Amps a fault is declared and the device cycles through a start-up procedure.

#### 10.4.3 Mode Selection

Depending on the settings of *CONFIG Register* the device can be operated at a quasi-constant 2.3-MHz frequency PWM mode or in automatic PFM/PWM mode. In this mode, the converter operates in pseudo-fixed frequency PWM mode at moderate to heavy loads and in the PFM mode during light loads, which maintains high efficiency over a wide load current range. For more details, see the *CONFIG Register* description.

The quasi-constant frequency PWM mode has the tightest regulation and the best line/load transient performance. In forced PWM mode, the device features a unique  $R_{DS(ON)}$  management function to maintain high broadband efficiency as well as low resistance in pass-through mode.

In the TPS61280 device, the GPIO pin can be configured (via the *CONFIG Register*) to select the operating mode of the device. In the other TPS6128x devices, the MODE pin is used to select the operating mode. Pulling this pin high forces the converter to operate in the PWM mode even at light load currents. The advantage is that the converter modulates its switching frequency according to a spread spectrum PWM modulation technique allowing simple filtering of the switching harmonics in noise-sensitive applications.

For additional flexibility, it is possible to switch from power-save mode (GPIO or MODE input = L) to PWM mode (GPIO or MODE input = H) during operation. This allows efficient power management by adjusting the operation of the converter to the specific system requirements (e.g. 2G RF PA Rx/Tx operation).

#### NOTE

During start-up (conventionally or when recovering from thermal shutdown) the device must be set to operate with auto PFM/PWM mode. Consequently, the device determines automatically PFM or PWM mode depending on the output's load. Once the output voltage settled and PG pin indicates that the converter's output voltage is within its regulation limits, the device can be forced in PWM mode operation, if desired.

Entry to forced pass-through mode (nBYP = L) initiates with a current limited transition followed by a true bypass state. To prevent reverse current to the battery, the devices waits until the output discharges below the input voltage level before entering forced pass-through mode. Care should be taken to prohibit the output voltage from collapsing whilst transitioning into forced pass-through mode under heavy load conditions and/or limited output capacitance. This can be easily done by adding capacitance to the output of the converter. In forced pass-through mode, the output follows the input below the preset output threshold voltage (VOUT\_TH).

Copyright © 2013–2014, Texas Instruments Incorporated

NSTRUMENTS

FXAS

### **Device Functional Modes (continued)**

#### 10.4.4 Current Limit Operation

The TPS6128x device features a valley inductor current limit scheme.

In dc/dc boost mode, the TPS6128x device employs a current limit detection scheme in which the voltage drop across the synchronous rectifier is sensed during the off-time. In the TPS61280 the current limit threshold can be set via an I<sup>2</sup>C register. TPS6128x devices have a fixed current limit threshold. See the *Device Comparison Table* for detailed information.