# TN1258 Technical note

An innovative high power IC surface mount package family: PowerSO-20 & PowerSO-36 Power IC packaging from insertion to surface mounting

## Introduction

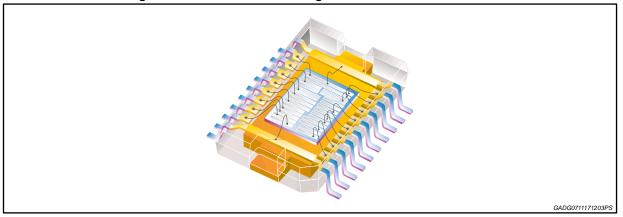

An innovative, high power IC surface mount package family is introduced in this note. It is called PowerSO family and has the Jedec registration MO-166.

STMicroelectronics developed PowerSO in order to answer the increasing demand of miniaturization and quality in power applications. Automotive, industrial, audio and telecom markets will take advantage of the new package, by introducing the use of Surface Mount Technology in the production of power systems.

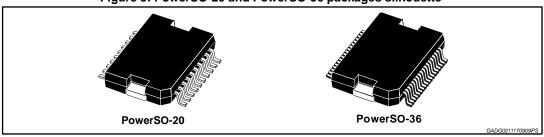

PowerSO-20 and PowerSO-36 are the elements of the MO-166 family having 20 leads at 0.050 inch pitch (1.27 mm) and 36 leads at 0.026 inch pitch (0.65 mm) respectively. These packages are in mass production since 1995.

This note is intended to compare the PowerSO-20/36 with alternative surface mount solutions and to the existing Multiwatt package, the well known "double TO-220" developed by STMicroelectronics in late 70s.

Data presented here demonstrates that PowerSO-20 is the real successor of Multiwatt for surface mount applications and becomes a milestone in power package technology with PowerSO-36 as Multiwatt did 30 years ago.

### Figure 1: PowerSO-20 – Jedec registration MO-166

| Con | itents    |                   |                                                        |    |

|-----|-----------|-------------------|--------------------------------------------------------|----|

| 1   | Power d   | evices an         | d surface mounting                                     | 5  |

|     | 1.1       | Intermedi         | ate solutions: insertion packages converted to SMT     | 5  |

|     | 1.2       |                   | tions: original STMicroelectronics packages with desig | -  |

|     |           |                   | CS                                                     |    |

| 2   | Structur  | e and cha         | aracteristics of PowerSO-20/36                         | 11 |

|     | 2.1       | High pow          | er structure and process (>20 W)                       | 11 |

|     | 2.2       | High curre        | ent capability (10-20 A)                               | 11 |

|     | 2.3       | Miniaturiz        | ation                                                  | 12 |

|     | 2.4       | Designed          | -in surface mount characteristics                      | 12 |

|     | 2.5       | Hermetici         | ty                                                     | 15 |

| 3   | Thermal   | design a          | nd applications                                        | 16 |

|     | 3.1       | Junction-1        | o-case thermal resistance                              | 16 |

|     | 3.2       | Applicatio        | ns with 1-2 Watt dissipation                           | 17 |

|     |           | 3.2.1             | On board dissipating elements                          | 17 |

|     | 3.3       | Applicatio        | ns with 2-5 W dissipation                              | 19 |

|     |           | 3.3.1             | Dissipating elements and ground layer                  |    |

|     |           | 3.3.2             | Via holes and ground layer                             |    |

|     |           | 3.3.3             | Via holes and external heatsink                        |    |

|     | 3.4       | 0 1               | er applications (up to 20 W) with standard substrate   |    |

|     |           | 3.4.1             | Slug-up package and external heatsink                  |    |

|     | 3.5       | 3.4.2<br>Lich pow | Cavity board and external heatsink                     | 24 |

|     |           | • •               | er applications (up to 20 W) with Insulated Metal      | 24 |

|     | 3.6       | High pow          | er pulses and thermal impedance                        | 25 |

| 4   | Solderin  | g informa         | ation                                                  | 28 |

| 5   | Reliabili | ty data           |                                                        | 29 |

| 6   | Conclus   | ion               |                                                        | 31 |

| 7   | Revisior  | history .         |                                                        | 32 |

# List of tables

| Table 1: PowerSO-20 package mechanical data                              | 7  |

|--------------------------------------------------------------------------|----|

| Table 2: PowerSO-36 package mechanical data                              | 9  |

| Table 3: Electrical resistance data of PowerSO-20 and Multiwatt 15 leads | 11 |

| Table 4: Miniaturization of PowerSO-20 vs surface mount Multiwatt        | 12 |

| Table 5: PowerSO-36 (slug-up) package mechanical data                    | 23 |

| Table 6: Thermal performance (ΔTj: 50°C)                                 | 26 |

| Table 7: Reliability tests description                                   | 29 |

| Table 8: ABS voltage regulator (die size 5.3 x 5.28 mm)                  | 30 |

| Table 9: TDA7350A (Bridge Audio Amplifier)                               | 30 |

| Table 10: Document revision history                                      | 32 |

# List of figures

| Figure 1: PowerSO-20 – Jedec registration MO-166                                            | 1  |

|---------------------------------------------------------------------------------------------|----|

| Figure 2: Heptawatt™ (surface mount) package silhouette drawing                             | 5  |

| Figure 3: PowerSO-20 and PowerSO-36 packages silhouette                                     |    |

| Figure 4: PowerSO-20 package outline                                                        |    |

| Figure 5: PowerSO-36 package outline                                                        |    |

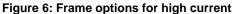

| Figure 6: Frame options for high current                                                    | 13 |

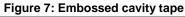

| Figure 7: Embossed cavity tape                                                              |    |

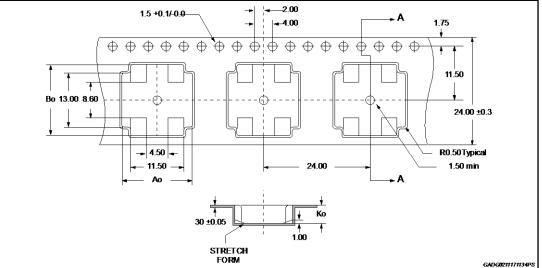

| Figure 8: Exposed slug edge for solder joint inspection                                     |    |

| Figure 9: Loss of thermal performance due to poor co-planarity and uneven solder joints     | 15 |

| Figure 10: Scanning acoustic microscope map                                                 | 15 |

| Figure 11: Thermal resistance junction-case vs. dissipating area of PowerSO-20/36           |    |

| Figure 12: Lead frame for medium power SO                                                   |    |

| Figure 13: Foot print for medium power SO                                                   |    |

| Figure 14: Rth(j-a) vs. board dissipating area                                              |    |

| Figure 15: Pad layout                                                                       |    |

| Figure 16: Footprint with dissipating element                                               |    |

| Figure 17: Mounting on PCB with ground layer                                                |    |

| Figure 18: Mounting on epoxy FR4 using via holes for heat transfer of ground layer          |    |

| Figure 19: Footprint of PowerSO20/36 with via holes                                         |    |

| Figure 20: Mounting on epoxy FR4 using via holes for heat transfer and external metal plate |    |

| Figure 21: Thermal resistance junction-substrate                                            |    |

| Figure 22: "Slug up" package with external heatsink                                         |    |

| Figure 23: PowerSO-36 (slug-up) package outline                                             |    |

| Figure 24: Mounting on cavity board and external heatsink applied                           |    |

| Figure 25: PowerSO-20/36 mounted with insulated metal substrate (IMS)                       |    |

| Figure 26: Thermal impedance of different packages (surface mount vs. insertion)            |    |

| Figure 27: Thermal impedance of different packages (SO20 vs. PowerSO-20/36)                 |    |

| Figure 28: PowerSO-20/36 typical heating profile                                            | 28 |

## **1** Power devices and surface mounting

Use of Surface Mount Technology (SMT) has dramatically increased in the last 30 years, moving from consumer to professional applications and serving highly demanding markets like telecom, industrial and automotive.

Major advantages expected from SMT are size reduction, automated board mounting, high reliability and cost effectiveness; larger density of functions is achieved in smaller systems.

Evolution of SMT drove the development of several new packages for discrete and IC devices: SOT23, SOT194, TO263, SO, PLCC, PQFP with many options in pin pitch, size and thickness.

All of them are compatible with the surface mount technique, based on fast picking and placing from tapes or trays, followed by mass soldering. Mounting lines are almost totally automated, with high throughput and high yield.

Only a few devices are not yet compatible with SMT principles: a few "exotic" components like large capacitors, resistors, inductors, varistors, etc. and almost all the power semiconductor packages. Several drawbacks are associated with existing power packages:

- 1. They still have the traditional structure for insertion and are mounted manually in the PCB, with loss of time, productivity, floor space and money;

- 2. They force the use of wave soldering techniques and are not compatible with reflow soldering;

- 3. They are not compatible with the increasing need of miniaturization of power systems.

The above points are so important that the development of totally new power packages fitting the SMT requirements is a clear demand of the industry and can pay back the heavy effort needed in terms of R&D, engineering and production resources.

# 1.1 Intermediate solutions: insertion packages converted to SMT

The fastest answer to the requirement discussed above is the adaptation of the existing insertion packages to obtain a kind of surface mount configuration.

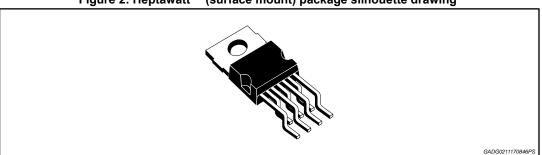

This can be conveniently done by redesigning the lead shape, as in the case of the surface mount Heptawatt package (7 lead TO-220) shown in *Figure 2: "Heptawatt™ (surface mount) package silhouette drawing"* which was introduced in the market by STMicroelectronics in 1989.

The package of *Figure 2: "Heptawatt™ (surface mount) package silhouette drawing"* is very attractive in terms of capital expenditure and time to market; as a minor modification of existing production line can provide the surface mount version in a short development time.

Figure 2: Heptawatt<sup>™</sup> (surface mount) package silhouette drawing

However, the experience of STMicroelectronics with the above solutions is not totally satisfactory, for a number of reasons:

- 1. HANDLING, which unlike all other surface mount packages, is complicated by the structure, which is asymmetrical in two directions (height and thickness). Existing pick and place tools are not readily compatible with this structure, as well as the tape and reel packing;

- 2. SIZE, which is basically the same as existing insertion packages; therefore, is not the answer to the demand of miniaturization of power systems coming from almost all the applications: automotive, audio and industrial;

- COPLANARITY, which can become an issue for 4-6 mm (0.16-0.24 inch) long leads. It

must be recalled that major coplanarity improvement is obtained by reducing the lead

length, down to 1-2 mm (0.04-0.08 inch); this cannot be readily obtained with

Multiwatt, whose average leadframe thickness is about 0.4 mm.

- 4. RELIABILITY AFTER THE SOLDERING PROCESS, due to the excess stress caused by the high temperature (>215 °C) even with "zero" absorbed moisture at the large interface between slug and molded body, with consequent delamination;

- 5. INSPECTION OF THE SOLDERED JOINT between slug and substrate, as discussed in next paragraph;

- 6. LIMITED PIN COUNT 7, which is no longer able to cover the requirements of advanced smart power, needing more I/Os for the logic circuitry.

Due to the above reasons, STMicroelectronics preferred to invest in new specifically developed power structures, with designed-in surface mount characteristics. Moreover, due to the increasing demand of quality, led by the automotive market, process and materials were selected in order to obtain intrinsic long term reliability and a very low failure rate, targeted at 1 ppm for early life.

# 1.2 New solutions: original STMicroelectronics packages with design-in SMT characteristics

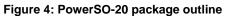

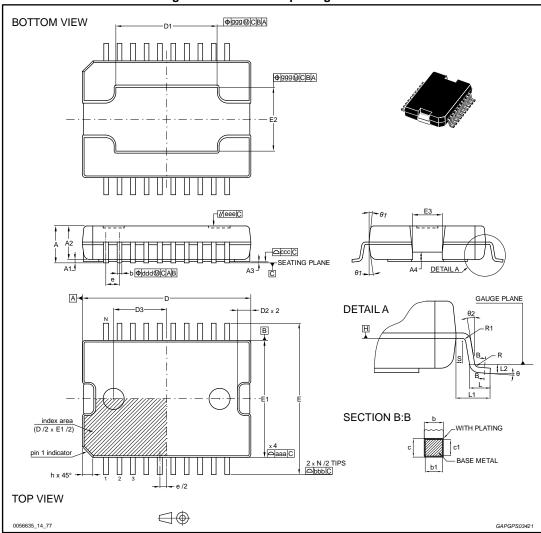

The well understood dual-in-line configuration was selected for the new housing (*Figure 4:* "*PowerSO-20 package outline*"), which does not look very much different from the Small Outline (SO) package; but, from high dissipation capability, the main difference is the internal massive slug, which provides the same thermal impedance as traditional insertion packages. In view of the larger pin count needed for smart power products, a family of packages has been designed, covering from 20 to 36 leads. The well established concept of "variable pitch in a fixed body" has been used, with 1.27 mm (0.05 inch), 1.0 mm, 0.8 mm and 0.65 mm.

The new family, named PowerSO, is Jedec registered as MO-166. PowerSO-20 and PowerSO-36 dimensions are described respectively in the following *Figure 4: "PowerSO-20 package outline"* and *Figure 5: "PowerSO-36 package outline"*.

#### Table 1: PowerSO-20 package mechanical data

| Def | Dimensions (mm) |      |      |  |

|-----|-----------------|------|------|--|

| Ref | Min.            | Тур. | Max. |  |

| θ   | 0°              | -    | 8°   |  |

| Θ1  | 5°              | -    | 10°  |  |

| θ2  | 0°              | -    | -    |  |

| A   | -               | -    | 3.6  |  |

| A1  | 0.1             | -    | -    |  |

| A2  | 3               | 3.15 | 3.3  |  |

| A3  | -               | -    | 0.1  |  |

| b   | 0.4             | -    | 0.53 |  |

| b1  | 0.4             | 0.45 | 0.5  |  |

| С   | 0.23            | -    | 0.32 |  |

DocID031323 Rev 1

### Power devices and surface mounting

| Def               | Dimensions (mm) |           |      |  |

|-------------------|-----------------|-----------|------|--|

| Ref               | Min.            | Тур.      | Max. |  |

| c1                | 0.23            | 0.25      | 0.29 |  |

| D                 |                 | 15.90 BSC |      |  |

| D1 <sup>(1)</sup> | 9               | -         | 13   |  |

| D2                | -               | -         | 1.1  |  |

| D3                | -               | 5         | -    |  |

| е                 |                 | 1.27 BSC  |      |  |

| E                 |                 | 14.20 BSC |      |  |

| E1 <sup>(1)</sup> |                 | 11.00 BSC |      |  |

| E2                | 5.6             | -         | 6.2  |  |

| E3                | -               | -         | 2.9  |  |

| h                 | -               | -         | 1.1  |  |

| L                 | 0.8             | -         | 1.1  |  |

| L1                | 1.60 REF        |           |      |  |

| L2                |                 | 0.35 BSC  |      |  |

| Ν                 | 20              |           |      |  |

| R                 | 0.2             | -         | -    |  |

| R1                | 0.2             | -         | -    |  |

| S                 | 0.25            | -         | -    |  |

| aaa               | 0.1             |           |      |  |

| bbb               | 0.3             |           |      |  |

| CCC               | 0.1             |           |      |  |

| ddd               | 0.25            |           |      |  |

| eee               | 0.1             |           |      |  |

| 999               | 0.25            |           |      |  |

#### Notes:

<sup>(1)</sup>Dimensions 'D' and 'E1' do not include mold flash or protrusions. Allowable mold flash or protrusions is "0.25 mm" per side D and "0.15 mm" per side E1. D and E1 are Maximum plastic body size dimensions including mold mismatch.

| Def               | Dimensions (mm) |       |       |  |

|-------------------|-----------------|-------|-------|--|

| Ref               | Min.            | Тур.  | Max.  |  |

| A                 | -               | -     | 3.60  |  |

| a1                | 0.10            | -     | 0.30  |  |

| a2                |                 | -     | 3.30  |  |

| a3                | 0               | -     | 0.10  |  |

| b                 | 0.22            | -     | 0.38  |  |

| С                 | 0.23            | -     | 0.32  |  |

| D <sup>(1)</sup>  | 15.80           | -     | 16.00 |  |

| D1                | 9.40            | -     | 9.80  |  |

| E                 | 13.90           | -     | 14.5  |  |

| E1 <sup>(1)</sup> | 10.90           | -     | 11.10 |  |

| E2                | -               | -     | 2.90  |  |

| E3                | 5.80            | -     | 6.20  |  |

| е                 | -               | 0.65  | -     |  |

| e3                | -               | 11.05 | -     |  |

### Power devices and surface mounting

| Ref | Dimensions (mm)       |      |       |  |

|-----|-----------------------|------|-------|--|

| Rei | Min.                  | Тур. | Max.  |  |

| G   | 0                     | -    | 0.10  |  |

| Н   | 15.50                 | -    | 15.90 |  |

| h   | -                     | -    | 1.10  |  |

| L   | 0.8                   | -    | 1.10  |  |

| N   | 10° (max)<br>8° (max) |      |       |  |

| S   |                       |      |       |  |

#### Notes:

<sup>(1)</sup>"D and E1" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm (0.006"). Critical dimensions are "a3", "E" and "G".

The most important features of PowerSO-20/36 are:

- 1. High power structure and process (see Section 2.1: "High power structure and process (>20 W)");

- 2. High current capability (see Section 2.2: "High current capability (10-20 A)");

- 3. Miniaturization (see Section 2.3: "Miniaturization")

- 4. Designed-in surface mount characteristics (see Section 2.4: "Designed-in surface mount characteristics"):

- Handling;

- Tape and reel packing;

- Co-planarity;

- Solder joint quality and inspection;

- High reliability after soldering process.

- 5. Designed-in "hermeticity", for low failure rate (1 ppm) see Section 2.5: "Hermeticity".

## 2 Structure and characteristics of PowerSO-20/36

In this section, design criteria listed in previous paragraph are presented and discussed.

## 2.1 High power structure and process (>20 W)

The main feature of the power package structure is the existence of a massive copper slug in the package onto which the silicon chip is soldered. Its function is twofold:

- 1. To provide a low thermal resistance path from the chip to the external heatsink;

- 2. To provide a large thermal capacitance, able to absorb power peaks in switching conditions.

The slug of PowerSO-20/36, is optimized in order to get a good compromise between miniaturization and thermal performance. As a result of this work, PowerSO-20 has the same junction to case thermal resistance  $R_{th(j-case)}$  of Multiwatt package and the same thermal impedance up to 0.5 sec. Therefore the range of application exceeds 20 W, the same as for traditional power packages.

In Section 3: "Thermal design and applications" the thermal design is described in detail. Here we explain the importance of the die attach process, typical of power IC packages, which uses a high melting temperature (300°C) tin based alloy. The control of this process, in terms of solder thickness and void reduction, is based on SPC.

## 2.2 High current capability (10-20 A)

At first glance, leads of the PowerSO-20/36 seem very fragile, thin and not compatible with the high currents (10-20 A) associated with a large number of power ICs, which require the utilization of large aluminum wires having a diameter ranging between 0.010 and 0.020 inch (0.25 to 0.5 mm).

*Table 3: "Electrical resistance data of PowerSO-20 and Multiwatt 15 leads"* reports the comparison of PowerSO-20 with insertion and surface mount Multiwatt and the following considerations are possible:

- 1. Electrical resistance of PowerSO-20 leads is about 760  $\mu\Omega$ , i.e. it is equivalent to insertion Multiwatt or better;

- 2. Electrical resistance of PowerSO-20 leads is worse than Surface Mount Multiwatt by a factor of 1.3 to 2;

- 3. In any case, lead resistance of PowerSO-20 is much lower than the wire resistance. Wire resistance is 450-1800  $\mu\Omega$ /mm and it must be considered that the minimum wire length is 2.5 mm corresponding to 1150-4500  $\mu\Omega$ ;

- 4. If needed, two or more leads are short circuited and different frame designs can be developed providing flexible options (*Figure 7: "Embossed cavity tape"*). With multiple wire bonding, current capability can be very large; for 45 A current, if 3 leads are used with 10 mil diameter, 3 mm long wires, electrical resistance of the interconnection is about 2 m $\Omega$ .

| Dimensions<br>(mm) | Multiwatt15<br>Insertion | Multiwatt15<br>Surf. Mount | PowerSO-20 |

|--------------------|--------------------------|----------------------------|------------|

| Long lead MW15     |                          |                            |            |

| 23x0.9x0.5         | 970 μΩ                   | -                          | -          |

| 18x0.9x0.5         | _                        | 760 μΩ                     | _          |

Table 3: Electrical resistance data of PowerSO-20 and Multiwatt 15 leads

## Structure and characteristics of PowerSO-20/36

| Dimensions<br>(mm) | Multiwatt15<br>Insertion | Multiwatt15<br>Surf. Mount | PowerSO-20 |

|--------------------|--------------------------|----------------------------|------------|

| Short lead MW15    |                          |                            |            |

| 14x0.9x0.5         | 590 μΩ                   | _                          | _          |

| 9x0.9x0.5          | _                        | 380 μΩ                     | _          |

| Lead PowerSO-20    |                          |                            |            |

| 5x0.5x0.25         | _                        | _                          | 760 μΩ     |

Copper resistivity : 1.9 mW x cm

Aluminum wire resistance:

Ø 10 mils: 1800 mW / mm

Ø 20 mils: 450 mW / mm

## 2.3 Miniaturization

The whole story of microelectronics has been a continuous race towards smaller products. This is also true for power systems.

The PowerSO-20 and PowerSO-36 offer excellent possibilities in miniaturization, without compromising power dissipation.

From *Table 4: "Miniaturization of PowerSO-20 vs surface mount Multiwatt"*, which compares the PowerSO-20 with the surface mount version of Multiwatt, advantages in terms of size, weight, height and volume are evident. They range between 22 and 64% improvement.

|                                 | SM MW15L | PowerSO-20 | Difference |

|---------------------------------|----------|------------|------------|

| footprint<br>(mm <sup>2</sup> ) | 320      | 227        | -30%       |

| height<br>(mm)                  | 4.5      | 3.5        | -22%       |

| volume<br>(mm <sup>3</sup> )    | 1160     | 590        | -49%       |

| weight (gr)                     | 5.6      | 1.9        | -64%       |

Table 4: Miniaturization of PowerSO-20 vs surface mount Multiwatt

## 2.4 Designed-in surface mount characteristics

## Handling

The PowerSO-20/36 structure is similar to the SO outline, which was introduced more than 30 years ago in STMicroelectronics. Therefore, the experience associated with the different aspects of production, testing, burn-in and on board mounting are quite solid.

Due to their optimized outline and reduced weight, handling of the PowerSO-20/36 packages does not present any particular problem and is fully compatible with the existing equipment.

## Packing

Tube and Tape & Reel packing are both possible with the PowerSO-20/36. Embossed cavity tape has been produced with a special design, able to minimize the mechanical effect of packing and shipment on the lead coplanarity (*Figure 7: "Embossed cavity tape"*).

## Coplanarity

Lead coplanarity is considered a major issue for surface mount devices. In the case of Power surface mount packages, whose slug is eventually soldered on a substrate, coplanarity is also referenced to the relative position of the slug and the leads.

In the PowerSO-20/36, lead extremities and package slug are positioned inside a 4 mil (0.1 mm) layer; this condition provides a high yield mounting and soldering process.

### Solder joint quality and inspection

When the package slug is soldered onto the substrate, as in the many applications developed so far, the need exists for producing a high quality solder joint between the slug and its solder pad on the board.

The PowerSO-20/36 structure is ideal from this viewpoint: symmetry existing in the x-y plane provides a very good balance of the wetting forces, once the solder paste is melted. A kind of self centering effect has been observed, which is mostly due to the dual-in-line outline and to the excellent wettability of both leads and slug. This results in a solder joint well controlled in thickness and consistency.

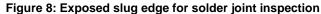

An additional advantage of the PowerSO-20/36 outline is the presence of two exposed inspection points on the slug, which has been intentionally obtained in the package body (*Figure 8: "Exposed slug edge for solder joint inspection"*). Proprietary processes keep these two points free of molding compound flash and allow evident solder fillets after the soldering process.

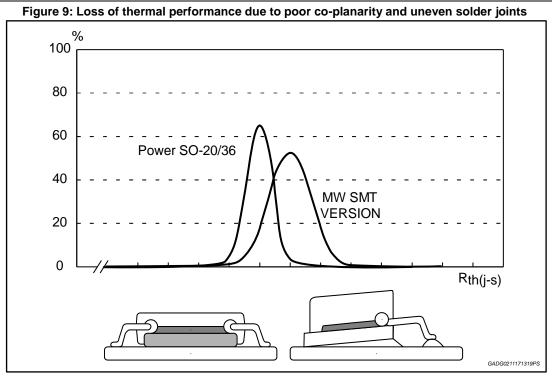

Due to the symmetrical structure of PowerSO-20,/36 the presence of solder fillet in both inspection points is a good indicator of joint quality and planarity. It should be noticed that the same kind of control is not possible in the surface mount Multiwatt structure, which can show a good solder fillet in the exposed section of the slug even with a non-parallel joint and possible voiding. In this case, the degradation of the junction to substrate thermal resistance R<sub>th(j-s)</sub> is more evident, as shown in *Figure 9: "Loss of thermal performance due to poor co-planarity and uneven solder joints*".

## Reliability after soldering process

Extensive evaluation of frame design and materials provides the PowerSO-20/36 excellent reliability performance after the soldering process, as discussed in *Section 5: "Reliability data"*. No degradation of the package structure has been observed after the high temperature stress, up to 260 °C.

#### Structure and characteristics of PowerSO-20/36

## 2.5 Hermeticity

Good hermeticity of package interfaces has been obtained by means of slug design and of the selection of low stress, high adhesion molding compounds.

State-of-the-art molding equipment and process is used, providing repeatability of the results in large volumes.

Moreover, improved mechanical clamping of the molding compound is obtained by using a new, proprietary finishing of the slug all along its periphery, which is provided with undercutting and controlled surface roughness.

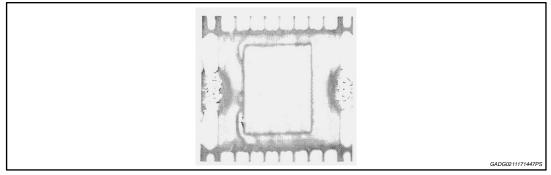

After severe tests consisting of alternate thermal cycling and pressure pot, and after the "pop corn" sequence, Scanning Acoustic Microscopy (SAM) analysis and die penetration test confirms the robustness of the PowerSO-20/36. *Figure 10: "Scanning acoustic microscope map"* shows a typical map of adhesion obtained in SAM evaluation after stress analysis.

#### Figure 10: Scanning acoustic microscope map

## 3 Thermal design and applications

Thermal characteristics of the new PowerSO-20/36 package can cover a wide range of applications, both in the medium power (1-5 W) and in the high power range (up to 20 W). Moreover, as sufficiently large thermal capacitance is associated with the new package, performance in switching conditions is equivalent to that of available insertion packages.

In this section, a number of typical applications of the PowerSO-20/36 will be considered and compared with the existing solutions, taking into account that a major role in the thermal design is played by the temperature increase  $T_j$ - $T_a$  specified in the different applications. "Delta"  $T_j$  can be as low as 25-30 °C in extreme conditions for automotive or as large as 100 °C in more relaxed systems.

Unless differently indicated,  $\Delta T_j$  of 50 °C is assumed in all the considerations of this note.

## 3.1 Junction-to-case thermal resistance

The main feature of PowerSO-20/36 packages are optimization of junction-to-case thermal resistance, from the junction to the external surface of the slug.

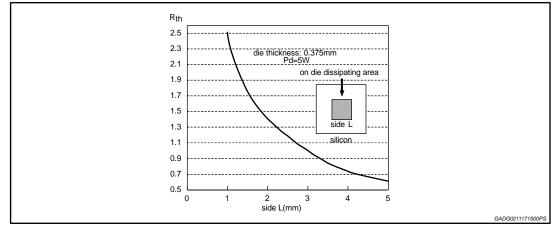

Unlike standard SO packages, which use epoxy die attach and thin leadframes, the PowerSO-20/36 take advantage of power package technology, with a massive copper slug and tin based alloy die soldering. This results in minimum junction-to-case thermal resistance Rth(j-c). *Figure 11: "Thermal resistance junction-case vs. dissipating area of PowerSO-20/36"* shows how much Rth(j-c) is affected by the die size, assuming that the power source is uniformly distributed on the die.

For actual applications,  $R_{th(j-c)}$  ranges between 2 °C/W for small dice and 0.5 °C/W for the maximum die size of 60k sq mils. Therefore, the PowerSO-20/36 are equivalent to insertion power packages like TO-220 and Multiwatt; this is due to the optimization of the slug dimensions, obtained by removal of any copper in excess, without affecting the thermal cone where the heat flows from the silicon to the substrate.

The PowerSO-20/36 offer a new possibility for a power package: direct soldering of the slug onto the board during the surface mount process; therefore junction to substrate thermal resistance is close to  $R_{th(j-c)}$  and reaches the very attractive value of 0.5-2.0 °C/W.

Figure 11: Thermal resistance junction-case vs. dissipating area of PowerSO-20/36

DocID031323 Rev 1

## 3.2 Applications with 1-2 Watt dissipation

## 3.2.1 On board dissipating elements

**TN1258**

In this power range, state of the art technology is based on the medium power SO.

It has the same outline of a standard SO package but with a modified leadframe in order to have a number of leads connected to the die pad (bat wing structure).

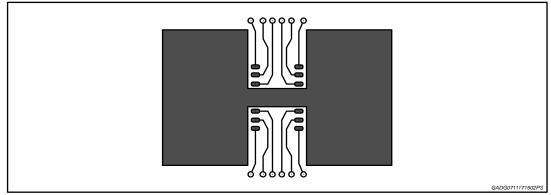

This solution, shown in *Figure 12: "Lead frame for medium power SO"*, is effective in minimizing the Junction-to-Pin thermal resistance  $R_{th(j-p)}$ , i.e. the thermal path between the junction and suitable dissipating areas obtained on the PCB and connected to the heat transfer leads *Figure 13: "Foot print for medium power SO"*.

Figure 12: Lead frame for medium power SO

Typical representatives of the medium power SO package family are the 300 mils SO20 and SO28 with 8 heat transfer leads, reported as SO(12+4+4) and SO(20+4+4) respectively.

Referring to STMicroelectronics guideline "Thermal management in Surface Mount Technology" (July 1988), thermal performance of medium power SO(12+4+4) is defined by the relationship:

$R_{th(j-a)} = R_{th(j-p)} + R_{th(sub-amb)}$

where  $R_{th(j-p)}$  is the thermal path from the junction to the board and  $R_{th(sub-amb)}$  is the thermal resistance of the two areas shown in *Figure 13: "Foot print for medium power SO"*.

$R_{th(j-p)}$  ranges between 12 and 14 °C/W, depending on the efficiency of the heat transfer leads (design and thermal conductivity) and on the die size.

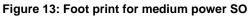

$R_{th(j-a)}$  is due to the size of the dissipating elements on the board, according to *Figure 14:* "*Rth(j-a) vs. board dissipating area*", which shows improved thermal resistance from 76 to 50 °C/W when the dissipating area is increased from 0 to 6 cm<sup>2</sup>.

The PowerSO-20/36 can be used in place of medium power SO, with the slug soldered on the board.

#### Figure 14: Rth(j-a) vs. board dissipating area

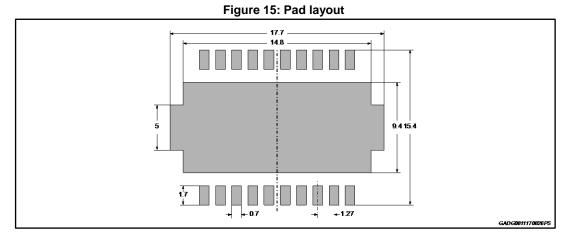

The first experimental evidence shows a very good heat exchange with the substrate, due to the large contact area associated with the basic footprint of *Figure 15: "Pad layout"*. The  $R_{th(j-a)}$  in this configuration is about 50 °C/W.

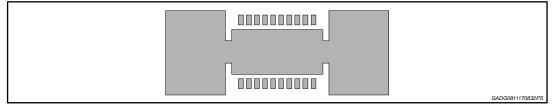

When the two dissipating elements are added and the footprint of *Figure 16: "Footprint with dissipating element"* is used, additional improvement is observed. For example, R<sub>th(j-a)</sub> is 35 °C/W with dissipation elements of 6 sq cm.

Figure 16: Footprint with dissipating element

Margin over the traditional medium power SO(12+4+4) is about 40%, with dissipation increased from 1 W to 1.4 W always with Delta  $T_j = 50$  °C. Improvement can be also understood taking into account that the junction to substrate thermal resistance is equivalent to  $R_{th(j-p)} = 12-14$  °C/W for medium power SO(12+4+4) and equivalent to  $R_{th(j-c)} = 0.52.0$  °C/W for PowerSO-20/36.

## 3.3 Applications with 2-5 W dissipation

## 3.3.1 Dissipating elements and ground layer

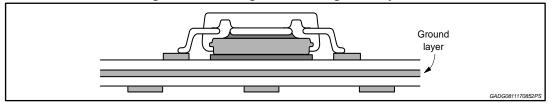

It must be noticed that previous data are observed with a simple PCB, with single or double face. In applications using multilayer boards, a much better efficiency is observed due to the heat spreading effect of the ground layer.

Looking at the board structure of *Figure 17: "Mounting on PCB with ground layer"*, heat generated at the junction is transferred to the dissipating areas on the board surface and then to the ground layer, which works as a large heat exchange element with the ambient.

The  $R_{th(j\text{-}a)}$  offered by this solution is 20-25  $^{\circ}\text{C/W}$  for 2.0-2.5 W dissipation.

## 3.3.2 Via holes and ground layer

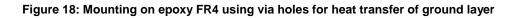

If via holes are used as in *Figure 18: "Mounting on epoxy FR4 using via holes for heat transfer of ground layer*", a more direct thermal path is obtained from the slug to the ground layer. The number of vias is chosen according to the desired performance.

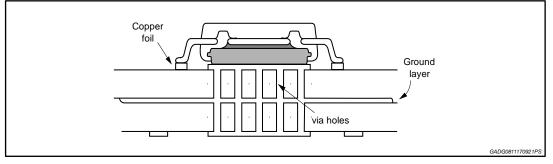

*Figure 19: "Footprint of PowerSO20/36 with via holes"* shows a typical high performance foot print for PowerSO20/36 with via holes

$R_{th(j\text{-}a)}$  can be reduced down to 15-20 °C/W and dissipation increased up to 2.5-3.3 W with Delta  $T_j$  = 50 °C.

Figure 19: Footprint of PowerSO20/36 with via holes

20/33

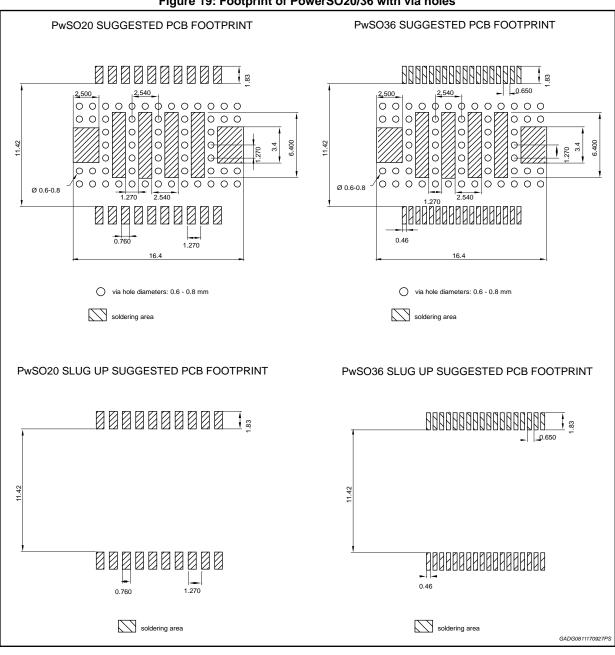

## 3.3.3 Via holes and external heatsink

The solution considered in *Figure 20: "Mounting on epoxy FR4 using via holes for heat transfer and external metal plate"* combines a PowerSO-20/36 soldered onto a via hole structure, with a metal plate glued on the opposite side of the board.

The final thermal resistance value is given by the resistance of via holes added to the resistance of the plate to the ambient.

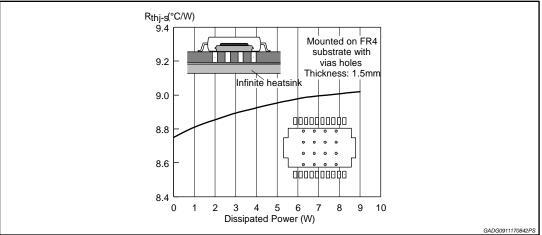

*Figure 21: "Thermal resistance junction-substrate"* shows the thermal resistance associated with 16 holes and reports its behavior with the dissipated power. Hole depth of 1.5 mm is an extreme case, existing in rather thick substrates only; the experimental value is about 9 °C/W, including the contribution of  $R_{th(j-c)}$ . In practical cases, structures with  $R_{th(j-a)} = 12-15$  °C/W are obtained for 3.3-4.2 W dissipation.

Figure 20: Mounting on epoxy FR4 using via holes for heat transfer and external metal plate

#### Figure 21: Thermal resistance junction-substrate

# 3.4 High power applications (up to 20 W) with standard substrate

In order to get an  $R_{th(j-a)}$  of few °C/W, high power applications require large and massive external heatsinks in close contact with the power device.

This is not a simple requirement when cost effective systems using the standard surface mount technology and the standard PCB substrate are considered.

Major concerns are related to the critical assembly of a large heatsink onto a small package; vibrations and thermal excursions can generate unwanted mechanical stress, thus damaging the package leads or the integrity of the contact between slug and heatsink.

DocID031323 Rev 1

### Thermal design and applications

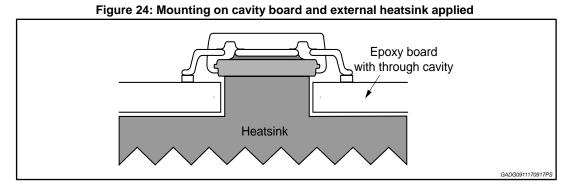

However, the fact that we have a well established, PCB based surface mount technology is pushing the industry to test several directions, similar to those sketched in *Figure 22: ""Slug up" package with external heatsink"* and *Figure 24: "Mounting on cavity board and external heatsink applied"*.

Rather than proven solutions, they should be considered here as early attempts aimed to explore the capability of existing surface mount processes and materials in the direction of increased heat dissipation at reduced cost.

## 3.4.1 Slug-up package and external heatsink

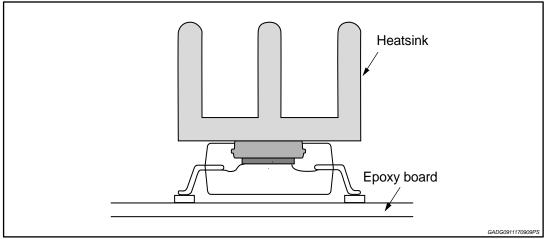

In the example of *Figure 22: ""Slug up" package with external heatsink"*, PowerSO-20 is shown in "reverse" or "slug-up" configuration, with a clip mounted external heatsink, which was studied for 3.5 W dissipation in still air and 5-6 W dissipation in forced ventilation.

A similar concept can be used for other applications and the sink size adapted to their specific requirements. A large variety of solutions will exist which will take advantage of the metal box in which the board can eventually be housed.

Figure 22: "Slug up" package with external heatsink

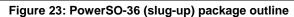

To minimize the mechanical stess on leads and solder joints derived from any pressure applied on top of package, the slug-up forming is specifically designed (see *Figure 23: "PowerSO-36 (slug-up) package outline"*).

| Def                 | Dimensions (mm) |      |       |

|---------------------|-----------------|------|-------|

| Ref                 | Min.            | Тур. | Max.  |

| А                   | 3.27            | -    | 3.41  |

| A2                  | 3.1             | -    | 3.18  |

| A4                  | 0.8             | -    | 1.0   |

| A5                  | -               | 0.2  | -     |

| a1                  | 0.03            | -    | -0.04 |

| b                   | 0.22            | -    | 0.38  |

| С                   | 0.23            | -    | 0.32  |

| D <sup>(1)(2)</sup> | 15.8            | -    | 16.0  |

| D1                  | 9.4             | -    | 9.8   |

| D2                  | -               | 1.0  | -     |

| E                   | 13.9            | -    | 14.5  |

| E1                  | 10.9            | -    | 11.1  |

| E2                  | -               | -    | 2.9   |

| E3                  | 5.8             | -    | 6.2   |

## Thermal design and applications

| Ref | Dimensions (mm) |       |        |  |

|-----|-----------------|-------|--------|--|

| Kei | Min.            | Тур.  | Max.   |  |

| E4  | 2.9             | -     | 3.2    |  |

| е   | -               | 0.65  | -      |  |

| e3  | -               | 11.05 | -      |  |

| G   | 0               | -     | 0.075  |  |

| н   | 15.5            | -     | 15.900 |  |

| h   | -               | -     | 1.1    |  |

| L   | 0.8             | -     | 1.1    |  |

| N   | -               | -     | 10°    |  |

| s   | -               | -     | 8°     |  |

#### Notes:

<sup>(1)</sup>Mold flash or protusions shall not exceed 0.15mm (0.006"). <sup>(2)</sup>D' and 'E1' do not include mold flash or protusions.

## 3.4.2 Cavity board and external heatsink

In the example of *Figure 24: "Mounting on cavity board and external heatsink applied"*, the PowerSO-20/36 is mounted onto an epoxy board, with a through cavity fabricated to correspond to the package slug. The external heatsink is directly applied in contact with the slug, secured by means of a spring system or glued. Also in this case, a high level of dissipation can be achieved with properly designed heatsinks.

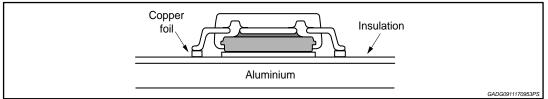

# 3.5 High power applications (up to 20 W) with Insulated Metal Substrates (IMS)

In the last decades, several companies developed the idea of a cost effective Insulated Metal Substrate (IMS) having:

- 1. A copper printed layer supported by an aluminum base, with epoxy or polyimide isolation in between;

- 2. A flexible printed circuit (polyimide) glued onto an aluminum base.

In both cases, the following conditions are offered:

1. The substrate is compatible with standard SMT processes, including infrared reflow soldering;

DocID031323 Rev 1

- 2. It is compatible with passive and active devices, including PowerSO-20/36;

- 3. It has an acceptable thermal resistance loss between the PowerSO-20/36 slug and

- the aluminum base, due to optimized thermal conductivity of the isolating layer;The aluminum baseplate has variable thickness, up to 5 mm, in order to sink different amounts of heat.

Utilization of IMS is considered for several applications both for automotive and industrial systems and is particularly fruitful when associated with PowerSO-20/36 packages (*Figure 25: "PowerSO-20/36 mounted with insulated metal substrate (IMS)"*).

Figure 25: PowerSO-20/36 mounted with insulated metal substrate (IMS)

Thermal performance has been measured for both substrates described above. The first result is related to the contribution of isolation to the total thermal resistance. When the footprint of *Figure 15: "Pad layout"* is used, with the 96 sq mm slug soldered onto a 155 sq mm pattern, this contribution is about  $0.5^{\circ}$ C/W.

Therefore, the thermal resistance from the junction to the aluminum baseplate ranges from 1.0 to 2.5 °C/W depending on the chip size.

For large dissipation, an external heat sink is applied to the IMS by means of screws, bolts or rivets. The total thermal resistance is obtained by adding the heat sink resistance to the junction to baseplate resistance (1.0-2.5 °C/W).

This solution is capable of 20-25 W per device and if a large sink is used, as massive parts existing in the car, more than one device can be assembled on the same ISM, thus obtaining a functional power subsystem with several tens of Watt dissipation.

It is interesting to notice that the aluminum plate itself has good dissipation properties to the ambient, depending on its size.

The PowerSO-20/36 soldered onto a 40 mm square, 1.5 mm thick IMS shows a thermal resistance of 7  $^{\circ}$ C/W, for about 7 W dissipation.

## 3.6 High power pulses and thermal impedance

In several applications, large power pulses are delivered by the device for a short time.

In this case, discussed in the STMicroelectronics paper "Designing with Thermal Impedance" (Semitherm Conf. 1988), the quantity which rules the junction temperature up to the time t0 is the thermal impedance of the three different elements: silicon chip, package slug and heatsink.

For pulse durations in the range of 0.1-1.0 sec, the package slug has the strongest influence on the system performance, depending on the associated thermal capacitance, i.e. the capability of heat accumulation.

In the presence of properly sized slugs with suitable capacitance, it is possible to maintain a low junction temperature for the switching time of most applications, which seldom exceeds 1 sec.

For popular power packages like TO-220 and Multiwatt, the value of the thermal impedance in the first second is lower than the value of  $R_{th(j-c)}$  in steady state.

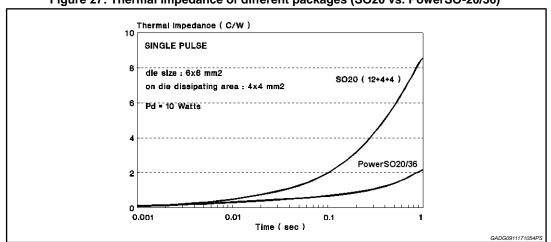

In order to compare the PowerSO-20/36 packages with the insertion equivalent, *Figure 26:* "*Thermal impedance of different packages (surface mount vs. insertion)*" is very helpful. It shows the thermal impedance of different packages in the first second of the power pulse, in the same conditions of power intensity and die size.

When similar comparisons are performed with medium power "bat wing" SO, the enhancement provided by the copper slug becomes very evident (*Figure 27: "Thermal impedance of different packages (SO20 vs. PowerSO-20/36)"*).

Due to the thermal capacitance of the slug, the transient thermal impedance of PowerSO20/36 after 1 sec pulse duration is 4 times lower.

A summary of the thermal performance of PowerSO-20/36 considering the different mounting approaches is given in *Table 6: "Thermal performance (\Delta T j: 50^{\circ}C)"*, assuming that the maximum rated temperature of the device is 150°C and that the  $\Delta T j$  is 50°C.

|                                                  | PowerSO-20/36 packages mounted on                               | R <sub>th(j-a)</sub> | Pdiss |

|--------------------------------------------------|-----------------------------------------------------------------|----------------------|-------|

| 1.                                               | 1.     FR4 using the recommended pad lay-out     50°C/W     1.0 |                      | 1.0W  |

| 2.FR4 with heat sink on board (6 cm2)35°C/W1.4 V |                                                                 | 1.4 W                |       |

| 3.                                               | 3.FR4 with heatsink (6 cm2) and ground20°C/W2.5W                |                      | 2.5W  |

| 4.                                               | 4. FR4 with 16 via holes and ground layer 15°C/W 3.3V           |                      | 3.3W  |

| 5.                                               | 5.FR4 with 16 via holes and external heatsink12°C/W4.2W         |                      | 4.2W  |

| 6.                                               | 6.         IMS floating in air (40cm²)         7°C/W         7W |                      | 7W    |

| 7.                                               | 7. IMS with external heatsink applied     2.5°C/W     20°       |                      | 20W   |

#### Figure 26: Thermal impedance of different packages (surface mount vs. insertion)

### TN1258

Thermal design and applications

Figure 27: Thermal impedance of different packages (SO20 vs. PowerSO-20/36)

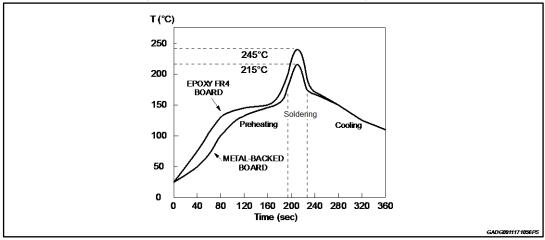

# 4 Soldering information

The soldering process causes considerable thermal stress to a semiconductor component. This has to be minimized to ensure a reliable and extended lifetime of the device.

PowerSO-20/36 are certified as MSL3 according to Jedec STD 020A

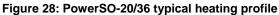

As reflow techniques are the most common in surface mounting, typical heating profiles are given in *Figure 28: "PowerSO-20/36 typical heating profile"*, with a preheating at 130 - 150 °C for 80 -100 seconds, either for mounting on FR4 epoxy substrate or mounting on metal-backed boards (IMS). Peak temperature should be at least 30 °C higher than the melting point of the solder chosen.

## 5 Reliability data

The information presented in this section shows that PowerSO-20/36 are able to work reliably in severe environments, like automotive, where the requested reliability target is 1 ppm failure rate.

In order to evaluate the reliability behavior of the present package a complete qualification program was compiled with two test vehicles:

- TDA7350A (Audio Power Amplifier)

- ABS voltage regulator

A list of the tests, their features and the failure modes associated to these tests is given in *Table 7: "Reliability tests description"*.

| Test                                           | Features                                                                   | Purpose                                                                                            |

|------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| High Temperature<br>Reverse Bias<br>(H.T.R.B.) | Reverse biased device at elevated temperature                              | To detect surface defects like poor passivation and contamination                                  |

| Operating Life Test<br>(O.L.T.)                | Device submitted to application conditions                                 | To put in evidence thermomechanical<br>stresses induced by internal power<br>dissipation           |

| Thermal Humidity Bias<br>(T.H.B.)              | Biased in presence of steam                                                | Metal corrosion detection                                                                          |

| Power ambient                                  | Detect cracked die, wire bond<br>breaking, mechanical damage<br>to package | -                                                                                                  |

| Pressure Pot Test<br>(P.P.T.)                  | High temperature and<br>pressure with saturated steam                      | Electrochemical and galvanic corrosion                                                             |

| Solderability Test<br>(S.T.)                   | Verifies tinning process                                                   | Detects poor solder joint                                                                          |

| Environmental<br>Sequence (E.S.)               | Thermal cycling combined<br>with pressure pot                              | To study corrosion mechanism after<br>thermal cycling stress                                       |

| Surface Mount (S.M.)                           | Simulation of soldering<br>process in the presence of<br>humidity          | To point out the package resistance to the tresses due to surface mounting in presence of humidity |

| Resistance to Solvents (R.S.)                  | Mil-Std-883 Meth. 2015                                                     | To verify the marking permanency                                                                   |

#### Table 7: Reliability tests description

Table 8: "ABS voltage regulator (die size 5.3 x 5.28 mm)" and Table 9: "TDA7350A (Bridge Audio Amplifier)" show the results of the qualification; all the package and die oriented tests were passed successfully. The test conditions and acceptance criteria are the same as those for standard power packages.

## Reliability data

## TN1258

| Table 8: ABS | voltage regulat   | or (die size | e 5.3 x 5.28 mm) |

|--------------|-------------------|--------------|------------------|

|              | , tonugo i ogului |              |                  |

| Test   | Condition                                                                       | Sample            | Duration    | Failure |

|--------|---------------------------------------------------------------------------------|-------------------|-------------|---------|

| T.C.T. | T <sub>amb</sub> = -65 °C to +150° C air to air                                 | 153 pcs. x 3 lots | 1000 cycles | 0       |

| 1.0.1. |                                                                                 | 153 pcs. x 1 lots | 2000 cycles | 0       |

| T.S.T. | $T_{amb}$ = -65 °C to +150 °C liquid to liquid                                  | 60 pcs. x 3 lots  | 1000 cycles | 0       |

| P.P.T. | T <sub>amb</sub> = 121 °C P = 2 atm                                             | 77 pcs. x 3 lots  | 500 hours   | 0       |

| S.T. 1 | T <sub>amb</sub> = 215 °C; precond. 8h vapor                                    | 22 pcs. x 3 lots  | -           | 0       |

| S.T. 2 | $T_{amb} = 215 \text{ °C}$ ; precond. 8h vapor at<br>$T_{amb} = 155 \text{ °C}$ | 22 pcs. x 3 lots  | -           | 0       |

| E.S.   | 100 cycles at -65 °C to +150 °C 48 hours of PPT at 3 atm (5 times repeated)     | 25 pcs. x 3 lots  | _           | 0       |

| S.M.   | 24 hours at 85 °C/85% dipping at 260 °C<br>10" 48 hours PPT at 2.5 atm          | 22 pcs. x 3 lots  | _           | 0       |

| R.S.   | Mil-Std-883 Meth 2015         22 pcs. x 3 lots         -                        |                   | -           | 0       |

| Test     | Condition                                                                             | Sample           | Duration   | Failure |

|----------|---------------------------------------------------------------------------------------|------------------|------------|---------|

| H.T.R.B. | V <sub>s</sub> = 18 V; T <sub>J</sub> = 150 °C                                        | 77 pcs. x 3 lots | 200 hours  | 0       |

| O.L.T.   | $V_s = 16 \text{ V}; \text{ P}_d = 10 \text{ W}; \text{ T}_J = 150^{\circ} \text{ C}$ | 90 pcs. x 3 lots | 2000 hours | 0       |

| T.H.B.   | Vs = 18 V; T <sub>amb</sub> = 85 °C; R.H. = 85%                                       | 77 pcs. x 3 lots | 2000 hours | 0       |

| P.T.C.   | $V_s = 14 V$ ; $t_{on} = t_{off} = 5$ ";<br>$T_{amb} = -40 to +85 $ °C;               | 33 pcs. x 3 lots | 1000 hours | 0       |

TN1258

The PowerSO-20/36 packages, belonging to innovative surface mount power package family, have been introduced (Jedec MO-166 registered).

They have been designed specifically for the surface mount industry and they can replace Multiwatt in many applications.

The main advantages of PowerSO-20/36 are:

- 1. Good thermal characteristics. They are able to handle die with the same size as Multiwatt.

- 2. Versatility. A wide variety of intelligent power products with a wide range of options can be managed.

- 3. Symmetrical package design. Slug up and slug down versions can be delivered giving more opportunities to the customers for power dissipation.

- 4. High power density through reduced package volume and height.

- 5. Compatibility with automatic placement equipment and soldering techniques used in surface-mount assembly. Reliable and inspectable solder joints can be achieved.

- 6. High reliability in terms of hermeticity. The correct choice of the materials and particular design features allow the PowerSO-20/36 to pass successfully severe tests like pressure pot and die penetrant.

It was demonstrated that this package family well meets the high demands in surfacemount power applications, where power ICs are becoming more and and more common.

Few years ago, a new component of this package family has been launched in production: the PowerSO-46 having 46 pins and 0.5 mm lead pitch, serving power train and safety automotive applications.

# 7 Revision history

Table 10: Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 23-Nov-2017 | 1        | Initial release. |

#### TN1258

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved