- Organization:

- DRAM: 262144 Words  $\times$  16 Bits SAM: 256 Words  $\times$  16 Bits

- Single 5.0-V Power Supply (±10%)

- Dual-Port Accessibility Simultaneous and Asynchronous Access From the DRAM and Serial-Address Memory (SAM) Ports

- Write-Per-Bit Function for Selective Write to Each I/O of the DRAM Port

- Byte Write Function for Selective Write to Lower Byte (DQ0-DQ7) or Upper Byte (DQ8-DQ15) of the DRAM Port

- 4-Column or 8-Column Block-Write Function for Fast Area-Fill Operations

- Enhanced Page Mode for Faster Access With Extended-Data-Output (EDO) Option for Faster System Cycle Time

- CAS-Before-RAS (CBR) and Hidden Refresh Functions

- Long Refresh Period Every 8 ms (Maximum)

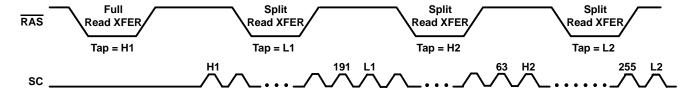

- Full-Register-Transfer Function Transfers

Data from the DRAM to the Serial Register

- Split-Register-Transfer Function Transfers

Data from the DRAM to One-Half of the

Serial Register While the Other Half is

Outputing Data to the SAM Port

- 256 Selectable Serial Register Starting Points

- Programmable Split-Register Stop Point

- Up to 55-MHz Uninterrupted Serial-Data Streams

- 3-State Serial Outputs for Easy Multiplexing of Video Data Streams

- All Inputs/Outputs and Clocks TTL Compatible

- Compatible With JEDEC Standards

- Designed to Work With the Texas Instruments (TI™) Graphics Family

- Fabricated Using TI's Enhanced Performance Implanted CMOS (EPIC™) Process

# performance ranges

|            | ACCESS TIME<br>ROW ENABLE<br>tRAC<br>(MAX) | ACCESS TIME<br>SERIAL DATA<br><sup>t</sup> SCA<br>(MIN) | DRAM PAGE<br>CYCLE TIME<br><sup>t</sup> PC<br>(MIN) | DRAM EDO<br>CYCLE TIME<br>tPC<br>(MIN) | SERIAL<br>CYCLE TIME<br><sup>t</sup> SCC<br>(MIN) | OPERATING CURRENT<br>SERIAL PORT STANDBY<br>ICC <sub>1</sub><br>(MAX) |

|------------|--------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|----------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------|

| - 60 Speed | 60 ns                                      | 15 ns                                                   | 35 ns                                               | 30 ns                                  | 18 ns                                             | 180 mA                                                                |

| - 70 Speed | 70 ns                                      | 20 ns                                                   | 40 ns                                               | 30 ns                                  | 22 ns                                             | 165 mA                                                                |

#### Table 1. Device Option Table

| DEVICE | POWER SUPPLY VOLTAGE | BLOCK-WRITE CAPABILITY | PAGE/EDO OPERATION |

|--------|----------------------|------------------------|--------------------|

| 55165  | $5.0~V\pm0.5~V$      | 4-column               | Page               |

| 55166  | $5.0~V\pm0.5~V$      | 4-column               | EDO                |

| 55175  | $5.0~V\pm0.5~V$      | 8-column               | Page               |

| 55176  | 5.0 V $\pm$ 0.5 V    | 8-column               | EDO                |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI and EPIC are trademarks of Texas Instruments Incorporated.

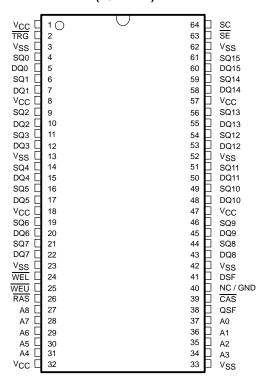

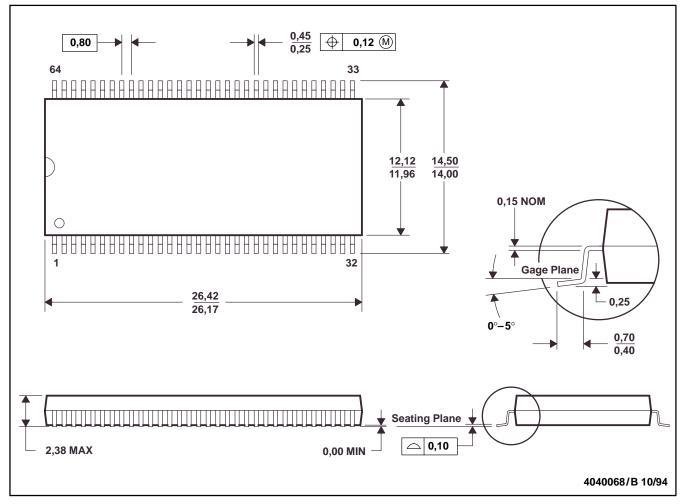

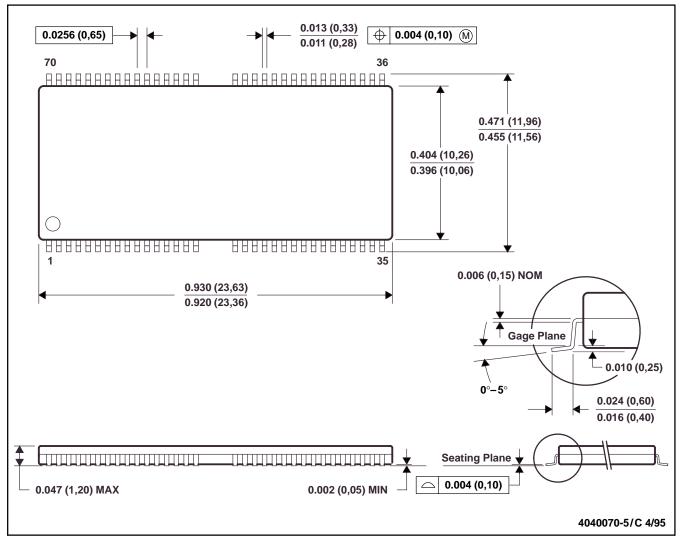

#### DGH PACKAGE (TOP VIEW)

|          | PIN NOMENCLATURE                             |

|----------|----------------------------------------------|

| A0-A8    | Address Inputs                               |

| RAS      | Row-Address Strobe                           |

| CAS      | Column-Address Strobe                        |

| DSF      | Special Function Select                      |

| TRG      | Output Enable, Transfer Select               |

| WEL, WEU | Write Enable, Byte Select, Write Mask Select |

| DQ0-DQ15 | DRAM Data I/O                                |

| SC       | Serial Clock                                 |

| SE       | Serial Enable                                |

| SQ0-SQ15 | Serial Data Output                           |

| QSF      | Special Function Output                      |

| Vcc      | Power Supply                                 |

| Vss      | Ground                                       |

| NC/GND   | No Connect/Ground                            |

|          | (Important: not connected internally to VSS) |

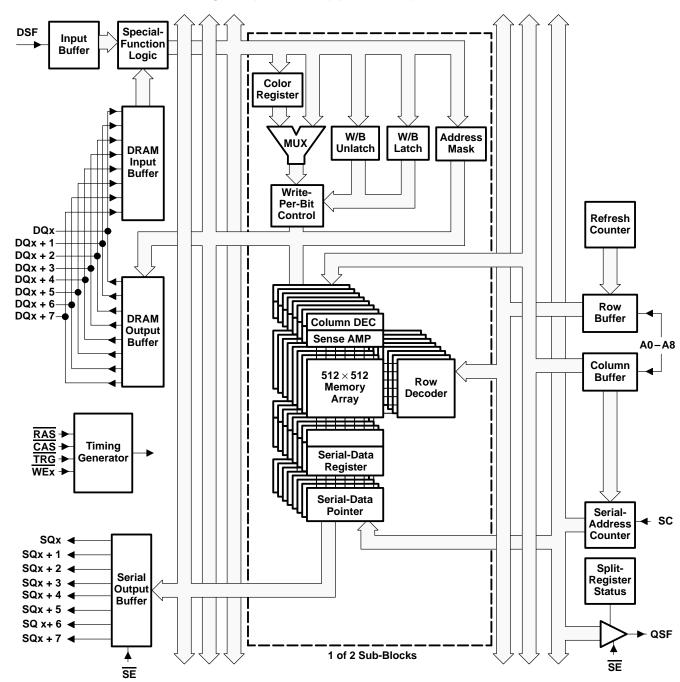

#### description

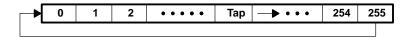

The TMS551xx multiport video RAMs are high-speed dual-ported memory devices. Each consists of a dynamic random-access memory (DRAM) organized as 262 144 words of 16 bits each interfaced to a serial-data register [serial-access memory (SAM)] organized as 256 words of 16 bits each. These devices support three basic types of operation: random access to and from the DRAM, serial access from the serial register, and transfer of data from the DRAM to the SAM. Except during transfer operations, these devices can be accessed simultaneously and asynchronously from the DRAM and SAM ports.

The TMS551xx multiport video RAMs provide several functions designed to provide higher system-level bandwidth and to simplify design integration on both the DRAM and SAM ports (see Table 2). On the DRAM port, greater pixel draw rates are achieved by the block-write function. The TMS5516x devices' 4-column block-write function allows 16 bits of data (present in an on-chip color-data register) to be written to any combination of four adjacent column-address locations, up to a total of 64 bits of data per CAS cycle time. Similarly, the TMS5517x devices' 8-column block-write function allows 16 bits of data to be written to any combination of eight adjacent column-address locations, up to a total of 128 bits of data per CAS cycle time. Also on the DRAM port, the write-per-bit (or write mask) function allows masking of any combination of the 16 DQs on any write cycle. The persistent write-per-bit function uses a mask register that, once loaded, can be used on subsequent write cycles without reloading. All TMS551xx devices offer byte control. Byte control can be applied in write cycles, block-write cycles, load-write-mask-register cycles, and load-color-register cycles. The TMS551xx devices offer enhanced page-mode operation that results in faster access time. The TMS551x6 devices also offer extended-data-output (EDO) mode. The EDO mode is effective in both the page-mode and the standard DRAM cycles.

The TMS551xx devices offer a split-register-transfer (DRAM to SAM) function. This feature enables real-time register load implementation for continuous serial-data streams without critical timing requirements. The serial register is divided into a high half and a low half. While one half is being read out of the SAM port, the other half can be loaded from the DRAM. For applications not requiring real-time register load (for example, loads done during CRT-retrace periods), the full-register-transfer operation is retained to simplify system design.

The SAM port is designed for maximum performance. Data can be accessed from the SAM at serial rates up to 55 MHz. A separate output, QSF, is included to indicate which half of the serial register is active. Refreshing the SAM is not required because the data register that comprises the SAM is static.

All inputs, outputs, and clock signals on the TMS551xx devices are compatible with Series 74 TTL. All address lines and data-in lines are latched on-chip to simplify system design. All data-out lines are unlatched to allow greater system flexibility.

All TMS551xx employ TI's state-of-the-art EPIC scaled-CMOS, double-level polysilicon/polycide gate technology combining very high performance with improved reliability.

All TMS551xx are offered in a 64-pin small-outline gull-wing-leaded package (DGH suffix) for direct surface mounting.

The TMS551xx video RAMs and other TI multiport video RAMs are supported by a broad line of graphics processors and control devices from Texas Instruments.

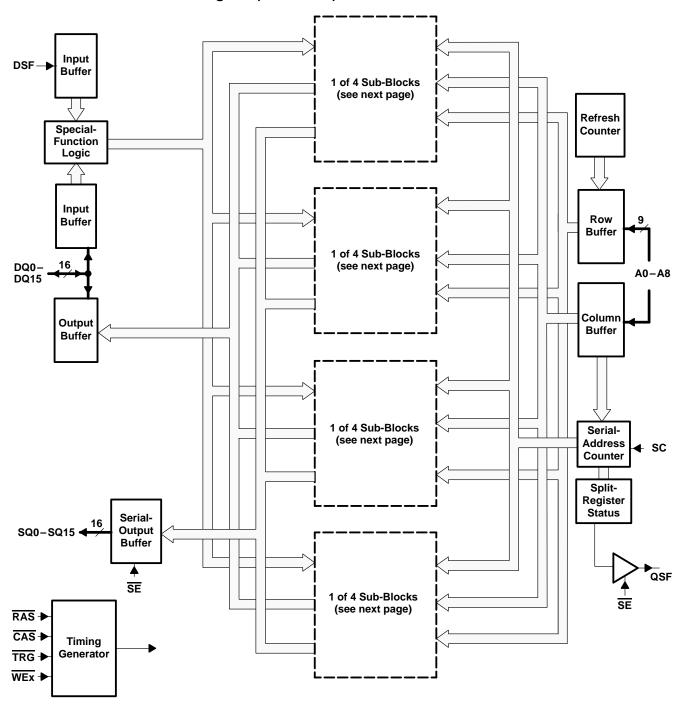

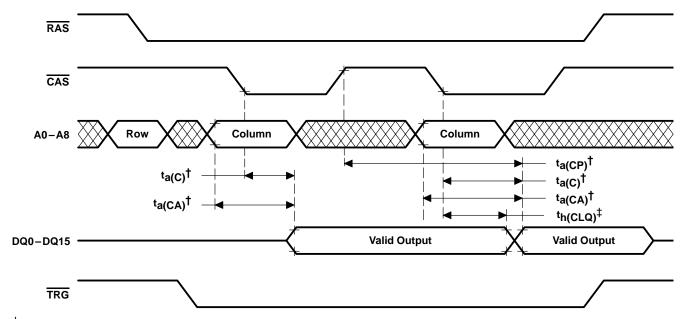

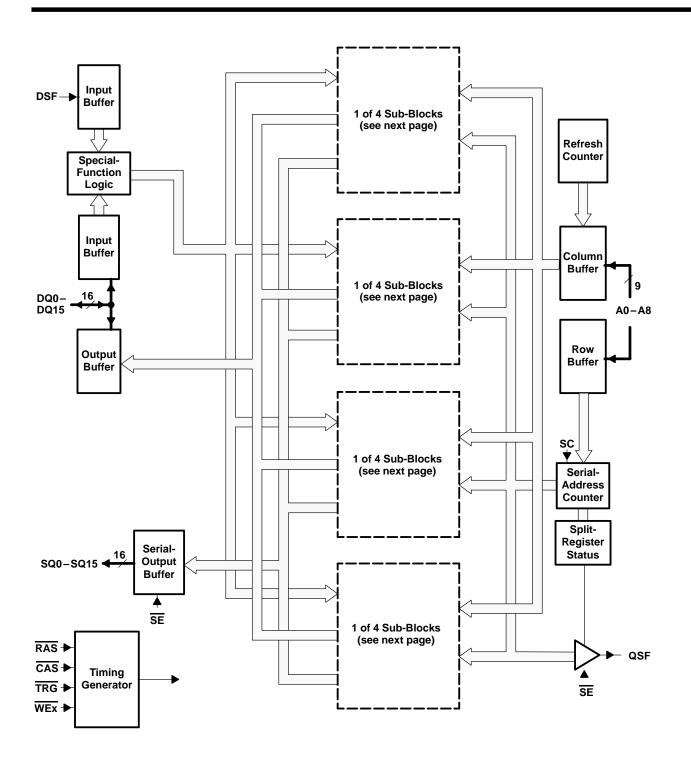

# 4-column functional block diagram (TMS5516x)

# 4-column functional block diagram (TMS5516x) (continued)

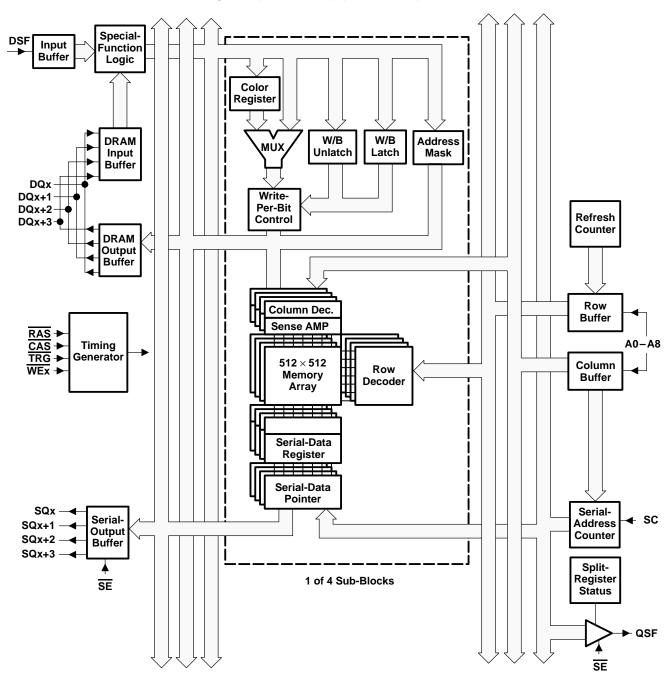

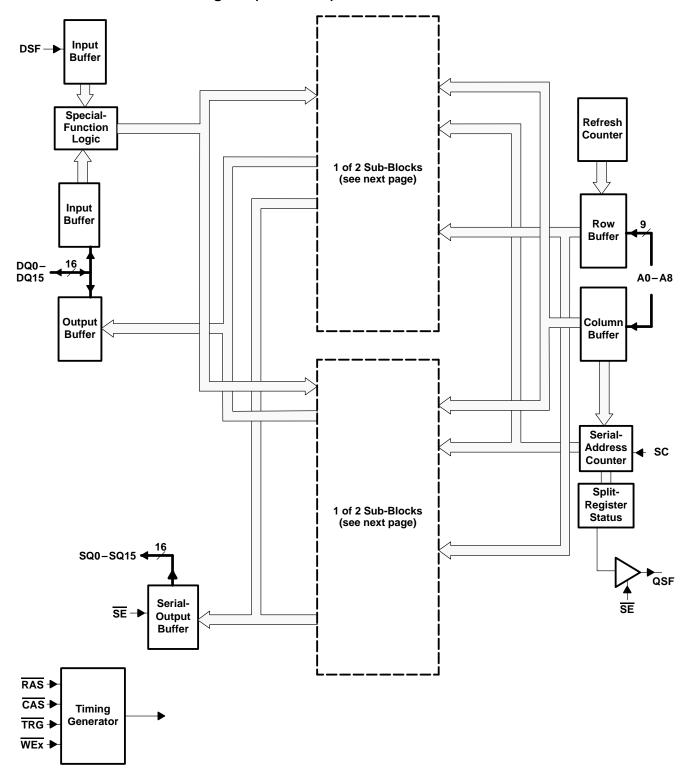

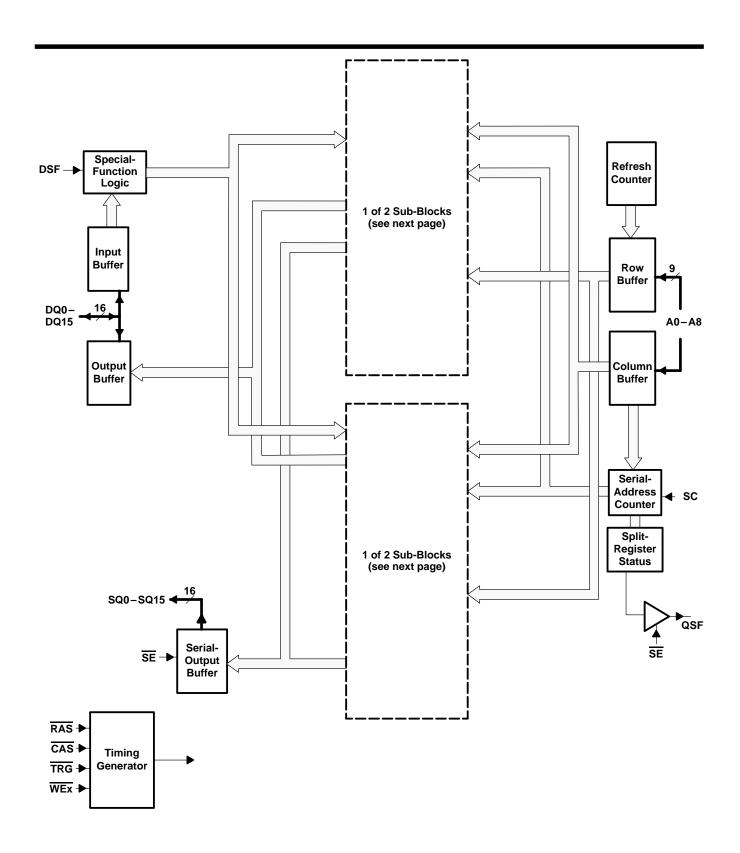

# 8-column functional block diagram (TMS5517x)

# 8-column functional block diagram (TMS5x17x) (continued)

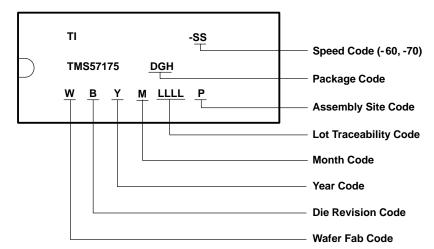

# TMS55165, TMS55166, TMS55175, TMS55176 262144 BY 16-BIT MULTIPORT VIDEO RAM

SMVS463 - DECEMBER 1995

#### **Table 2. Function Table**

|                                                 |     | RAS | FALL |     | CAS<br>FALL | ADDRESS         |               | DQ0-DQ15 <sup>†</sup> |               | MNE  |

|-------------------------------------------------|-----|-----|------|-----|-------------|-----------------|---------------|-----------------------|---------------|------|

| FUNCTION                                        | CAS | TRG | WEx‡ | DSF | DSF         | RAS             | CAS§          | RAS                   | WEU<br>CAS    | CODE |

| Reserved (do not use)                           | L   | L   | L    | L   | Х           | Х               | Х             | Х                     | Х             | _    |

| CBR refresh (no reset) and stop-point set ¶     | L   | Х   | L    | I   | Х           | Stop<br>Point#  | Х             | Х                     | Х             | CBRS |

| CBR refresh (option reset)                      | L   | Х   | Н    | L   | Х           | Х               | Х             | Χ                     | Х             | CBR  |

| CBR refresh (no reset) <sup>☆</sup>             | L   | Х   | Η    | Н   | Х           | Х               | Х             | Х                     | Х             | CBRN |

| Full-register transfer                          | Н   | L   | Ħ    | L   | Х           | Row<br>Addr     | Tap<br>Point  | Х                     | Х             | RT   |

| Split-register transfer                         | Н   | L   | Н    | Н   | Х           | Row<br>Addr     | Tap<br>Point  | Х                     | Х             | SRT  |

| DRAM write (nonmasked)                          | Н   | Ι   | н    | L   | L           | Row<br>Addr     | Col<br>Addr   | Х                     | Valid<br>Data | RW   |

| DRAM write (nonpersistent write-per-bit)        | Н   | Ħ   | L    | L   | L           | Row<br>Addr     | Col<br>Addr   | Write<br>Mask         | Valid<br>Data | RWM  |

| DRAM write (persistent write-per-bit)           | Н   | Η   | L    | L   | L           | Row<br>Addr     | Col<br>Addr   | Х                     | Valid<br>Data | RWM  |

| DRAM block write (nonmasked) <sup>□</sup>       | Н   | Η   | Ι    | L   | Н           | Row<br>Addr     | Block<br>Addr | Х                     | Col<br>Mask   | BW   |

| DRAM block write (nonpersistent write-per-bit)□ | Н   | Η   | L    | L   | Н           | Row<br>Addr     | Block<br>Addr | Write<br>Mask         | Col<br>Mask   | BWM  |

| DRAM block write (persistent write-per-bit)□    | Н   | н   | L    | L   | Н           | Row<br>Addr     | Block<br>Addr | Х                     | Col<br>Mask   | BWM  |

| Load write-mask register <sup>◊</sup>           | Н   | н   | Н    | н   | L           | Refresh<br>Addr | Х             | Х                     | Write<br>Mask | LMR  |

| Load color register                             | Н   | Н   | Н    | Н   | Н           | Refresh<br>Addr | Х             | Х                     | Color<br>Data | LCR  |

#### Legend:

X = Don't care

Col Mask = H: Write to address/column enabled

Write Mask = H: Write to I/O enabled

$<sup>\</sup>dagger$  DQ0-DQ15 are latched on either the falling edge of  $\overline{\text{CAS}}$  or the first falling edge of  $\overline{\text{WEx}}$ , whichever occurs later.

<sup>‡</sup> Logic L is selected when either or both WEL and WEU are low.

<sup>§</sup> The column address, the block address, or the tap point is latched on the falling edge of CAS depending upon which function is executed.

<sup>¶</sup>CBRS cycle should be performed immediately after the power-up initialization for stop-point mode.

<sup>#</sup>A0-A3, A8: don't care; A4-A7: stop-point code

CBR refresh (option reset) mode ends persistent write-per-bit mode and stop-point mode.

<sup>★</sup>CBR refresh (no reset) mode does not end persistent write-per-bit mode or stop-point mode.

<sup>□</sup> For 4-column block write (TMS5516x), block address is A2 – A8; for 8-column block write (TMS5517x), block address is A3 – A8.

<sup>♦</sup> Load-write-mask-register cycle sets the persistent write-per-bit mode. The persistent write-per-bit mode is reset only by the CBR (option reset) cycle.

**Table 3. Pin Description Versus Operational Mode**

| PIN               | DRAM                                                                                             | TRANSFER                       | SAM                                    |

|-------------------|--------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------|

| A0-A8             | Row, column address                                                                              | Row address, tap point         |                                        |

| RAS               | Row-address strobe                                                                               | Row-address strobe             |                                        |

| CAS               | Column-address strobe, DQ output enable                                                          | Tap-address strobe             |                                        |

| DSF               | Block-write enable Load-write-mask-register enable Load-color-register enable CBR (option reset) | Split-register-transfer enable |                                        |

| TRG               | DQ output enable                                                                                 | Transfer enable                |                                        |

| WEL<br>WEU        | Write enable, write-per-bit enable                                                               |                                |                                        |

| DQx               | DRAM data I/O, write mask                                                                        |                                |                                        |

| SC                |                                                                                                  |                                | Serial clock                           |

| SE                |                                                                                                  |                                | SQ output enable,<br>QSF output enable |

| SQx               |                                                                                                  |                                | Serial-data output                     |

| QSF               |                                                                                                  |                                | Serial-register status                 |

| V <sub>CC</sub> † | Power supply                                                                                     |                                |                                        |

| v <sub>ss</sub> † | Ground                                                                                           |                                |                                        |

| NC/GND            | Make no external connection or tie to system GND                                                 |                                |                                        |

<sup>†</sup> For proper device operation, all VCC pins must be connected to a 5.0-V supply and all VSS pins must be tied to ground.

#### pin definitions

#### address (A0-A8)

Eighteen address bits are required to decode one of 262 144 storage cell locations. Nine row-address bits are set up on pins A0–A8 and latched onto the chip on the falling edge of  $\overline{RAS}$ . Nine column-address bits are set up on pins A0–A8 and latched onto the chip on the falling edge of  $\overline{CAS}$ . All addresses must be stable on or before the falling edge of  $\overline{RAS}$  and the falling edge of  $\overline{CAS}$ .

In 4-column block-write operations (TMS5516x), column-address bits A0-A1 are ignored. Column-address bits A2-A8 become the block address that selects one of the 128 blocks in the active row. In 8-column block write operations (TMS5517x), column-address bits A0-A2 are ignored. Column address bits A3-A8 become the block address that selects one of the 64 blocks in the active row.

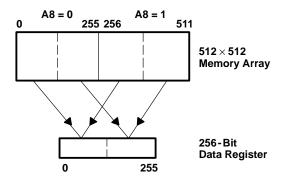

In full-register operations, column-address bit A8 selects which half of the active row in the DRAM is transferred to the SAM. Column address bits A0–A7 select one of 256 tap points (starting positions) for the serial-data output.

In split-register-transfer operations, column address bit A8 selects the DRAM half row. Column-address bit A7 is ignored. The internal serial-address counter identifies which half of the SAM is in use. If the high half of the SAM is in use, the low half of the SAM is loaded with the low half of the DRAM half row, and vice versa. Column-address bits A0-A6 select one of 127 tap points (starting locations) for the serial output. Locations 127 and 255 are not valid tap points in split-register-transfer operations. In stop-point mode, stop-point locations are not valid tap points in split-register-transfer operations.

#### row-address strobe (RAS)

The falling edge of RAS latches the states of the row address, CAS, DSF, TRG, WEL, and WEU, and the DQs onto the chip to initiate DRAM and transfer functions. RAS also functions as a DRAM output enable.

# TMS55165, TMS55166, TMS55175, TMS55176 262144 BY 16-BIT MULTIPORT VIDEO RAM

SMVS463 - DECEMBER 1995

#### column-address strobe (CAS)

The falling edge of <u>CAS</u> latches the states of the column address and DSF onto the chip to control DRAM and transfer functions. <u>CAS</u> also functions as a DRAM output enable.

#### special-function select (DSF)

DSF is latched on the falling edge of  $\overline{RAS}$  and the falling edge of  $\overline{CAS}$  to determine which functions are invoked on a particular cycle (see Table 2).

# output enable, transfer select (TRG)

TRG selects either DRAM or transfer operation as RAS falls. Holding TRG high on the falling edge of RAS selects the DRAM operation. Dropping TRG low on the falling edge of RAS selects the transfer operation. TRG also functions as DRAM output enable.

# write enable, write-per-bit select, byte select (WEL, WEU)

WEL and WEU select either the write mode or the read mode in a CAS cycle. Dropping either or both WEL and WEU low selects the write mode. Holding both WEL and WEU high selects the read mode. Holding either or both WEL and WEU low on the falling edge of RAS selects the write-per-bit operation. WEL and WEU provide byte control in DRAM operations. WEL controls the lower byte (DQ0-DQ7), and WEU controls the upper byte (DQ8-DQ15). Byte control can be applied in write cycles, block-write cycles, load-write-mask-register cycles, and load-color-register cycles.

## DRAM data I/O, write mask, column mask (DQ0-DQ15)

DQ0-DQ15 function as the DRAM input/output port in DRAM operations. In normal DRAM write cycles, all 16 bits of write data are latched on either the falling edge of  $\overline{CAS}$  or the first falling edge of  $\overline{WEx}$ , whichever occurs later. Similarly, the DQs are latched as write mask in load-mask-register cycles, as color data in load-color-register cycles, and as column mask in block-write cycles. In non-persistent write-per-bit cycles, the DQs are latched as the write mask on the falling edge of  $\overline{RAS}$ .

Data out is in the same polarity as data in. The 3-state output buffer provides direct TTL compatibility (no pullup resistor required) with a fan-out of one Series 74 TTL load. The outputs are in the high-impedance (floating) state until  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{TRG}$  have all been brought low in read cycles. For the TMS551x5 devices, the outputs remain valid until  $\overline{CAS}$  is brought high,  $\overline{TRG}$  is brought high, or  $\overline{WEx}$  is brought low. For the TMS551x6 devices, the outputs remain valid until both  $\overline{RAS}$  and  $\overline{CAS}$  are brought high,  $\overline{TRG}$  is brought high, or  $\overline{WEx}$  is brought low.

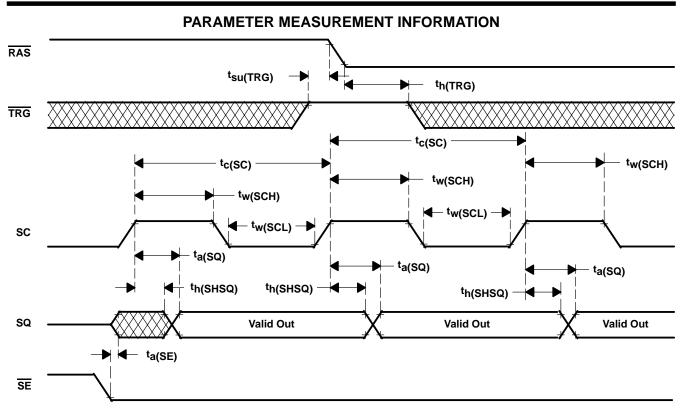

#### serial clock (SC)

The rising edge of SC increments the internal serial-address counter and accesses serial data at the next SAM location.

#### serial enable (SE)

SE functions as the output enable for SQ0-SQ15 and QSF. SE low enables the serial-data output. SE high disables the serial-data output. Holding SE high does not disable the serial clock SC. The rising edge of SC automatically increments the internal serial-address counter regardless of the state of SE.

#### serial data outputs (SQ0-SQ15)

SQ0-SQ15 function as the SAM output port. The 3-state output buffer provides direct TTL compatibility (no pullup resistors) with a fan-out of one Series 74 TTL load. Serial data is accessed from the SAM on the rising edge of SC. SE low enables the outputs. The outputs are in the high-impedance (floating) state when disabled.

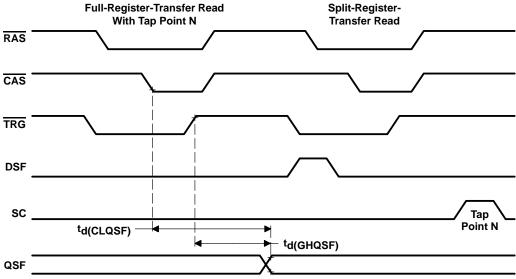

#### special-function output (QSF)

QSF is an output pin that indicates which half of the SAM is being accessed. QSF is low when the internal serial-address counter points to the lower (least significant) 128 bits of the SAM. QSF is high when the internal serial-address counter points to the higher (most significant) 128 bits of SAM. QSF is in the high-impedance state when  $\overline{SE}$  is high.

# functional operation description random access operation

**Table 4. DRAM Function Table**

|                                                 |     | RAS | FALL |     | CAS<br>FALL | ADDR            | ESS           | DQ0-          | DQ15 <sup>†</sup> | MNE  |

|-------------------------------------------------|-----|-----|------|-----|-------------|-----------------|---------------|---------------|-------------------|------|

| FUNCTION                                        | CAS | TRG | WEx‡ | DSF | DSF         | RAS             | CAS§          | RAS           | WEU<br>CAS        | CODE |

| Reserved (do not use)                           | L   | L   | L    | L   | Х           | Х               | Х             | Х             | Х                 | _    |

| CBR refresh (no reset) and stop-point set¶      | L   | Х   | L    | Н   | Х           | Stop<br>Point#  | Х             | Х             | Х                 | CBRS |

| CBR refresh (option reset)                      | L   | Х   | Н    | L   | Х           | Х               | Х             | Х             | Х                 | CBR  |

| CBR refresh (no reset) <sup>☆</sup>             | L   | Х   | Н    | Ι   | Х           | Х               | Х             | Х             | Х                 | CBRN |

| DRAM write (nonmasked)                          | Н   | Н   | Н    | L   | L           | Row<br>Addr     | Col<br>Addr   | Х             | Valid<br>Data     | RW   |

| DRAM write (nonpersistent write-per-bit)        | Н   | Н   | L    | L   | L           | Row<br>Addr     | Col<br>Addr   | Write<br>Mask | Valid<br>Data     | RWM  |

| DRAM write (persistent write-per-bit)           | Н   | Н   | L    | L   | L           | Row<br>Addr     | Col<br>Addr   | Х             | Valid<br>Data     | RWM  |

| DRAM block write (nonmasked) <sup>□</sup>       | Н   | Н   | Н    | L   | Н           | Row<br>Addr     | Block<br>Addr | Х             | Col<br>Mask       | BW   |

| DRAM block write (nonpersistent write-per-bit)□ | Н   | Н   | L    | L   | Н           | Row<br>Addr     | Block<br>Addr | Write<br>Mask | Col<br>Mask       | BWM  |

| DRAM block write (persistent write-per-bit)□    | Н   | Н   | L    | L   | Н           | Row<br>Addr     | Block<br>Addr | Х             | Col<br>Mask       | BWM  |

| Load write-mask register <sup>◊</sup>           | Н   | Н   | Н    | Н   | L           | Refresh<br>Addr | Х             | Х             | Write<br>Mask     | LMR  |

| Load color register                             | Н   | Н   | Н    | Н   | Н           | Refresh<br>Addr | Х             | Х             | Color<br>Data     | LCR  |

#### Legend:

X = Don't care

Col Mask = H: Write to address/column enabled

Write Mask = H: Write to I/O enabled

‡ Logic L is selected when either or both WEL and WEU are low.

<sup>†</sup>DQ0-DQ15 are latched on either the falling edge of CAS or the first falling edge of WEx, whichever occurs later.

<sup>§</sup> The column address, the block address, or the tap point is latched on the falling edge of CAS depending upon which function is executed.

<sup>¶</sup> CBRS cycle should be performed immediately after the power-up for stop-point mode.

<sup>#</sup> A0-A3, A8: don't care; A4-A7: stop-point code

CBR refresh (option reset) mode ends persistent write-per-bit mode and stop-point mode.

**<sup>☆</sup>CBR** refresh (no reset) mode does not end persistent write-per-bit mode or stop-point mode.

<sup>□</sup> For 4-column block write (TMS5516x), block address is A2−A8; for 8-column block write (TMS5517x), block address is A3−A8.

<sup>♦</sup> Load-write-mask-register cycle sets the persistent write-per-bit mode. The persistent write-per-bit mode is reset only by the CBR (option reset) cycle.

#### refresh

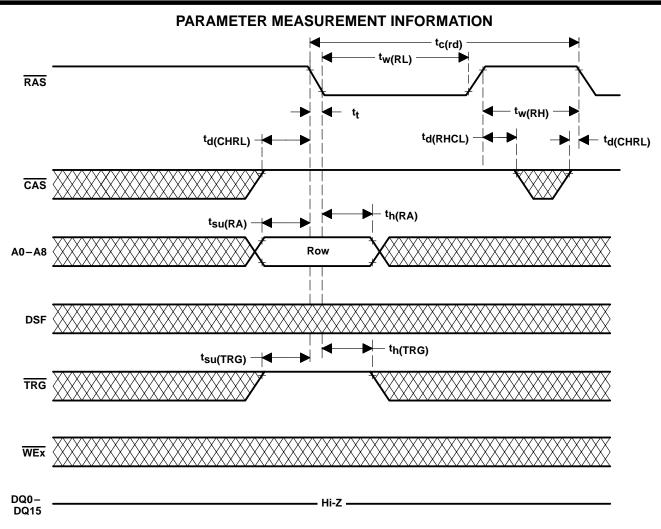

# CAS-before-RAS (CBR) refresh

CBR refreshes are accomplished when CAS is brought low earlier than RAS. The external row address is ignored, and the refresh row address is generated internally. Three types of CBR refresh cycles are available. The CBR refresh (option reset) ends the persistent write-per-bit mode and the stop-point mode. The CBRN (no reset) and CBRS (no reset and stop point set) refreshes do not end the persistent write-per-bit mode or the stop-point mode. The 512 rows of the DRAM do not necessarily need to be refreshed consecutively as long as the entire refresh is completed within the required time period, t<sub>rf(MA)</sub>. The output buffers remain in the high-impedance state during the CBR type refresh cycles regardless of the state of TRG.

#### hidden refresh

A hidden refresh is accomplished by holding CAS low in the DRAM read cycle and cycling RAS. The output data of the DRAM read cycle remains valid while the refresh is carried out. Like the CBR refresh, the refreshed row addresses are generated internally during the hidden refresh.

#### RAS-only refresh

A RAS-only refresh is accomplished by cycling RAS at every row address. Unless CAS and TRG are low, the output buffers remain in the high-impedance state to conserve power. Externally generated addresses must be supplied during  $\overline{RAS}$ -only refresh. Strobing each of the 512 row addresses with  $\overline{RAS}$  causes all bits in each row to be refreshed.

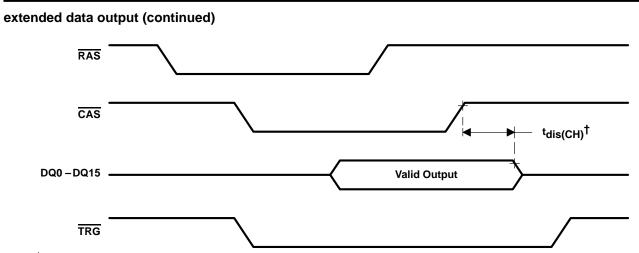

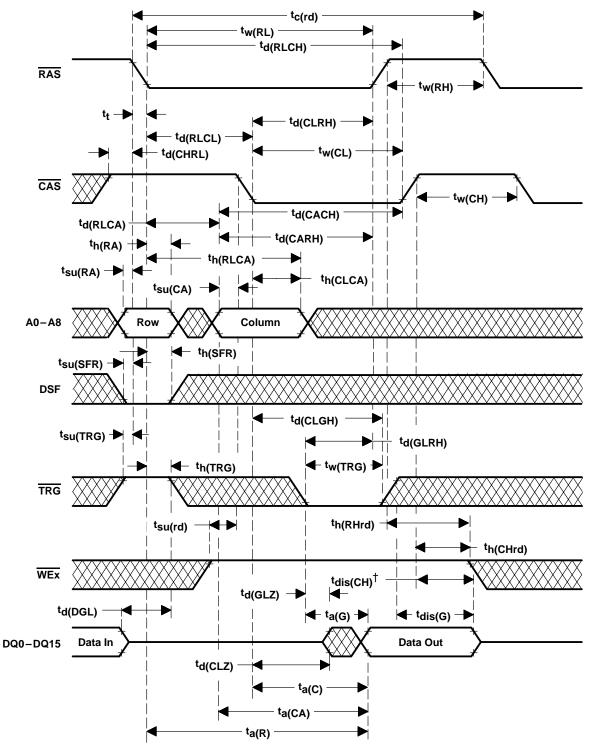

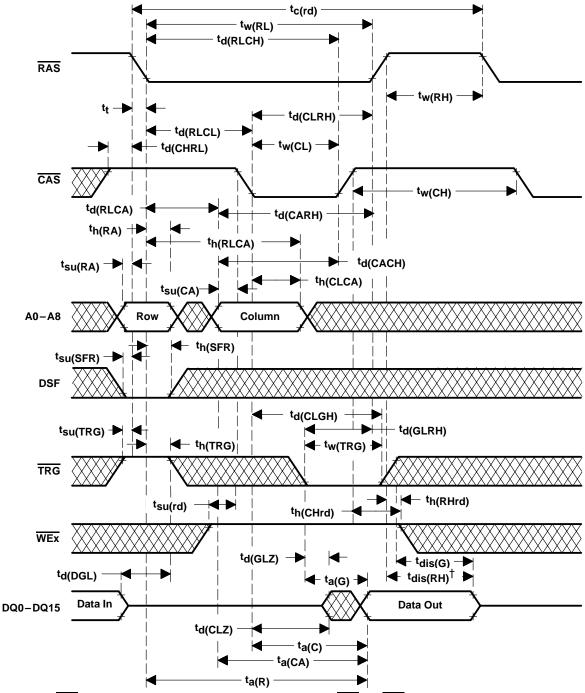

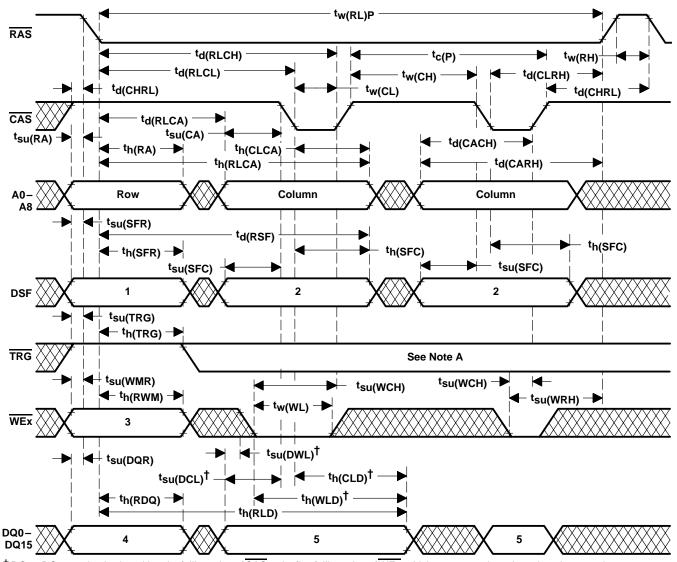

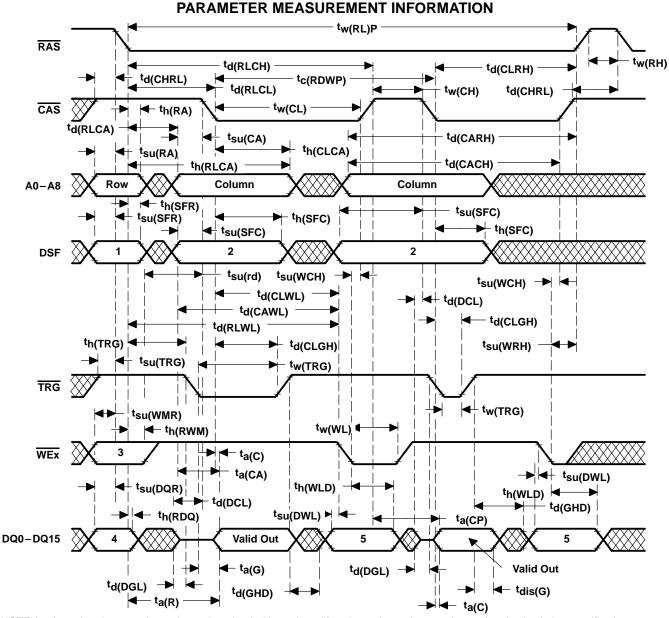

#### enhanced page mode (TMS551x5)

Enhanced page mode allows faster memory access by keeping the same row address while selecting random column addresses. The maximum RAS low time and minimum CAS page cycle time are used to determine the number of columns that can be accessed.

Unlike conventional page mode, the enhanced page mode allows the TMS551x5 to operate at a higher data bandwidth. Data retrieval begins as soon as the column address is valid rather than when CAS transitions low. A valid column address can be presented immediately after the row-address hold time has been satisfied, usually well in advance of the falling edge of  $\overline{CAS}$ . In this case, data is obtained after  $t_{a(C)}$  max (access time from  $\overline{\text{CAS}}$  low) if  $t_{a(CA)}$  max (access time from column address) has been satisfied.

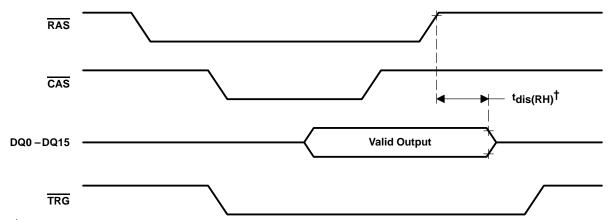

## extended data output (TMS551x6)

The TMS551x6 features extended data output during DRAM accesses. While  $\overline{RAS}$  and  $\overline{TRG}$  are low, the DRAM output remains valid even when CAS returns high. The output remains valid until WEx is low, TRG is high, or both CAS and RAS are high (see Figures 1, 2, and 3). The extended data-output mode functions in all read cycles including DRAM read, page-mode read, and read-modify-write cycles.

† See "switching characteristics over recommended ranges of supply voltage and operating free-air temperature" table.

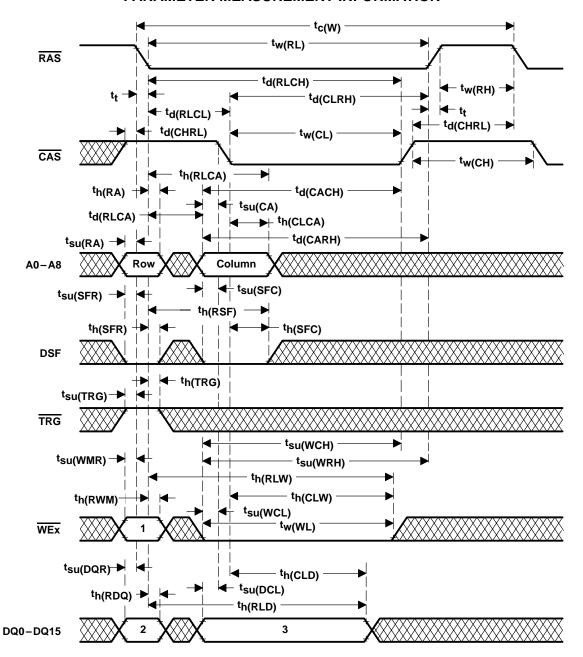

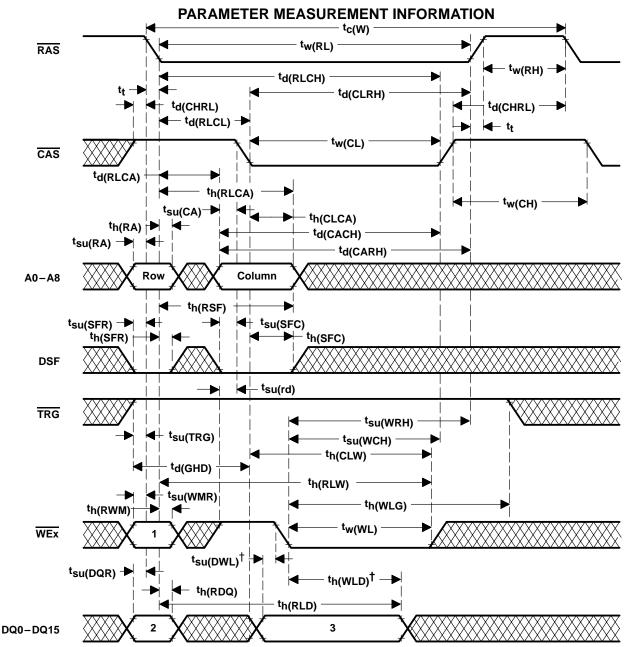

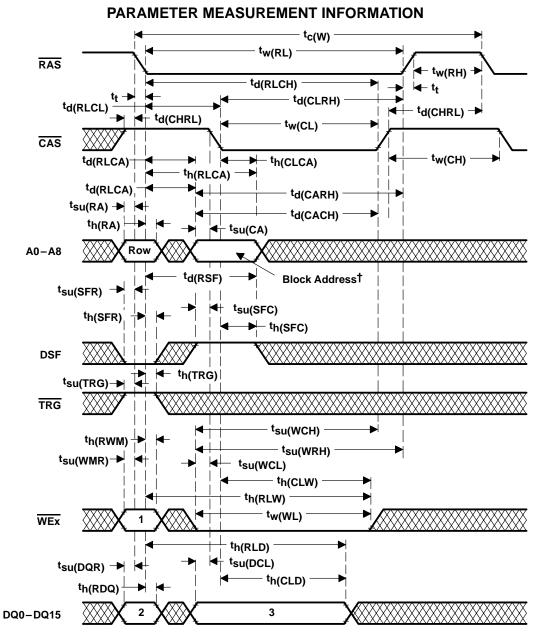

Figure 1. DRAM Read Cycle With RAS-Controlled Output (TMS551x6)

<sup>†</sup> See "switching characteristics over recommended ranges of supply voltage and operating free-air temperature" table.

Figure 2. DRAM Read Cycle With CAS-Controlled Output (TMS551x6)

<sup>†</sup> See "switching characteristics over recommended ranges of supply voltage and operating free-air temperature" table.

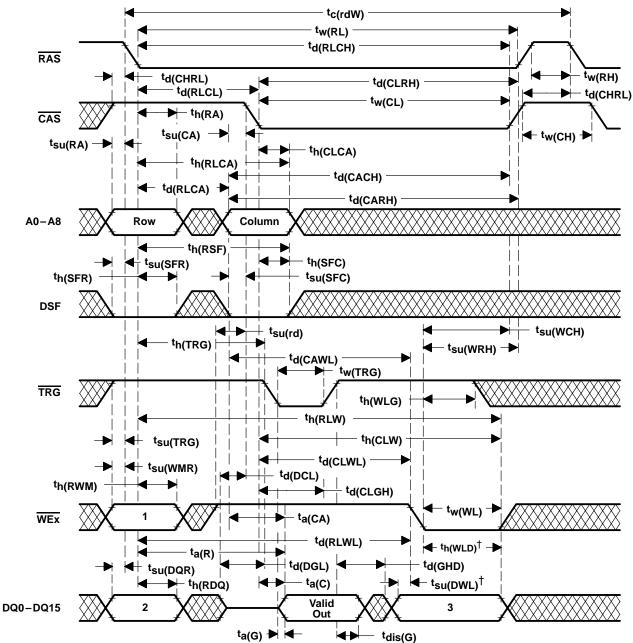

Figure 3. DRAM Page-Read Cycle With Extended Data Output (TMS551x6)

<sup>‡</sup> See "timing requirements over recommended ranges of supply voltage and operating free-air temperature" table.

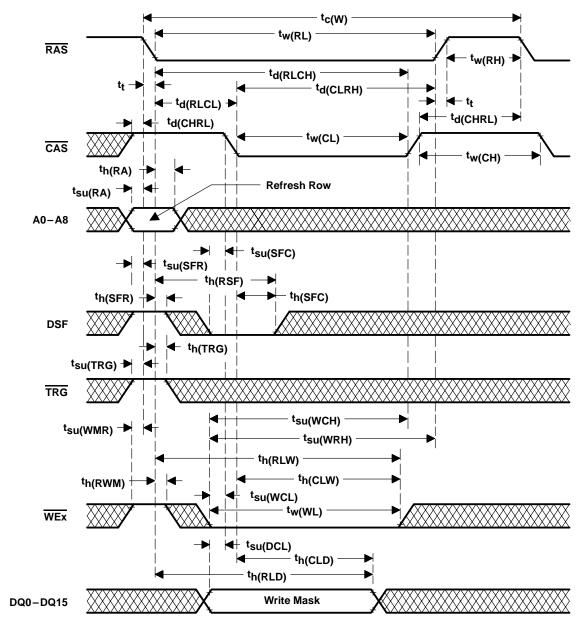

#### byte-write

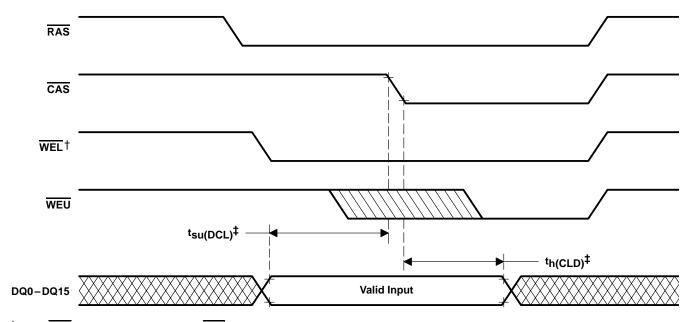

Byte-write operations can be applied in DRAM-write cycles, block-write cycles, load-write-mask-register cycles, and load-color-register cycles. Holding either or both  $\overline{WEL}$  and  $\overline{WEU}$  low selects the write mode. In normal write cycles,  $\overline{WEL}$  enables data to be written to the lower byte (DQ0-DQ7) and  $\overline{WEU}$  enables data to be written to the upper byte (DQ8-DQ15). For early-write cycles, one  $\overline{WEx}$  is brought low before  $\overline{CAS}$  falls. The other  $\overline{WEx}$  can be brought low before or after  $\overline{CAS}$  falls. The data is latched in with data setup and hold times for DQ0-DQ15 referenced to  $\overline{CAS}$  (see Figure 4).

<sup>†</sup> Either WEx can be brought low prior to CAS to initiate an early-write cycle.

Figure 4. Example of an Early-Write Cycle

<sup>‡</sup> See "timing requirements over recommended ranges of supply voltage and operating free-air temperature" table.

#### byte-write (continued)

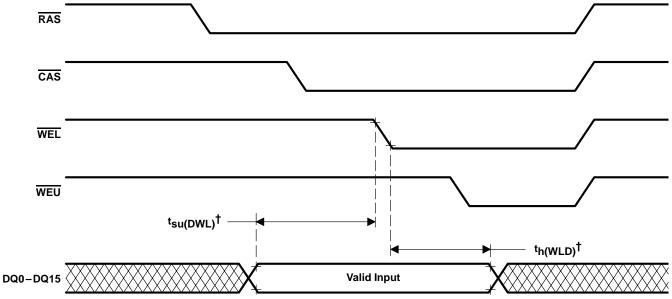

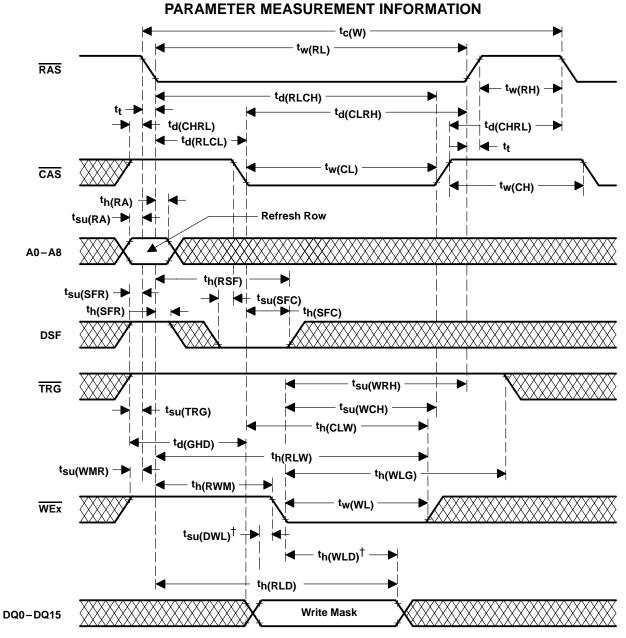

For late-write or read-modify-write cycles,  $\overline{WEL}$  and  $\overline{WEU}$  are both held high before  $\overline{CAS}$  falls. After  $\overline{CAS}$  falls, either or both  $\overline{WEL}$  and  $\overline{WEU}$  are brought low to select the corresponding byte or bytes to be written. The data is latched in with data setup and hold times for DQ0-DQ15 referenced to the first falling edge of  $\overline{WEx}$  (see Figure 5).

† See "timing requirements over recommended ranges of supply voltage and operating free-air temperature" table.

Figure 5. Example of a Late-Write Cycle

#### write-per-bit

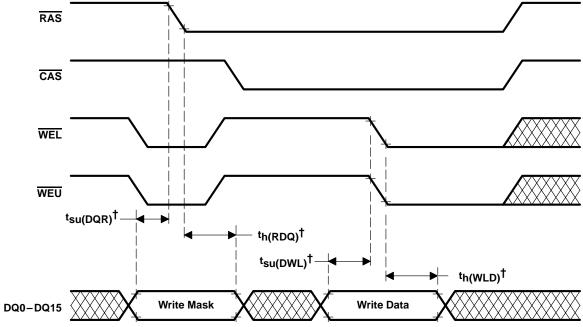

The write-per-bit function allows masking <u>any</u> combination of the 16 DQs on any write cycle. <u>The</u> write-per-bit operation is invoked when either or both <u>WEL</u> and <u>WEU</u> are held low on the falling edge of <u>RAS</u>. Either <u>WEX</u> allows entry of the entire 16-bit mask on DQ0-DQ15. Byte control of the mask input is not allowed. If both <u>WEL</u> and <u>WEU</u> are held high on the falling edge of <u>RAS</u>, the write operation is performed without any masking. There are two write-per-bit modes: the nonpersistent write-per-bit and the persistent write-per-bit.

#### nonpersistent write-per-bit

When either or both  $\overline{WEL}$  and  $\overline{WEU}$  are low on the falling edge of  $\overline{RAS}$ , the write mask is reloaded. A 16-bit binary code (the write mask) is input to the device via the DQ pins and latched on the falling edge of  $\overline{RAS}$ . The write-per-bit mask selects which of the 16 DQs are to be written and which are not. After  $\overline{RAS}$  has latched the on-chip write-per-bit mask, input data is driven onto the DQ pins and is latched on either the falling edge of  $\overline{CAS}$  or the first falling edge of  $\overline{WEx}$ , whichever occurs later.  $\overline{WEL}$  enables the lower byte (DQ0 –DQ7) to be written through the mask and  $\overline{WEU}$  enables the upper byte (DQ8 –DQ15) to be written through the mask. If a write mask low (write mask = 0) is latched into a particular DQ pin on the falling edge of  $\overline{RAS}$ , write data is not written to that DQ. If a write mask high (write mask = 1) is latched into a particular DQ pin on the falling edge of  $\overline{RAS}$ , write data is written to that DQ (see Figure 6).

<sup>†</sup> See "timing requirements over recommended ranges of supply voltage and operating free-air temperature" table.

Figure 6. Example of a Nonpersistent Write-Per-Bit (Late-Write) Operation

#### persistent write-per-bit

Mask Data

1 : Write to DQ enabled 0 : Write to DQ disabled

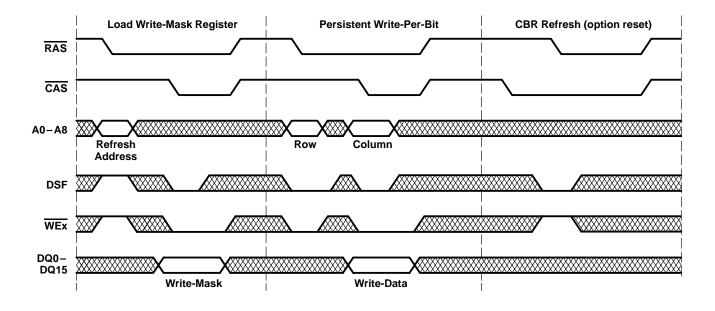

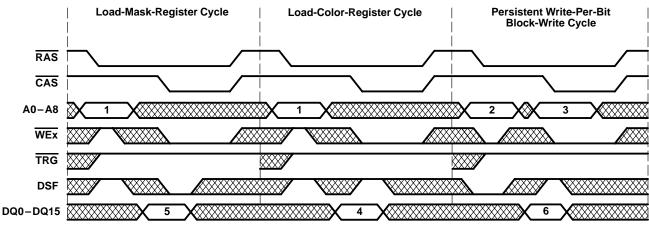

The persistent write-per-bit mode is initiated by performing a load-write-mask-register (LMR) cycle. In the persistent write-per-bit mode, the write mask is not overwritten but remains valid over an arbitrary number of write cycles until another LMR cycle is performed, a CBR with reset is executed, or power is removed.

The load-write-mask-register cycle is performed using DRAM write-cycle timing with DSF held high on the falling edge of  $\overline{RAS}$  and held low on the falling edge of  $\overline{CAS}$ . A binary code is input to the write-mask register via the DQ pins and latched on either the falling edge of  $\overline{CAS}$  or the first falling edge of  $\overline{WEx}$ , whichever occurs later. Byte write control can be applied to the write mask during the load-write-mask-register cycle. The persistent write-per-bit mode can then be used in exactly the same way as the nonpersistent write-per-bit mode except that the input data on the falling edge of  $\overline{RAS}$  is ignored. When the device is set to the persistent write-per-bit mode, it remains in this mode and is reset only by a CBR refresh (option reset) cycle (see Figure 7).

Figure 7. Example of a Persistent Write-Per-Bit Operation

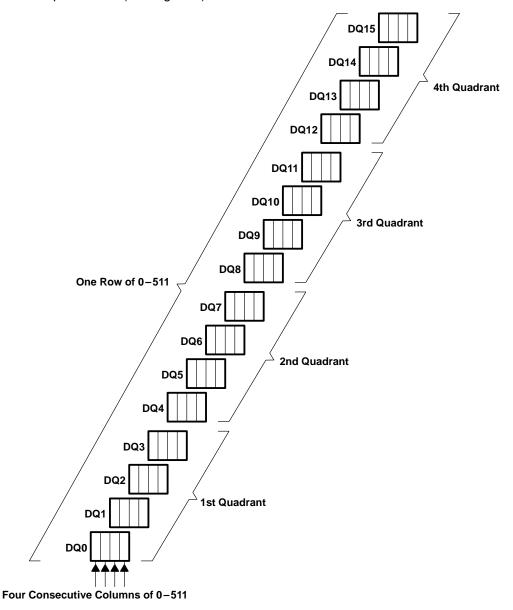

#### 4-column block write (TMS5516x)

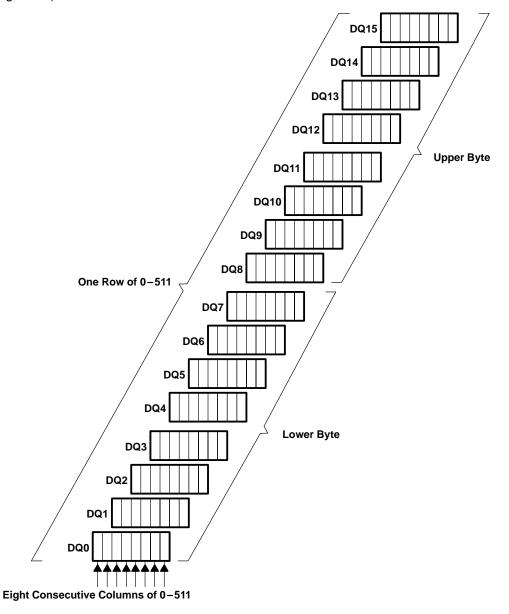

The 4-column block-write function allows up to 64 bits of data to be written simultaneously to one row of the memory array. This function is implemented as 4 columns  $\times$  4 DQs and repeated in four quadrants. In this manner, each of the four one-megabit quadrants can have up to four consecutive columns written at a time with up to four DQs per column (see Figure 8).

Figure 8. 4-Column Block-Write Operation

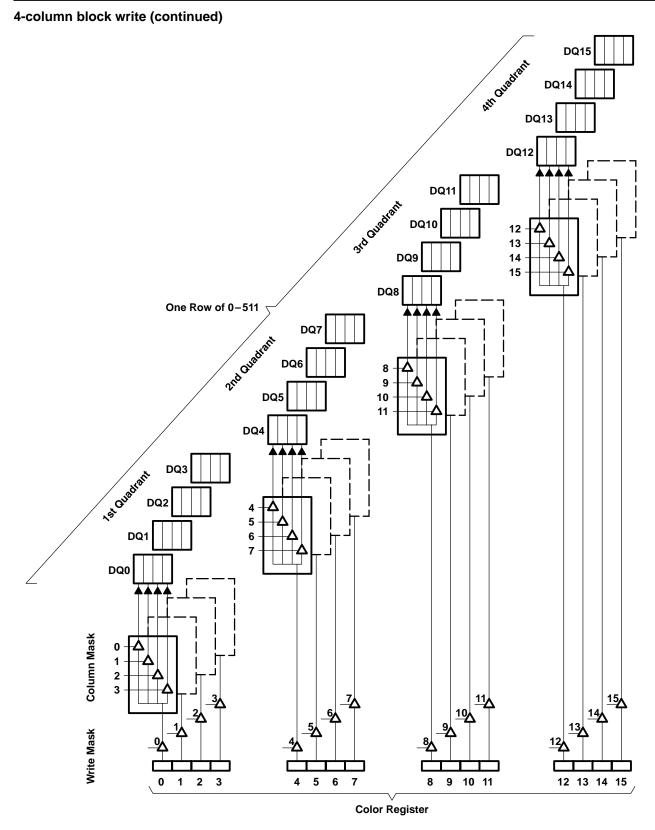

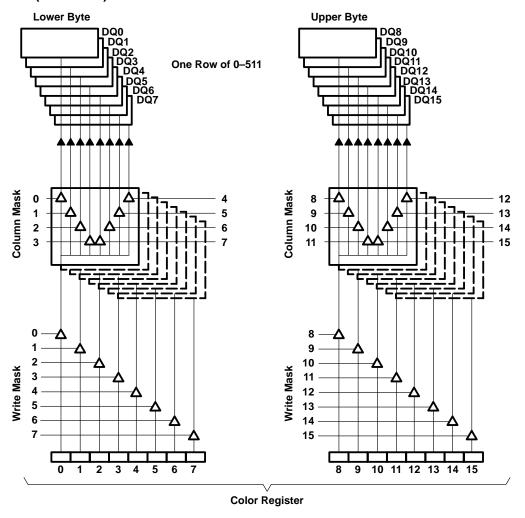

Each one-megabit quadrant has a 4-bit column mask to mask off any or all of the four columns from being written with data. Nonpersistent write-per-bit or persistent write-per-bit functions can be applied to the block-write operation to provide write-masking options. Write data (color data) is provided by four bits from the on-chip color register. Bits 0-3 from the 16-bit write-mask register, bits 0-3 from the 16-bit color-data register configure the block write for the first quadrant, while bits 4-7, 8-11, and 12-15 of the corresponding registers control the other quadrants in a similar fashion (see Figure 9).

Figure 9. 4-Column Block Write With Masks

#### 4-column block write (continued)

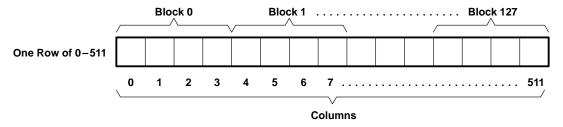

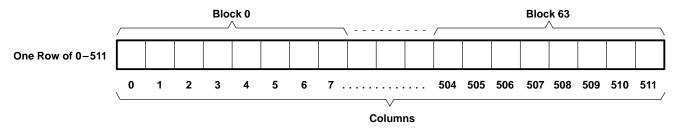

Every four adjacent columns makes a block, which results in 128 blocks along one row. Block 0 comprises columns 0 – 3, block 1 comprises columns 4 – 7, block 2 comprises columns 8 – 11, etc., as shown in Figure 10.

Figure 10. 4-Column-Block Column-Organization

During 4-column block-write cycles, only the seven most significant column addresses (A2 -A8) are latched on the falling edge of  $\overline{CAS}$  to decode one of the 128 blocks. Address bits A0 -A1 are ignored. All one-megabit quadrants have the same block selected.

A block-write cycle is entered in a manner similar to a DRAM write cycle except DSF is held high on the falling edge of  $\overline{CAS}$ . As in a DRAM write operation,  $\overline{WEL}$  and  $\overline{WEU}$  enable the corresponding lower and upper DRAM DQ bytes to be written, respectively. The column-mask data is input via the DQs and is latched on either the falling edge of  $\overline{CAS}$  or the first falling edge of  $\overline{WEx}$ , whichever occurs later. The 16-bit color-data register must be loaded prior to performing a block write as described below. Refer to the write-per-bit section for details on use of the write-mask capability, allowing additional performance options.

Example of block write:

block-write column address = 110000000 (A0 – A8 from left to right)

|                      | bit 0  |      |      | bit 15 |

|----------------------|--------|------|------|--------|

| color-data register  | = 1011 | 1011 | 1100 | 0111   |

| write-mask register  | = 1110 | 1111 | 1111 | 1011   |

| column-mask register | = 1111 | 0000 | 0111 | 1010   |

|                      | 1st    | 2nd  | 3rd  | 4th    |

|                      | Quad   | Quad | Quad | Quad   |

Column-address bits A0 and A1 are ignored. Block 0 (columns 0-3) is selected for all one-megabit quadrants. The first quadrant has DQ0 – DQ2 written with bits 0-2 from the color-data register to all four columns of block 0. DQ3 is not written and retains its previous data due to the write-mask bit 3 being a 0.

The second quadrant (DQ4-DQ7) has all four columns masked off due to the column-mask bits 4-7 being 0, so that no data is written.

The third quadrant (DQ8-DQ11) has its four DQs written with bits 8 –11 from the color-data register to columns 1–3 of its block 0. Column 0 is not written and retains its previous data on all four DQs due to the column-mask bit 8 being 0.

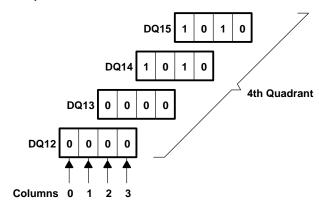

The fourth quadrant (DQ12-DQ15) has DQ12, DQ14, and DQ15 written with bits 12, 14, and 15 from the color-data register to column 0 and column 2 of its block 0. DQ13 retains its previous data on all columns due to the write mask. Columns 1 and 3 retain their previous data on all DQs due to the column mask. If the previous data for the quadrant was all 0s, the fourth quadrant would contain the data pattern shown in Figure 11 after the 4-column block-write operation shown in the example.

# 4-column block write (continued)

Figure 11. Example of Fourth Quadrant After 4-Column Block-Write Operation

#### 8-column block write (TMS5517x)

The 8-column block-write function allows up to 128 bits of data to be written simultaneously to one row of the memory array. This function is implemented as 8 columns  $\times$  8 DQs and repeated in two bytes. In this manner, each of the two bytes can have up to eight consecutive columns written at a time with up to eight DQs per column (see Figure 12).

Figure 12. 8-Column Block-Write Operation

Each byte has an 8-bit column mask to mask off any or all of the eight columns from being written with data. Nonpersistent write-per-bit or persistent write-per-bit functions can be applied to the block-write operation to provide write-masking options. Write data (color data) is provided by eight bits from the on-chip color register. Bits 0-7 from the 16-bit write-mask register, bits 0-7 from the 16-bit column-mask register, and bits 0-7 from the 16-bit color-data register configure the block write for the lower byte, while bits 8-15 control the upper byte in a similar fashion (see Figure 13).

#### 8-bit block write (continued)

Figure 13. 8-Column Block Write With Masks

Every eight adjacent columns makes a block resulting in 64 blocks along one row. Block 0 comprises columns 0-7, block 1 comprises columns 8-15, block 2 comprises columns 16-23, etc., as shown in Figure 14.

Figure 14. 8-Column-Block Column-Organization

During 8-column block-write cycles, only the six most significant column addresses (A3 - A8) are latched on the falling edge of  $\overline{CAS}$  to decode one of the 64 blocks. Address bits A0 - A2 are ignored. Both bytes have the same block selected.

#### 8-column block write (continued)

A block-write cycle is entered in a manner similar to a DRAM write cycle except DSF is held high on the falling edge of CAS. As in a DRAM write operation, WEL and WEU enable the corresponding lower and upper DRAM DQ bytes to be written, respectively. The column-mask data is input via the DQs and is latched on either the falling edge of CAS or the first falling edge of WEx, whichever occurs later. The 16-bit color-data register must be loaded prior to performing a block write as described below. Refer to the write-per-bit section for details on use of the write-mask capability allowing additional performance options.

#### Example of block write:

110000000 (A0 – A8 from left to right) block-write column address = bit 0 bit 15 color-data register = 10111011 11000111 write-mask register = 11101111 11111011 01111010 column-mask register = 11110000 Lower Upper Byte Byte

Column-address bits A0-A2 are ignored. Block 0 (columns 0-7) is selected for both bytes. The lower byte has DQ0-DQ2 and DQ4-DQ7 written with bits 0-2 and 4-7 from the color-data register to columns 0-3. Columns 4-7 are not written and retain their previous data due to the column-mask bits 4-7 being 0. DQ3 is not written and retains its previous data due to the write-mask bit 3 being 0.

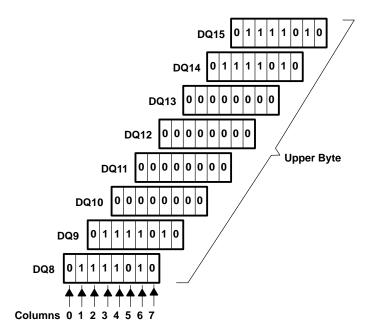

The upper byte has DQ8-DQ12 and DQ14-DQ15 written with bits 8-12 and 14-15 from the color-data register to columns 1-4 and 6. Columns 0, 5, and 7 are not written and retain their previous data due to the column-mask bits 8, 13, and 15 being 0. DQ13 is not written and retains its previous data due to the write-mask-register bit 13 being 0. If the previous data was all 0s, the upper byte would contain the data pattern in Figure 15 after the 8-column block-write operation shown in the example.

Figure 15. Example of Upper Byte After 8-Column Block-Write Operation

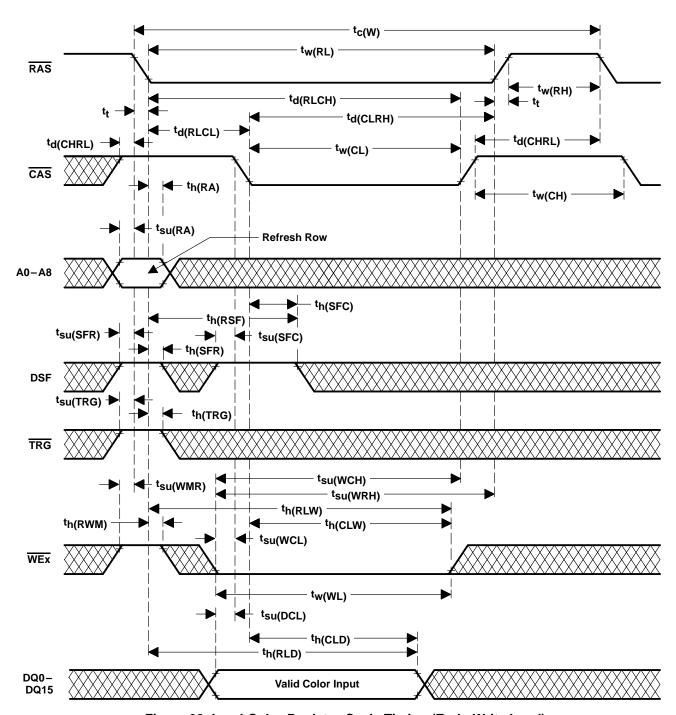

#### load color register

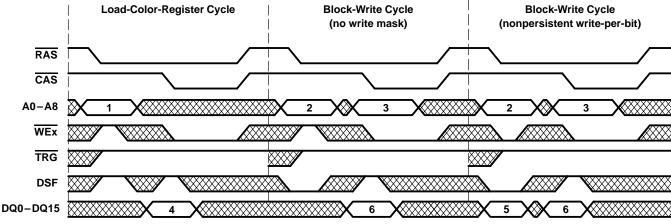

The load-color-register cycle is performed using normal DRAM write-cycle timing except that DSF is held high on the falling edges of RAS and CAS. The color register is loaded from pins DQ0 – DQ15, which are latched on either the first falling edge of WEx or the falling edge of CAS, whichever occurs later. If only one WEx is low, only the corresponding byte of the color register is loaded. When the color register is loaded, it retains data until power is lost or until another load-color-register cycle is performed (see Figure 16 and Figure 17).

Legend:

- 1. Refresh address: A0 A8 are latched on the falling edge of RAS.

- 2. Row address: A0-A8 are latched on the falling edge of RAS.

- 3. Block address A2-A8 (TMS5516x) or A3-A8 (TMS5517x) are latched on the falling edge of CAS.

- Color data: DQ0 DQ15 are latched on the falling edge CAS or the first falling edge of WEX, whichever occurs first.

- 5. Write-mask data: DQ0-DQ15 are latched on the falling edge RAS.

- 6. Column-mask data: DQ0-DQ15 are latched on the falling edge CAS or the first falling edge of WEx, whichever occurs first.

Figure 16. Example of Block Writes

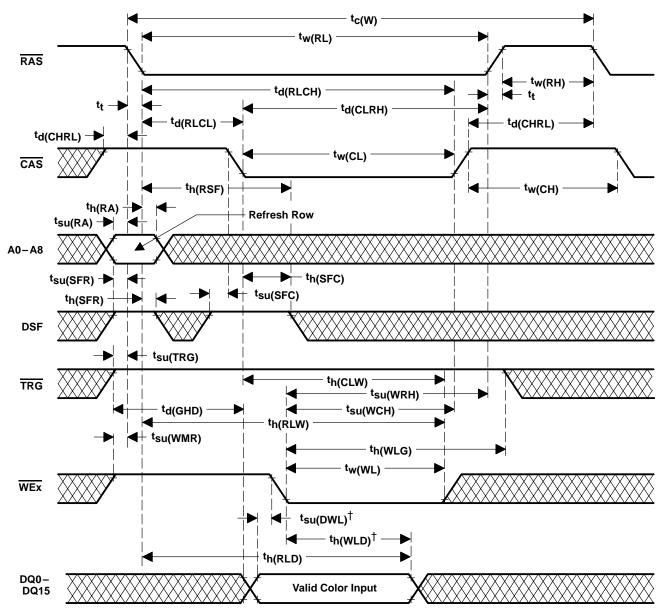

### load color register (continued)

Legend:

- 1. Refresh address: A0 A8 are latched on the falling edge of RAS.

- 2. Row address: A0 A8 are latched on the falling edge of RAS.

- 3. Block address A2-A8 (TMS5516x) or A3-A8 (TMS5517x) are latched on the falling edge of CAS.

- 4. Color data: DQ0 DQ15 are latched on the falling edge CAS or the first falling edge of WEx, whichever occurs first.

- 5. Write-mask data: DQ0-DQ15 are latched on the falling edge RAS.

- 6. Column-mask data: DQ0-DQ15 are latched on the falling edge CAS or the first falling edge of WEx, whichever occurs first. = don't care

Figure 17. Example of a Persistent Block Write

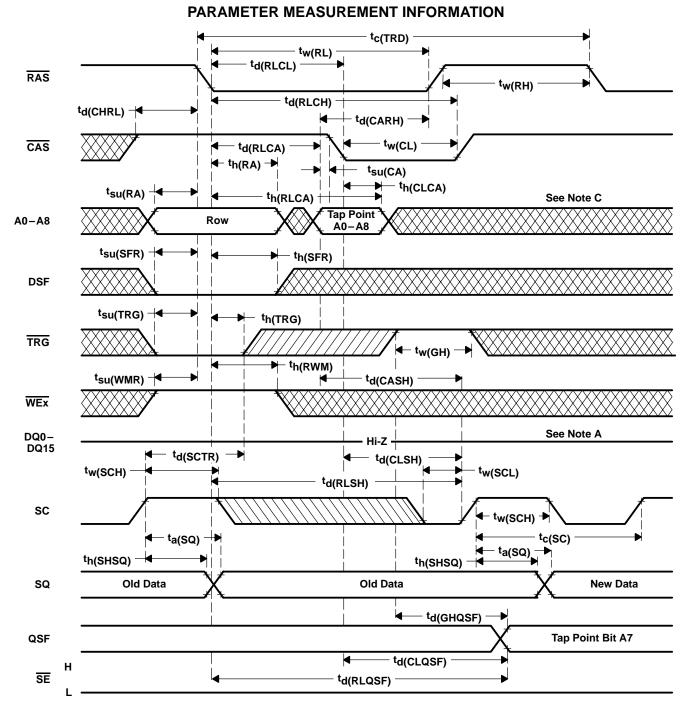

#### DRAM-to-SAM transfer operation

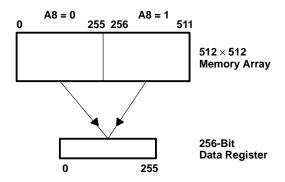

During the DRAM-to-SAM transfer operation, one half of a row (256 columns) in the DRAM array is selected to be transferred to the 256-bit serial-data register. The transfer operation is invoked by bringing TRG low and holding WEx high on the falling edge of RAS. The state of DSF, which is latched on the falling edge of RAS, determines whether the full-register-transfer operation or the split-register-transfer operation is performed.

**Table 5. SAM Function Table**

| FUNCTION                     | RAS FALL |     |      | CAS<br>FALL | ADDRESS |             | DQ0          | -DQ15 | MNE        |      |

|------------------------------|----------|-----|------|-------------|---------|-------------|--------------|-------|------------|------|

| FUNCTION                     | CAS      | TRG | WEx† | DSF         | DSF     | RAS         | CAS          | RAS   | CAS<br>WEx | CODE |

| Full-register-transfer read  | Н        | L   | Н    | L           | Х       | Row<br>Addr | Tap<br>Point | Х     | Х          | RT   |

| Split-register-transfer read | Н        | L   | Н    | Н           | Х       | Row<br>Addr | Tap<br>Point | Х     | Х          | SRT  |

<sup>†</sup> Logic L is selected when either or both  $\overline{WEL}$  and  $\overline{WEU}$  are low.

X = don't care

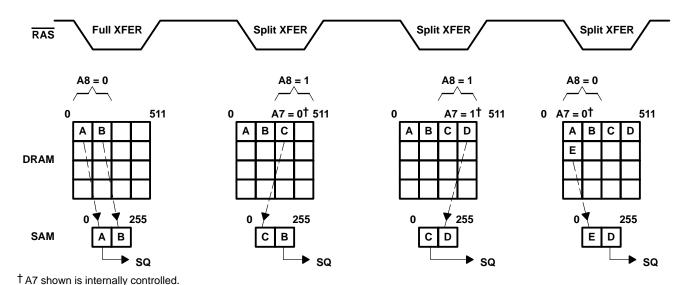

#### full-register-transfer read

A full-register-transfer operation loads data from a selected half of a row in the DRAM into the SAM.  $\overline{TRG}$  is brought low and latched at the falling edge of  $\overline{RAS}$ . Nine row-address bits (A0 – A8) are also latched at the falling edge of  $\overline{RAS}$  to select one of the 512 rows available for the transfer. The nine column-address bits (A0 – A8) are latched at the falling edge of  $\overline{CAS}$ , where address bit A8 selects which half of the row is transferred. Address bits A0 – A7 select one of the SAM's 256 available tap points from which the serial data is read out (see Figure 18).

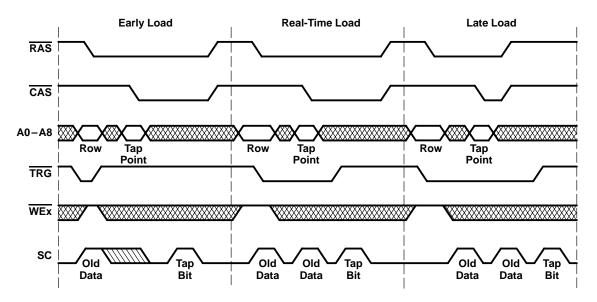

Figure 18. Full-Register-Transfer Read

A full-register transfer can be performed in three ways: early load, real-time load (or midline load), or late load. Each of these offers the flexibility of controlling the TRG trailing edge in the full-register-transfer cycle (see Figure 19).

Figure 19. Example of Full-Register-Transfer Read Operations

#### split-register-transfer read

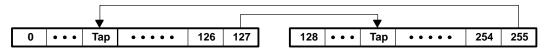

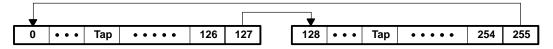

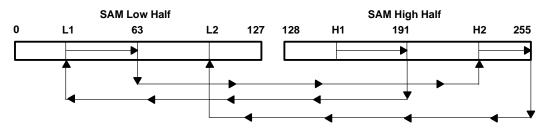

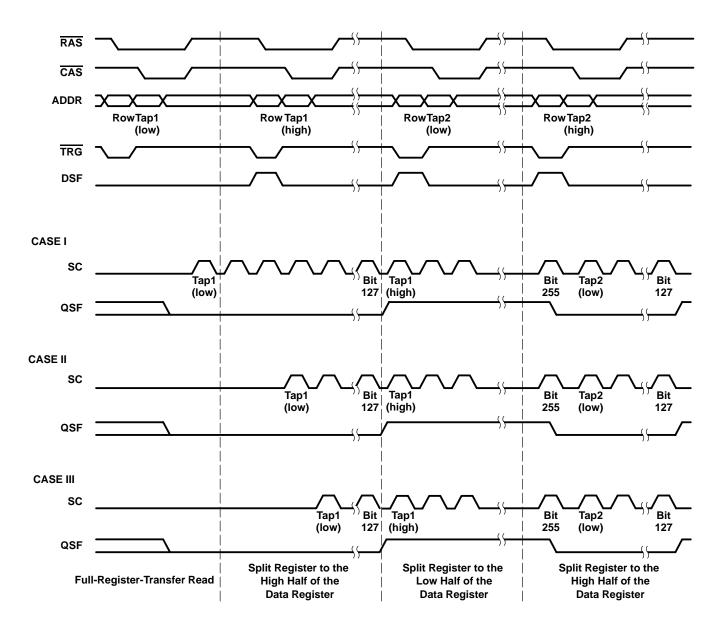

In split-register-transfer operations, the serial-data register is split into halves. The low half contains bits 0 – 127, and the high half contains bits 128 – 255 (see Figure 20). While one half is being read out of the SAM port, the other half can be loaded from the memory array.

Figure 20. Split-Register-Transfer Read

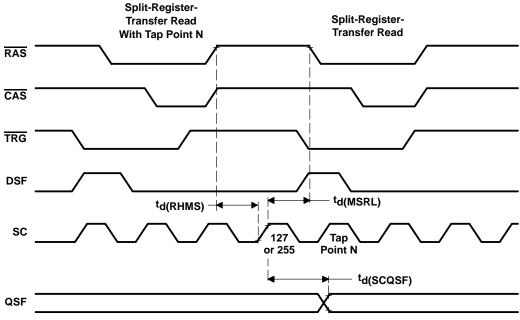

To invoke a split-register-transfer cycle, DSF is brought high,  $\overline{TRG}$  is brought low, and both are latched at the falling edge of  $\overline{RAS}$  (see Figure 21). Nine row-address bits (A0 – A8) are also latched at the falling edge of  $\overline{RAS}$  to select one of the 512 rows available for the transfer. Eight of the nine column-address bits (A0 – A6 and A8) are latched at the falling edge of  $\overline{CAS}$ . Column-address bit A8 selects which half of the row is to be transferred. Column-address bit A7 is ignored, and the split-register transfer is internally controlled to select the inactive half. Column-address bits A0 – A6 select one of 127 tap points in the specified half of SAM. Locations 127 and 255 are not valid tap points in split-register-transfer operations. In stop-point mode, stop-point locations are not valid tap points in split-register-transfer operations.

Figure 21. Example of a Split-Register-Transfer Read Operation

A full-register transfer must precede the first split-register transfer to ensure proper operation. After the full-register transfer cycle, the first split-register transfer can follow immediately without any minimum SC clock requirement (see Figure 22).

#### split-register-transfer read (continued)

QSF indicates which half of the register is being accessed during serial-access operation. When QSF is low, the serial-address pointer is accessing the lower (least significant) 128 bits of SAM. When QSF is high, the pointer is accessing the higher (most significant) 128 bits of SAM (see Figure 23). QSF changes state upon completing a full-register-transfer read cycle. The tap point loaded during the current transfer cycle determines the state of QSF. QSF also changes state when a boundary between two register halves is reached.

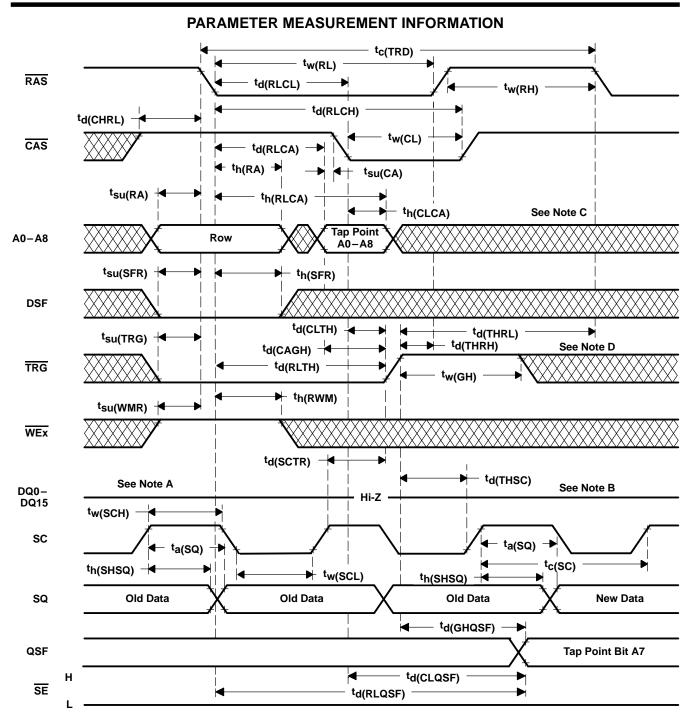

NOTE A: See "timing requirements over recommended ranges of supply voltage and operating free-air temperature" table.

Figure 22. Example of a Split-Register-Transfer Read After a Full-Register-Transfer Read

NOTE A: See "timing requirements over recommended ranges of supply voltage and operating free-air temperature" table.

Figure 23. Example of Successive Split-Register-Transfer Read Operations

#### serial-read operation

The serial-read operation can be performed through the SAM port simultaneously and asynchronously with DRAM operations except during transfer operations. Serial data is accessed from the SAM at the rising edge of serial clock SC.  $\overline{SE}$  low enables the outputs.  $\overline{SE}$  high disables the outputs. Holding  $\overline{SE}$  high does not disable SC. The rising edge of SC automatically increments the internal serial-address counter regardless of the state of  $\overline{SE}$ . In full-register-transfer operations, the counter proceeds sequentially to the most significant bit (bit 255), and then wraps around to the least significant bit (bit 0), as shown in Figure 24.

Figure 24. Serial-Pointer Direction for Serial Read

In split-register-transfer operations, serial data can be read out from the active half of SAM by clocking SC starting at the tap point loaded by the preceding split-register-transfer cycle. The serial pointer then proceeds sequentially to the most significant bit of the half, bit 127 or bit 255. If there is a split-register-transfer read to the inactive half during this period, the serial pointer points next to the tap point location loaded by that split-register-transfer (see Figure 25).

Figure 25. Serial Pointer for Split-Register Read - Case I

If there is no split-register transfer to the inactive half during this period, the serial pointer points to the next bit, bit 128 or bit 0, respectively (see Figure 26).

Figure 26. Serial Pointer for Split-Register Read – Case II

#### split-register programmable stop point

The TMS551xx offers programmable stop-point mode for split-register-transfer read operation. This mode can be used to improve 2-D drawing performance in a nonscanline data format.

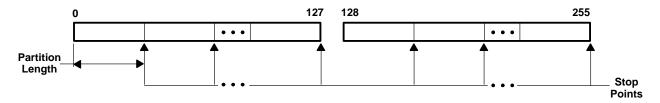

In split-register-transfer read operations, the stop point is defined as a register location at which the serial output stops coming from one half of the SAM and switches to the opposite half of the SAM. While in stop-point mode, the SAM is divided into partitions whose length is programmed via row addresses A4–A7 in a CBR set (CBRS) cycle. The last serial-address location of each partition is the stop point (see Figure 27).

Figure 27. Example of SAM With Partitions

#### split-register programmable stop point (continued)

Stop-point mode is not active until the CBRS cycle is initiated. The CBRS operation is performed by holding CAS and WEx low and DSF high on the falling edge of RAS. The falling edge of RAS also latches row addresses A4–A7, which are used to define the SAM's partition length. The other row-address inputs are don't cares. Stop-point mode should be initiated immediately after the power-up initialization (see Table 6).

| MAXIMUM<br>PARTITION | Al | DDRESS | AT RAS | IN CBF | RS CYCL | .E    | NUMBER OF  | STOP-POINT LOCATIONS                                                     |  |  |

|----------------------|----|--------|--------|--------|---------|-------|------------|--------------------------------------------------------------------------|--|--|

| LENGTH               | A8 | Α7     | A6     | A5     | A4      | A0-A3 | PARTITIONS |                                                                          |  |  |

| 16                   | Х  | L      | L      | L      | L       | Х     | 16         | 15, 31, 47, 63, 79, 95, 111, 127, 143, 159, 175, 191, 207, 223, 239, 255 |  |  |

| 32                   | Х  | L      | L      | L      | Н       | Х     | 8          | 31, 63, 95, 127, 159, 191, 223, 255                                      |  |  |

| 64                   | Х  | L      | L      | Н      | Н       | Х     | 4          | 63, 127, 191, 255                                                        |  |  |

| 128<br>(default)     | Х  | L      | Н      | Н      | Н       | Х     | 2          | 127, 255                                                                 |  |  |

**Table 6. Programming Code for Stop-Point Mode**

In stop-point mode, the tap point loaded during the split-register-transfer read cycle determines in which SAM partition the serial output begins and at which stop point the serial output stops coming from one half of SAM and switches to the opposite half of SAM (see Figure 28).

Figure 28. Example of Split-Register Operation With Programmable Stop Points

### 256-/512-bit compatibility of split-register programmable stop point

The stop-point mode is designed to be compatible with both 256-bit SAM and 512-bit SAM devices. After the CBRS cycle is initiated, the stop-point mode becomes active. In the stop-point mode, and only in the stop-point mode, the column-address bits AY7 and AY8 are internally swapped to assure compatibility (see Figure 29). This address-bit swap applies to the column address, and it is effective for all DRAM and transfer cycles. For example, during the split-register-transfer cycle with stop point, column-address bit AY8 is a don't care and AY7 decodes the DRAM row half for the split-register-transfer. During stop-point mode, a CBR (option reset) cycle is not recommended because this ends the stop-point mode and restores address bits AY7 and AY8 to their normal functions. Consistent use of CBR cycles ensures that the TMS551xx remains in nomal mode.

Figure 29. DRAM-to-SAM Mapping, Nonstop-Point Versus Stop Point

IMPORTANT: For proper device operation, a stop-point-mode (CBRS) cycle should be initiated immediately after the power-up initialization cycles are performed.

#### power up

To achieve proper device operation, an initial pause of 200  $\mu$ s is required after power up followed by a minimum of eight RAS cycles or eight CBR cycles to initialize the DRAM port. A full-register-transfer read cycle and two SC cycles are required to initialize the SAM port.

After initialization, the internal state of the TMS551xx is as follows:

|                           | STATE AFTER INITIALIZATION                          |

|---------------------------|-----------------------------------------------------|

| QSF                       | Defined by the transfer cycle during initialization |

| Write mode                | Nonpersistent mode                                  |

| Write-mask register       | Undefined                                           |

| Color register            | Undefined                                           |

| Serial-register tap point | Defined by the transfer cycle during initialization |

| SAM port                  | Output mode                                         |

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

|                                                      |      | TMS551xx    |

|------------------------------------------------------|------|-------------|

| Supply voltage range, V <sub>CC</sub> (see Note 1)   |      | –1 V to 7 V |

| Voltage range on any pin                             |      | –1 V to 7 V |

| Short-circuit output current                         |      | 50 mA       |

| Power dissipation                                    |      | 1.1 W       |

| Operating free-air temperature range, T <sub>A</sub> | 0    | °C to 70°C  |

| Storage temperature range, T <sub>stg</sub>          | -55° | C to 150°C  |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

|          |                                      | T    | MS551xx | (   | UNIT |

|----------|--------------------------------------|------|---------|-----|------|

|          |                                      | MIN  | NOM     | MAX | UNII |

| VCC      | Supply voltage                       | 4.5  | 5.0     | 5.5 | V    |

| VSS      | Supply voltage                       |      | 0       |     | V    |

| ٧ıH      | High-level input voltage             | 2.4  |         | 6.5 | V    |

| $V_{IL}$ | Low-level input voltage (see Note 2) | -1.0 |         | 8.0 | V    |

| TA       | Operating free-air temperature       | 0    |         | 70  | °C   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used for logic-voltage levels only.

NOTE 1: All voltage values are with respect to VSS.

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

| DADAMETED         |                                    | TEST SAM                                                                                                      |         | '551xx-60 |     | '551xx-70 |     |      |

|-------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------|---------|-----------|-----|-----------|-----|------|

|                   | PARAMETER                          | CONDITIONS†                                                                                                   | PORT    | MIN       | MAX | MIN       | MAX | UNIT |

| Vон               | High-level output voltage          | I <sub>OH</sub> = -1 mA                                                                                       |         | 2.4       |     | 2.4       |     | V    |

| VOL               | Low-level output voltage           | $I_{OL} = 2 \text{ mA}$                                                                                       |         |           | 0.4 |           | 0.4 | V    |

| Ц                 | Input current (leakage)            | $V_{CC} = 5.5 \text{ V},$<br>$V_{I} = 0 \text{ V to } 5.8 \text{ V},$<br>All other pins<br>at 0 V to $V_{CC}$ |         | ±10       |     |           | ±10 | μΑ   |

| IO                | Output current (leakage)           | V <sub>CC</sub> = 5.5 V,<br>V <sub>O</sub> = 0 V to V <sub>CC</sub><br>See Note 3                             |         | ±10       |     |           | ±10 | μΑ   |

| I <sub>CC1</sub>  | Operating current <sup>‡</sup>     | See Note 4                                                                                                    | Standby |           | 180 |           | 165 | mA   |

| ICC1A             | Operating current <sup>‡</sup>     | $t_{C(SC)} = MIN$                                                                                             | Active  |           | 225 |           | 205 | mA   |

| I <sub>CC2</sub>  | Standby current                    | All clocks = V <sub>CC</sub>                                                                                  | Standby | 5         |     |           | 5   | mA   |

| I <sub>CC2A</sub> | Standby current <sup>‡</sup>       | $t_{C(SC)} = MIN$                                                                                             | Active  | 70        |     |           | 65  | mA   |

| I <sub>CC3</sub>  | RAS only refresh current           | See Note 4                                                                                                    | Standby | 180       |     |           | 165 | mA   |

| I <sub>CC3A</sub> | RAS only refresh current‡          | t <sub>C(SC)</sub> = MIN,<br>See Note 4                                                                       | Active  | 225       |     |           | 205 | mA   |

|                   | D                                  | $t_{C(P)} = MIN,$                                                                                             | Standby | '551x5    | 135 |           | 115 | 1    |

| ICC4              | Page-mode current∓                 | See Note 5                                                                                                    |         | '551x6    | 140 |           | 140 | mA   |

|                   | Dana mada sumant T                 | $t_{C(SC)} = MIN,$                                                                                            | A =4:   | '551x5    | 175 |           | 155 | A    |

| ICC4A             | Page-mode current‡                 | See Note 5                                                                                                    | Active  | '551x6    | 185 |           | 185 | mA   |

| I <sub>CC5</sub>  | CBR current                        | See Note 4                                                                                                    | Standby | •         | 180 |           | 165 | mA   |

| I <sub>CC5A</sub> | CBR current <sup>‡</sup>           | t <sub>C</sub> (SC) = MIN,<br>See Note 4                                                                      | Active  |           | 225 |           | 205 | mA   |

| I <sub>CC6</sub>  | Data-transfer current              | See Note 4                                                                                                    | Standby | 200       |     |           | 180 | mA   |

| I <sub>CC6A</sub> | Data-transfer current <sup>‡</sup> | $t_{C(SC)} = MIN$                                                                                             | Active  |           | 250 |           | 225 | mA   |

<sup>†</sup> For conditions shown as MIN/MAX, use the appropriate value specified in the timing requirements.

NOTES: 3. SE is disabled for SQ output leakage tests.

4. Measured with one address change while  $\overline{RAS} = V_{IL}$ ;  $t_{C(rd)}$ ,  $t_{C(W)}$ ,  $t_{C(TRD)} = MIN$

5. Measured with one address change while  $\overline{CAS} = V_{IH}$

# capacitance over recommended ranges of supply voltage and operating free-air temperature, f = 1 MHz (see Note 6)

|                     | PARAMETER                                  | MIN | MAX | UNIT |

|---------------------|--------------------------------------------|-----|-----|------|

| C <sub>i(A)</sub>   | Input capacitance, address inputs          |     | 6   | pF   |

| C <sub>i(RC)</sub>  | Input capacitance, address strobe inputs   |     | 7   | pF   |

| C <sub>i(W)</sub>   | Input capacitance, write enable input      |     | 7   | pF   |

| C <sub>i(SC)</sub>  | Input capacitance, serial clock            |     | 7   | pF   |

| C <sub>i(SE)</sub>  | Input capacitance, serial enable           |     | 7   | pF   |

| C <sub>i(DSF)</sub> | Input capacitance, special function        |     | 7   | pF   |

| C <sub>i(TRG)</sub> | Input capacitance, transfer register input |     | 7   | pF   |

| C <sub>o(O)</sub>   | Output capacitance, SQ and DQ              |     | 7   | pF   |

| C <sub>o(QSF)</sub> | Output capacitance, QSF                    |     | 9   | pF   |

NOTE 6:  $V_{CC}$  = 5 V  $\pm$  0.5 V, and the bias on pins under test is 0 V.

<sup>‡</sup> Measured with outputs open

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Note 7)

|                      | PARAMETER                                              | TEST                   | ALT.             | '551xx-60 |     | '551x | x-70 | UNIT |  |

|----------------------|--------------------------------------------------------|------------------------|------------------|-----------|-----|-------|------|------|--|

|                      | FARAMETER                                              | CONDITIONS† SY         |                  | MIN       | MAX | MIN   | MAX  | ONT  |  |

| ta(C)                | Access time, DQx from CAS low                          | $t_{d(RLCL)} = MAX$    | <sup>t</sup> CAC |           | 17  |       | 20   | ns   |  |

| ta(CA)               | Access time, DQx from column address                   | $t_{d(RLCL)} = MAX$    | t <sub>AA</sub>  |           | 30  |       | 35   | ns   |  |

| ta(CP)               | Access time, DQx from CAS high                         | $t_{d(RLCL)} = MAX$    | t <sub>CPA</sub> |           | 35  |       | 40   | ns   |  |

| ta(G)                | Access time, DQx from TRG low                          |                        | tOEA             |           | 15  |       | 20   | ns   |  |

| ta(R)                | Access time, DQx from RAS low                          | $t_{d(RLCL)} = MAX$    | tRAC             |           | 60  |       | 70   | ns   |  |

| ta(SE)               | Access time, SQx from SE low                           | C <sub>L</sub> = 30 pF | <sup>t</sup> SEA |           | 12  |       | 15   | ns   |  |

| ta(SQ)               | Access time, SQx from SC high                          | C <sub>L</sub> = 30 pF | <sup>t</sup> SCA |           | 15  |       | 20   | ns   |  |

| tdis(CH)             | Disable time, random output from CAS high (see Note 8) | C <sub>L</sub> = 50 pF | <sup>t</sup> OFF | 3         | 15  | 3     | 20   | ns   |  |

| <sup>t</sup> dis(G)  | Disable time, random output from TRG high (see Note 8) | C <sub>L</sub> = 50 pF | <sup>t</sup> OEZ | 3         | 15  | 3     | 20   | ns   |  |

| <sup>t</sup> dis(RH) | Disable time, random output from RAS high (see Note 8) | C <sub>L</sub> = 50 pF |                  | 3         | 15  | 3     | 20   | ns   |  |

| tdis(SE)             | Disable time, serial output from SE high (see Note 8)  | C <sub>L</sub> = 30 pF | <sup>t</sup> SEZ | 3         | 10  | 3     | 20   | ns   |  |

| tdis(WL)             | Disable time, random output from WEx low (see Note 8)  | C <sub>L</sub> = 30 pF | tWEZ             | 0         | 15  | 0     | 20   | ns   |  |

<sup>†</sup> For conditions shown as MIN/MAX, use the appropriate value specified in the timing requirements.

NOTES: 7. Switching times for RAM-port output are measured with a load equivalent to 1 TTL load and 50 pF. Data out reference level: V<sub>OH</sub>/V<sub>OL</sub> = 2 V/0.8 V. Switching times for SAM-port output are measured with a load equivalent to 1 TTL load and 30 pF. Serial-data out reference level: V<sub>OH</sub> / V<sub>OL</sub> = 2 V/0.8 V.

$<sup>8. \</sup>quad t_{\mbox{dis}(\mbox{CH})}, t_{\mbox{dis}(\mbox{RH})}, t_{\mbox{dis}(\mbox{G})}, t_{\mbox{dis}(\mbox{WL})}, \mbox{ and } t_{\mbox{dis}(\mbox{SE})} \mbox{ are specified when the output is no longer driven.}$

# TMS55165, TMS55166, TMS55175, TMS55176 262144 BY 16-BIT MULTIPORT VIDEO RAM

SMVS463 - DECEMBER 1995

# timing requirements over recommended ranges of supply voltage and operating free-air temperature†

|                       |                                                                           |                                     | ALT.<br>SYMBOL    | '551xx-60 '551xx-70 |         |     |         |      |

|-----------------------|---------------------------------------------------------------------------|-------------------------------------|-------------------|---------------------|---------|-----|---------|------|

|                       |                                                                           |                                     |                   | MIN                 | MAX     | MIN | MAX     | UNIT |

| 4                     | Cycle time name made read putits                                          | '551x5                              | t <sub>PC</sub>   | 35                  |         | 40  |         | ns   |

| t <sub>C</sub> (P)    | Cycle time, page-mode read, write                                         | '551x6                              | tPC               | 30                  |         | 30  |         | ns   |

| t <sub>c(rd)</sub>    | Cycle time, read                                                          |                                     | t <sub>RC</sub>   | 110                 |         | 130 |         | ns   |

| t <sub>c(rdW)</sub>   | Cycle time, read-modify-write                                             |                                     | t <sub>RMW</sub>  | 150                 |         | 175 |         | ns   |

| t <sub>c</sub> (RDWP) | Cycle time, page-mode read-modify-write                                   |                                     | t <sub>PRMW</sub> | 80                  |         | 90  |         | ns   |

| t <sub>c(SC)</sub>    | Cycle time, serial clock (see Note 9)                                     | cle time, serial clock (see Note 9) |                   | 18                  |         | 22  |         | ns   |

| t <sub>c(TRD)</sub>   | Cycle time, transfer read                                                 |                                     | t <sub>RC</sub>   | 110                 |         | 130 |         | ns   |

| t <sub>c(W)</sub>     | Cycle time, write                                                         |                                     | tWC               | 110                 |         | 130 |         | ns   |

| tw(CH)                | Pulse duration, CAS high                                                  |                                     | tCPN              | 10                  |         | 10  |         | ns   |

|                       | Pulso duration CAS law (see Note 10)                                      | '551x5                              | tCAS              | 10                  | 10 000  | 10  | 10 000  | ns   |

| tw(CL)                | Pulse duration, CAS low (see Note 10)                                     | '551x6                              | tCAS              | 17                  | 10 000  | 20  | 10 000  | ns   |

| <sup>t</sup> w(GH)    | Pulse duration, TRG high                                                  |                                     | t <sub>TP</sub>   | 20                  |         | 20  |         | ns   |

| tw(RH)                | Pulse duration, RAS high                                                  |                                     | t <sub>RP</sub>   | 40                  |         | 50  |         | ns   |

| tw(RL)                | Pulse duration, RAS low (see Note 11)                                     |                                     | tRAS              | 60                  | 10 000  | 70  | 10 000  | ns   |

| tw(RL)P               | Pulse duration, RAS low (page mode)                                       |                                     | tRASP             | 60                  | 100 000 | 70  | 100 000 | ns   |

| tw(SCH)               | Pulse duration, SC high                                                   |                                     | tsc               | 5                   |         | 8   |         | ns   |

| tw(SCL)               | Pulse duration, SC low                                                    |                                     | tSCP              | 5                   |         | 8   |         | ns   |

| tw(TRG)               | Pulse duration, TRG low                                                   |                                     |                   | 15                  |         | 20  |         | ns   |

| t <sub>w(WL)</sub>    | Pulse duration, WEx low                                                   |                                     | twp               | 10                  |         | 10  |         | ns   |

| t <sub>su(CA)</sub>   | Setup time, column address before CAS low                                 |                                     | tASC              | 0                   |         | 0   |         | ns   |

| tsu(DCL)              | Setup time, data valid before CAS low, early write                        |                                     | tDSC              | 0                   |         | 0   |         | ns   |

| t <sub>su(DQR)</sub>  | Setup time, write mask valid before RAS low, non-persistent write-per-bit |                                     | t <sub>MS</sub>   | 0                   |         | 0   |         | ns   |

| t <sub>su(DWL)</sub>  | Setup time, data valid before first WEx low, late write                   |                                     | tDSW              | 0                   |         | 0   |         | ns   |

| t <sub>su(RA)</sub>   | Setup time, row address before RAS low                                    |                                     | t <sub>ASR</sub>  | 0                   |         | 0   |         | ns   |

| tsu(rd)               | Setup time, both WEx high before CAS low, read                            |                                     | tRCS              | 0                   |         | 0   |         | ns   |

| t <sub>su(SFC)</sub>  | Setup time, DSF before CAS low                                            |                                     | tFSC              | 0                   |         | 0   |         | ns   |

| t <sub>su(SFR)</sub>  | Setup time, DSF before RAS low                                            |                                     | tFSR              | 0                   |         | 0   |         | ns   |

| t <sub>su</sub> (TRG) | Setup time, TRG before RAS low                                            | Setup time, TRG before RAS low      |                   | 0                   |         | 0   |         | ns   |

| t <sub>su(WCH)</sub>  | Setup time, WEx low before CAS high, write                                |                                     | tCWL              | 15                  |         | 15  |         | ns   |

| t <sub>su(WCL)</sub>  | Setup time, first WEx low before CAS low, early write                     |                                     | twcs              | 0                   |         | 0   |         | ns   |

| t <sub>su(WMR)</sub>  | Setup time, WEx low before RAS low, write-per-bit                         |                                     | tWSR              | 0                   |         | 0   |         | ns   |

| t <sub>su(WRH)</sub>  | Setup time, WEx low before RAS high, write                                |                                     | tRWL              | 15                  |         | 15  |         | ns   |

| th(CHrd)              | Hold time, both WEx high after CAS high, read (see Note 12)               |                                     | <sup>t</sup> RCH  | 0                   |         | 0   |         | ns   |

| th(CLCA)              | Hold time, column address after CAS low                                   |                                     | t <sub>CAH</sub>  | 10                  |         | 10  |         | ns   |

| th(CLD)               | Hold time, data valid after CAS low, early write                          |                                     | <sup>t</sup> DH   | 15                  |         | 15  |         | ns   |

| th(CLQ)               | Hold time, DQ output after CAS low (TMS551x6)                             |                                     | <sup>t</sup> DHC  | 4                   |         | 5   |         | ns   |

<sup>†</sup> Timing measurements are referenced to VIL max and VIH min.

NOTES: 9. Cycle time assumes  $t_t = 3$  ns.

<sup>12.</sup> Either th(RHrd) or th(CHrd) must be satisfied for a read cycle.

<sup>10.</sup> In a read- $\frac{\text{modify-write cycle}}{\text{CAS}}$  low time [ $t_{\text{W(CL)}}$ ] and  $t_{\text{SU(WCH)}}$  must be observed. Depending on the user's transition times, this can require additional  $\frac{1}{\text{CAS}}$  low time [ $t_{\text{W(CL)}}$ ].

<sup>11.</sup> In a read-modify-write cycle, t<sub>d(RLWL)</sub> and t<sub>su(WRH)</sub> must be observed. Depending on the user's transition times, this can require additional RAS low time [t<sub>w(RL)</sub>].

SMVS463 - DECEMBER 1995

# timing requirements over recommended ranges of supply voltage and operating free-air temperature (continued) $^{\dagger}$

|                       |                                                                                                                   | ALT.             | '551x | x-60 | '551x | x-70 |      |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|------------------|-------|------|-------|------|------|

|                       |                                                                                                                   | SYMBOL           | MIN   | MAX  | MIN   | MAX  | UNIT |

| th(CLW)               | Hold time, first WEx low after CAS low, early write                                                               | tWCH             | 10    |      | 15    |      | ns   |

| th(RA)                | Hold time, row address after RAS low                                                                              | <sup>t</sup> RAH | 10    |      | 10    |      | ns   |

| th(RDQ)               | Hold time, write mask valid after RAS low, non-persistent write-per-bit                                           | tMH              | 10    |      | 10    |      | ns   |