- Cancels the Acoustic Echo Common in Hands-Free Use of Cellular Phones in **Automobiles**

- Eliminates Echo Created by Speaker **Output Feeding Back Into the** Microphone

- Suppresses Wind, Engine, and Tire Noise

- Line Echo Canceler

- Standard Independent - IS-54B, IS-136, GSM, AMPS, IS-95

- Continuous, Automatic Adaptation to **Changing Acoustic Environment** - Initial System Training Not Required

- Based on TMS320C5x Platforms

- Support for Industry Standard **Microcontrollers**

- Interfaces Easily with TI's Voice Codec, the **TCM320AC36**

- Acoustic Echo Canceler Performance

- Length of Echo Path up to 44 ms

- Initial Adaptation Rate > 20 dB/s for **Speech Signals**

- Zero Speech Delay

- Echo Return Loss up to 30 dB for Speech Echo in Automobiles and 41 dB for Sine Wave Input

- Noise Suppressor Performance

- Up to 10 dB Noise Suppression for Hands-Free Use of Cellular Phones in **Automobiles Without Distorting Speech** Signals

- 16 ms Processing Delay

- Continuous Adaptation

- Demonstration Platform

- Allows Evaluation of Software Algorithm Performance in Lab and Automobile

- Ability to Enable/Disable AEC, ANS, and **LEC**

## description

For the cellular phone cradle market, the TMS320WP010 provides enhanced quality, full-duplex, hands-free communications. The 'WP010 is a ROM-coded DSP that provides all the adaptive filtering and processing necessary for acoustic echo cancellation (AEC), line echo cancellation (LEC), and adaptive noise suppression (ANS).

The 'WP010's acoustic echo cancellation function is based on a Finite Impulse Response (FIR) filter with an adaptive coefficient updating algorithm. The adaptive algorithm updates continuously so that it can constantly track acoustic path changes from the speaker to the microphone. Based upon FIR filter coefficients, the echo signal can be estimated and subtracted from the observed signal at the microphone. The acoustic echo cancellation function provides continuous adaptation and needs no initial system training. It is capable of canceling an echo path of up to 44 milliseconds and provides up to 30 dB cancellation for speech signals. In addition, the initial convergence rate is faster than 20 dB per second.

The line echo cancellation function cancels the near-end speech that has been reflected at the network switch and transmitted back to the cellular phone. The principle of the line echo cancellation function is very similar to that of the acoustic echo cancellation function. The difference is that the line echo cancellation function is designed to cancel the echo signal caused by network feedback due to impedance mismatch in the network circuit. The line echo cancellation function is capable of canceling a line echo path of up to 16 milliseconds.

The received signal at the microphone consists of the near-end speech signal, acoustic feedback echo, and ambient noise from the environment. The purpose of the adaptive noise suppression function is to suppress ambient noise components without distorting near-end speech. The initial adaptation rate is about 3 dB per second without initial system training. It tracks the changes of the noise characteristics and suppresses noise accordingly. The adaptive noise suppression provides up to 10 dB of noise cancellation without degrading near-end speech.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

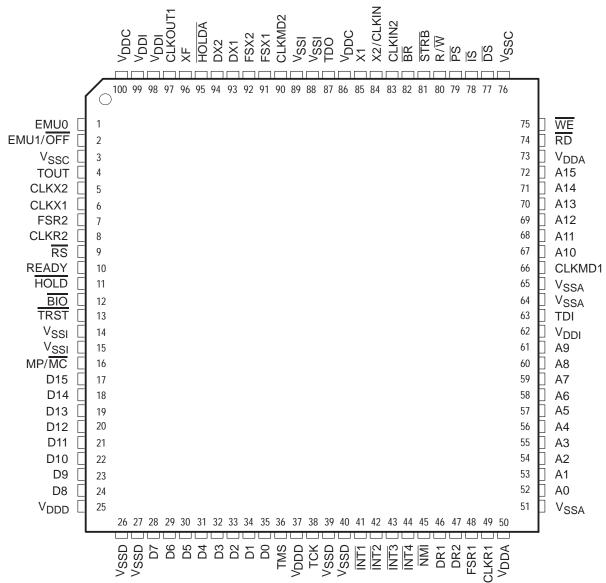

## Pin Functions for Devices in the PZ Package

| SIGNAL           | TYPE  | DESCRIPTION                                                                |

|------------------|-------|----------------------------------------------------------------------------|

|                  | •     | PARALLEL INTERFACE BUS                                                     |

| A0-A15           | I/O/Z | 16-bit external address bus (MSB: A15, LSB: A0)                            |

| D0-D15           | I/O/Z | 16-bit external data bus (MSB: D15, LSB: D0)                               |

| PS, DS, IS       | O/Z   | Program, data, and I/O space select outputs, respectively                  |

| STRB             | I/O/Z | Timing strobe for external cycles and external DMA                         |

| $R/\overline{W}$ | I/O/Z | Read/write select for external cycles and external DMA                     |

| RD, WE           | O/Z   | Read and write strobes, respectively, for external cycles                  |

| READY            | I     | External bus ready/wait-state control input                                |

| BR               | I/O/Z | Bus request. Arbitrates global memory and external DMA                     |

|                  |       | SYSTEM INTERFACE/CONTROL SIGNALS                                           |

| RS               | I     | Reset. Initializes device and sets PC to zero                              |

| MP/MC            | I     | Microprocessor/microcomputer mode select. Enables internal ROM             |

| HOLD             | 1     | Puts parallel I/F bus in high-impedance state after current cycle          |

| HOLDA            | O/Z   | Hold acknowledge. Indicates external bus in hold state                     |

| XF               | O/Z   | External flag output. Set/cleared through software                         |

| BIO              | I     | I/O branch input. Implements conditional branches                          |

| TOUT             | O/Z   | Timer output signal. Indicates output of internal timer                    |

| INT1-INT4        | 1     | External interrupt inputs                                                  |

| NMI              | 1     | Nonmaskable external interrupt                                             |

|                  |       | SERIAL PORT INTERFACE                                                      |

| DR1, DR2         | I     | Serial receive-data input                                                  |

| DX1, DX2         | O/Z   | Serial transmit-data output. In high-impedance state when not transmitting |

| CLKR1, CLKR2     | 1     | Serial receive-data clock input                                            |

| CLKX1, CLKX2     | I/O/Z | Serial transmit-data clock. Internal or external source                    |

| FSR1, FSR2       | 1     | Serial receive-frame-synchronization input                                 |

| FSX1, FSX2       | I/O/Z | Serial transmit-frame-synchronization signal. Internal or external source  |

## LEGEND:

I = Input

O = Output Z = High impedance

## TMS320WP010 **DIGITAL SIGNAL PROCESSOR** FOR AEC/LEC/ANS SPRS040-OCTOBER 1995

## Pin Functions for Devices in the PZ Package (Continued)

| TYPE  | DESCRIPTION                                                        |

|-------|--------------------------------------------------------------------|

|       | EMULATION/JTAG INTERFACE                                           |

| I     | JTAG-test-port scan data input                                     |

| O/Z   | JTAG-test-port scan data output                                    |

| I     | JTAG-test-port mode select input                                   |

| I     | JTAG-port clock input                                              |

| I     | JTAG-port reset (with pull-down resistor). Disables JTAG when low  |

| I/O/Z | Emulation control 0. Reserved for emulation use                    |

| I/O/Z | Emulation control 1. Puts outputs in high-impedance state when low |

|       | CLOCK GENERATION AND CONTROL                                       |

| 0     | Oscillator output                                                  |

| I     | Clock/oscillator input                                             |

| I     | Clock input                                                        |

| I     | Clock-mode select inputs                                           |

| I/O/Z | Device system-clock output                                         |

|       | POWER SUPPLY CONNECTIONS                                           |

| S     | Supply connection, address-bus output                              |

| S     | Supply connection, data-bus output                                 |

| S     | Supply connection, control output                                  |

| S     | Supply connection, internal logic                                  |

| S     | Supply connection, address-bus output                              |

| S     | Supply connection, data-bus output                                 |

| S     | Supply connection, control output                                  |

| S     | Supply connection, internal logic                                  |

|       | I                                                                  |

## LEGEND:

I = Input O = Output

S = Supply Z = High impedance

### architecture

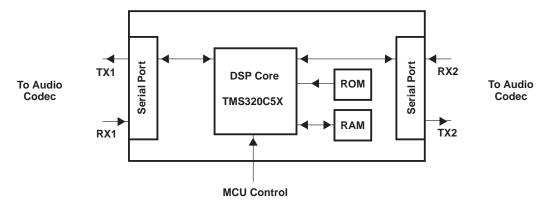

The 'WP010 architecture is based on the TMS320C5x Digital Signal Processor as shown in Figure 1. The 'WP010 sends/receives data through two serial ports available in the device. The first serial port (both RX1 and TX1) should be connected to the audio codec to interface with the phone line (in the cradle). The other serial port (RX2 and TX2) should be connected to the audio codec for the microphone and the speaker interfaces. The necessary software for the 'WP010 is ROM-coded and contained in ROM space. The 'WP010 also provides an MCU control interface to receive control commands from an MCU. The MCU control commands include the ability to reset the 'WP010 and to enable/disable some functions of the 'WP010.

Figure 1. TMS320WP010 Architecture

## functional description

The 'WP010 contains three main functional blocks: the adaptive line echo canceler, the adaptive acoustic echo canceler, and the adaptive noise suppressor. All three functions can be enabled or disabled by MCU control commands.

#### line echo canceler

The line echo canceler is to cancel the feedback line echo between two ports: RX1 and TX1. This function is performed by estimating the line echo path adaptively and subtracting it from the input signal. The line echo canceler cancels up to 16 milliseconds of line echo.

#### acoustic echo canceler

The purpose of the acoustic echo canceler (AEC) is to cancel the feedback acoustic echo from TX2 (interfaced with the speaker) to RX2 (interfaced with the microphone). The signal from the microphone (via RX2) is subtracted from the estimate of the acoustic echo path. The acoustic echo canceler is capable of canceling an echo up to 44 milliseconds long.

## adaptive noise suppressor

The purpose of the adaptive noise suppressor (ANS) is to selectively suppress noise from the signal coming from the microphone (via RX2) without distorting near-end speech. Near-end speech is the desired speech signal of the user of the hands-free phone in a car. The adaptive noise suppressor tracks noise characteristics and suppresses accordingly. The ANS can suppress noise up to 10 dB.

#### development support

Texas Instruments offers a demonstration platform for the 'WP010. This platform contains all software modules including AEC, LEC, and ANS. There are switches that allow the algorithms to be turned on and off. The demonstration platform can be used in a lab or an automobile to fully evaluate the performance of the 'WP010.

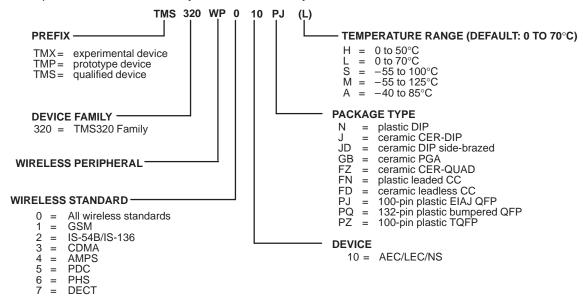

#### device nomenclature

To designate the stages in the product development cycle, Texas Instruments assigns prefixes to the part numbers of all TMS320 devices. Each TMS320 member has one of three prefixes: TMX, TMP, or TMS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMX) through fully qualified production devices/tools (TMS). This development flow is defined below.

**TMX** Experimental device that is not necessarily representative of the final device's electrical

specifications.

**TMP** Final silicon die that conforms to the device's electrical specifications but has not completed

quality and reliability verification.

**TMS** Fully-qualified production device

Predictions show that prototype devices (TMX or TMP) will have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate is still undefined. Only qualified production devices should be used.

TI™ device nomenclature also includes a suffix with the device family name. This suffix indicates the package type (for example, N, FN, or GB) and temperature range (for example, L). Figure 2 provides a legend for reading the complete device name for any TMS320WP family member.

Figure 2. TMS320WP Device Nomenclature

### documentation support

In addition to this data sheet, a product bulletin and demonstration platform user's guide are available.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>DD</sub> (see Note 1)  | $\dots$ - 0.3 V to 7 V |

|-----------------------------------------------------|------------------------|

| Input voltage range, V <sub>I</sub>                 | $\dots$ - 0.3 V to 7 V |

| Output voltage range, VO                            | 0.3 V to 7 V           |

| Operating ambient temperature range, T <sub>A</sub> | 40°C to 85°C           |

| Storage temperature range, T <sub>stq</sub>         | - 55°C to 150°C        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## NOTE 1: All voltage values are with respect to VSS.

## recommended operating conditions

|                |                                        |                                              | MIN   | NOM | MAX                  | UNIT |

|----------------|----------------------------------------|----------------------------------------------|-------|-----|----------------------|------|

| $V_{DD}$       | Supply voltage                         |                                              | 4.75  | 5   | 5.25                 | V    |

| VSS            | Supply voltage                         |                                              |       | 0   |                      | V    |

|                |                                        | X2/CLKIN, CLKIN2                             | 3     |     | V <sub>DD</sub> +0.3 |      |

| VIH            | High-level input voltage               | CLKX1, CLKX2, CLKR1, CLKR2                   | 2.5   |     | V <sub>DD</sub> +0.3 | V    |

|                |                                        | All others                                   | 2     |     | V <sub>DD</sub> +0.3 |      |

| \/             | Low-level input voltage                | X2/CLKIN, CLKIN2, CLKX1, CLKX2, CLKR1, CLKR2 | - 0.3 |     | 0.7                  | V    |

| VIL            | Low-level input voltage                | All others                                   | - 0.3 |     | 0.8                  | V    |

| loh            | High-level output current (see Note 2) |                                              |       |     | - 300                | μΑ   |

| lOL            | Low-level output current               |                                              |       |     | 2                    | mA   |

| TC             | Operating case temperature             |                                              | 0     |     | 85                   | °C   |

| T <sub>A</sub> | Operating ambient temperature (indu    | strial)                                      | -40   |     | 85                   | °C   |

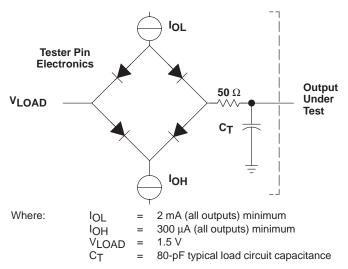

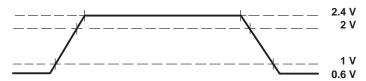

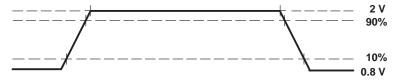

NOTE 2: Figure 3 shows the test load circuit and Figures 4 and 5 show the voltage reference levels.

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                         | PARAMETER                                                            | TEST CONDITIONS†                       | MIN   | TYP <sup>‡</sup> | MAX | UNIT   |  |

|-------------------------|----------------------------------------------------------------------|----------------------------------------|-------|------------------|-----|--------|--|

| Vон                     | High-level output voltage (see Note 2)                               | I <sub>OH</sub> = MAX                  | 2.4   | 3                |     | V      |  |

| VOL                     | Low-level output voltage (see Note 2)                                | I <sub>OL</sub> = MAX                  |       | 0.3              | 0.6 | V      |  |

| lo-                     | High-impedance output current (V <sub>DD</sub> = MAX)                | BR (with internal pull-up)             | - 500 |                  | 20  |        |  |

| loz                     | High-impedance output current (VDD = MAX)                            | All others                             | - 20  |                  | 20  | μΑ     |  |

|                         | Input current (V <sub>I</sub> = V <sub>SS</sub> to V <sub>DD</sub> ) | TRST (with internal pull-down)         | - 10  |                  | 800 |        |  |

| <b>.</b>                |                                                                      | TMS, TCK, TDI (with internal pull-ups) | - 500 |                  | 10  | ⊢ μA I |  |

| "                       |                                                                      | X2/CLKIN                               | - 50  |                  | 50  |        |  |

|                         |                                                                      | All other inputs                       | - 10  |                  | 10  |        |  |

| I <sub>DD(core)</sub>   | Supply current, core CPU                                             | V <sub>DD</sub> = 5.25 V               |       | 94               |     | mA     |  |

| I <sub>DD(pins)</sub>   | Supply current, pins                                                 | V <sub>DD</sub> = 5.25 V               |       | 63               |     | mA     |  |

| I <sub>DD</sub> (standb | y)Supply current, standby                                            | IDLE2, Clocks shut off                 |       | 5                |     | μΑ     |  |

| Ci                      | Input capacitance                                                    |                                        |       | 15               |     | pF     |  |

| Co                      | Output capacitance                                                   |                                        |       | 15               |     | pF     |  |

<sup>†</sup> For conditions shown as MIN/MAX, use the appropriate value specified under "recommended operating conditions".

<sup>‡</sup> Typical values are at  $V_{DD} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise specified.

NOTE 2: Figure 3 shows the test load circuit and Figures 4 and 5 show the voltage reference levels.

### PARAMETER MEASUREMENT INFORMATION

Figure 3. Test Load Circuit

## signal transition levels

TTL-output levels are driven to a minimum logic-high level of 2.4 V and to a maximum logic-low level of 0.6 V. Figure 4 shows the TTL-level outputs.

Figure 4. TTL-Level Outputs

TTL-output transition times are specified as follows:

- For a *high-to-low transition*, the level at which the output is said to be no longer high is 2 V, and the level at which the output is said to be low is 1 V.

- For a *low-to-high transition*, the level at which the output is said to be no longer low is 1 V, and the level at which the output is said to be high is 2 V.

Figure 5 shows the TTL-level inputs.

Figure 5. TTL-Level Inputs

TTL-compatible input transition times are specified as follows:

- For a *high-to-low transition* on an input signal, the level at which the input is said to be no longer high is 2 V, and the level at which the input is said to be low is 0.8 V.

- For a *low-to-high transition* on an input signal, the level at which the input is said to be no longer low is 0.8 V, and the level at which the input is said to be high is 2 V.

## **CLOCK CHARACTERISTICS AND TIMING**

The 'WP010 can use either its internal oscillator or an external frequency source for a clock. The clock mode is determined by the clock mode pins (CLKMD1 and CLKMD2). Table 1 shows the standard clock options available on the 'WP010.

**Table 1. Standard Clock Options**

| CLKMD1 | CLKMD2 | CLOCK SOURCE                                                                                  |

|--------|--------|-----------------------------------------------------------------------------------------------|

| 1      | 0      | PLL clock generator option                                                                    |

| 0      | 1      | Reserved for test purposes                                                                    |

| 1      | 1      | External divide-by-two option or internal divide-by-two clock option with an external crystal |

| 0      | 0      | External divide-by-two option with the internal oscillator disabled                           |

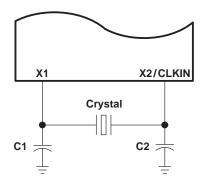

## internal divide-by-two clock option with external crystal

The internal oscillator is enabled by connecting a crystal across X1 and X2/CLKIN. The frequency of CLKOUT1 is one-half the crystal's oscillating frequency. The crystal should be in either fundamental or overtone operation and parallel resonant, with an effective series resistance of 30 ohms and a power dissipation of 1 mW; it should be specified at a load capacitance of 20 pF. Note that overtone crystals require an additional tuned-LC circuit. Figure 6 shows an external crystal (fundamental frequency) connected to the on-chip oscillator.

## recommended operating conditions for internal divide-by-two clock option

|                                        | MIN | NOM | MAX | UNIT |

|----------------------------------------|-----|-----|-----|------|

| f <sub>Clk</sub> Input clock frequency | 0†  |     | 80  | MHz  |

| C1, C2 Load capacitance                |     | 10  |     | pF   |

<sup>†</sup> This device utilizes a fully static design and, therefore, can operate with input clock cycle time (t<sub>C(CI)</sub>) approaching infinity. The device is characterized at frequencies approaching 0 Hz, but is tested at f<sub>Clk</sub> = 6.7 MHz to meet device test time requirements.

Figure 6. Internal Clock Option

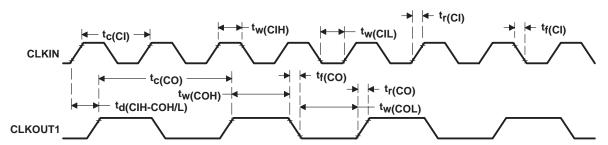

## external divide-by-two clock option

An external frequency source can be used by injecting the frequency directly into X2/CLKIN with X1 left unconnected, CLKMD1 set low, and CLKMD2 set low. This external frequency is divided by two to generate the internal machine cycle. The external frequency injected must conform to specifications listed in the timing requirements table.

## switching characteristics over recommended operating conditions [H = $0.5 t_{c(CO)}$ ] (see Figure 7)

|                     | PARAMETER                                     | MIN   | TYP                  | MAX   | UNIT |

|---------------------|-----------------------------------------------|-------|----------------------|-------|------|

| t <sub>C</sub> (CO) | Cycle time, CLKOUT1                           | 25    | 2t <sub>C</sub> (CI) | †     | ns   |

| td(CIH-COH/L)       | Delay time, X2/CLKIN high to CLKOUT1 high/low | 1     | 9                    | 18    | ns   |

| t <sub>f</sub> (CO) | Fall time, CLKOUT1                            |       | 4                    |       | ns   |

| t <sub>r(CO)</sub>  | Rise time, CLKOUT1                            |       | 4                    |       | ns   |

| tw(COL)             | Pulse duration, CLKOUT1 low                   | H – 3 | Н                    | H + 2 | ns   |

| tw(COH)             | Pulse duration, CLKOUT1 high                  | H – 3 | Н                    | H + 2 | ns   |

<sup>†</sup> This device utilizes a fully static design and, therefore, can operate with t<sub>C(CO)</sub> approaching infinity. The device is characterized at frequencies approaching 0 Hz but is tested at  $t_{C(CO)} = 300$  ns to meet device test time requirements

## timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figure 7)

|                     |                                  | MIN  | MAX | UNIT |

|---------------------|----------------------------------|------|-----|------|

| t <sub>C</sub> (CI) | Cycle time, X2/CLKIN             | 12.5 | †   | ns   |

| t <sub>f</sub> (CI) | Fall time, X2/CLKIN <sup>‡</sup> |      | 4   | ns   |

| tr(CI)              | Rise time, X2/CLKIN <sup>‡</sup> |      | 4   | ns   |

| tw(CIL)             | Pulse duration, X2/CLKIN low     | 5    | †   | ns   |

| tw(CIH)             | Pulse duration, X2/CLKIN high    | 5    | †   | ns   |

<sup>†</sup> This device utilizes a fully static design and, therefore, can operate with t<sub>C(CI)</sub> approaching infinity. The device is characterized at frequencies approaching 0 Hz, but is tested at a minimum of t<sub>C(CI)</sub> = 150 ns to meet device test time requirements.

<sup>&</sup>lt;sup>‡</sup> Values derived from characterization data and not tested

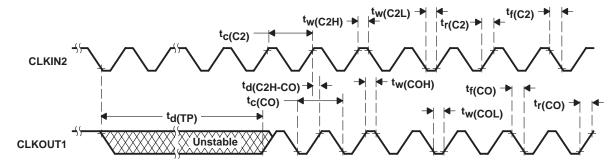

Figure 7. External Divide-by-Two Clock Timing

## PLL clock generator option

An external frequency source can be used by injecting the frequency directly into CLKIN2 with X1 left unconnected and X2 connected to V<sub>DD</sub>. This external frequency is multiplied by one or by two to generate the internal machine cycle. The multiply-by-one option is available on the 'WP010. The PLL clock generator option is used when CLKMD1 is strapped high and CLKMD2 is strapped low. The external frequency injected must conform to specifications listed in the timing requirements table.

## switching characteristics over recommended operating conditions [H = $0.5 t_{c(CO)}$ ] (see Figure 8)

|                     | PARAMETER                                                                        | MIN                | TYP | MAX                    | UNIT |

|---------------------|----------------------------------------------------------------------------------|--------------------|-----|------------------------|------|

| t <sub>C</sub> (CO) | Cycle time, CLKOUT1                                                              | 25                 |     | 55                     | ns   |

| t <sub>f</sub> (CO) | Fall time, CLKOUT1                                                               |                    | 4   |                        | ns   |

| t <sub>r(CO)</sub>  | Rise time, CLKOUT1                                                               |                    | 4   |                        | ns   |

| tw(COL)             | Pulse duration, CLKOUT1 low                                                      | H – 3 <sup>†</sup> | Н   | H + 2 <sup>†</sup>     | ns   |

| tw(COH)             | Pulse duration, CLKOUT1 high                                                     | H – 3 <sup>†</sup> | Н   | H + 2 <sup>†</sup>     | ns   |

| td(C2H-COH)         | Delay time, CLKIN2 high to CLKOUT1 high                                          | 1                  | 8   | 15                     | ns   |

| t <sub>d</sub> (TP) | Delay time, transitory phase—PLL synchronized after CLKIN2 supplied <sup>†</sup> |                    |     | 1000t <sub>C(C2)</sub> | ns   |

<sup>†</sup> Values assured by design and not tested

## timing requirements over recommended ranges of supply voltage and operating free-air temperature (see Figure 8)

|                     |                                     |                 | MIN | MAX                   | UNIT |

|---------------------|-------------------------------------|-----------------|-----|-----------------------|------|

| 4 (2-)              | Cycle time, CLKIN2                  | Multiply by one | 25  | 75†                   | ns   |

| t <sub>C</sub> (C2) | Cycle time, CLKINZ                  | Multiply by two | 50  | 150†                  | ns   |

| t <sub>f</sub> (C2) | (C2) Fall time, CLKIN2 <sup>‡</sup> |                 |     | 4                     | ns   |

| t <sub>r(C2)</sub>  | Rise time, CLKIN2 <sup>‡</sup>      |                 |     | 4                     | ns   |

| tw(C2L)             | Pulse duration, CLKIN2 low          |                 | 8   | t <sub>C</sub> (C2)-8 | ns   |

| tw(C2H)             | Pulse duration, CLKIN2 high         |                 | 8   | t <sub>C(C2)</sub> -8 | ns   |

<sup>†</sup> Clocks may only be stopped while executing IDLE2 when using the PLL clock generator option. Note that t<sub>d(TP)</sub> (the transitory phase) will occur when restarting clock from IDLE2 in this mode.

<sup>‡</sup> Values derived from characterization data and not tested

Figure 8. PLL Clock Generator Timing

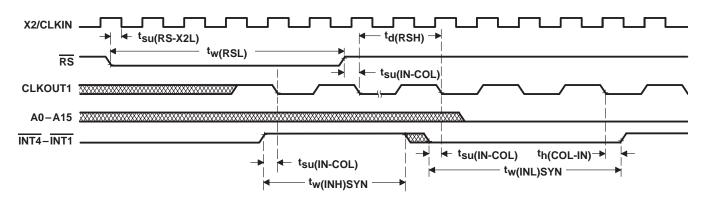

## **RESET AND INTERRUPT**

timing requirements over recommended ranges of supply voltage and operating free-air temperature [H =  $0.5t_{c(CO)}$ ] (see Figure 9)

|                          |                                                          | MIN      | MAX                 | UNIT |

|--------------------------|----------------------------------------------------------|----------|---------------------|------|

| t <sub>su</sub> (IN-COL) | Setup time, INT1-INT4, NMI before CLKOUT1 low†           | 10       |                     | ns   |

| tsu(RS-COL)              | Setup time, RS before CLKOUT1 low                        | 10       | 2H – 5 <sup>‡</sup> | ns   |

| t <sub>su(RS-X2L)</sub>  | Setup time, RS before X2/CLKIN low                       | 7        |                     | ns   |

| th(COL-IN)               | Hold time, INT1-INT4, NMI after CLKOUT1 low <sup>†</sup> | 0        |                     | ns   |

| tw(INL)SYN               | Pulse duration, INT1-INT4, NMI low, synchronous          | 4H + 10§ |                     | ns   |

| tw(INH)SYN               | Pulse duration, INT1-INT4, NMI high, synchronous         | 2H + 10§ |                     | ns   |

| tw(INL)ASY               | Pulse duration, INT1-INT4, NMI low, asynchronous‡        | 6H + 10§ |                     | ns   |

| tw(INH)ASY               | Pulse duration, INT1-INT4, NMI high, asynchronous‡       | 4H + 10§ |                     | ns   |

| tw(RSL)                  | Pulse duration, RS low                                   | 12H      | ·                   | ns   |

| t <sub>d</sub> (RSH)     | Delay time, RS high to reset vector fetch                | 34H      | ·                   | ns   |

<sup>†</sup> These parameters must be met to use the synchronous timings. Both reset and the interrupts can operate asynchronously. The pulse durations require an extra half-cycle to ensure internal synchronization.

<sup>§</sup> If in IDLE2, add 4H to these timings.

Figure 9. Reset and Interrupt Timing

<sup>&</sup>lt;sup>‡</sup> Values derived from characterization data and not tested

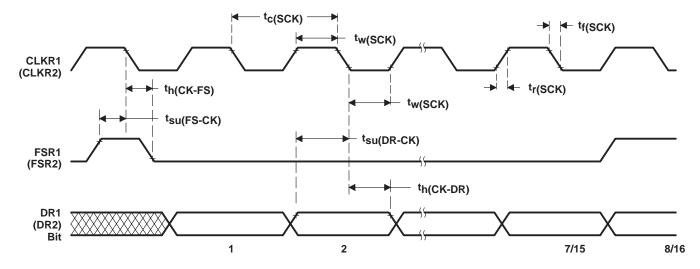

## **SERIAL-PORT RECEIVE**

# timing requirements over recommended ranges of supply voltage and operating free-air temperature [H = $0.5t_{c(CO)}$ ] (see Figure 10)

|                        |                                                           | MIN               | MAX | UNIT |

|------------------------|-----------------------------------------------------------|-------------------|-----|------|

| t <sub>c</sub> (SCK)   | Cycle time, serial-port clock                             | 5.2H <sup>†</sup> | ‡   | ns   |

| t <sub>f</sub> (SCK)   | Fall time, serial-port clock                              |                   | 6§  | ns   |

| tr(SCK)                | Rise time, serial-port clock                              |                   | 6§  | ns   |

| tw(SCK)                | Pulse duration, serial-port clock low/high                | 2.1H <sup>†</sup> |     | ns   |

| t <sub>su(FS-CK)</sub> | Setup time, FSR1 (FSR2) before CLKR1 (CLKR2) falling edge | 7                 |     | ns   |

| t <sub>su(DR-CK)</sub> | Setup time, DR1 (DR2) before CLKR1 (CLKR2) falling edge   | 7                 |     | ns   |

| th(CK-FS)              | Hold time, FSR1 (FSR2) after CLKR1 (CLKR2) falling edge   | 7                 |     | ns   |

| th(CK-DR)              | Hold time, DR1 (DR2) after CLKR1 (CLKR2) falling edge     | 7                 |     | ns   |

<sup>†</sup> Values ensured by design but not tested

<sup>§</sup> Values derived from characterization data and not tested

Figure 10. Serial-Port Receive Timing

<sup>&</sup>lt;sup>‡</sup> The serial-port design is fully static and, therefore, can operate with t<sub>c(SCK)</sub> approaching infinity. It is characterized approaching an input frequency of 0 Hz but tested at a much higher frequency to minimize test time.

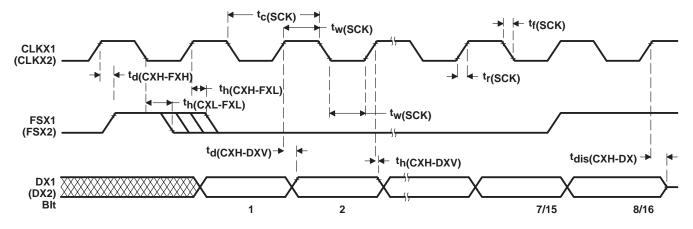

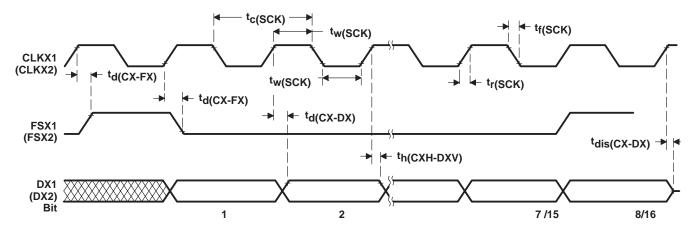

## SERIAL-PORT TRANSMIT, EXTERNAL CLOCKS, AND EXTERNAL FRAMES

## switching characteristics over recommended operating conditions (see Note 3) (see Figure 11)

|              | PARAMETER                                                | MIN | MAX | UNIT |

|--------------|----------------------------------------------------------|-----|-----|------|

| td(CXH-DXV)  | Delay time, DX1 (DX2) valid after CLKX1 (CLKX2) high     |     | 25  | ns   |

| tdis(CXH-DX) | Disable time, DX1 (DX2) invalid after CLKX1 (CLKX2) high |     | 40† | ns   |

| th(CXH-DXV)  | Hold time, DX1 (DX2) valid after CLKX1 (CLKX2) high      | - 5 |     | ns   |

## timing requirements over recommended ranges of supply voltage and operating free-air temperature $[H = 0.5t_{C(CO)}]$ (see Note 3) (see Figure 11)

|                      |                                                       | MIN               | MAX     | UNIT |

|----------------------|-------------------------------------------------------|-------------------|---------|------|

| t <sub>C</sub> (SCK) | Cycle time, serial-port clock                         | 5.2H <sup>‡</sup> | §       | ns   |

| tf(SCK)              | Fall time, serial-port clock                          |                   | 6†      | ns   |

| tr(SCK)              | Rise time, serial-port clock                          |                   | 6†      | ns   |

| tw(SCK)              | Pulse duration, serial-port clock low/high            | 2.1H <sup>‡</sup> |         | ns   |

| td(CXH-FXH)          | Delay time, FSX1 (FSX2) high after CLKX1 (CLKX2) high |                   | 2H – 8  | ns   |

| th(CXL-FXL)          | Hold time, FSX1 (FSX2) low after CLKX1 (CLKX2) low    | 7                 |         | ns   |

| th(CXH-FXL)          | Hold time, FSX1 (FSX2) low after CLKX1 (CLKX2) high   |                   | 2H – 8¶ | ns   |

<sup>†</sup> Values derived from characterization data and not tested

NOTE 3: Internal clock with external FSX1 (FSX2) and vice versa are also allowable. However, FSX1 (FSX2) timings to CLKX1 (CLKX2) are always defined depending on the source of FSX1 (FSX2), and CLKX1 (CLKX2) timings are always dependent upon the source of CLKX1 (CLKX2). Specifically, the relationship of FSX1 (FSX2) to CLKX1 (CLKX2) is independent of the source of CLKX1 (CLKX2).

Figure 11. Serial-Port Transmit Timing of External Clocks and External Frames

<sup>‡</sup> Values ensured by design but not tested

<sup>§</sup> The serial-port design is fully static and, therefore, can operate with t<sub>C(SCK)</sub> approaching infinity. It is characterized approaching an input frequency of 0 Hz but tested at a much higher frequency to minimize test time.

If the FSX1 (FSX2) pulse does not meet this specification, the first bit of serial data will be driven on the DX1 (DX2) pin until the falling edge of FSX1 (FSX2). After the falling edge of FSX1 (FSX2), data will be shifted out on the DX1 (DX2) pin. The transmit buffer empty interrupt will be generated when the th(CXL-FXL) and th(CXH-FXL) specification is met.

# SERIAL-PORT TRANSMIT, INTERNAL CLOCKS, AND INTERNAL FRAMES (SEE NOTE 3)

## switching characteristics over recommended operating conditions [H = $0.5t_{c(CO)}$ ] (see Figure 12)

|                      | PARAMETER                                            | MIN     | TYP | MAX | UNIT |

|----------------------|------------------------------------------------------|---------|-----|-----|------|

| td(CX-FX)            | Delay time, CLKX1 (CLKX2) rising edge to FSX1 (FSX2) | - 4     |     | 18  | ns   |

| td(CX-DX)            | Delay time, CLKX1 (CLKX2) rising edge to DX1 (DX2)   |         |     | 18  | ns   |

| tdis(CX-DX)          | Disable time, CLKX1 (CLKX2) rising edge to DX1 (DX2) |         |     | 29† | ns   |

| t <sub>c</sub> (SCK) | Cycle time, serial-port clock                        |         | 8H  |     | ns   |

| tf(SCK)              | Fall time, serial-port clock                         |         | 4   |     | ns   |

| tr(SCK)              | Rise time, serial-port clock                         |         | 4   |     | ns   |

| tw(SCK)              | Pulse duration, serial-port clock low/high           | 4H – 14 |     |     | ns   |

| th(CXH-DXV)          | Hold time, DX1 (DX2) valid after CLKX1 (CLKX2) high  | - 4     |     |     | ns   |

† Values derived from characterization data and not tested

NOTE 3: Internal clock with external FSX1 (FSX2) and vice versa are also allowable. However, FSX1 (FSX2) timings to CLKX1 (CLKX2) are always defined depending on the source of FSX1 (FSX2), and CLKX1 (CLKX2) timings are always dependent upon the source of CLKX1 (CLKX2). Specifically, the relationship of FSX1 (FSK2) to CLKX1 (CLKX2) is independent of the source of CLKX1 (CLKX2).

Figure 12. Serial-Port Transmit Timing of Internal Clocks and Internal Frames

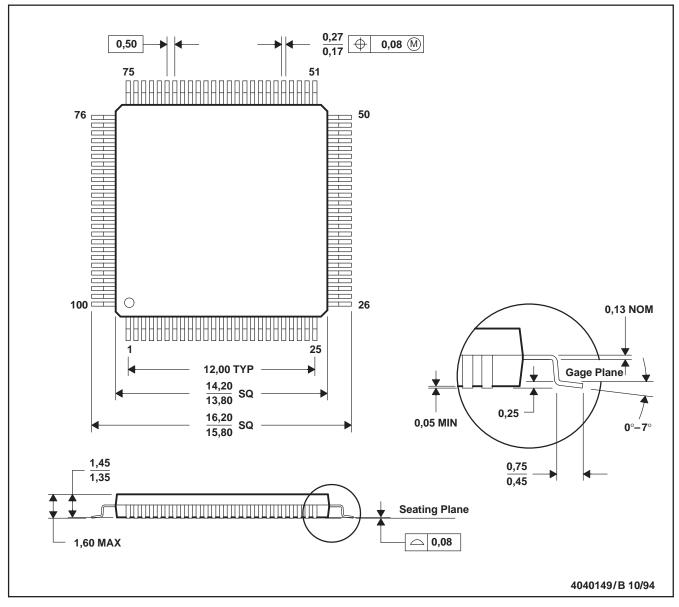

## **MECHANICAL DATA**

## PZ (S-PQFP-G100)

### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MO-136

## PACKAGE OPTION ADDENDUM

30-Mar-2005

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins Package<br>Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|---------------------|-------------------------|------------------|------------------------------|

| TMS320WP010PZ    | OBSOLETE              | LQFP            | PΖ                 | 100                 | TBD                     | Call TI          | Call TI                      |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS) or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2005, Texas Instruments Incorporated