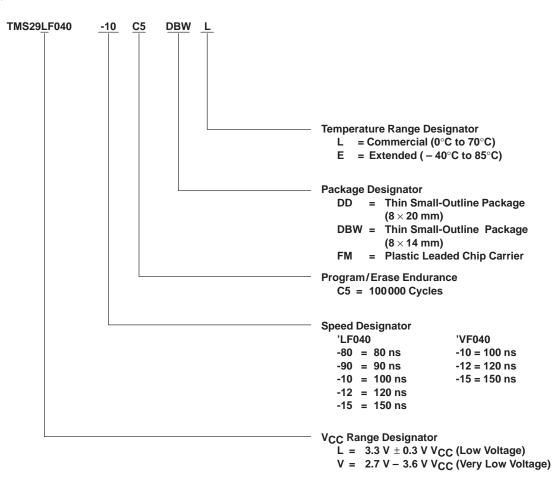

## TMS29LF040, TMS29VF040 524288 BY 8-BIT FLASH MEMORIES SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

- Single Power Supply

3.3 V ± 0.3 V TMS29LF040

2.7 V to 3.6 V TMS29VF040

5 V ± 10% See TMS29F040 Data sheet (Literature Number SMJS820)

- Organization ... 524288 By 8 Bits

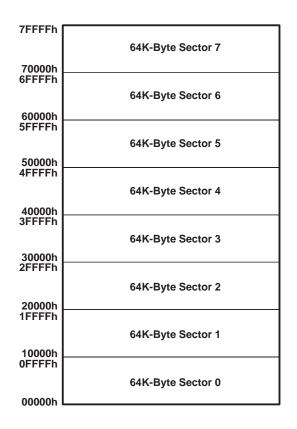

- Eight Equal Sectors of 64K Bytes

- Any Combination of Sectors Can Be Erased

- Any Combination of Sectors Can Be Marked as Read-Only

- Compatible With JEDEC Electrically Erasable Programmable Read-Only Memory (EEPROM) Command Set

- Fully Automated On-Chip Erase and Byte-Program Operations

- 100000 Program/Erase Cycles

- Erase-Suspend/Erase-Resume Operation

- Compatible With JEDEC Byte-Wide Pinouts

- Low-Current Consumption

- Active Read . . . 20 mA Typical

- Active Program/Erase ... 30 mA Typical

- All Inputs/Outputs CMOS-Compatible Only

|                    | PIN NOMENCLATURE                               |

|--------------------|------------------------------------------------|

| A[0:18]<br>DQ[0:7] | Address Inputs<br>Inputs (programming)/Outputs |

| E                  | Chip Enable                                    |

| G                  | Output Enable                                  |

| VCC                | Power Supply                                   |

| VCC<br>VSS<br>W    | Ground                                         |

| W                  | Write Enable                                   |

## description

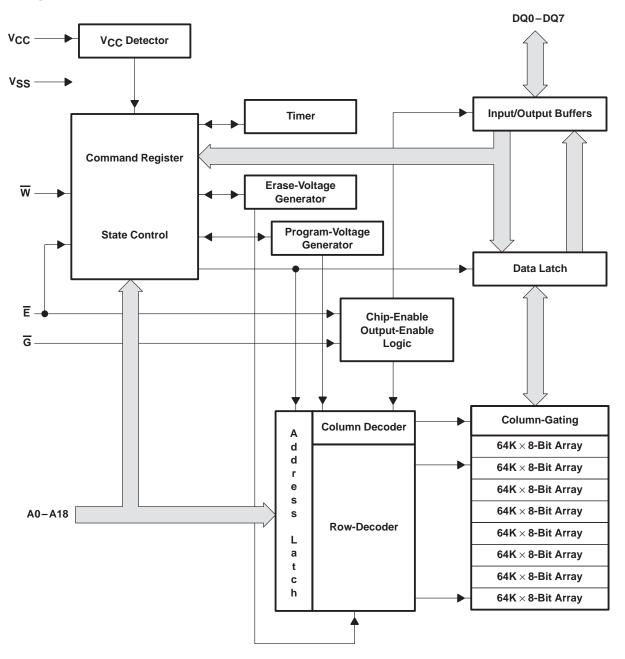

The TMS29LF040 and TMS29VF040 are 524288 by 8-bit (4194304-bit), low-voltage, single-supply, programmable read-only memories that can be erased electrically and reprogrammed. These devices are organized as eight independent 64K-byte sectors and are offered with access times between 80 ns and 150 ns.

An on-chip state machine controls the program and erase operations. The embedded-byte program and sector/chip-erase functions are fully automatic. The command set is compatible with that of JEDEC 4M-bit EEPROMs. A suspend/resume feature allows access to unaltered memory sectors during a sector-erase operation. Data protection of any sector combination is accomplished using a hardware sector-protection feature.

Device operations are selected by writing JEDEC-standard commands into the command register using standard microprocessor-write timings. The command register acts as input to an internal state machine that interprets the commands, controls the erase and programming operations, and outputs the status of the device, the data stored in the device, and the device algorithm-selection code. On initial power-up operation, the device defaults to the read mode.

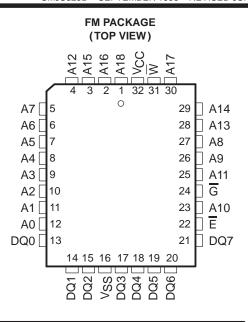

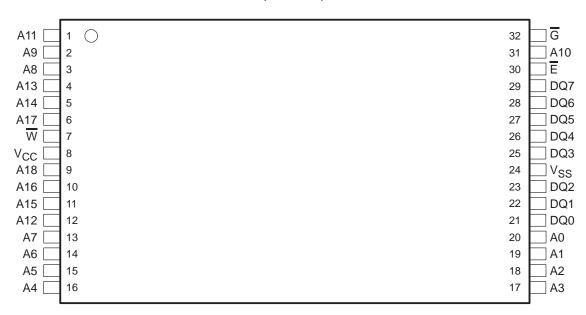

The TMS29xF040 is offered in a 32-pin 8 x 14 mm thin small-outline package (DBW suffix), a 32-pin 8 x 20 mm thin small-outline package (DD suffix), and a 32-pin plastic leaded chip carrier (FM suffix) using 1.27 mm (50-mil) lead pitch.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1998, Texas Instruments Incorporated

SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

**DBW and DD PACKAGES** (TOP VIEW)

## device symbol nomenclature

## block diagram

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

## memory-sector architecture

|          | A18 | A17 | A16 | Address Range   |

|----------|-----|-----|-----|-----------------|

| Sector 0 | 0   | 0   | 0   | 00000h – 0FFFFh |

| Sector 1 | 0   | 0   | 1   | 10000h – 1FFFFh |

| Sector 2 | 0   | 1   | 0   | 20000h – 2FFFFh |

| Sector 3 | 0   | 1   | 1   | 30000h – 3FFFFh |

| Sector 4 | 1   | 0   | 0   | 40000h – 4FFFFh |

| Sector 5 | 1   | 0   | 1   | 50000h – 5FFFFh |

| Sector 6 | 1   | 1   | 0   | 60000h – 6FFFFh |

| Sector 7 | 1   | 1   | 1   | 70000h – 7FFFFh |

## operation

| 11005                     | FUNCTIONS <sup>†</sup> |                 |               |               |               |               |                 |                            |  |  |

|---------------------------|------------------------|-----------------|---------------|---------------|---------------|---------------|-----------------|----------------------------|--|--|

| MODE                      | Ē                      | G               | W             | A0            | A1            | A6            | A9              | DQ0-DQ7                    |  |  |

| Read                      | VIL                    | VIL             | VIH           | A0            | A1            | A6            | A9              | Data out                   |  |  |

| Output disable            | VIL                    | VIH             | VIH           | Х             | Х             | Х             | Х               | Hi-Z                       |  |  |

| Standby and write inhibit | $V_{IH}$               | Х               | Х             | Х             | Х             | Х             | Х               | Hi-Z                       |  |  |

| Algorithm coloction mode  | \/                     | N/m             |               | VIL           | \/            | ) (n          |                 | Mfr. equivalent code 97h   |  |  |

| Algorithm-selection mode  | VIL                    | VIL             | VIH           | VIH           | VIL           | VIL           | VID             | Device equivalent code 94h |  |  |

| Write <sup>‡</sup>        | VIL                    | VIH             | VIL           | A0            | A1            | A6            | A9              | Data in                    |  |  |

| Sector-protect§           | VIL                    | V <sub>ID</sub> | VIL           | Х             | Х             | Х             | V <sub>ID</sub> | Х                          |  |  |

| Sector-protect verify§    | VIL                    | VIL             | VIH           | VIL           | VIH           | VIL           | VID             | Data out                   |  |  |

| Sector-unprotect§¶        | VID                    | VID             | VIL           | Х             | Х             | VIH           | VID             | Х                          |  |  |

| Sector-unprotect verify§  | VIL                    | VIL             | VIH           | VIL           | VIH           | VIH           | VID             | Data out                   |  |  |

| Erase operations          | VIL                    | VIH             | See<br>Note 1   | See Note 1                 |  |  |

Table 1 summarizes the operation modes.

Table 1. Operation Modes

<sup>†</sup> X can be V<sub>IL</sub> or V<sub>IH</sub>.

<sup>‡</sup> See Table 3 for valid address and data during write (byte program).

§ Operation at  $V_{CC} = 3.3$  V and  $T_A = 25^{\circ}C$ .

¶ Address pins A12 and A16 =  $V_{IH}$ . NOTE 1: See Figure 6 through Figure 9.

NOTE 1. See Figure 6 through

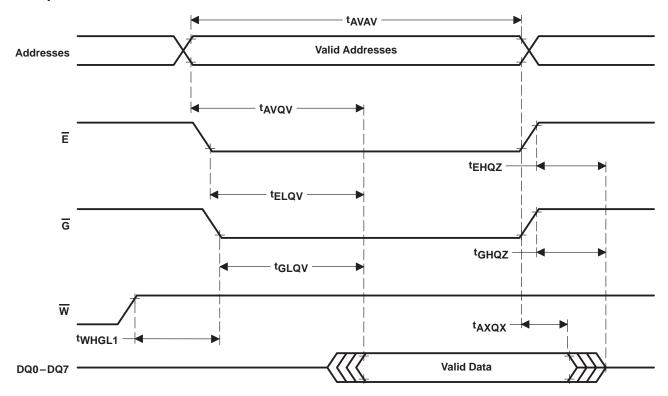

#### read mode

To read the output of the TMS29xF040, a low-level logic signal is applied to the  $\overline{E}$  and  $\overline{G}$  pins. When two or more TMS29xF040 devices are connected in parallel, the output of any one device can be read without interference. The  $\overline{E}$  pin is power control and is used for device selection. The  $\overline{G}$  pin is output control and is used to gate the data output onto the bus from the selected device.

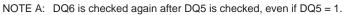

The address-access time ( $t_{AVQV}$ ) is the delay from stable address to valid output data. The chip-enable access time ( $t_{ELQV}$ ) is the delay from  $\overline{E} = V_{IL}$  and stable addresses to valid output data. The output-enable access time ( $t_{GLQV}$ ) is the delay from  $\overline{G} = V_{IL}$  to valid output data when  $\overline{E} = V_{IL}$  and addresses are stable for at least the duration of  $t_{AVQV} - t_{GLQV}$ .

## standby mode

The I<sub>CC</sub> supply current is reduced by applying a logic-high level on  $\overline{E}$  to enter the standby mode. In the standby mode, the outputs are placed in the high-impedance state. Applying a CMOS logic-high level on  $\overline{E}$  reduces the current to 100  $\mu$ A maximum.

If the TMS29xF040 is deselected during erasure or programming, the device continues to draw active current until the operation is complete.

## output disable

When either  $\overline{G} = V_{IH}$  or  $\overline{E} = V_{IH}$ , output from the device is disabled and the output pins (DQ0-DQ7) are placed in the high-impedance state.

#### algorithm selection mode

The algorithm-selection mode provides access to a binary code that matches the device with its proper programming- and erase-command operations. This mode is activated when  $V_{ID}$  (11.5 V to 12.5 V) is placed on address pin A9. Address pins A1 and A6 must be logic low. Two bytes of code are accessed by toggling the address pin A0 from  $V_{IL}$  to  $V_{IH}$ . All other address pins can be logic low or logic high.

The algorithm-selection code also can be read by using the command register, which is useful when  $V_{ID}$  is not available to be placed on address pin A9. Table 2 lists the binary algorithm-selection codes for the TMS29xF040.

| ALGORITHM SELECTION | A0 | DQ7 | DQ6 | DQ5 | DQ4 | DQ3 | DQ2 | DQ1 | DQ0 | HEX |

|---------------------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Byte 0              | 0  | 1   | 0   | 0   | 1   | 0   | 1   | 1   | 1   | 97h |

| Byte 1              | 1  | 1   | 0   | 0   | 1   | 0   | 1   | 0   | 0   | 94h |

## Table 2. Algorithm-Selection Codes<sup>†</sup>

$\uparrow$  A1 = V<sub>IL</sub>, A6 = V<sub>IL</sub>, E = V<sub>IL</sub>, G = V<sub>IL</sub>

## erasure and programming

Erasure and programming of the TMS29xF040 are accomplished by writing a sequence of commands using standard microprocessor write timings. The commands are written to a command register and input to the command-state machine (CSM). The CSM interprets the command entered and initiates program, erase, suspend, and resume operations as instructed. The CSM acts as the interface between the write-state machine (WSM) and the external chip operations. The WSM controls all voltage generation, pulse generation, preconditioning, and verification of the memory contents. Program and sector/chip-erase functions are fully automatic. When the end of a program or erase operation is reached, the device internally resets to the read mode. If a byte-program or chip-erase operation is in progress, additional program/erase commands are ignored until the operation in progress is completed.

## command definitions

Device operating modes are selected by writing specific address and data sequences into the command register. Table 3 defines the valid command sequences. Writing incorrect address and data values or writing them in the incorrect sequence causes the device to reset to the read mode. The command register does not occupy an addressable memory location. The register stores the command sequence along with the address and data needed by the memory array. Commands are written by setting  $\overline{E} = V_{IL}$  and  $\overline{G} = V_{IH}$  and bringing  $\overline{W}$  from  $V_{IH}$  to  $V_{IL}$ . Addresses are latched on the falling edge of  $\overline{W}$  and data is latched on the rising edge of  $\overline{W}$ . Holding  $\overline{W} = V_{IL}$  and toggling  $\overline{E}$  is an alternative method. See the byte-program and chip/sector-erase sections for a more complete description.

## command definitions (continued)

| COMMAND                 | BUS<br>CYCLES | 1ST CYCLE<br>ADDR DATA | 2ND CYCLE<br>ADDR DATA                            | 3RD CYCLE<br>ADDR DATA | 4TH CYCLE<br>ADDR DATA | 5TH CYCLE<br>ADDR DATA | 6TH CYCLE<br>ADDR DATA |  |  |  |

|-------------------------|---------------|------------------------|---------------------------------------------------|------------------------|------------------------|------------------------|------------------------|--|--|--|

| Read <sup>‡</sup>       | 1             | RA RD                  |                                                   |                        |                        |                        |                        |  |  |  |

| Reset/Read <sup>§</sup> | 2             | XXXXh F0h              | RA RD                                             |                        |                        |                        |                        |  |  |  |

| Resel/Reads             | 4             | 5555h AAh              | 2AAAh 55h                                         | 5555h F0h              | RA RD                  |                        |                        |  |  |  |

| Algorithm selection     | 4             | 5555h AAh              | 2AAAh 55h                                         | 5555h 90h              | RA RD                  |                        |                        |  |  |  |

| Byte program            | 4             | 5555h AAh              | 2AAAh 55h                                         | 5555h A0h              | PA PD                  |                        |                        |  |  |  |

| Chip erase              | 6             | 5555h AAh              | 2AAAh 55h                                         | 5555h 80h              | 5555h AAh              | 2AAAh 55h              | 5555h 10h              |  |  |  |

| Sector erase            | 6             | 5555h AAh              | 2AAAh 55h                                         | 5555h 80h              | 5555h AAh              | 2AAAh 55h              | SA 30h                 |  |  |  |

| Sector-erase suspend    |               | XXXXh B0h              | Erase-suspend valid during sector-erase operation |                        |                        |                        |                        |  |  |  |

| Sector-erase resume     |               | XXXXh 30h              | Erase-resume v                                    | alid only after era    | ase-suspend            |                        |                        |  |  |  |

## Table 3. Command Definitions<sup>†</sup>

RA = Address of the location to be read

PA = Address of the location to be programmed

SA = Address of the sector to be erased

Addresses A16, A17, and A18 select one of eight sectors

RD = Data to be read at selected address location

PD = Data to be programmed at selected address location

<sup>+</sup> Address pins A15, A16, A17, A18 = V<sub>IL</sub> or V<sub>IH</sub> for all bus cycle addresses except for program address (PA), sector address (SA), and read address (RA).

<sup>‡</sup>No command cycles are required when the device is in read mode.

§ The reset command is required to return to the read mode when the device is in the algorithm-selection mode or if DQ5 goes high.

#### reset/read command

The read mode is activated by writing either of the two reset command sequences into the command register. The device remains in this mode until another valid command sequence is input into the command register. Memory data is available in the read mode and can be read with standard microprocessor read-cycle timing.

On power up, the device defaults to the read mode; therefore, a reset command sequence is not required and memory data is available.

## algorithm-selection command

The algorithm-selection command allows access to a binary code that matches the device with the proper programming and erase-command operations. After writing the three-bus-cycle command sequence, the first byte of the algorithm-selection code (97h) can be read from address XX00h. The second byte of the code (94h) can be read from address XX01h (see Table 2). This mode remains in effect until another valid command sequence is written to the device.

Sector-protection can be determined using the algorithm-selection command. After issuing the three-bus-cycle command sequence, the sector-protection status can be read on DQ0. Set address pins A0 =  $V_{IL}$  and A1 =  $V_{IH}$ . The sector address pins A16, A17, and A18 select the sector to be checked. The remaining address pins can be  $V_{IL}$  or  $V_{IH}$ . If the sector selected is protected, DQ0 outputs a 1. If the sector selected is not protected, DQ0 outputs a 0. This mode remains in effect until another valid command sequence is written to the device.

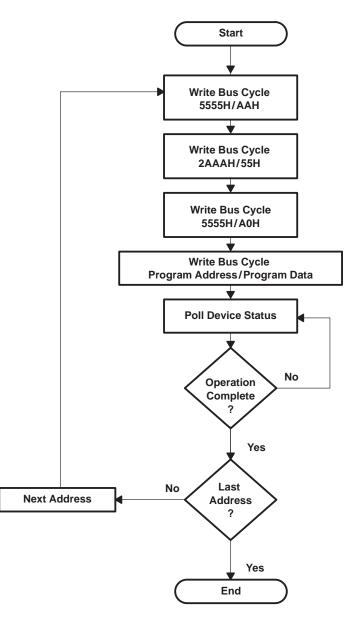

## byte-program command

Byte-programming is a four-bus-cycle command sequence. The first three bus cycles put the device into the program-setup state. The fourth bus cycle loads the address location and the data to be programmed into the device. The addresses are latched on the falling edge of  $\overline{W}$  and the data is latched on the rising edge of  $\overline{W}$  in the fourth bus cycle. The rising edge of  $\overline{W}$  starts the byte-program operation. The embedded byte-programming function automatically provides voltage and timing to program and to verify the cell margin. Any further commands written to the device during the program operation are ignored.

#### byte-program command (continued)

Programming can be performed at any address location in any order, resulting in logic 0s being programmed into the device. Attempting to program a logic 1 into a bit that was previously programmed to a logic 0 causes the internal pulse counter to exceed the pulse-count limit. This sets the exceed-timing-limit indicator (DQ5) to a logic-high state. Only an erase operation can change bits from logic 0s to logic 1s. When erased, all bits become logic 1. Figure 3 shows a flow chart of the typical byte-programming operation.

The status of the device during the automatic programming operation can be monitored for completion using the data-polling feature or the toggle-bit feature. See the operation status section for a full description.

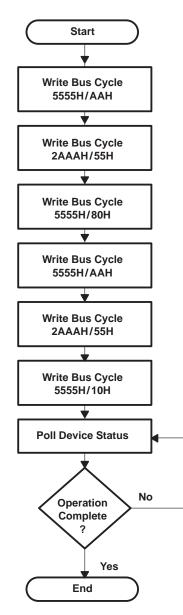

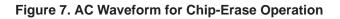

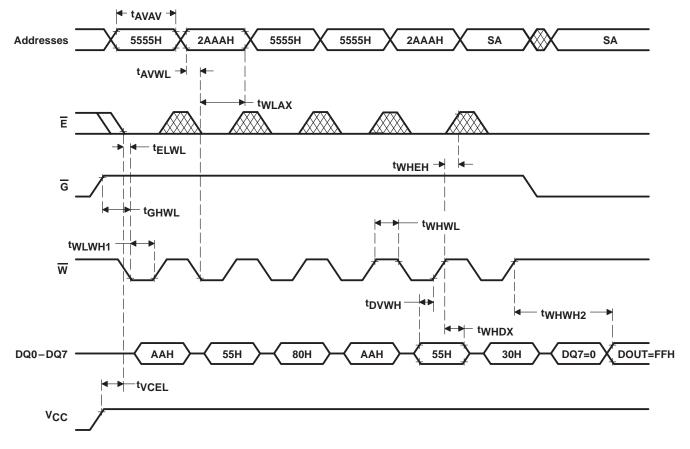

#### chip-erase command

Chip erase is a six-bus-cycle command sequence. The first three bus cycles put the device into the erase-setup state. The next two bus cycles unlock the erase mode and then the sixth bus cycle loads the chip-erase command. This command sequence is required to ensure that the memory contents are not erased accidentally. The rising edge of  $\overline{W}$  starts the chip-erase operation. Any further commands written to the device during the chip-erase operation are ignored.

The embedded chip-erase function automatically provides the voltage and timing needed to program and verify all the memory cells prior to electrical erase, and then erases and verifies the cell margin automatically. The user is not required to program the memory cells prior to erase. The status of the device during the automatic chip-erase operation can be monitored for completion using the data-polling feature or the toggle-bit feature. See the operation status section for a full description. Figure 6 shows a flow chart of the typical chip-erase operation.

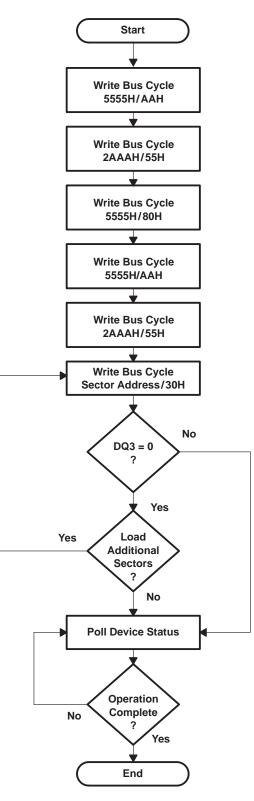

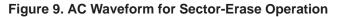

#### sector-erase command

Sector erase is a six-bus-cycle command sequence. The first three bus cycles cause the device to go into the erase-setup state. The next two bus cycles unlock the erase mode, and the sixth bus cycle loads the sector-erase command and the sector-address location to be erased. Any address location within the desired sector can be used. The addresses are latched on the falling edge of  $\overline{W}$  and the sector-erase command (30h) is latched on the rising edge of  $\overline{W}$  in the sixth bus cycle. After a delay of 80 µs from the rising edge of  $\overline{W}$ , the sector-erase operation begins on the selected sector(s).

Additional sectors can be selected to be erased concurrently during the sector-erase command sequence. For each additional sector to be selected for erase, another bus cycle is issued. The bus cycle loads the next sector-address location and the sector-erase command. The time between the end of the previous bus cycle and the start of the next bus cycle must be less than 80  $\mu$ s; otherwise, the new sector location is not loaded. A time delay of 80  $\mu$ s from the rising edge of the last  $\overline{W}$  starts the sector-erase operation. If there is a falling edge of  $\overline{W}$  within the 80- $\mu$ s time delay, the timer is reset.

One to eight sector-address locations can be loaded in any order. The state of the delay timer can be monitored using the sector-erase delay indicator (DQ3). If DQ3 is logic-low, the time delay has not expired. See the operation status section for a description.

Any command other than erase suspend (B0h) or sector erase (30h) written to the device during the sector-erase operation causes the device to exit the sector-erase mode and the contents of the sector(s) selected for erase are no longer valid. To complete the sector-erase operation, the sector-erase command sequence must be repeated.

The embedded sector-erase function automatically provides needed voltage and timing to program and to verify all of the memory cells prior to electrical erase and then erases and verifies the cell margin automatically. Programming the memory cells prior to erase is not required. The status of the device during the automatic sector-erase operation can be monitored for completion by using the data-polling feature or the toggle-bit feature. See the operation status section for a full description. Figure 8 shows a flow chart of the typical sector-erase operation.

#### erase-suspend command

The erase-suspend command (B0h) allows interruption of a sector-erase operation to read data from unaltered sectors of the device. Erase-suspend is a one-bus-cycle command. The addresses can be  $V_{IL}$  or  $V_{IH}$  and the erase-suspend command (B0h) is latched on the rising edge of  $\overline{W}$ . Once the sector-erase operation is in progress, the erase-suspend command requests the internal write-state machine to halt operation at predetermined breakpoints. The erase-suspend command is valid only during the sector-erase operation and is invalid during the byte-programming and chip-erase operations. The sector-erase delay timer expires immediately if the erase-suspend command is issued while the delay is active.

After the erase-suspend command is issued, the device typically takes between 0.1  $\mu$ s and 15  $\mu$ s to suspend the operation. The toggle bit must be monitored to determine when the suspend has been executed. When the toggle bit stops toggling, data can be read from sectors that are not selected for erase. Reading from a sector selected for erase can result in invalid data. See the operation status section for a full description.

Once the sector-erase operation is suspended, further writes of the erase-suspend command are ignored. The erase-resume command (30h) causes the device to restart the suspended sector operation. To erase additional sectors, reissue the six-cycle sector-erase command sequence. Any other command sequence written while in suspend mode causes the device to reset to the read mode.

#### erase-resume command

The erase-resume command (30h) restarts a suspended sector-erase operation from where it was halted to completion. Erase resume is a one-bus-cycle command. The addresses can be  $V_{IL}$  or  $V_{IH}$  and the erase-resume command (30h) is latched on the rising edge of  $\overline{W}$ . When an erase-suspend/erase-resume command combination is written, the internal pulse counter is reset to zero and the exceed-timing-limit indicator (DQ5) is set to logic-low. The erase-resume command is valid only in the erase-suspend state. After the erase-resume command is executed, the device returns to the valid sector-erase state and further writes of the erase-resume command are ignored. After the device has resumed the sector-erase operation, another erase-suspend command can be issued to the device.

#### operation status

#### status-bit definitions

During operation of the embedded program and erase functions, the status of the device can be determined by reading the data state of designated outputs. The data-polling bit (DQ7) and toggle bit (DQ6) require multiple successive reads to observe a change in the state of the designated output. Table 4 defines the values of the status flags.

| Device Operation <sup>‡</sup>        | DQ7 | DQ6 | DQ5 | DQ4 | DQ3 | DQ2 | DQ1 | DQ0 |

|--------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Byte-programming in progress         | DQ7 | Т   | 0   | Х   | 0   | Х   | Х   | Х   |

| Byte-programming exceed time limit   | DQ7 | Т   | 1   | Х   | 0   | Х   | Х   | Х   |

| Byte-programming complete            | D   | D   | D   | D   | D   | D   | D   | D   |

| Sector-/chip-erase in progress       | 0   | Т   | 0   | Х   | 1   | Х   | Х   | Х   |

| Sector-/chip-erase exceed time limit | 0   | Т   | 1   | Х   | 1   | Х   | Х   | Х   |

| Sector-/chip-erase complete          | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

## Table 4. Operation Status Flags<sup>†</sup>

<sup>†</sup> T= toggle, D = data, X = data undefined,  $\overline{DQ7}$  = complement of data written to DQ7 <sup>‡</sup> DQ4, DQ2, DQ1, and DQ0 are received for future use

$\ddagger$  DQ4, DQ2, DQ1, and DQ0 are reserved for future use.

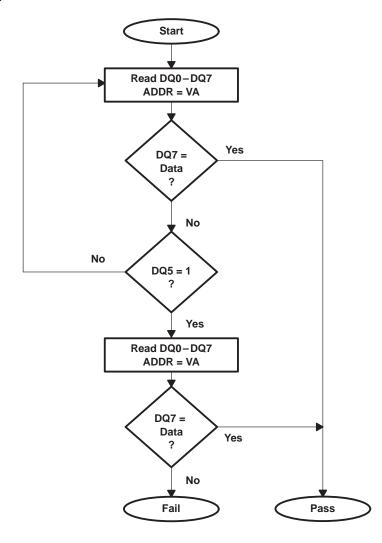

## data-polling (DQ7)

The data-polling status function outputs the complement of the data latched into the DQ7 data register while the write-state machine is engaged in a program or erase operation. Data bit DQ7 changing from complement to true indicates the end of an operation. Data-polling is available only during the byte-programming, chip-erase, sector-erase, and sector-erase timing delay. Data-polling is valid after the rising edge of W in the last bus cycle of the command sequence loaded into the command register. Figure 10 shows a flow chart of the data-polling operation.

During a byte-program operation, reading DQ7 outputs the complement of the DQ7 data to be programmed at the selected address location. Upon completion, reading DQ7 outputs the true DQ7 data loaded into the program data register. During the erase operations, reading DQ7 outputs a 0. Upon completion of erase operations, reading DQ7 outputs a 1. Also, data-polling must be performed at a sector address that is within a sector being erased; otherwise, the status is invalid. When using data-polling, the address must remain stable throughout the operation.

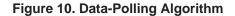

During a data-polling read, while  $\overline{G}$  is low, data bit DQ7 can change asynchronously with the other DQs. Depending on the read timing, the system can read valid data on DQ7, while other DQ pins are still invalid. The data on DQ0–DQ7 is valid with a subsequent read of the device. Figure 11 shows the data-polling timing diagram.

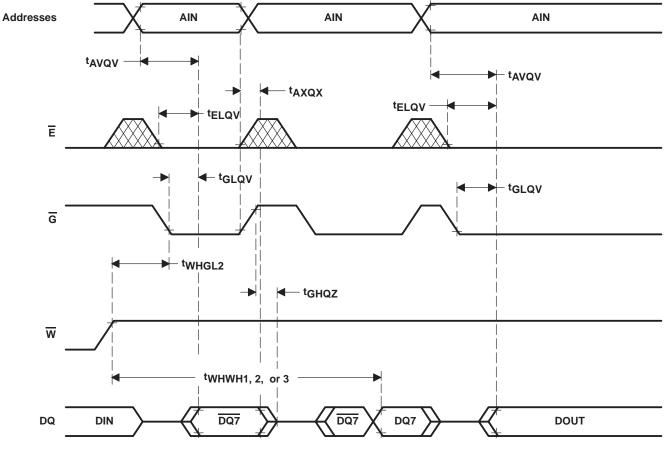

## toggle bit (DQ6)

The toggle-bit status function outputs data on DQ6 that toggles between logic 1 and logic 0 while the write-state machine is engaged in a program or erase operation. When toggle bit DQ6 stops toggling after two consecutive reads to the same address, the operation is complete. The toggle bit is only available during the byte-programming, chip-erase, sector-erase, and sector-erase timing delay. Toggle-bit data is valid after the rising edge of  $\overline{W}$  in the last bus cycle of the command sequence loaded into the command register. Figure 12 shows a flow chart of the toggle-bit status-read algorithm. Depending on the read timing, DQ6 can stop toggling while other DQ pins are still invalid. The data on DQ0–DQ7 is valid with a subsequent read of the device. Figure 13 shows the toggle-bit timing diagram.

## exceed-time-limit (DQ5)

The program and erase operations use an internal pulse counter to limit the number of pulses applied. If the pulse count limit is exceeded, DQ5 is set to a logic 1, indicating that the program or erase operation has failed. DQ7 does not change from complemented data to true data and DQ6 does not stop toggling when read. The device must be reset to continue operation.

This condition occurs when attempting to program a logic 1 into a bit that has been programmed previously to a logic 0. Only an erase operation can change bits from 0 to 1. After reset, the device is functional and can be erased and reprogrammed.

## sector-load-timer bit (DQ3)

The sector-load-timer status bit, DQ3, is used to determine whether the time to load additional sector addresses has expired. After completion of a sector-erase command sequence, DQ3 remains at a logic 0 for 80  $\mu$ s. This indicates that another sector-erase command sequence can be issued. If DQ3 is at a logic 1, it indicates that the delay has expired and attempts to issue additional sector-erase commands are ignored. See the sector-erase command section for a description.

The data-polling bit and toggle bit are valid during the 80-µs time delay and can be used to determine if a valid sector-erase command has been issued. To ensure additional sector-erase commands have been accepted, the status of DQ3 should be read before and after each additional sector-erase command. If DQ3 is at a logic low on both reads, then the additional sector-erase command was accepted.

## data protection

## hardware-sector protection feature

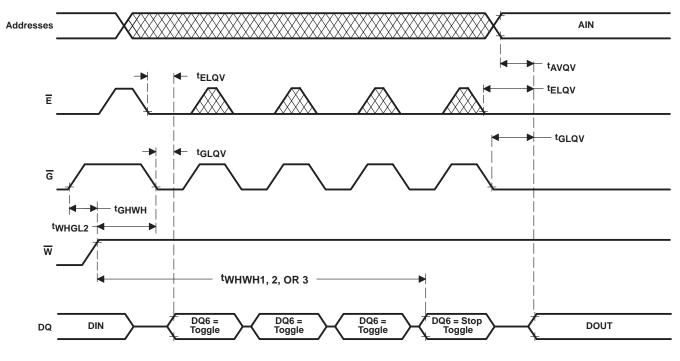

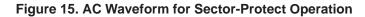

This feature disables both programming and erase operations on any combination of one to eight sectors. Commands to program or erase a protected sector do not change the data contained in the sector. The data-polling and toggle bits operate for  $2\,\mu$ s to  $100\,\mu$ s and then return to valid data. This feature is enabled using high-voltage V<sub>ID</sub> (11.5 V to 12.5 V) on address pin A9 and control pin  $\overline{G}$ , and V<sub>IL</sub> on control pin  $\overline{E}$ . Figure 14 shows a flow chart of the sector-protect operation.

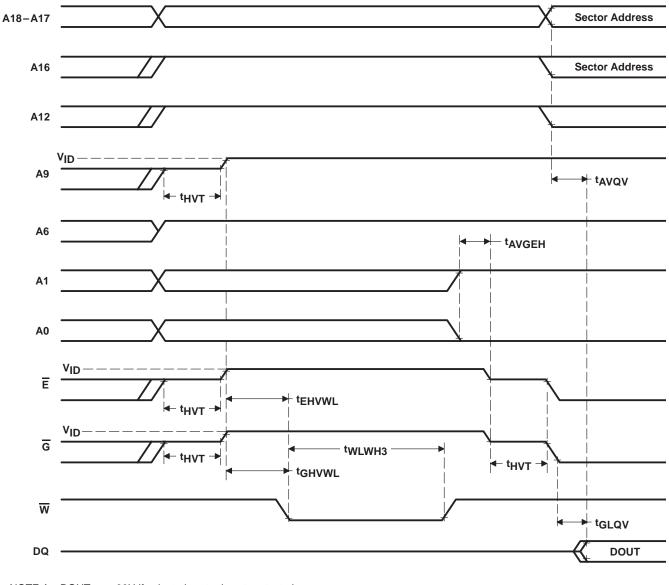

The device is delivered with all sectors unprotected. The sector-unprotect mode is available to unprotect protected sectors. Figure 16 is a flow chart of the sector-unprotect operation.

## sector-protect operation

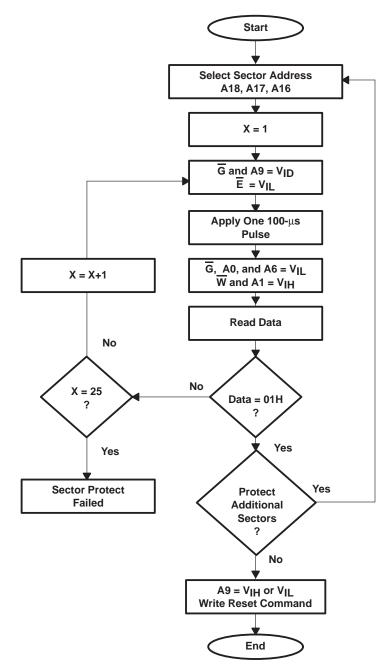

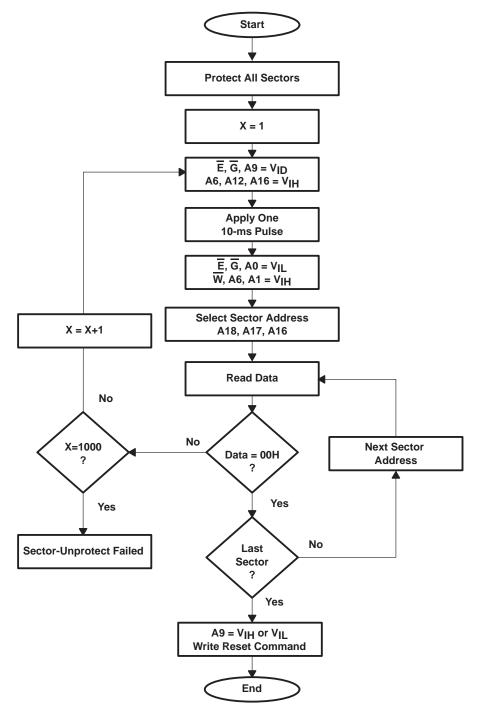

The sector-protect mode is activated when  $V_{CC} = 3.3 \text{ V}$  (operating at  $T_A = 25^{\circ}\text{C}$ ),  $\overline{W} = V_{IH}$ ,  $\overline{E} = V_{IL}$ , and address pin A9 and control pin  $\overline{G}$  are forced to  $V_{ID}$ . The sector-select address pins A16, A17, and A18 are used to select the sector to be protected. Address pins A0–A8, A10–A15, and I/O pins DQ0–DQ7 must be stable and can be  $V_{IL}$  or  $V_{IH}$ . Once the addresses are stable,  $\overline{W}$  is pulsed low for 100 µs. The operation begins on the falling edge of  $\overline{W}$  and terminates on the rising edge of  $\overline{W}$ . Figure 15 shows a timing diagram of the sector-protect operation.

## sector-protect verify

Verification of sector-protection is activated when  $V_{CC} = 3.3 \text{ V}$  (operating at  $T_A = 25^{\circ}\text{C}$ ),  $\overline{W} = V_{IH}$ ,  $\overline{G} = V_{IL}$ ,  $\overline{E} = V_{IL}$ , and address pin A9 =  $V_{ID}$ . Address pins A0 and A6 are set to  $V_{IL}$ , and A1 is set to  $V_{IH}$ . The sector-address pins A16, A17, and A18 select the sector to be verified. The other address pins can be  $V_{IH}$  or  $V_{IL}$ . If the sector selected is protected, the DQs output 01h. If the sector selected is not protected, the DQs output 00h.

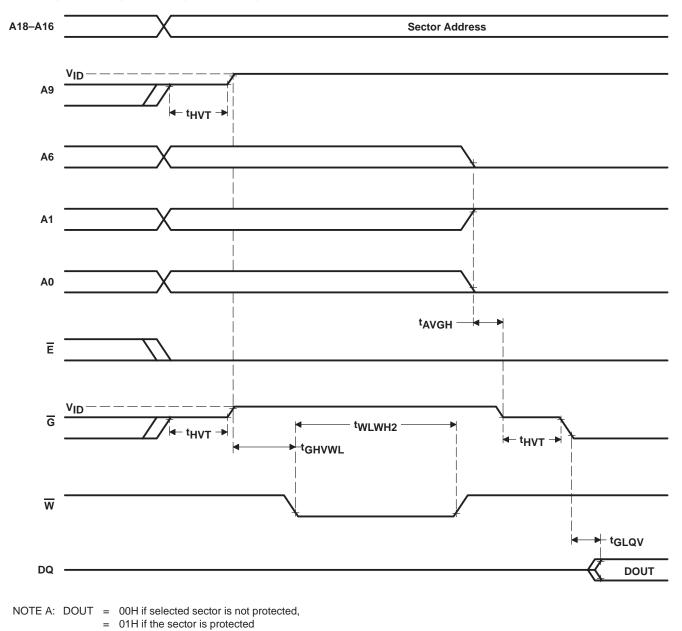

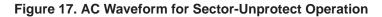

## sector-unprotect operation

Prior to a sector-unprotect operation, all sectors should be protected using the sector-protect mode. Sector-unprotect mode is activated when  $V_{CC} = 3.3 \text{ V}$  (operating at  $T_A = 25^{\circ}\text{C}$ ),  $\overline{W} = V_{IH}$ , and address pin A9 and control pins  $\overline{G}$  and  $\overline{E}$  are forced to  $V_{ID}$ . Address pins A6, A12, and A16 are set to  $V_{IH}$ . The sector-select address pins A17 and A18 can be  $V_{IL}$  or  $V_{IH}$ . All eight sectors are unprotected in parallel. Once the inputs are stable,  $\overline{W}$  is pulsed low for 10 ms. The unprotect operation begins on the falling edge of  $\overline{W}$  and terminates on the rising edge of  $\overline{W}$ . Figure 17 shows a timing diagram of the sector-unprotect operation.

## sector-unprotect verify

Verification of the sector-unprotection is activated when  $V_{CC} = 3.3 \text{ V}$  (operating at  $T_A = 25^{\circ}\text{C}$ ),  $\overline{W} = V_{IH}$ ,  $\overline{G} = V_{IL}$ ,  $\overline{E} = V_{IL}$ , and address pin A9 =  $V_{ID}$ . The sector to be verified must be selected. Address pins A1 and A6 are set to  $V_{IH}$ , and A0 is set to  $V_{IL}$ . The other address pins can be  $V_{IH}$  or  $V_{IL}$ . If the sector that is selected is protected, the DQs output 01h. If the sector selected is not protected, the DQs output 00h.

## glitching

Pulses of less than 5 ns (typical) on  $\overline{G}$ ,  $\overline{W}$ , or  $\overline{E}$  do not issue a write cycle.

## power supply considerations

Each device should have a 0.1- $\mu$ F ceramic capacitor connected between V<sub>CC</sub> and V<sub>SS</sub> to suppress circuit noise. Printed-circuit traces to V<sub>CC</sub> should be appropriate to handle the current demand and minimize inductance.

## absolute maximum ratings over operating ambient temperature range (unless otherwise noted)<sup>†</sup>

| Voltage range with respect to ground:                               |              |

|---------------------------------------------------------------------|--------------|

| Supply voltage range, V <sub>CC</sub> (see Note 2)                  | to + 3.6 V   |

| All pins except A9, $\overline{E}$ , $\overline{G}$ (see Note 2)    | ′ to + 3.6 V |

| A9, E, G (see Note 3)                                               | to + 13.5 V  |

| Ambient temperature range during read/erase/program, T <sub>A</sub> |              |

| Commercial (L)                                                      | °C to 70°C   |

| Extended (E)                                                        | °C to 85°C   |

| Storage temperature range, T <sub>stg</sub> 65°                     | C to 150°C   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 2. Minimum dc voltage on input or I/O pins is –0.5 V. During voltage transitions, input or I/O pins may undershoot V<sub>SS</sub> to –2.0 V for periods of up to 20 ns. Maximum dc voltage on input and I/O pins is +3.6 V. During voltage transitions, input and I/O pins may overshoot to V<sub>CC</sub> + 2.0 V for periods up to 20 ns.

- 3. Minimum dc input voltage on A9, E, and G pins is –0.5 V. During voltage transitions, A9, E, and G may undershoot V<sub>SS</sub> to –2.0 V for periods of up to 20 ns. Maximum dc input voltage on A9, E, and G pins is +12.5 V, which may overshoot to +13.5 V for periods up to 20 ns.

## recommended operating conditions

|     |                                                 |                                | MIN | NOM | MAX | UNIT |  |

|-----|-------------------------------------------------|--------------------------------|-----|-----|-----|------|--|

| Vaa | Supply voltage                                  | '29LF040 V <sub>CC</sub> range | 3   | 3.3 | 3.6 | V    |  |

| Vcc | Supply voltage                                  | '29VF040 V <sub>CC</sub> range | 2.7 | 3   | 3.6 | v    |  |

| Τ.  | Ambient temperature during read/cross/program   | Commercial (L)                 | 0   |     | 70  | °C   |  |

| TA  | A Ambient temperature during read/erase/program | Extended (E)                   | -40 |     | 85  |      |  |

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

|                 | PARAMETER                                       |                     | TEST CO                               | NDITIONS                                           | MIN                   | MAX                   | UNIT |

|-----------------|-------------------------------------------------|---------------------|---------------------------------------|----------------------------------------------------|-----------------------|-----------------------|------|

| VIH             | High-level dc input voltage                     | CMOS                |                                       |                                                    | 0.7 * V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | V    |

| VIL             | Low-level dc input voltage                      | CMOS                |                                       |                                                    | - 0.5                 | 0.8                   | V    |

| V <sub>ID</sub> | Algorithm-selection and sector<br>input voltage | r-protect/unprotect | V <sub>CC</sub> = 3.3 V               |                                                    | 11.5                  | 12.5                  | V    |

|                 | Lligh lovel de output veltege                   | CMOS                | $V_{CC} = V_{CC} MIN^{\dagger}$       | I <sub>OH</sub> = – 2.0 mA                         | 0.85 * VCC            |                       | V    |

| Vон             | High-level dc output voltage                    | CMOS                | $V_{CC} = V_{CC} MIN$                 | I <sub>OH</sub> = – 100 μA                         | V <sub>CC</sub> - 0.4 |                       | V    |

| V <sub>OL</sub> | Low-level dc output voltage (see Note 4)        | CMOS                | $V_{CC} = V_{CC} MIN$                 | I <sub>OL</sub> = 4.0 mA                           |                       | 0.45                  | V    |

| l               | Input current (leakage)                         | -                   | $V_{CC} = V_{CC} MAX$                 | $V_I = V_{SS}$ to $V_{CC}$                         |                       | ±1                    | μA   |

| lo              | Output current (leakage)                        |                     | $V_{CC} = V_{CC} MAX$                 | V <sub>O</sub> =V <sub>SS</sub> to V <sub>CC</sub> |                       | ±1                    | μA   |

| IID             | High-voltage load current                       |                     | $V_{CC} = V_{CC} MAX$                 | A9 = 12.5 V                                        |                       | 50                    | μΑ   |

| ICC1            | V <sub>CC</sub> active current (see Note        | 5)                  | $\overline{E} = V_{IL}$ ,             | G = V <sub>IH</sub>                                |                       | 40                    | mA   |

| ICC2            | V <sub>CC</sub> active current (see Note        | es 6)               | $\overline{E} = V_{ L},$              | G = V <sub>IH</sub>                                |                       | 60                    | mA   |

| ICC3            | V <sub>CC</sub> supply current<br>(standby)     | CMOS-input level    | V <sub>CC</sub> = V <sub>CC</sub> MAX | $\overline{E} = V_{CC} \pm 0.3 V$                  |                       | 100                   | μΑ   |

## electrical dc characteristics over recommended ranges of supply voltage and ambient temperature

<sup>†</sup> See the recommended operating conditions table.

NOTES: 4. 5.8-mA IOL also available

5. ICC current in the read mode, switching at 6 MHz, IOUT = 0 mA

6. ICC current while erase or program operation is in progress

## capacitance over recommended ranges of supply voltage and ambient temperature

|                 | PARAMETER                                                                  | TEST CONDITIONS                 | MIN MAX | UNIT |

|-----------------|----------------------------------------------------------------------------|---------------------------------|---------|------|

| C <sub>i1</sub> | Input capacitance (All inputs except A9, $\overline{E}$ , $\overline{G}$ ) | $V_I = 0 V$ , $f = 1 MHz$       | 7.5     | pF   |

| C <sub>i2</sub> | Input capacitance (A9, E, G)                                               | $V_I = 0 V$ , $f = 1 MHz$       | 9       | pF   |

| Co              | Output capacitance                                                         | V <sub>O</sub> = 0 V, f = 1 MHz | 12      | pF   |

switching characteristics over recommended ranges of supply voltage and ambient temperature, read-only operation<sup>†</sup> (see Figure 2, Figure 11, Figure 13, Figure 15, and Figure 17)

| PARAMETER         |                                                                         | ALTERNATE<br>SYMBOL | '29LF040-80 |     | '29LF040-90 |     | 29LF040-10<br>29VF040-10 |     | UNIT |

|-------------------|-------------------------------------------------------------------------|---------------------|-------------|-----|-------------|-----|--------------------------|-----|------|

|                   |                                                                         | STMBOL              | MIN         | MAX | MIN         | MAX | MIN                      | MAX |      |

| <sup>t</sup> AVQV | Access time, address                                                    | <sup>t</sup> a(A)   |             | 80  |             | 90  |                          | 100 | ns   |

| <sup>t</sup> ELQV | Access time, E                                                          | <sup>t</sup> a(E)   |             | 80  |             | 90  |                          | 100 | ns   |

| <sup>t</sup> GLQV | Access time, G                                                          | <sup>t</sup> a(G)   |             | 35  |             | 40  |                          | 45  | ns   |

| t <sub>AVAV</sub> | Cycle time, read                                                        | <sup>t</sup> c(R)   | 80          |     | 90          |     | 100                      |     | ns   |

| <sup>t</sup> EHQZ | Disable time, $\overline{E}$ to high impedance                          | <sup>t</sup> dis(E) |             | 20  |             | 20  |                          | 30  | ns   |

| <sup>t</sup> GHQZ | Disable time, $\overline{G}$ to high impedance                          | <sup>t</sup> dis(G) |             | 20  |             | 20  |                          | 30  | ns   |

| <sup>t</sup> AXQX | Hold time, output from address, $\overline{E}$ or $\overline{G}$ change | <sup>t</sup> h(D)   | 0           |     | 0           |     | 0                        |     | ns   |

| tWHGL1            | Hold time, G read                                                       |                     | 0           |     | 0           |     | 0                        |     | ns   |

| tWHGL2            | Hold time, $\overline{G}$ toggle and data polling                       |                     | 10          |     | 10          |     | 10                       |     | ns   |

|                   | PARAMETER                                                               |                     | 29LF040-12<br>29VF040-12 |     | 29LF040-15<br>29VF040-15 |     | UNIT |

|-------------------|-------------------------------------------------------------------------|---------------------|--------------------------|-----|--------------------------|-----|------|

|                   |                                                                         | STMBOL              | MIN                      | MAX | MIN                      | MAX |      |

| t <sub>AVQV</sub> | Access time, address                                                    | <sup>t</sup> a(A)   |                          | 120 |                          | 150 | ns   |

| <sup>t</sup> ELQV | Access time, E                                                          | <sup>t</sup> a(E)   |                          | 120 |                          | 150 | ns   |

| tGLQV             | Access time, G                                                          | <sup>t</sup> a(G)   |                          | 50  |                          | 55  | ns   |

| t <sub>AVAV</sub> | Cycle time, read                                                        | <sup>t</sup> c(R)   | 120                      |     | 150                      |     | ns   |

| <sup>t</sup> EHQZ | Disable time, $\overline{E}$ to high impedance                          | <sup>t</sup> dis(E) |                          | 30  |                          | 35  | ns   |

| <sup>t</sup> GHQZ | Disable time, $\overline{G}$ to high impedance                          | <sup>t</sup> dis(G) |                          | 30  |                          | 35  | ns   |

| t <sub>AXQX</sub> | Hold time, output from address, $\overline{E}$ or $\overline{G}$ change | <sup>t</sup> h(D)   | 0                        |     | 0                        |     | ns   |

| tWHGL1            | Hold time, G read                                                       |                     | 0                        |     | 0                        |     | ns   |

| tWHGL2            | Hold time, $\overline{G}$ toggle and data polling                       |                     | 10                       |     | 10                       |     | ns   |

<sup>†</sup>See Figure 1 for ac test output load circuit and voltage waveforms.

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

# timing requirements controlled by $\overline{W}$ (see Figure 4, Figure 7, Figure 9, Figure 11, Figure 13, Figure 15, and Figure 17)

|                    |                                                                           | ALTERNATE<br>SYMBOL | '29LF040-80 |     |     | '29LF040-90 |     |     | '29LF040-10<br>'29VF040-10 |     |     | UNIT |

|--------------------|---------------------------------------------------------------------------|---------------------|-------------|-----|-----|-------------|-----|-----|----------------------------|-----|-----|------|

|                    |                                                                           |                     | MIN         | TYP | MAX | MIN         | TYP | MAX | MIN                        | ТҮР | MAX |      |

| tavav              | Cycle time, write                                                         | <sup>t</sup> c(W)   | 80          |     |     | 90          |     |     | 100                        |     |     | ns   |

| <sup>t</sup> WHWH1 | Cycle time, programming operation                                         | <sup>t</sup> c(W)PR |             | 20  |     |             | 20  |     |                            | 20  |     | μs   |

| twhwh2             | Cycle time, sector-erase operation                                        |                     |             | 2   | 30  |             | 2   | 30  |                            | 2   | 30  | s    |

| twhwh3             | Cycle time, chip-erase operation                                          |                     |             | 14  | 120 |             | 14  | 120 |                            | 14  | 120 | S    |

| tWLAX              | Hold time, address                                                        | <sup>t</sup> h(A)   | 45          |     |     | 45          |     |     | 45                         |     |     | ns   |

| <sup>t</sup> WHDX  | Hold time, data valid after<br>W high                                     | <sup>t</sup> h(D)   | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> WHEH  | Hold time, E                                                              | <sup>t</sup> h(E)   | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| tWHWL              | Pulse duration, W high                                                    | <sup>t</sup> w(WH)  | 20          |     |     | 20          |     |     | 20                         |     |     | ns   |

| tWLWH1             | Pulse duration, W low                                                     | tw(WL)              | 35          |     |     | 45          |     |     | 45                         |     |     | ns   |

| twlwH2             | Pulse duration, $\overline{W}$ low (see Note 7)                           |                     | 100         |     |     | 100         |     |     | 100                        |     |     | μs   |

| twlwH3             | Pulse duration, $\overline{W}$ low (see Note 8)                           |                     | 10          |     |     | 10          |     |     | 10                         |     |     | ms   |

| <sup>t</sup> GHWL  | Recovery time, read before write                                          | <sup>t</sup> rec(R) | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| tavwl.             | Setup time, address                                                       | t <sub>su(A)</sub>  | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> DVWH  | Setup time, data                                                          | t <sub>su(D)</sub>  | 35          |     |     | 45          |     |     | 45                         |     |     | ns   |

| <sup>t</sup> AVGH  | Setup time, A0 and A6 low and A1 high to $\overline{G}$ high (see Note 7) |                     | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> AVGEH | Setup time, A0 low and<br>A1 high to G and E high<br>(see Note 8)         |                     | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| telwl              | Setup time, E                                                             | <sup>t</sup> su(E)  | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> GHWH  | Setup time, G                                                             |                     | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> VCEL  | Setup time, V <sub>CC</sub>                                               |                     | 50          |     |     | 50          |     |     | 50                         |     |     | μs   |

| <sup>t</sup> EHVWL | Setup time, $\overline{E} V_{ID}$ to $\overline{W}$ (see Note 8)          |                     | 4           |     |     | 4           |     |     | 4                          |     |     | μs   |

| <sup>t</sup> GHVWL | Setup time, $\overline{G} V_{ID}$ to $\overline{W}$ (see Notes 7 and 8)   |                     | 4           |     |     | 4           |     |     | 4                          |     |     | μs   |

| <sup>t</sup> HVT   | Transition time, V <sub>ID</sub> (see Notes 7 and 8)                      |                     | 4           |     |     | 4           |     |     | 4                          |     |     | μs   |

NOTES: 7. Sector-protect timing (see Figure 15)

8. Sector-unprotect timing (see Figure 17)

SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

## timing requirements controlled by $\overline{W}$ (see Figure 4, Figure 7, Figure 9, Figure 11, Figure 13, Figure 15, and Figure 17) (continued)

|                    |                                                                                       | ALTERNATE<br>SYMBOL | '29LF040-12<br>'29VF040-12 |     |     | ²29LF040-15<br>²29VF040-15 |     |     | UNIT |

|--------------------|---------------------------------------------------------------------------------------|---------------------|----------------------------|-----|-----|----------------------------|-----|-----|------|

|                    |                                                                                       | STMBOL              | MIN                        | TYP | MAX | MIN                        | TYP | MAX | 1    |

| t <sub>AVAV</sub>  | Cycle time, write                                                                     | <sup>t</sup> c(W)   | 120                        |     |     | 150                        |     |     | ns   |

| tWHWH1             | Cycle time, programming operation                                                     | <sup>t</sup> c(W)PR |                            | 20  |     |                            | 20  |     | μs   |

| tWHWH2             | Cycle time, sector-erase operation                                                    |                     |                            | 2   | 30  |                            | 2   | 30  | S    |

| twhwh3             | Cycle time, chip-erase operation                                                      |                     |                            | 14  | 120 |                            | 14  | 120 | S    |

| <sup>t</sup> WLAX  | Hold time, address                                                                    | <sup>t</sup> h(A)   | 50                         |     |     | 50                         |     |     | ns   |

| <sup>t</sup> WHDX  | Hold time, data valid after $\overline{W}$ high                                       | <sup>t</sup> h(D)   | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> WHEH  | Hold time, E                                                                          | <sup>t</sup> h(E)   | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> WHWL  | Pulse duration, $\overline{W}$ high                                                   | <sup>t</sup> w(WH)  | 20                         |     |     | 20                         |     |     | ns   |

| tWLWH1             | Pulse duration, $\overline{W}$ low                                                    | <sup>t</sup> w(WL)  | 50                         |     |     | 50                         |     |     | ns   |

| tWLWH2             | Pulse duration, $\overline{W}$ low (see Note 7)                                       |                     | 100                        |     |     | 100                        |     |     | μs   |

| twlwh3             | Pulse duration, $\overline{W}$ low (see Note 8)                                       |                     | 10                         |     |     | 10                         |     |     | ms   |

| <sup>t</sup> GHWL  | Recovery time, read before write                                                      | <sup>t</sup> rec(R) | 0                          |     |     | 0                          |     |     | ns   |

| tavwL              | Setup time, address                                                                   | <sup>t</sup> su(A)  | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> DVWH  | Setup time, data                                                                      | t <sub>su(D)</sub>  | 50                         |     |     | 50                         |     |     | ns   |

| <sup>t</sup> AVGH  | Setup time, A0 and A6 low and A1 high to $\overline{G}$ high (see Note 7)             |                     | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> AVGEH | Setup time, A0 low and A1 high to $\overline{G}$ and $\overline{E}$ high (see Note 8) |                     | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> ELWL  | Setup time, E                                                                         | <sup>t</sup> su(E)  | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> GHWH  | Setup time, G                                                                         |                     | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> VCEL  | Setup time, V <sub>CC</sub>                                                           |                     | 50                         |     |     | 50                         |     |     | μs   |

| <sup>t</sup> EHVWL | Setup time, $\overline{E} V_{ID}$ to $\overline{W}$ (see Note 8)                      |                     | 4                          |     |     | 4                          |     |     | μs   |

| <sup>t</sup> GHVWL | Setup time, $\overline{G}$ V <sub>ID</sub> to $\overline{W}$ (see Notes 7 and 8)      |                     | 4                          |     |     | 4                          |     |     | μs   |

| <sup>t</sup> HVT   | Transition time, VID (see Notes 7 and 8)                                              |                     | 4                          |     |     | 4                          |     |     | μs   |

NOTES: 7. Sector-protect timing (see Figure 15)

8. Sector-unprotect timing (see Figure 17)

## TMS29LF040, TMS29VF040 524288 BY 8-BIT FLASH MEMORIES SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

## timing requirements controlled by $\overline{E}$ (see Figure 5)

|                    |                                                 | ALTERNATE<br>SYMBOL | '29LF040-80 |     |     | '29LF040-90 |     |     | '29LF040-10<br>'29VF040-10 |     |     | UNIT |

|--------------------|-------------------------------------------------|---------------------|-------------|-----|-----|-------------|-----|-----|----------------------------|-----|-----|------|

|                    |                                                 | STMBOL              | MIN         | TYP | MAX | MIN         | TYP | MAX | MIN                        | TYP | MAX |      |

| t <sub>AVAV</sub>  | Cycle time, write                               | <sup>t</sup> c(W)   | 80          |     |     | 90          |     |     | 100                        |     |     | ns   |

| <sup>t</sup> EHEH1 | Cycle time, programming operation               |                     |             | 20  |     |             | 20  |     |                            | 20  |     | μs   |

| <sup>t</sup> EHEH2 | Cycle time, sector-erase operation (see Note 9) |                     |             | 2   | 30  |             | 2   | 30  |                            | 2   | 30  | s    |

| <sup>t</sup> EHEH3 | Cycle time, chip-erase operation (see Note 10)  |                     |             | 14  | 120 |             | 14  | 120 |                            | 14  | 120 | s    |

| <sup>t</sup> ELAX  | Hold time, address                              | <sup>t</sup> h(A)   | 45          |     |     | 45          |     |     | 45                         |     |     | ns   |

| <sup>t</sup> EHDX  | Hold time, data                                 | <sup>t</sup> h(D)   | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> EHWH  | Hold time, W                                    | <sup>t</sup> h(W)   | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> ELEH  | Pulse duration, E low                           | <sup>t</sup> w(EL)  | 35          |     |     | 45          |     |     | 45                         |     |     | ns   |

| <sup>t</sup> EHEL  | Pulse duration, E high                          | <sup>t</sup> w(EH)  | 20          |     |     | 20          |     |     | 20                         |     |     | ns   |

| <sup>t</sup> GHEL  | Recovery time, read before write                | <sup>t</sup> rec(R) | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> AVEL  | Setup time, address                             | <sup>t</sup> su(A)  | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

| <sup>t</sup> DVEH  | Setup time, data                                | t <sub>su(D)</sub>  | 35          |     |     | 45          |     |     | 45                         |     |     | ns   |

| tWLEL              | Setup time, W                                   | t <sub>su(W)</sub>  | 0           |     |     | 0           |     |     | 0                          |     |     | ns   |

|                   |                                                 | ALTERNATE<br>SYMBOL | '29LF040-12<br>'29VF040-12 |     |     | ²29LF040-15<br>²29VF040-15 |     |     | UNIT |

|-------------------|-------------------------------------------------|---------------------|----------------------------|-----|-----|----------------------------|-----|-----|------|

|                   |                                                 | STMBOL              | MIN                        | TYP | MAX | MIN                        | TYP | MAX |      |

| tAVAV             | Cycle time, write                               | t <sub>c(W)</sub>   | 120                        |     |     | 150                        |     |     | ns   |

| tEHEH1            | Cycle time, programming operation               |                     |                            | 20  |     |                            | 20  |     | μs   |

| tEHEH2            | Cycle time, sector-erase operation (see Note 9) |                     |                            | 2   | 30  |                            | 2   | 30  | S    |

| tEHEH3            | Cycle time, chip-erase operation (see Note 10)  |                     |                            | 14  | 120 |                            | 14  | 120 | S    |

| <sup>t</sup> ELAX | Hold time, address                              | <sup>t</sup> h(A)   | 50                         |     |     | 50                         |     |     | ns   |

| <sup>t</sup> EHDX | Hold time, data                                 | <sup>t</sup> h(D)   | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> EHWH | Hold time, $\overline{W}$                       | <sup>t</sup> h(W)   | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> ELEH | Pulse duration, E low                           | <sup>t</sup> w(EL)  | 50                         |     |     | 50                         |     |     | ns   |

| <sup>t</sup> EHEL | Pulse duration, E high                          | <sup>t</sup> w(EH)  | 20                         |     |     | 20                         |     |     | ns   |

| <sup>t</sup> GHEL | Recovery time, read before write                | t <sub>rec(R)</sub> | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> AVEL | Setup time, address                             | t <sub>su(A)</sub>  | 0                          |     |     | 0                          |     |     | ns   |

| <sup>t</sup> DVEH | Setup time, data                                | <sup>t</sup> su(D)  | 50                         |     |     | 50                         |     |     | ns   |

| <sup>t</sup> WLEL | Setup time, $\overline{W}$                      | <sup>t</sup> su(W)  | 0                          |     |     | 0                          |     |     | ns   |

NOTES: 9. Timing diagram of E-controlled sector-erase operation not enclosed. 10. Timing diagram of E-controlled chip-erase operation not enclosed.

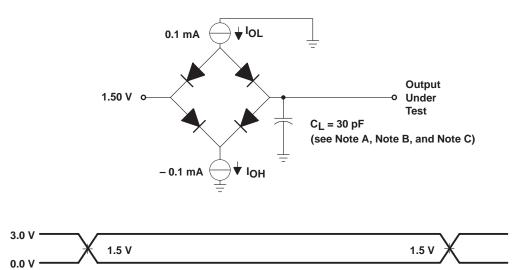

## PARAMETER MEASUREMENT INFORMATION

- NOTES: A. CL includes probe and fixture capacitance.

- B. The ac testing inputs are driven at 3 V for logic high and 0 V for logic low. Timing measurements are made at 1.5 V for logic high and 1.5 V for logic low on both inputs and outputs. Each device should have a 0.1-μF ceramic capacitor connected between V<sub>CC</sub> and V<sub>SS</sub> as closely as possible to the device pins.

- C. Input rise and fall  $\leq$  5 ns.

## Figure 1. AC Test Output Load Circuit and Voltage Waveforms

read operation

Figure 2. AC Waveform for Read Operation

SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

## write operation

Figure 3. Byte-Program Algorithm

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

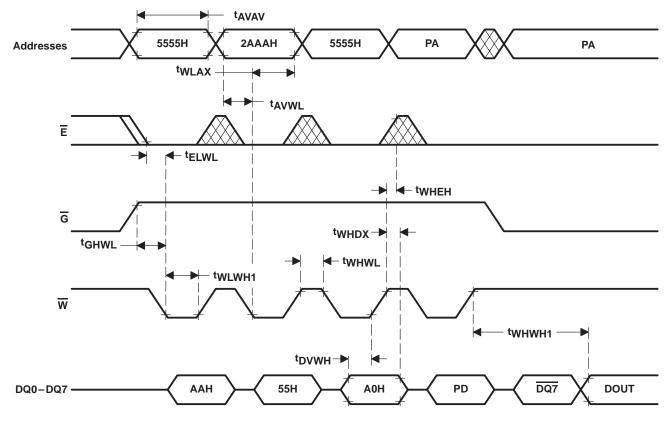

## write operation (continued)

NOTES: A. PA = Address of the location to be programmed

B. PD = Data to be programmed

C.  $\overline{DQ7}$  = Complement of data written to DQ7

## Figure 4. AC Waveform for Byte-Program (W-Controlled) Operation

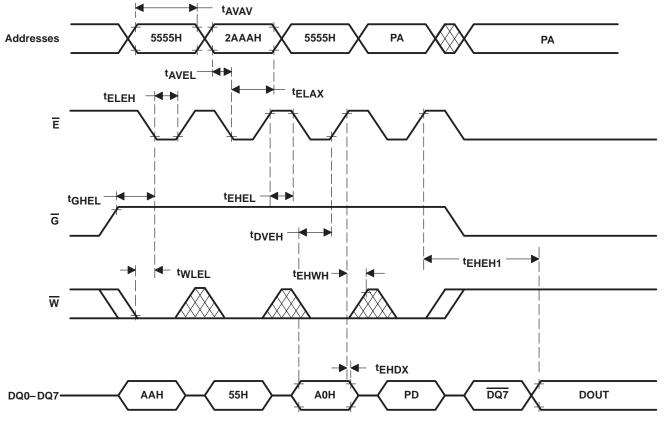

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

## write operation (continued)

NOTES: A. PA = Address of the location to be programmed

B. <u>PD</u> = Data to be programmed

C. DQ7 = Complement of data written to DQ7

Figure 5. AC Waveform for Byte-Program (Alternate  $\overline{E}$ -Controlled) Operation

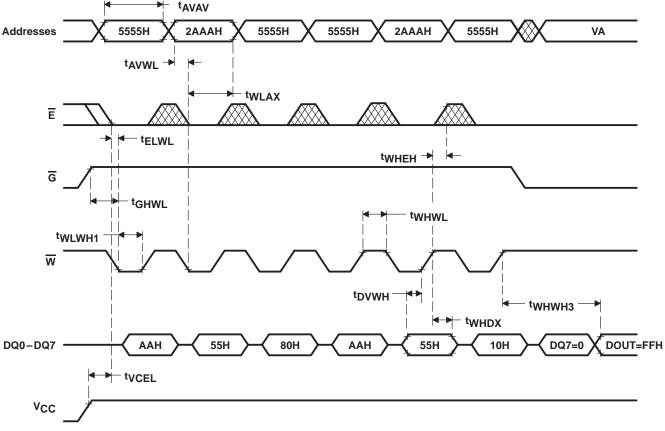

## chip-erase operation

Figure 6. Chip-Erase Algorithm

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

## chip-erase operation (continued)

NOTE A: VA = any valid address

## sector-erase operation

Figure 8. Sector-Erase Algorithm

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

## sector-erase operation (continued)

NOTE A: SA = Sector address to be erased

## data-polling operation

- NOTES: A. DQ7 is checked again after DQ5 is checked, even if DQ5 = 1.

- B. VA = Program address for byte-programming

- = Selected sector address for sector erase

- = Any valid address for chip erase

SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

## data-polling operation (continued)

NOTES: A. DIN

= Last command data written to the device B. DQ7 = Complement of data written to DQ7

C. DOUT = Valid data output

D. AIN = Valid address for byte-program, sector-erase, or chip-erase operation E. The data-polling operation is valid for both  $\overline{W}$ - and  $\overline{E}$ -controlled byte-program, sector-erase, and chip-erase operations.

Figure 11. AC Waveform for Data-Polling Operation

## toggle-bit operation

Figure 12. Toggle-Bit Algorithm

## TMS29LF040, TMS29VF040 524288 BY 8-BIT FLASH MEMORIES SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

## toggle-bit operation (continued)

NOTES: A. DIN = Last command data written to the device

- B. DQ6 = Toggle bit output

- C. DOUT = Valid data output

D. AIN = Valid address for byte-program, sector-erase, or chip-erase operation

E. The toggle-bit operation is valid for both W- and E-controlled byte-program, sector-erase, and chip-erase operations.

Figure 13. AC Waveform for Toggle-Bit Operation

## sector-protect operation

Figure 14. Sector-Protect Algorithm

SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

## sector-protect operation (continued)

## sector-unprotect operation

Figure 16. Sector-Unprotect Algorithm

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

## sector-unprotect operation (continued)

NOTE A: DOUT = 00H if selected sector is not protected, = 01H if the sector is protected

SMJS825D - SEPTEMBER 1995 - REVISED JUNE 1998

MECHANICAL DATA

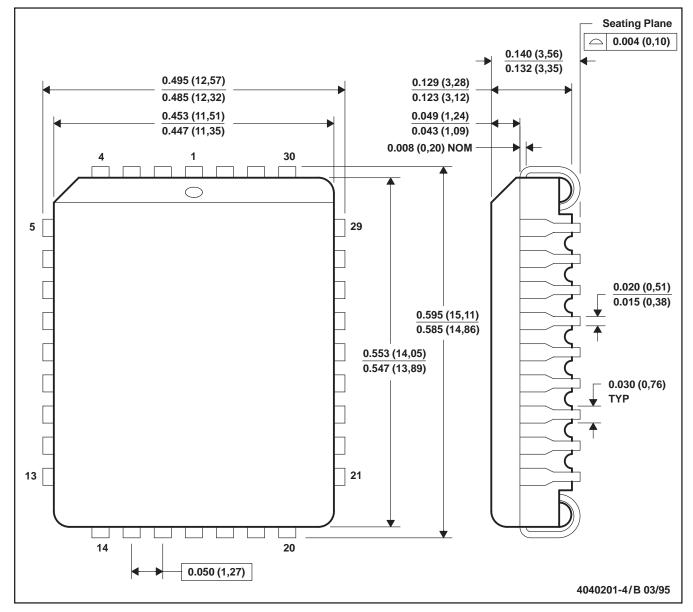

## PLASTIC J-LEADED CHIP CARRIER

FM (R-PQCC-J32)

NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-016

SMJS825D – SEPTEMBER 1995 – REVISED JUNE 1998

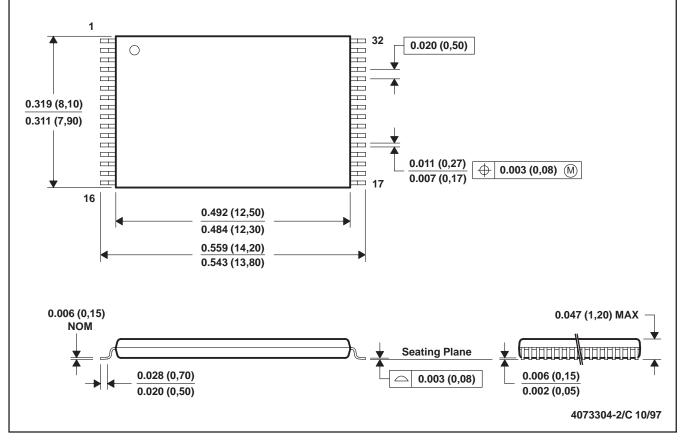

**MECHANICAL DATA**

DBW (R-PDSO-G32)

#### PLASTIC THIN SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

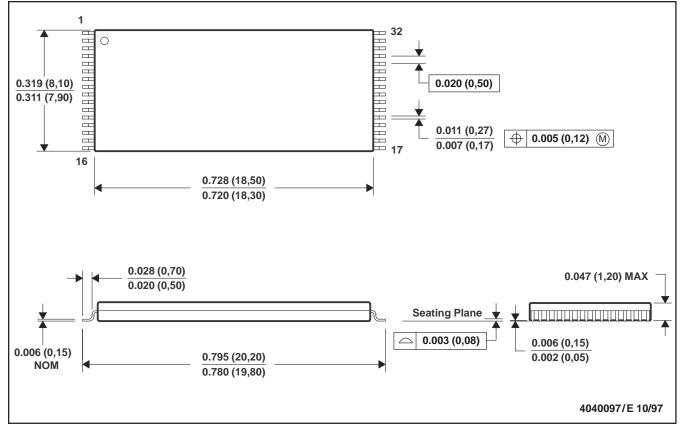

MECHANICAL DATA

DD (R-PDSO-G32)

#### PLASTIC THIN SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated