# TOSHIBA

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

#### \*\*CAUTION\*\*

How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts = (NMI, INTO), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of X1) with IDLE or STOP mode. (In this case, an interrupt request is kept on hold internally.) If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb-free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

- 1. Part number

- Example: TMPxxxxxF  $\rightarrow$  TMPxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C → LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page,

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

| Previous Part Number (in Body Text) | New Part Number |

|-------------------------------------|-----------------|

| TMP96C041BF                         | TMP96C041BFG    |

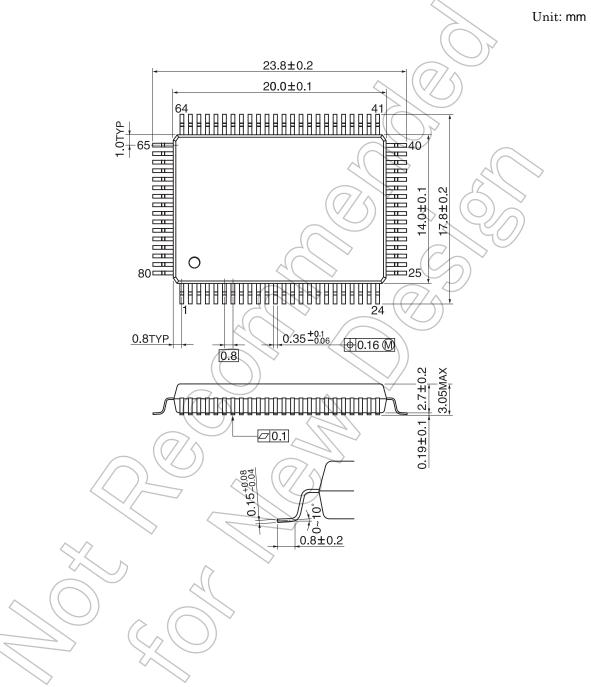

#### 2. Package code and dimensions

| Previous Package Code (in Body Text) | New Package Code   |

|--------------------------------------|--------------------|

| QFP80-P-1420-0.80B                   | QFP80-P-1420-0.80M |

\*: For the dimensions of the new package, see the attached Package Dimensions diagram.

#### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

Solderability of lead free products

| Test Parameter | Test Condition                                                                                                                                                                                                                                                                                                    | Note                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Solderability  | Use of Sn-37Pb solder Bath<br>Solder bath temperature = 230°C, Dipping time = 5 seconds<br>The number of times = one, Use of R-type flux<br>Use of Sn-3.0Ag-0.5Cu solder bath<br>Solder bath temperature = 245°C, Dipping time = 5 seconds<br>The number of times = one, Use of R-type flux<br>(use of lead free) | Pass:<br>Solderability rate until forming<br>≥ 95% |

### 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### RESTRICTIONS ON PRODUCT USE

• The information contained herein is subject to change without notice.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or tailure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

#### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

20070701-EN

(Annex)

Package Dimensions

QFP80-P-1420-0.80M

# CMOS 16-bit Microcontrollers

# TMP96C041BF

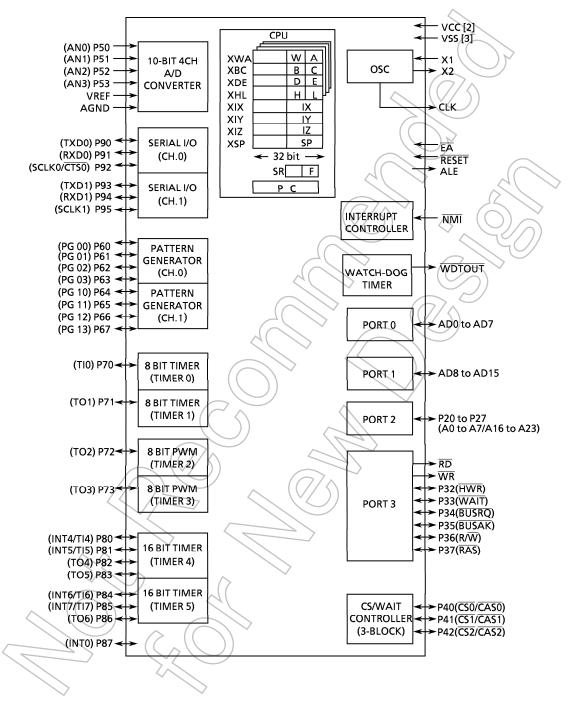

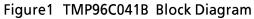

# 1. Outline and Device Characteristics

TMP96C041BF is high-speed advanced 16-bit microcontrollers developed for controlling medium to large-scale equipment. The TMP96C041B has RAMless for TMP96C141BF. Otherwise, the devices function in the same way.

TMP96C041BF is housed in an 80-pin flat package.

Device characteristics are as follows:

- (1) Original 16-bit CPU

- TLCS-90 instruction mnemonic upward compatible.

- 16M-byte linear address space

- General-purpose registers and register bank system

- 16-bit multiplication / division and bit transfer/arithmetic instructions

- High-speed micro DMA : 4 channels (1.6 µs/2 bytes @ 20 MHz)

- Minimum instruction execution time : 200 ns @ 20 MHz

- (2) Minimum instruction executio

(3) Internal RAM : None

- Internal ROM : None

- (4) External memory expansion

- Can be expanded up to16M bytes (for both programs and data).

- Can mix 8- and 16-bit external data buses.

- (5) 8-bit timers : 2 channels

- (6) 8-bit PWM timers : 2 channels

- (7) 16-bit timers : 2 channels

- (8) Pattern generators : 4 bits, 2 channels

- (9) Serial interface : 2 channels

- (10) 10-bit A/D converter : 4 channels

- (11) Watchdog timer

(15) Standby function

- (12) Chip select/wait controller : 3 blocks

- (13) Interrupt functions

- 3 CPU interrupts --- SWI instruction, priviledged violation, and Illegal instruction

- 14 internal interrupts

- 6 external interrupts \_\_\_\_\_7-level priority can be set.

- (14) I/O ports 47 pins

: 3 halt modes (RUN, IDLE, STOP)

000707EBP1

• For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

The products described in this document are subject to the foreign exchange and foreign trade laws.

• The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

• The information contained herein is subject to change without notice.

# TOSHIBA

# 2. Pin Assignment and Functions

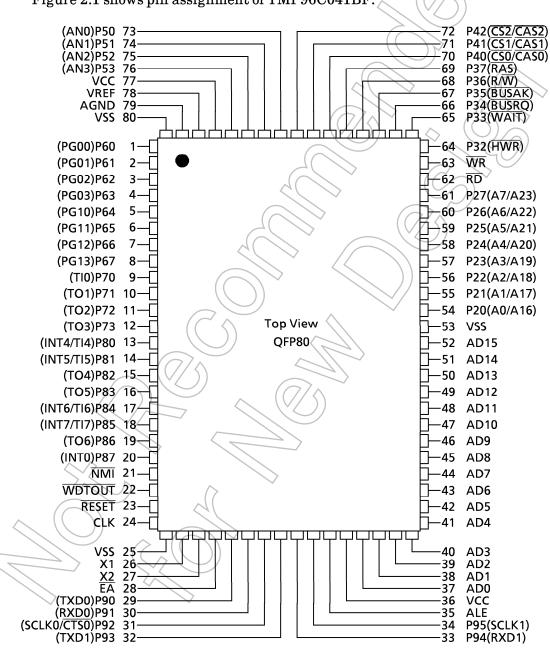

The assignment of input / output pins for TMP96C041B, their name and outline functions are described below.

#### 2.1 Pin Assignment

Figure 2.1 shows pin assignment of TMP96C041BF.

Figure 2.1 Pin Assignment (80-pin QFP)

### 2.2 Pin Names and Functions

The names of input/output pins and their functions are described below. Table 2.2 Pin Names and Functions.

| Pin name               | Number<br>of pins | I/O              | Functions                                                                                                                                                                                                                      |

|------------------------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0 to AD7             | 8                 | Tri-state        | Address/data (lower): 0 to 7 for address/data bus                                                                                                                                                                              |

| AD8 to AD15            | 8                 | Tri-state        | Address data (upper): 8 to 15 for address/data bus                                                                                                                                                                             |

| P20 to P27             | 8                 | I/O              | Port 2: I/O port that allows selection of I/O on a bit basis<br>(with pull-down resistor)                                                                                                                                      |

| A0 to A7<br>A16 to A23 |                   | Output<br>Output | Address: 0 to 7 for address bus<br>Address: 16 to 23 for address bus                                                                                                                                                           |

| RD                     | 1                 | Output           | Read: Strobe signal for reading external memory                                                                                                                                                                                |

| WR                     | 1                 | Output           | Write: Strobe signal for writing data on pins AD0 to 7                                                                                                                                                                         |

| P32<br>HWR             | 1                 | l/O<br>Output    | Port 32: I/O port (with pull-up resistor)<br>High write: Strobe signal for writing data on pins AD8 to 15                                                                                                                      |

| P33<br>WAIT            | 1                 | l/O<br>Input     | Port 33: 1/O port (with pull-up resistor)<br>Wait: Pin used to request CPU bus wait                                                                                                                                            |

| P34<br>BUSRQ           | 1                 | l/O<br>Input     | Port34: I/O port (with pull-up resistor)<br>Bus request: Signal used to request high impedance for AD0 to<br>15, A0 to 23, RD, WR, HWR, R/W, RAS, CS0, CS1, and CS2 pins.<br>(For external DMAC)                               |

| P35<br>BUSAK           | 1                 | l/O<br>Output    | Port 35: I/O port (with pull-up resistor)<br>Bus acknowledge: Signal indicating that AD0 to 15, A0 to 23,<br>RD, WR, HWR, R/W, RAS, CS0, CS1, and CS2 pins are at high<br>impedance after receiving BUSRQ. (For external DMAC) |

| P36<br>R/W             | 1                 | l/O<br>Output    | Port 36: I/O port (with pull-up resistor)<br>Read/write: 1 represents read or dummy cycle; 0, write cycle.                                                                                                                     |

| P37<br>RAS             | 1                 | l/O<br>Output    | Port 37: 1/0 port (with pull-up resistor)<br>Row address strobe: Outputs RAS strobe for DRAM.                                                                                                                                  |

| P40<br>CS0             |                   | l/O<br>Output    | Port 40: 1/O port (with pull-up resistor)<br>Chip select 0: Outputs 0 when address is within specified address<br>area.                                                                                                        |

| CASO                   | $\bigcirc$        | Output           | Column address strobe 0: Outputs CAS strobe for DRAM when address is within specified address area.                                                                                                                            |

Note : With the external DMA controller, this device's built-in memory or built-in I/O cannot be accessed using the BUSRQ and BUSAK pins.

| Pin name             | Number<br>of pins | I/O                     | Functions                                                                                                                                                                                                                           |

|----------------------|-------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P41<br>CS1<br>CAS1   | 1                 | l/O<br>Output<br>Output | Port 41: I/O port (with pull-up resistor)<br>Chip select 1: Outputs 0 if address is within specified address area.<br>Column address strobe 1: Outputs CAS strobe for DRAM if address<br>is within specified address area.          |

| P42<br>CS2<br>CAS2   | 1                 | l/O<br>Output<br>Output | Port 42: I/O port (with pull-down resistor) (Note)<br>Chip select 2: Outputs 0 if address is within specified address area.<br>Column address strobe 2: Outputs CAS strobe for DRAM if address<br>is within specified address area. |

| P50~P53<br>AN0~AN3   | 4                 | Input<br>Input          | Port 5: Input port<br>Analog input: Input to A/D converter                                                                                                                                                                          |

| VREF                 | 1                 | Input                   | Pin for reference voltage input to A/D converter                                                                                                                                                                                    |

| AGND                 | 1                 | Input                   | Ground pin for A/D converter                                                                                                                                                                                                        |

| P60~P63<br>PG00~PG03 | 4                 | l/O<br>Output           | Ports 60 to 63: I/O ports that allow selection of I/O on a bit basis<br>(with pull-up resistor)<br>Pattern generator ports: 00 to 03                                                                                                |

| P64~P67              | 4                 | I/O                     | Ports 64 to 67: 1/O ports that allow selection of I/O on a bit basis                                                                                                                                                                |

| PG10~PG13            |                   | Output                  | (with pull-up resistor)<br>Pattern generator ports: 10 to 13                                                                                                                                                                        |

| P70<br>TI0           | 1                 | l/O<br>Input            | Port 70: 1/O port (with pull-up resistor)<br>Timer input 0: Timer 0 input                                                                                                                                                           |

| P71<br>TO1           | 1                 | l/O<br>Output           | Port 71: I/O port (with pull-up resistor)<br>Timer output 1: Timer 0 or 1 output                                                                                                                                                    |

| P72<br>TO2           | 1                 | l/O<br>Output           | Port 72: I/O port (with pull-up resistor)<br>PWM output 2: 8-bit PWM timer 2 output                                                                                                                                                 |

| Р73<br>ТО3           | 1                 | 1/0<br>Output           | Port 73: I/O port (with pull-up resistor)<br>PWM output 3: 8-bit PWM timer 3 output                                                                                                                                                 |

| P80<br>TI4<br>INT4   | 1                 | l/O<br>Input<br>Input   | Port 80: I/O port (with pull-up resistor)<br>Timer input 4: Timer 4 count/capture trigger signal input<br>Interrupt request pin 4: Interrupt request pin with programmable<br>rising/falling edge                                   |

| P81<br>TI5<br>INT5   |                   | l/O<br>Input<br>Input   | Port 81: I/O port (with pull-up resistor)<br>Timer input 5: Timer 4 count/capture trigger signal input<br>Interrupt request pin 5: Interrupt request pin with rising edge                                                           |

| P82<br>TQ4           |                   | V/O<br>Output           | Port 82: I/O port (with pull-up resistor)<br>Timer output 4: Timer 4 output pin                                                                                                                                                     |

| P83<br>TO5           | 1                 | l/O<br>Output           | Port 83: I/O port (with pull-up resistor)<br>Timer output 5: Timer 4 output pin                                                                                                                                                     |

Note : Case of the settable CS2 or CAS2; when TMP96C041BF is bus release, this pin is not added the internal pull-down resistor but is added the internal pull-up resistor.

| Pin name             | Number<br>of pins | I/O                               | Functions                                                                                                                                                                                         |

|----------------------|-------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P84<br>TI6<br>INT6   | 1                 | l/O<br>Input<br>Input             | Port 84: I/O port (with pull-up resistor)<br>Timer input 6: Timer 5 count/capture trigger signal input<br>Interrupt request pin 6: Interrupt request pin with<br>programmable rising/falling edge |

| P85<br>TI7<br>INT7   | 1                 | l/O<br>Input<br>Input             | Port 85: I/O port (with pull-up resistor)<br>Timer input 7: Timer 5 count/capture trigger signal input<br>Interrupt request pin 7: Interrupt request pin with rising edge                         |

| P86<br>TO6           | 1                 | l/O<br>Output                     | Port 86: I/O port (with pull-up resistor)<br>Timer output 6: Timer 5 output pin                                                                                                                   |

| P87<br>INT0          | 1                 | l/O<br>Input                      | Port 87: I/O port (with pull-up resistor)<br>Interrupt request pin 0: Interrupt request pin with<br>programmable level/rising edge                                                                |

| P90<br>TXD0          | 1                 | l/O<br>Output                     | Port 90: I/O port (with pull-up resistor)<br>Serial send data 0                                                                                                                                   |

| P91<br>RXD0          | 1                 | l/O<br>Input                      | Port 91: I/O port (with pull-up resistor)<br>Serial receive data 0                                                                                                                                |

| P92<br>CTS0<br>SCLK0 | 1                 | l/O<br>Input                      | Port 92: 1/O port (with pull-up resistor)<br>Serial data send enable 0 (Clear to Send)<br>Serial clock 1/O 0                                                                                      |

| P93<br>TXD1          | 1                 | l/O<br>Output                     | Port 93: 1/O port (with pull-up resistor)<br>Serial send data 1                                                                                                                                   |

| P94<br>RXD1          | 1                 | l/O<br>Input                      | Port 94: I/O port (with pull-up resistor)<br>Serial receive data 1                                                                                                                                |

| P95<br>SCLK1         | 1                 | 1/0<br>1/0                        | Port 95: I/O port (with pull-up resistor)<br>Serial clock I/O 1                                                                                                                                   |

| WDTOUT               | 1                 | Output                            | Watchdog timer output pin                                                                                                                                                                         |

| NMI                  | 1                 | Input                             | Non-maskable interrupt request pin: Interrupt request pin with falling edge. Can also be operated at rising edge by program.                                                                      |

| CLK                  | 1                 | Output                            | Clock output: Outputs [X1÷4] clock. Pulled-up during reset.                                                                                                                                       |

| EA                   | $\sim 7$          | Input                             | External access: 0 should be inputted with TMP96C041B.                                                                                                                                            |

| ALE                  | $\sum_{i=1}^{n}$  | Output                            | Address latch enable                                                                                                                                                                              |

| RESET                |                   | Input                             | Reset: Initializes LSI. (With pull-up resistor)                                                                                                                                                   |

| X1/X2                | 2                 | 1/0                               | Oscillator connecting pin                                                                                                                                                                         |

| VCC                  | 2                 | $\langle \rangle \langle \rangle$ | Power supply pin ( + 5 V) (All Vcc pins should be connected with the power supply pin.)                                                                                                           |

| VSS                  | 3                 |                                   | GND pin (0 V) (All Vss pins should be connected with GND (0 V).)                                                                                                                                  |

Note : Pull-up/pull-down resistor can be released from the pin by software (except the RESET pin).

# 3. Operation

This section describes the functions and basic operations of TMP96C041B device.

The function of CPU and internal I/O devices are the same function as TMP96C141B. Check the  $\lceil 7$ . Care Points and Restriction of TMP96C141B  $\rfloor$  because of the Care described.

Regarding the functions of TMP96C041B (not described), see the part of TMP96C141B.

TMP96C141B/TMP96C041B have much the same function but they are different from following points.

| Parameter                                          | ТМР96С141В    | ТМР96С041В   |

|----------------------------------------------------|---------------|--------------|

| Interrnal RAM                                      | 1 Kbyte       | not exist    |

| Mapping area of CS1 defult<br>setting (B1C1/0: 00) | 480H to 7FFFH | 80H to 7FFFH |

|                                                    |               |              |

# 3.1 CPU

TMP96C041B device has a built-in high-performance 16-bit CPU (900-CPU). (For CPU operation, see TLCS-900 CPU in the previous section.)

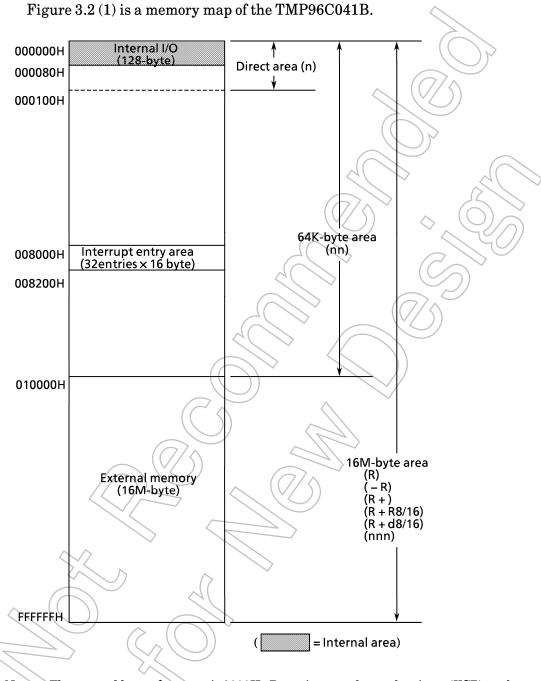

# 3.2 Memory Map

TMP96C041B has two register modes. One is a minimum mode; in this mode, the area of program memory is 64 Kbytes maximum. The other is a maximum mode; in this mode, the area of program memory is 16 Mbytes maximum.

Both minimum and maximum modes are the data memory area of 16 Mbytes maximum.

That is, the program memory can locate 0H to FFFFH in minimum mode and can locate 0H to FFFFFFH in maximum mode.

#### **Memory Map**

Note : The start address after reset is 8000H. Resetting sets the stack pointer (XSP) on the system mode side to 100H.

Figure 3.2 (1) Memory map

# TOSHIBA

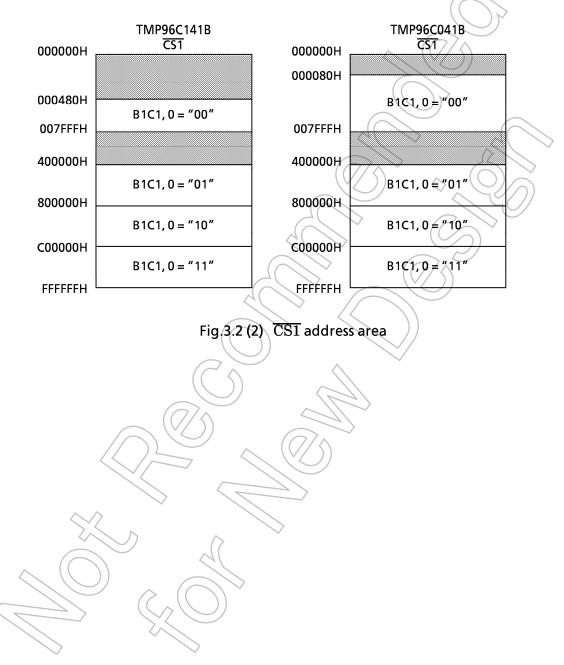

## (2) $\overline{CS1}$ area (Chip select / wait controller)

TMP96C041B is expanded the part of address area for  $\overline{\text{CS1}}$  (only B1C1.0="00"). Show the address area of  $\overline{\text{CS1}}$  in Fig 3.2 (2).

# 4. Electrical Characteristics

### 4.1 Absolute Maximum Ratings (TMP96C041BF)

|                                         |          | 2                  |      |

|-----------------------------------------|----------|--------------------|------|

| Parameter                               | Symbol   | Rating             | Unit |

| Power Supply Voltage                    | V cc     | – 0.5 to 6.5       | V    |

| Input Voltage                           | VIN      | – 0.5 to Vcc + 0.5 | v    |

| Output Current (total)                  | ΣIOL     | 100                | mA   |

| Output Current (total)                  | ΣΙΟΗ     | - 100              | mA   |

| Power Dissipation (Ta = $85^{\circ}$ C) | P D      | 500                | m₩   |

| Soldering Temperature (10 s)            | T SOLDER | 260                | °C   |

| Storage Temperature                     | T STG    | -65 to 150         | °C > |

| Operating Temperature                   | T OPR    | -40 to 85          |      |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

### 4.2 DC Characteristics (TMP96C041BF)

Vcc = 5 V ± 10%, TA = -40 to 85°C (4 to 16 MHz) TA = -20 to 70°C (4 to 20 MHz) (Typical values are for Ta = 25°C and Vcc = 5 V)

| Parameter                                                                                                        | Symbol                                   | Test Condition                                                               | Min                                                | Max                                                                        | Unit                     |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------|--------------------------|

| Input Low Voltage (AD0 to 15)<br><u>P2, P3, P4,</u> P5, P6, P7, P8, P9<br><u>RESET,NMI,INT0(P87)</u><br>EA<br>X1 | V IL<br>V IL1<br>V IL2<br>V IL3<br>V IL4 |                                                                              | -0.3<br>-0.3<br>-0.3<br>-0.3<br>-0.3<br>-0.3       | 0.8<br>0.3 Vcc<br>0.25 Vcc<br>0.3<br>0.2 Vcc                               | V<br>V<br>V<br>V<br>V    |

| Input High Voltage (AD0 – 15)<br>P2, P3, P4, P5, P6, P7, P8, P9<br>RESET, NMI, INTO (P87)<br>EA<br>X1            | V IH<br>V IH1<br>V IH2<br>V IH3<br>V IH4 |                                                                              | 2.2<br>0.7 Vcc<br>0.75 Vcc<br>Vcc – 0.3<br>0.8 Vcc | Vcc + 0.3<br>Vcc + 0.3<br>Vcc + 0.3<br>Vcc + 0.3<br>Vcc + 0.3<br>Vcc + 0.3 | V<br>V<br>V<br>V<br>V    |

| Output Low Voltage                                                                                               | VOL                                      | I OL = 1.6 mA                                                                | (                                                  | 0.45                                                                       | V                        |

| Output High Voltage                                                                                              | V OH<br>V OH1<br>V OH2                   | I OH = - 400 μA<br>I OH = - 100 μA<br>I OH = - 20 μA                         | 2.4<br>0.75 Vcc<br>0.9 Vcc                         | RO                                                                         | V<br>V<br>V              |

| Darlington Drive Current<br>(8 Output Pins max.)                                                                 | IDAR                                     | V EXT = 1.5 V<br>R EXT = 1.1 kΩ                                              | -1.0                                               | - 3.5                                                                      | mA                       |

| Input Leakage Current<br>Output Leakage Current                                                                  | I LI<br>I LO                             | 0.0≦Vin≧Vcc<br>0.2≦Vin≦Vcc – 0.2                                             | 0.02 (Typ)<br>0.05 (Typ)                           | ±5<br>±10                                                                  | μ <b>Α</b><br>μ <b>Α</b> |

| Operating Current (RUN)<br>IDLE<br>STOP (Ta = − 40 to 85℃)<br>STOP (Ta = 0 to 50℃)                               |                                          | t osc = 20 MHz<br>$0.2 \le Vin \le Vcc - 0.2$<br>$0.2 \le Vin \le Vcc - 0.2$ | 21 (Typ)<br>1.7 (Typ)<br>0.2 (Typ)                 | 50<br>10<br>50<br>10                                                       | mA<br>mA<br>μA<br>μA     |

| Power Down Voltage<br>(@ STOP, RAM Back up)                                                                      | V STOP                                   | V IL2 = 0.2 Vcc,<br>V IH2 = 0.8 Vcc                                          | 2.0                                                | 6.0                                                                        | V                        |

| RESET Pull Up Resistor                                                                                           | RRST                                     |                                                                              | 50                                                 | 150                                                                        | kΩ                       |

| Pin Capacitance                                                                                                  | C-10                                     | tosc = 1 MHz                                                                 |                                                    | 10                                                                         | рF                       |

| Schmitt Width<br>RESET, NMI, INTO (P87)                                                                          | VTH                                      |                                                                              | 0.4                                                | 1.0 (Typ)                                                                  | V                        |

| Programmable Pull Down Resistor                                                                                  | RKL                                      | (7/5)                                                                        | 10                                                 | 80                                                                         | kΩ                       |

| Programmable Pull Up Resistor                                                                                    | RKH                                      |                                                                              | 50                                                 | 150                                                                        | kΩ                       |

Note : I-DAR is guaranteed for a total of up to 8 ports.

2003-03-31

### 4.3 AC Electrical Characteristics (TMP96C041BF)

| 4 CLK Valid<br>5 A0 to 15 V<br>6 ALE fall –<br>7 ALE High<br>8 ALE fall –<br>9 $\overline{RD}/WR$ ris<br>10 A0 to 15 V<br>11 A0 to 23 V<br>12 $\overline{RD}/WR$ ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 $\overline{RD}$ fall →<br>16 $\overline{RD}$ Low<br>17 $\overline{RD}$ rise →                                                 | $d (= x)$ $Alid \rightarrow CLK Hold$ $Alid \rightarrow CLK Hold$ $Alid \rightarrow ALE fall$ $Alid \rightarrow ALE fall$ $Alid \rightarrow ALE fall$        | Symbol<br>t <sub>OSC</sub><br>t <sub>CLK</sub><br>t <sub>AK</sub><br>t <sub>KA</sub><br>t <sub>AL</sub> | Min<br>50<br>2x - 40<br>0.5x - 20<br>1.5x - 70 | avle<br>Max<br>250    | Min<br>62.5<br>85 | ИНz<br>Max               | Min<br>50  | ИНz<br>Max | Unit<br>ns |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------|-------------------|--------------------------|------------|------------|------------|

| 2 CLK width<br>3 A0 to 23 $\land$<br>4 CLK Valid<br>5 A0 to 15 $\land$<br>6 ALE fall –<br>7 ALE High<br>8 ALE fall –<br>9 RD/WR ris<br>10 A0 to 15 $\land$<br>11 A0 to 23 $\land$<br>12 RD/WR ris<br>13 A0 to 15 $\land$<br>14 A0 to 23 $\land$<br>15 RDfall →<br>16 RD Low<br>17 RDrise →                                                 | a<br>A alid → CLK Hold<br>→ A0 to 23 Hold<br>A alid → ALE fall<br>A0 to 15 Hold                                                                              | t <sub>CLK</sub><br>t <sub>AK</sub><br>t <sub>KA</sub><br>t <sub>AL</sub>                               | 2x - 40<br>0.5x - 20                           |                       | 62.5              |                          | 50         |            | ns         |

| 2 CLK width<br>3 A0 to 23 $\land$<br>4 CLK Valid<br>5 A0 to 15 $\land$<br>6 ALE fall –<br>7 ALE High<br>8 ALE fall –<br>9 RD/WR ris<br>10 A0 to 15 $\land$<br>11 A0 to 23 $\land$<br>12 RD/WR ris<br>13 A0 to 15 $\land$<br>14 A0 to 23 $\land$<br>15 RDfall →<br>16 RD Low<br>17 RDrise →                                                 | a<br>A alid → CLK Hold<br>→ A0 to 23 Hold<br>A alid → ALE fall<br>A0 to 15 Hold                                                                              | t <sub>CLK</sub><br>t <sub>AK</sub><br>t <sub>KA</sub><br>t <sub>AL</sub>                               | 0.5x – 20                                      |                       | 85                |                          | 6          |            |            |

| 4 CLK Valid<br>5 A0 to 15 V<br>6 ALE fall –<br>7 ALE High<br>8 ALE fall –<br>9 $\overline{RD}/WR$ ris<br>10 A0 to 15 V<br>11 A0 to 23 V<br>12 $\overline{RD}/WR$ ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 $\overline{RD}$ fall →<br>16 $\overline{RD}$ Low<br>17 $\overline{RD}$ rise →                                                 | $\rightarrow$ A0 to 23 Hold<br>(alid $\rightarrow$ ALE fall<br>$\Rightarrow$ A0 to 15 Hold                                                                   | t <sub>AK</sub><br>t <sub>KA</sub><br>t <sub>AL</sub>                                                   | 0.5x – 20                                      |                       |                   |                          | 60         | 1          | ns         |

| 5 A0 to 15 $\land$<br>6 ALE fall –<br>7 ALE High<br>8 ALE fall –<br>9 RD/WR ris<br>10 A0 to 15 $\land$<br>11 A0 to 23 $\land$<br>12 RD/WR ris<br>13 A0 to 15 $\land$<br>14 A0 to 23 $\land$<br>15 RDfall →<br>16 RD Low<br>17 RDrise →                                                                                                     | /alid → ALE fall<br>→ A0 to 15 Hold                                                                                                                          | t <sub>KA</sub><br>t <sub>AL</sub>                                                                      |                                                | ~                     | (11/              | $\langle \wedge \rangle$ | 5          |            | ns         |

| 5 A0 to 15 $\land$<br>6 ALE fall –<br>7 ALE High<br>8 ALE fall –<br>9 RD/WR ris<br>10 A0 to 15 $\land$<br>11 A0 to 23 $\land$<br>12 RD/WR ris<br>13 A0 to 15 $\land$<br>14 A0 to 23 $\land$<br>15 RDfall →<br>16 RD Low<br>17 RDrise →                                                                                                     | /alid → ALE fall<br>→ A0 to 15 Hold                                                                                                                          | t <sub>AL</sub>                                                                                         | 1.37 - 70                                      |                       | 24                | $\mathcal{D}\mathcal{D}$ | 5          |            | ns         |

| 7 ALE High<br>8 ALE fall –<br>9 $\overline{RD}/WR$ ris<br>10 A0 to 15 V<br>11 A0 to 23 V<br>12 $\overline{RD}/WR$ ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 $\overline{RD}$ fall $\rightarrow$<br>16 $\overline{RD}$ Low<br>17 $\overline{RD}$ rise $\rightarrow$                                                                        |                                                                                                                                                              |                                                                                                         | 0.5x – 15                                      |                       | 16                |                          | 10         |            | ns         |

| 7 ALE High<br>8 ALE fall –<br>9 $\overline{RD}/WR$ ris<br>10 A0 to 15 V<br>11 A0 to 23 V<br>12 $\overline{RD}/WR$ ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 $\overline{RD}$ fall $\rightarrow$<br>16 $\overline{RD}$ Low<br>17 $\overline{RD}$ rise $\rightarrow$                                                                        |                                                                                                                                                              | t <sub>LA</sub>                                                                                         | 0.5x – 15                                      |                       | 16                |                          | 10         |            | ns         |

| $\begin{array}{c c} 8 & ALE fall - \\ 9 & \overline{RD}/WR ris \\ \hline 10 & A0 to 15 \\ \hline 11 & A0 to 23 \\ \hline 12 & \overline{RD}/WR ris \\ \hline 13 & A0 to 15 \\ \hline 14 & A0 to 23 \\ \hline 15 & \overline{RD}fall \rightarrow \\ \hline 16 & \overline{RD} Low \\ \hline 17 & \overline{RD}rise \rightarrow \end{array}$ |                                                                                                                                                              | t <sub>LL</sub>                                                                                         | x – 40                                         |                       | 23                |                          | 10         |            | ns         |

| 10 A0 to 15 V<br>11 A0 to 23 V<br>12 RD/WR ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 RDfall $\rightarrow$<br>16 RD Low<br>17 RDrise $\rightarrow$                                                                                                                                                                                        | RD/WR fall                                                                                                                                                   | t <sub>LC</sub>                                                                                         | 0.5x – 30                                      |                       | 1                 |                          | -5         |            | ns         |

| 11 A0 to 23 V<br>12 $\overline{RD}/\overline{WR}$ ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 $\overline{RD}$ fall $\rightarrow$<br>16 $\overline{RD}$ Low<br>17 $\overline{RD}$ rise $\rightarrow$                                                                                                                                        | $e \rightarrow ALE rise$                                                                                                                                     | t <sub>CL</sub>                                                                                         | 0.5x – 20                                      | 40                    | 2 11              |                          | $\sqrt{5}$ | $\searrow$ | ns         |

| 11 A0 to 23 V<br>12 $\overline{RD}/\overline{WR}$ ris<br>13 A0 to 15 V<br>14 A0 to 23 V<br>15 $\overline{RD}$ fall $\rightarrow$<br>16 $\overline{RD}$ Low<br>17 $\overline{RD}$ rise $\rightarrow$                                                                                                                                        | /alid → $\overline{RD}/\overline{WR}$ fall                                                                                                                   | t <sub>ACL</sub>                                                                                        | x – 25                                         | $\sim$                | 38                | 0                        | 25         |            | ns         |

| 13 A0 to 15 $\land$<br>14 A0 to 23 $\land$<br>15 RDfall →<br>16 RD Low<br>17 RDrise →                                                                                                                                                                                                                                                      | $\operatorname{Alid} \rightarrow \overline{\mathrm{RD}} / \overline{\mathrm{WR}}$ fall                                                                       | tACH                                                                                                    | 1.5x – 50                                      | $(7/\delta)$          | 44                | 6                        | 25         | 7          | ns         |

| 13 A0 to 15 $\land$<br>14 A0 to 23 $\land$<br>15 RDfall →<br>16 RD Low<br>17 RDrise →                                                                                                                                                                                                                                                      | $e \rightarrow A0$ to 23 Hold                                                                                                                                | t <sub>CA</sub>                                                                                         | 0.5x – 20                                      | $( \langle \rangle )$ | Ń                 | $\mathcal{C}$            | 1/5        | )          | ns         |

| 14 A0 to 23 $^{15}$ RD fall →<br>16 RD Low<br>17 RD rise →                                                                                                                                                                                                                                                                                 | /alid → D0 to 15 input                                                                                                                                       | t <sub>ADL</sub>                                                                                        |                                                | 3.0x - 45             |                   | 143                      | 50         | 105        | ns         |

| $\begin{array}{c c} 15 & \overline{RD} \text{fall} \rightarrow \\ \hline 16 & \overline{RD} & \text{Low} \\ \hline 17 & \overline{RD} & \text{rise} \rightarrow \end{array}$                                                                                                                                                               | /alid → D0 to 15 input                                                                                                                                       | t <sub>ADH</sub>                                                                                        | 70                                             | 3.5x – 65             |                   | 154                      |            | 110        | ns         |

| $\begin{array}{c c} 16 & \overline{RD} & Low \\ \hline 17 & \overline{RD} & rise \rightarrow \end{array}$                                                                                                                                                                                                                                  | •                                                                                                                                                            | t <sub>RD</sub>                                                                                         |                                                | 2.0x – 50             |                   | 75                       | ~          | 50         | ns         |

|                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              | t <sub>RR</sub>                                                                                         | 2.0x - 40                                      |                       | 85                | $\mathcal{T}$            | 60         |            | ns         |

|                                                                                                                                                                                                                                                                                                                                            | D0 to 15 Hold                                                                                                                                                | t <sub>HR</sub>                                                                                         | $\overline{)}$                                 |                       |                   | $\bigcirc$               | 0          |            | ns         |

|                                                                                                                                                                                                                                                                                                                                            | A0 to 15output                                                                                                                                               | tRAE                                                                                                    | x - 15                                         | (                     | 48                | )                        | 35         |            | ns         |

| 19 WR Low                                                                                                                                                                                                                                                                                                                                  | width                                                                                                                                                        | tww                                                                                                     | 2.0x – 40                                      |                       | 85                | (                        | 60         |            | ns         |

| 20 D0 to 15 \                                                                                                                                                                                                                                                                                                                              | $\operatorname{Valid} \rightarrow \overline{\operatorname{WR}}$ rise                                                                                         | t <sub>DW</sub>                                                                                         | 2.0x - 50                                      | $\langle \rangle$     | 75                |                          | 50         |            | ns         |

|                                                                                                                                                                                                                                                                                                                                            | D0 to 15 Hold                                                                                                                                                | twp                                                                                                     | 0.5x – 10                                      | $\langle \rangle$     | 21                |                          | 15         |            | ns         |

|                                                                                                                                                                                                                                                                                                                                            | $\operatorname{Alid} \rightarrow \overline{WAIT} \operatorname{input} \begin{pmatrix} 1WAIT \\ + n \mod e \end{pmatrix}$                                     | tAEH                                                                                                    |                                                | 3.5x - 90             | /                 | 129                      |            | 85         | ns         |

|                                                                                                                                                                                                                                                                                                                                            | $\operatorname{Alid} \rightarrow \overline{WAIT} \operatorname{input} \left( \begin{smallmatrix} 1WAIT \\ + n \operatorname{mode} \end{smallmatrix} \right)$ | tAWL                                                                                                    |                                                | 3.0x - 80             |                   | 108                      |            | 70         | ns         |

|                                                                                                                                                                                                                                                                                                                                            | $   \rightarrow \overline{\text{WAIT}} \text{ Hold } (1 \text{WAIT} + n \text{ mode})$                                                                       | tcw                                                                                                     | 2.0x + 0                                       |                       | 125               |                          | 100        |            | ns         |

|                                                                                                                                                                                                                                                                                                                                            | $/alid \rightarrow PORT input$                                                                                                                               | )t <sub>APH</sub>                                                                                       | ~                                              | 2.5x – 120            |                   | 36                       |            | 5          | ns         |

|                                                                                                                                                                                                                                                                                                                                            | $/alid \rightarrow PORT Hold$                                                                                                                                | t <sub>APH2</sub>                                                                                       | 2.5x + 50                                      | $\geq$                | 206               |                          | 175        |            | ns         |

| 27 WR rise –                                                                                                                                                                                                                                                                                                                               | PORT Valid                                                                                                                                                   | t <sub>CP</sub>                                                                                         | $\sim$                                         | 200                   |                   | 200                      |            | 200        | ns         |

| 28 A0 to 23 \                                                                                                                                                                                                                                                                                                                              | $\operatorname{Alid} \rightarrow \overline{\operatorname{RAS}}$ fall                                                                                         | tASRH                                                                                                   | 1.0x-40                                        | 2                     | 23                |                          | 10         |            | ns         |

| 29 A0 to 15 \                                                                                                                                                                                                                                                                                                                              | alid $\rightarrow \overline{RAS}$ fall                                                                                                                       | tASRL                                                                                                   | 0.5x - 15                                      |                       | 16                |                          | 10         |            | ns         |

| 30 RAS fall –                                                                                                                                                                                                                                                                                                                              | D0 to 15 input                                                                                                                                               | t <sub>RAC</sub>                                                                                        | $\overline{(O)}$                               | 2.5x – 70             |                   | 86                       |            | 55         | ns         |

|                                                                                                                                                                                                                                                                                                                                            | A0 to 15 Hold                                                                                                                                                | t <sub>RAH</sub>                                                                                        | 0.5x - 15                                      |                       | 16                |                          | 10         |            | ns         |

| 32 RAS Low                                                                                                                                                                                                                                                                                                                                 | width                                                                                                                                                        | tRAS                                                                                                    | 2.0x – 40                                      |                       | 85                |                          | 60         |            | ns         |

| 33 RAS High                                                                                                                                                                                                                                                                                                                                | width                                                                                                                                                        | t <sub>RP</sub>                                                                                         | 2.0x - 40                                      |                       | 85                |                          | 60         |            | ns         |

| 34 CAS fall                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              | t <sub>RSH</sub>                                                                                        | 1.0x – 35                                      |                       | 28                |                          | 15         |            | ns         |

| 35 RAS rise –                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                              | t <sub>RSC</sub>                                                                                        | 0.5x – 25                                      |                       | 6                 |                          | 0          |            | ns         |

| 36 RAS fall                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              | t <sub>RCD</sub>                                                                                        | 1.0x – 40                                      |                       | 23                |                          | 10         |            | ns         |

| 37 CAS fall                                                                                                                                                                                                                                                                                                                                | D0 to 15 input                                                                                                                                               | tCAC                                                                                                    |                                                | 1.5x – 65             |                   | 29                       |            | 10         | ns         |

| 38 CAS Low                                                                                                                                                                                                                                                                                                                                 | width                                                                                                                                                        | tcas                                                                                                    | 1.5x – 30                                      |                       | 64                |                          | 40         |            | ns         |

| 39 D0 to 15                                                                                                                                                                                                                                                                                                                                | $\operatorname{Alid} \to \overline{\operatorname{CAS}}$ fall                                                                                                 | t <sub>DS</sub>                                                                                         | 0.5x – 15                                      |                       | 16                |                          | 10         |            | ns         |

|                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              | -                                                                                                       |                                                |                       |                   |                          |            |            |            |

|                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |                                                                                                         |                                                |                       | L i               | L i                      |            | L          | L          |

|                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |                                                                                                         |                                                |                       |                   |                          |            |            |            |

|                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                              |                                                                                                         |                                                |                       |                   |                          |            |            |            |

AC Measuring Conditions

• Output Level : High 2.2 V / Low 0.8 V, CL50 pF

(However CL = 100pF for AD0 to AD15, A0 to A23, ALE, RD, WR, HWR, R/W, CLK, RAS, CAS0 to CAS2) Input Level : High 2.4 V / Low 0.45 V (AD0 to AD15)

High 0.8 Vcc / Low 0.2 Vcc (Except for AD0 to AD15)

# TOSHIBA

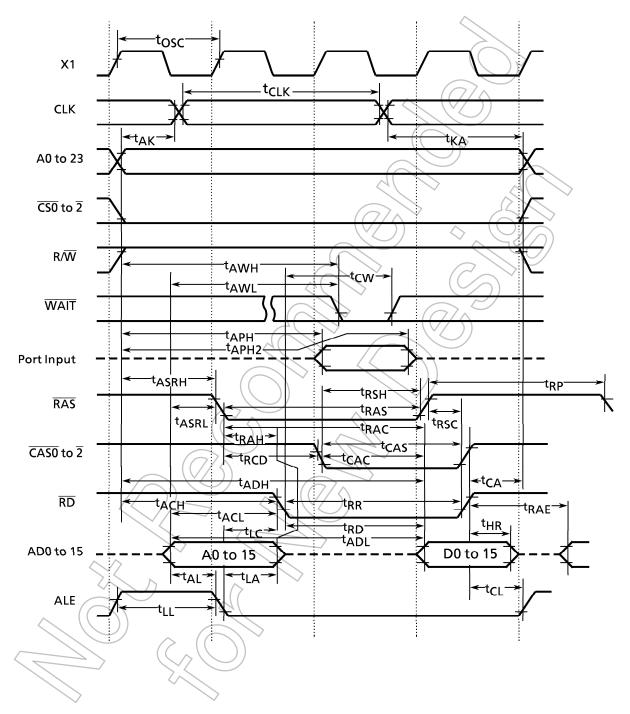

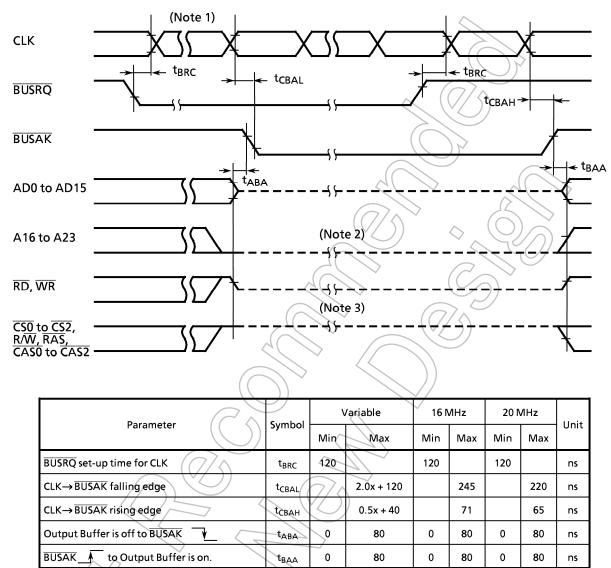

## (1) Read Cycle

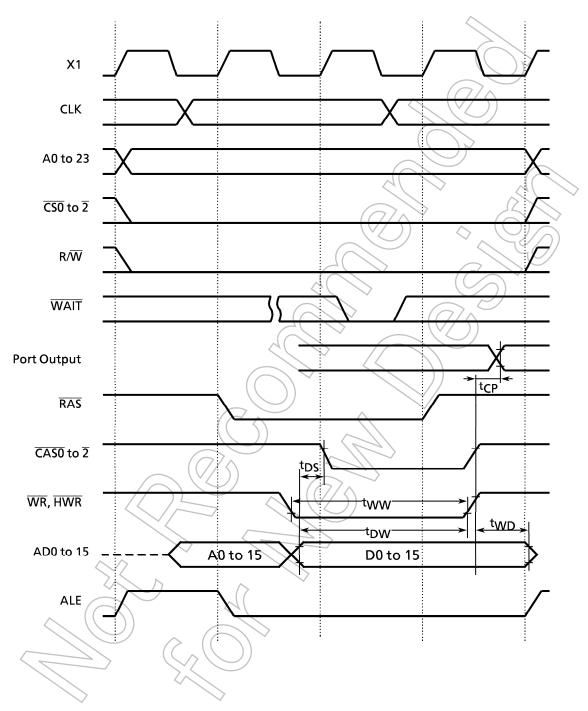

### (2) Write Cycle

#### 4.4 A/D Conversion Characteristics (TMP96C041BF)

|                                                                                                                                | Vcc = 5          | V ± 10%, TA = - 40             | to 85℃ (4 to 1 | 6 MHz) TA = - 2 | 20 to 70℃ (4 to | 20 MHz) |  |

|--------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|----------------|-----------------|-----------------|---------|--|

| Parameter                                                                                                                      |                  | Symbol                         | Min            | Тур.            | Max             | Unit    |  |

| Analog reference voltage                                                                                                       |                  | V <sub>REF</sub>               | Vcc – 1.5      |                 | Vec             |         |  |

| Analog reference voltage                                                                                                       |                  | A <sub>GND</sub>               | Vss            |                 | Vss             | v       |  |

| Analog input voltage range                                                                                                     |                  | V <sub>AIN</sub>               | Vss            | 6               | Vcc             |         |  |

| Anlog current for analog reference voltage                                                                                     |                  | I <sub>REF</sub>               |                | 0.5             | ) 1.5           | mA      |  |

| Low change mode                                                                                                                |                  |                                |                | ±1.5            | ± 4.0           |         |  |

| $4 \le fc \le 16 \text{ MHz} \qquad \qquad \text{High change mode}$                                                            |                  | Total error<br>(Quantize error |                | (±3.0           | ±6.0            | LSB     |  |

| 16 <fc≦20 mhz<="" td=""><td>Low change mode</td><td>of ± 0.5 LSB not</td><td></td><td>±1.5</td><td>± 4.0</td><td></td></fc≦20> | Low change mode  | of ± 0.5 LSB not               |                | ±1.5            | ± 4.0           |         |  |

| 16< IC ≧ 20 IVIHZ                                                                                                              | High change mode | included)                      | 2              | ±4,0            | ± 8.0           |         |  |

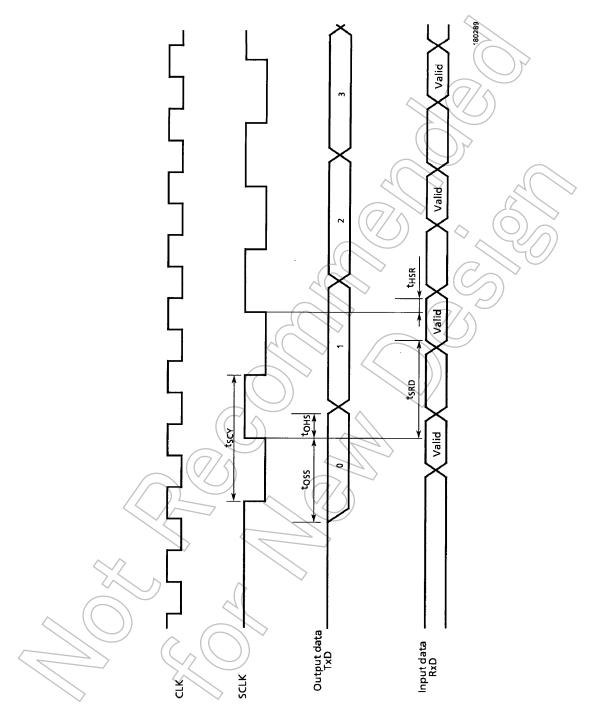

#### 4.5 Serial Channel Timing – I/O Interface Mode

#### (1) SCLK Input Mode Vcc = 5 V ± 10%, TA = -40 to 85°C (4 to 16 MHz) TA = -20 to 70°C (4 to 20 MHz)

| Parameter                                           | Cumple al        | Varia                             | 16 MHz 20 M                 |     |            | viHz / | Hz  |         |

|-----------------------------------------------------|------------------|-----------------------------------|-----------------------------|-----|------------|--------|-----|---------|

| Parameter                                           | Symbol           | Min 🔟                             | Max                         | Min | Max        | Min    | Max | Unit    |

| SCLK cycle                                          | t <sub>SCY</sub> | 16X                               |                             | 1   | (C         | 0.8    |     | $\mu$ S |

| Output Data $\rightarrow$ Rising edge of SCLK       | t <sub>OSS</sub> | t <sub>SCY</sub> /2 – 5X – 50     |                             | 137 |            | 100    |     | ns      |

| SCLK rising edge $\rightarrow$ Output Data hold     | t <sub>OHS</sub> | 5X - 100                          | $\geq$                      | 212 | 7/         | 150    |     | ns      |

| SCLK rising edge $\rightarrow$ Input Data hold      | t <sub>HSR</sub> | 0                                 |                             | 0   | $\bigcirc$ | 0      |     | ns      |

| SCLK rising edge $\rightarrow$ effective data input | t <sub>SRD</sub> | $\langle \langle \rangle \rangle$ | t <sub>SCY</sub> – 5X – 100 |     | 587        |        | 450 | ns      |

(2) SCLK Output Modecc =  $5 V \pm 10\%$ , TA = -40 to 85% (4 to 16 MHz) TA = -20 to 70% (4 to 20 MHz)

| Parameter                                           | Symbol            | Varia                             | 16 MHz                      |     | 20 MHz |     | Unit  |      |

|-----------------------------------------------------|-------------------|-----------------------------------|-----------------------------|-----|--------|-----|-------|------|

|                                                     |                   | Min                               | Max                         | Min | Max    | Min | Max   | Unit |

| SCLK cycle (programmable)                           | t <sub>SCY</sub>  | 16X                               | 8192X                       | 1   | 512    | 0.8 | 409.6 | μs   |