#### CMOS 32-bit Micro-controller

### TMP92FD54AIF

### 1. Outline and Device Characteristics

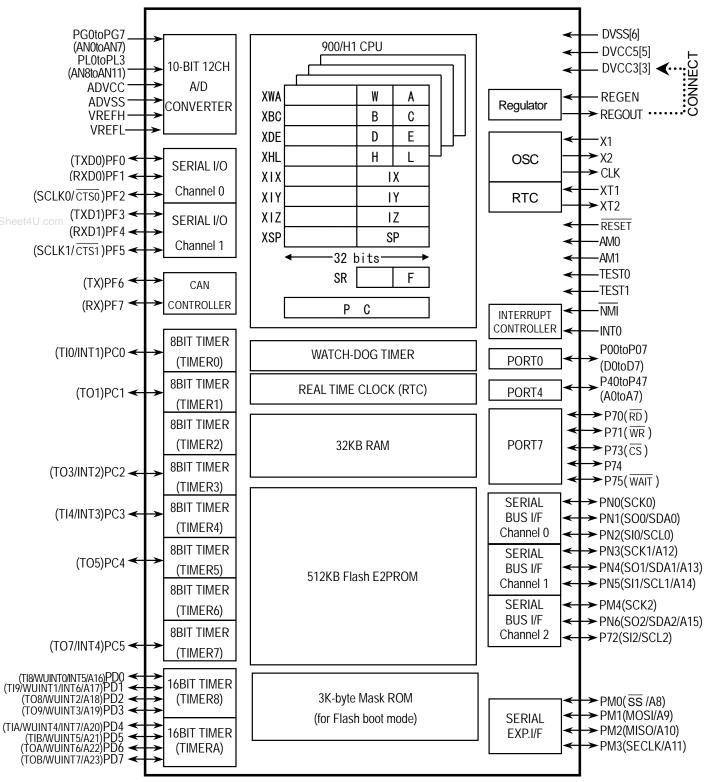

TMP92FD54AI is high-speed advanced 32-bit micro-controller developed for controlling equipment which processes mass data.

TMP92FD54AI is a micro-controller which has a high-performance CPU (900/H1 CPU) and various built-in I/Os. TMP92FD54AI is housed in a 100-pin mini flat package.

Device characteristics are as follows:

(1) CPU: 32-bit CPU(900/H1 CPU)

Compatible with TLCS-900,900/L,900/L1,900/H,900/H2's instruction code 16Mbytes of linear address space General-purpose register and register banks Micro DMA : 8channels (250ns / 4bytes at fc = 20MHz, best case) Minimum instruction execution time : 50ns(at 20MHz) Internal data bus : 32-bit

(2) Internal memory

Internal RAM : 32K-byte Internal ROM : 512K-byte Flash E2PROM 3K-byte Mask ROM (for Flash boot mode)

#### **RESTRICTIONS ON PRODUCT USE**

060116EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. 021023\_C

- The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

# TOSHIBA

|            | (3)               | External memory expansion                                          |

|------------|-------------------|--------------------------------------------------------------------|

|            |                   | 16M-byte linear address space (memory mapped I/O)                  |

|            |                   | External data bus : 8bit(for external I/O expansion)               |

|            |                   | * Can't use upper address bus when built-in I/Os are selected      |

|            | (4)               | Memory controller (MEMC)                                           |

|            |                   | Chip select output : 1 channel                                     |

|            | (5)               | 8-bit timer : 8 channels                                           |

|            |                   | 8-bit interval timer mode (8 channels)                             |

|            |                   | 16-bit interval timer mode (4 channels)                            |

|            |                   | 8-bit programmable pulse generation (PPG) output mode (4 channels) |

|            |                   | 8-bit pulse width modulation (PWM) output mode (4 channels)        |

| Sheet4U.co | (6)               | 16-bit timer : 2 channels                                          |

|            |                   | 16-bit interval timer mode                                         |

|            |                   | 16-bit event counter mode                                          |

|            |                   | 16-bit programmable pulse generation (PPG) output mode             |

|            |                   | Frequency measurement mode<br>Pulse width measurement mode         |

|            |                   | Time differential measurement mode                                 |

|            | (7)               | Serial interface (SIO) : 2 channels                                |

|            | (1)               | I/O interface mode                                                 |

|            |                   | Universal asynchronous receiver transmitter (UART) mode            |

|            | (8)               | Serial expansion interface (SEI) : 1 channel                       |

|            |                   | Baud rate 4/2/0.5Mbps at fc=20MHz.                                 |

|            | (9)               | Serial bus interface (SBI) : 3 channels                            |

|            | (0)               | Clocked-synchronous 8-bit serial interface mode                    |

|            |                   | I <sup>2</sup> C bus mode                                          |

|            | (10)              | CAN controller : 1channel                                          |

|            |                   | Supports CAN version 2.0B.                                         |

|            |                   | 16 mailboxes                                                       |

|            | (11)              | 10-bit A/D converter (ADC) : 12 channels                           |

|            |                   | A/D conversion time 8µsec @fc=20MHz.                               |

|            |                   | Total tolerance +/- 3LSB (excluding quantization error)            |

|            |                   | Scan mode for all 12channels                                       |

|            |                   | Watch dog timer (WDT)                                              |

|            | (13)              | Timer for real-time clock (RTC)                                    |

|            |                   | Can operate with only low frequency oscillator.                    |

|            | (14)              | Interrupt controller (INTC) : 60 interrupt sources                 |

|            |                   | 9 interrupts from CPU                                              |

|            |                   | 42 internal interrupt vectors                                      |

|            |                   | 9 external interrupt vectors                                       |

|            |                   | I/O Port: 68pins                                                   |

|            | (16)              | Standby mode                                                       |

|            |                   | Four modes : IDLE3, IDLE2, IDLE1 and STOP                          |

|            | $( \rightarrow )$ | STOP mode can be released by 9 external inputs.                    |

|            | (17)              | Internal voltage detection flag (RAMSTB)                           |

# TOSHIBA

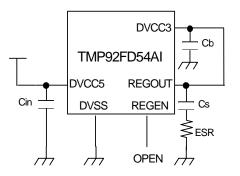

- (18) Power supply voltage

- VCC5 = 4.5V to 5.25V

VCC3 = 3.3V (VCC3 Connect to REGOUT; built-in voltage regulator.)

- (19) Operating temperature : -40 to 85 degree C

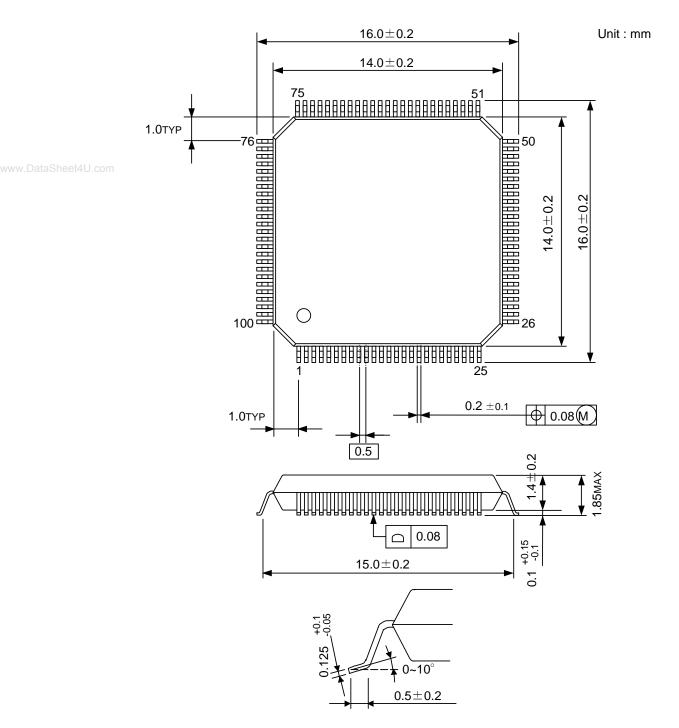

- (20) Package: P-LQFP100-1414-0.50C

Figure 1 TMP92FD54AI block diagram

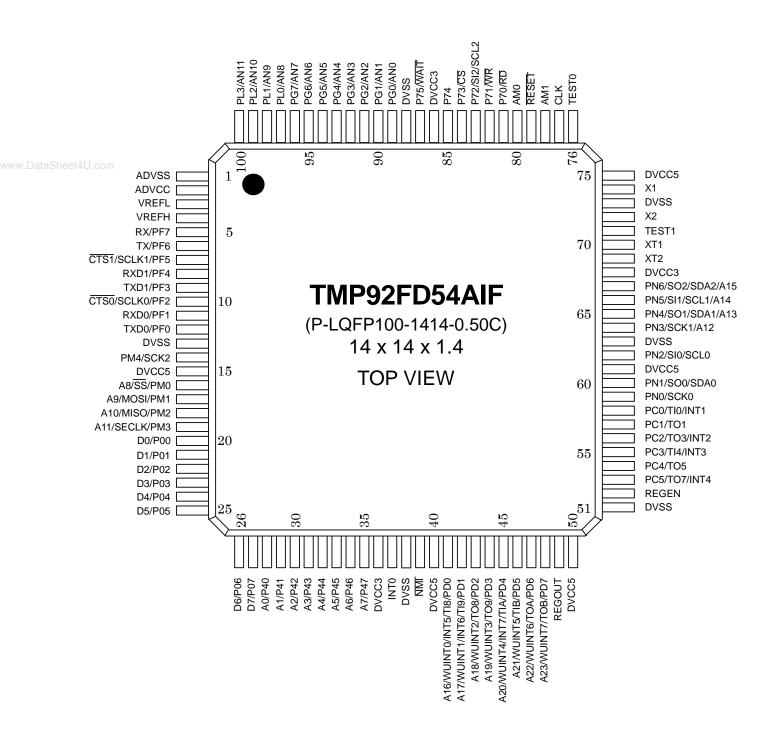

# 2. Pin Assignment and Functions

2.1 Pin Assignment

### 2.2 Pin names and functions

The following table shows the names and functions of the input/output pins.

| Pin name                                           | Pin<br>number                     | Number of pins    | In/Out                          | Function                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------|-----------------------------------|-------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00P07<br>D0D7                                     | 20 <sup>th</sup> 27 <sup>th</sup> | 8 (CMOS)<br>(TTL) | in/out<br>in/out                | Port 0: I/O port. Input or output specifiable in units of bits.<br>Data: Data bus 0 to 7.                                                                                                                                                                                                                                                                                    |

| P40P47<br>A0A7                                     | 28 <sup>th</sup> 35 <sup>th</sup> | 8                 | in/out<br>out                   | Port4: I/O port. Input or output specifiable in units of bits.<br>Address: Address bus 0 to 7.                                                                                                                                                                                                                                                                               |

| $\frac{P70}{RD}$                                   | $81^{\rm st}$                     | 1                 | in/out<br>out                   | Port70: I/O port.<br>Read: Outputs strobe signal to read external memory.                                                                                                                                                                                                                                                                                                    |

| P71                                                | 82 <sup>nd</sup>                  | 1                 | in/out<br>out                   | Port 71: I/O port.<br>Write: Output strobe signal to write external memory.                                                                                                                                                                                                                                                                                                  |

| WR<br>P72<br>SI2                                   | 83 <sup>rd</sup>                  | 1                 | in/out                          | Port 72: I/O port.<br>SBI channel 2: Input data at SIO mode                                                                                                                                                                                                                                                                                                                  |

| $\frac{\text{SCL2}}{\frac{\text{P73}}{\text{CS}}}$ | 84 <sup>th</sup>                  | 1                 | in/out<br>out                   | SBI channel 2: Clock input/output at I <sup>2</sup> C mode<br>Port 73: I/O port.<br>Chip select: Outputs "low" if address is within specified address area.                                                                                                                                                                                                                  |

| P74                                                | $85^{\text{th}}$                  | 1                 | in/out                          | Port 74: I/O port.                                                                                                                                                                                                                                                                                                                                                           |

| $\frac{P75}{WAIT}$                                 | $87^{\mathrm{th}}$                | 1                 | in/out<br>in                    | Port 75: I/O port.<br>Wait: Signal used to request CPU bus wait.                                                                                                                                                                                                                                                                                                             |

| PC0<br>TI0<br>INT1                                 | $58^{\mathrm{th}}$                | 1                 | in/out<br>in<br>in              | Port C0: I/O port.<br>Timer input 0: Input pin for timer 0.<br>Interrupt request pin 1: Rising-edge interrupt request pin.                                                                                                                                                                                                                                                   |

| PC1<br>TO1                                         | $57^{\mathrm{th}}$                | 1                 | in/out<br>out                   | Port C1: I/O port.<br>Timer output 1: Output pin for timer 1.                                                                                                                                                                                                                                                                                                                |

| PC2<br>TO3<br>INT2                                 | $56^{\mathrm{th}}$                | 1                 | in/out<br>out<br>in             | Port C2: I/O port.<br>Timer output 3: Output pin for timer 3.<br>Interrupt request pin 2: Rising-edge interrupt request pin.                                                                                                                                                                                                                                                 |

| PC3<br>TI4<br>INT3                                 | $55^{\mathrm{th}}$                | 1                 | in/out<br>in<br>in              | Port C3: I/O port.<br>Timer input 4: Input pin for timer 4.<br>Interrupt request pin 3: Rising-edge interrupt request pin.                                                                                                                                                                                                                                                   |

| PC4<br>TO5                                         | $54^{\mathrm{th}}$                | 1                 | in/out<br>out                   | Port C4: I/O port.<br>Timer output 5: Output pin for timer 5.                                                                                                                                                                                                                                                                                                                |

| PC5<br>TO7<br>INT4                                 | $53^{ m rd}$                      | 1                 | in/out<br>out<br>in             | Port C5: I/O port.<br>Timer output 7: Output pin for timer 7.<br>Interrupt request pin 4: Rising-edge interrupt request pin.                                                                                                                                                                                                                                                 |

| PD0<br>TI8<br>INT5<br>A16                          | 41 <sup>st</sup>                  | 1                 | in/out<br>in<br>in<br>out       | Port D0: I/O port.<br>Timer input 8: Input pin for timer 8.<br>Interrupt request pin 5: Interrupt request pin with programmable rising/falling<br>edge.<br>Address: Address bus 16.                                                                                                                                                                                          |

| WUINTO<br>PD1<br>TI9<br>INT6<br>A17<br>WUINT1      | 42 <sup>nd</sup>                  | 1                 | in<br>in/out<br>in<br>out<br>in | Wake up input 0: Wake up request pin with programmable rising, falling or both falling and rising edge.<br>Port D1: I/O port.<br>Timer input 9: Input pin for timer 9.<br>Interrupt request pin 6: Rising-edge interrupt request pin.<br>Address: Address bus 17.<br>Wake up input 1: Wake up request pin with programmable rising, falling or both falling and rising edge. |

| PD2<br>TO8<br>A18<br>WUINT2                        | 43 <sup>rd</sup>                  | 1                 | in/out<br>out<br>out<br>in      | Port D2: I/O port.<br>Timer output 8: Output pin for timer 8<br>Address: Address bus 18.<br>Wake up input 2: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.                                                                                                                                                                       |

| PD3<br>TO9<br>A19<br>WUINT3                        | 44 <sup>th</sup>                  | 1                 | in/out<br>out<br>out<br>in      | Port D3: I/O port.<br>Timer output 9: Output pin for timer 9<br>Address: Address bus 19.<br>Wake up input 3: Wake up request pin with programmable rising, falling or both<br>falling and rising edge.                                                                                                                                                                       |

| Pin name                   | Pin<br>number                   | Number<br>of pins | In/Out           | Function                                                                              |

|----------------------------|---------------------------------|-------------------|------------------|---------------------------------------------------------------------------------------|

| PD4                        |                                 | •                 | in/out           | Port D4: I/O port.                                                                    |

| TIA                        |                                 |                   | in               | Timer input A: Input pin for timer A                                                  |

| INT7                       | $45^{\text{th}}$                | 1                 | in               | Interrupt request pin 7: Interrupt request pin with programmable rising/falling edge. |

| A20                        | 40                              | 1                 | out              | Address: Address bus 20.                                                              |

| WUINT4                     |                                 |                   | in               | Wake up input 4: Wake up request pin with programmable rising, falling or both        |

|                            |                                 |                   |                  | falling and rising edge.                                                              |

| PD5                        |                                 |                   | in/out           | Port D5: I/O port.                                                                    |

| TIB                        |                                 |                   | in               | Timer input B: Input pin for timer B. WUNT5 🖌 🗔 🦷                                     |

| A21                        | $46^{\text{th}}$                | 1                 | out              | Address: Address bus 21.                                                              |

| WUINT5                     |                                 |                   | in               | Wake up input 5: Wake up request pin with programmable rising, falling or both        |

| PD6                        |                                 |                   | in land          | falling and rising edge.                                                              |

| PD6<br>TOA                 |                                 |                   | in/out<br>out    | Port D6: I/O port.<br>Timer output A: Output pin for timer A.                         |

| A22                        | $47^{\text{th}}$                | 1                 | out              | Address: Address bus 22.                                                              |

| WUINT6                     | -17                             | T                 | in               | Wake up input 6 Wake up request pin with programmable rising, falling or both         |

|                            |                                 |                   |                  | falling and rising edge.                                                              |

| PD7                        |                                 |                   | in/out           | Port D7: I/O port.                                                                    |

| TOB                        |                                 |                   | out              | Timer output B: Output pin for timer B. WUNT7                                         |

| A23                        | $48^{\text{th}}$                | 1                 | out              | Address: Address bus 23.                                                              |

| WUINT7                     |                                 |                   | in               | Wake up input 7: Wake up request pin with programmable rising, falling or both        |

| PF0                        |                                 |                   | in land          | falling and rising edge.                                                              |

| TXD0                       | $12^{\text{th}}$                | 1                 | in/out<br>out    | Port F0: I/O port.<br>Serial interface channel 0: Transmission data.                  |

| PF1                        |                                 |                   | in/out           | Port F1: I/O port.                                                                    |

| RXD0                       | $11^{\text{th}}$                | 1                 | in               | Serial interface channel 0: Receive data.                                             |

| PF2                        |                                 |                   | in/out           | Port F2: I/O port.                                                                    |

| SCLK0                      | 10 <sup>th</sup>                | 1                 | in/out           | Serial interface channel 0: Clock input/output.                                       |

| $\overline{\mathrm{CTS0}}$ |                                 |                   | in               | Serial interface channel 0: Data ready to send. (Clear-to-send)                       |

| PF3                        | oth                             |                   | in/out           | Port F3: I/O port.                                                                    |

| TXD1                       | $9^{\text{th}}$                 | 1                 | out              | Serial interface channel 1: Transmission data.                                        |

| PF4                        | 8 <sup>th</sup>                 | 1                 | in/out           | Port F4: I/O port.                                                                    |

| RXD1                       | 0                               | Ŧ                 | in               | Serial interface channel 1: Receive data.                                             |

| PF5                        |                                 |                   | in/out           | Port F5: I/O port.                                                                    |

| SCLK1                      | $7^{ m th}$                     | 1                 | in/out           | Serial interface channel 1: Clock input/output.                                       |

| CTS1                       |                                 |                   | in               | Serial interface channel 1: Data ready to send. (Clear-to-send)                       |

| PF6                        | $6^{\text{th}}$                 | 1                 | in/out           | Port F6: I/O port.                                                                    |

| TX<br>DE7                  |                                 |                   | out              | CAN: Transmission data.                                                               |

| PF7<br>RX                  | $5^{\text{th}}$                 | 1                 | in/out<br>in     | Port F7: I/O port.<br>CAN: Receive data.                                              |

| PG0PG7                     |                                 |                   | in               | Port G: Input-only port.                                                              |

| AN0AN7                     | $89^{\text{th}}96^{\text{th}}$  | 8                 | in               | Analog input 0 to 7: AD converter input pins.                                         |

| PL0PL3                     |                                 |                   | in               | Port L0 to L3: Input-only port.                                                       |

|                            | $97^{\text{th}}100^{\text{th}}$ | 4                 | in               | Analog input 8 to 11: AD converter input pins.                                        |

| 1                          |                                 |                   |                  |                                                                                       |

| PM0                        |                                 |                   | in/out           | Port MO: I/O port.                                                                    |

| $\overline{SS}$            | $16^{\text{th}}$                | 1                 | in               | SEI: Slave select input.                                                              |

| A8                         |                                 |                   | out              | Address: Address bus 8.                                                               |

| PM1                        |                                 |                   | in/out           | Port M1: I/O port.                                                                    |

| MOSI                       | $17^{\text{th}}$                | 1                 | in/out           | SEI: Master output, slave input.                                                      |

| A9<br>PM2                  |                                 |                   | out              | Address: Address bus 9.<br>Port M2: I/O port.                                         |

| PM2<br>MISO                | $18^{\text{th}}$                | 1                 | in/out<br>in/out | SEI: Master input, slave output.                                                      |

| A10                        | 10                              | T                 | out              | Address: Address bus 10.                                                              |

| PM3                        |                                 |                   | in/out           | Port M3: I/O port.                                                                    |

| SECLK                      | $19^{\text{th}}$                | 1                 | in/out           | SEI: Clock input/output.                                                              |

| A11                        |                                 |                   | out              | Address: Address bus 11.                                                              |

| PM4                        | $14^{\text{th}}$                | 1                 | in/out           | Port M4: I/O port.                                                                    |

| SCK2                       | 14.                             | Ŧ                 | in/out           | SBI channel 2: Clock input/output at SIO mode.                                        |

| PN0                        | $59^{\text{th}}$                | 1                 | in/out           | Port N0: I/O port.                                                                    |

| SCK0                       |                                 |                   | in/out           | SBI channel 0: Clock input/output at SIO mode.                                        |

| Pin name    | Pin<br>number                                                                                                  | Number<br>of pins | In/Out        | Function                                                                                                                                                            |  |

|-------------|----------------------------------------------------------------------------------------------------------------|-------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PN1         |                                                                                                                |                   | in/out        | Port N1: I/O port.                                                                                                                                                  |  |

| SO0         | 60 <sup>th</sup>                                                                                               | 1                 | out           | SBI channel 0: Output data input/output at SIO mode                                                                                                                 |  |

| SDA0        |                                                                                                                | in/out            |               | SBI channel 0: Data input/output at I <sup>2</sup> C mode                                                                                                           |  |

| PN2         |                                                                                                                |                   | in/out        | Port N2: I/O port.                                                                                                                                                  |  |

| SI0         | 62 <sup>nd</sup>                                                                                               | 1                 | in            | SBI channel 0: Input data at SIO mode                                                                                                                               |  |

| SCL0        |                                                                                                                |                   | in/out        | SBI channel 0: Clock input/output at I <sup>2</sup> C mode                                                                                                          |  |

| PN3         | 0.4h                                                                                                           |                   | in/out        | Port N3: I/O port.                                                                                                                                                  |  |

| SCK1<br>A12 | $64^{\text{th}}$                                                                                               | 1                 | in/out        | SBI channel 1: Clock input/output at SIO mode                                                                                                                       |  |

| PN4         |                                                                                                                |                   | out<br>in/out | Address: Address bus 12.<br>Port N4: I/O port.                                                                                                                      |  |

| SO1         |                                                                                                                |                   | out           | SBI channel 1: Output data at SIO mode                                                                                                                              |  |

| SDA1        | $65^{\text{th}}$                                                                                               | 1                 | in/out        | SBI channel 1: Data input/output at I <sup>2</sup> C mode                                                                                                           |  |

| A13         |                                                                                                                |                   | out           | Address: Address bus 13.                                                                                                                                            |  |

| PN5         |                                                                                                                |                   | in/out        | Port N5: I/O port.                                                                                                                                                  |  |

| SI1         | aath                                                                                                           |                   | in            | SBI channel 1: Input data at SIO mode                                                                                                                               |  |

| SCL1        | $66^{\text{th}}$                                                                                               | 1                 | in/out        | SBI channel 1: Clock input/output at I <sup>2</sup> C mode                                                                                                          |  |

| A14         |                                                                                                                |                   | out           | Address: Address bus 14                                                                                                                                             |  |

| PN6         |                                                                                                                |                   |               | Port N6: I/O port.                                                                                                                                                  |  |

| SO2         | $67^{\mathrm{th}}$                                                                                             | 1                 | in/out        | SBI channel 2: Output data at SIO mode                                                                                                                              |  |

| SDA2        | 01                                                                                                             | 1                 | out           | SBI channel 2: data input output at I2C mode                                                                                                                        |  |

| A15         |                                                                                                                |                   |               | Address: Address bus 15.                                                                                                                                            |  |

|             | oot                                                                                                            |                   |               | Non-maskable interrupt: Interrupt request pin with programmable falling or both                                                                                     |  |

| NMI         | $39^{\text{th}}$                                                                                               | 1                 | in            | falling and rising edge.                                                                                                                                            |  |

| INT0        | $37^{\mathrm{th}}$                                                                                             | 1                 | in            | Interrupt request pin 0: Interrupt request pin with programmable level or rising edge.                                                                              |  |

| AM0,1       | 80 <sup>th</sup> , 78 <sup>th</sup>                                                                            | 2                 | in            | Address mode pins: These pins are set as following,         (Single-Chip mode)       AM0 = L,       AM1 = H         (Single-Boot mode)       AM0 = H,       AM1 = H |  |

| TEST0,1     | 76 <sup>th</sup> , 71 <sup>st</sup>                                                                            | 2                 | in            | Test mode pins: These pins are set as following,<br>(Single Chip & Single Boot mode) TEST0 = L, TEST1 = L                                                           |  |

| CLK         | $77^{\text{th}}$                                                                                               | 1                 | out           | Programmable clock output (with pull-up register).                                                                                                                  |  |

| X1/X2       | $74^{\rm th}, 72^{\rm nd}$                                                                                     | 2                 | in/out        | Oscillator connecting pins                                                                                                                                          |  |

| XT1/XT2     | $70^{\text{th}}, 69^{\text{th}}$                                                                               | 2                 | in/out        | Low frequency oscillator connecting pins. Crystal or ceramic resonator is connected. RC oscillation is also possible depending on MASK option.                      |  |

| RESET       | $79^{\text{th}}$                                                                                               | 1                 | in            | Reset: Initializes LSI (with pull-up register).                                                                                                                     |  |

| VREFH       | 4 <sup>th</sup>                                                                                                | 1                 | in            | AD reference voltage high                                                                                                                                           |  |

| VREFL       | $3^{rd}$                                                                                                       | 1                 | in            | AD reference voltage low                                                                                                                                            |  |

| ADVCC       | $2^{nd}$                                                                                                       | 1                 | -             | Power supply pin for AD converter (+5V): Connect ADVCC pin to 5V power supply.                                                                                      |  |

| ADVSS       | $1^{st}$                                                                                                       | 1                 | -             | GND pin for AD converter: Connect ADVSS pin to GND (0V).                                                                                                            |  |

| DVCC5       | 15 <sup>th</sup> , 40 <sup>th</sup> ,<br>50 <sup>th</sup> ,61 <sup>st</sup> ,75 <sup>th</sup>                  | 5                 | -             | Power supply pins (+5V): Connect all DVCC5 pins to 5V power supply.                                                                                                 |  |

| DVCC3       | 36 <sup>th</sup> ,68 <sup>th</sup> ,86 <sup>th</sup>                                                           | 3                 | -             | Power supply pins (+3.3V): Connect all DVCC3 pins to REGOUT pin.                                                                                                    |  |

| DVSS        | 13 <sup>th</sup> ,38 <sup>th</sup> ,51 <sup>st</sup> ,<br>63 <sup>rd</sup> ,73 <sup>rd</sup> ,88 <sup>th</sup> | 6                 | -             | GND: Connect all DVSS pins to GND (0V).                                                                                                                             |  |

| REGOUT      | $49^{\text{th}}$                                                                                               | 1                 | out           | Regulator output 3.3V: Connect capacitor to stabilize the regulator output.                                                                                         |  |

| L           |                                                                                                                |                   |               |                                                                                                                                                                     |  |

# TOSHIBA

# 3. OPERATION

This section describes the basic components, functions and operation of TMP92FD54AI.

### 3.1 CPU

TMP92FD54AI contains an advanced high-speed 32-bit CPU (900/H1 CPU)

#### 3.1.1 CPU Outline

900/H1 CPU is high-speed and high-performance CPU based on 900/H CPU. 900/H1 CPU has expanded 32-bit internal data bus to process Instructions more quickly.

Outline of 900/H1 CPU are as follows:

|                                  | 900/H1 CPU                              |                  |  |  |

|----------------------------------|-----------------------------------------|------------------|--|--|

| Width of CPU Address Bus         | 24-bit                                  |                  |  |  |

| Width of CPU Data Bus            | 32-bit                                  |                  |  |  |

| Internal Operating Frequency     | 16 to 20MHz (@fosc=8 to 10M             | (Hz)             |  |  |

| Minimum Bus Cycle (Internal RAM) | 1-clock access (50ns@fosc=10            | MHz)             |  |  |

| Internal RAM                     | 32-bit 1-clock access                   |                  |  |  |

| Internal ROM                     | 32-bit interleave 2-1-1-1-cloc          | k access         |  |  |

| Internal I/O                     | 8/16-bit 2-clock access                 | PORT, INTC,      |  |  |

|                                  |                                         | MEMC             |  |  |

|                                  | 8/16-bit 5 to 6-clock access            | SEI, SIO, WDT,   |  |  |

|                                  |                                         | 8-bit Timer,     |  |  |

|                                  |                                         | 16-bit Timer,    |  |  |

|                                  |                                         | RTC, 10-bit ADC, |  |  |

|                                  |                                         | SBI, CAN         |  |  |

| External Device                  | 8-bit 2-clock access (can inse          | ert some waits)  |  |  |

| Minimum Instruction              | 1-clock(50ns@fosc=10MHz)                |                  |  |  |

| Execution Cycle                  |                                         |                  |  |  |

| Conditional Jump                 | 2-clock(100ns@fosc=10MHz)               |                  |  |  |

| Instruction Queue Buffer         | 12-byte                                 |                  |  |  |

| Instruction Set                  | Compatible with TLCS-900, 900/H, 900/L, |                  |  |  |

|                                  | 900/L1 and 900/H2 (NORMA                | AL, MIN, MAX and |  |  |

|                                  | LDX instruction is deleted)             |                  |  |  |

| Micro DMA                        | 8-channels                              |                  |  |  |

# 4. Functional Description

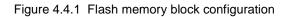

This section describes the hardware configuration of the TMP92FD54AI and how it operates. This device is a modified version of the TMP92CD54I with an internal 512K-byte flash memory instead of an internal 512K-byte Mask ROM. These internal RAM are same size, 32K-byte. In all other respects the hardware configuration and the functionality of the TMP92FD54AI are identical to those of the TMP92CD54I.

## 4.1 Flash Memory

www.DataSheet4U.com

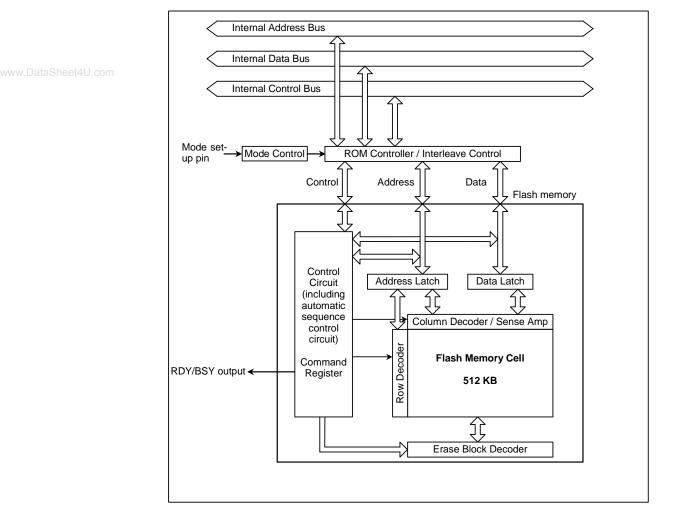

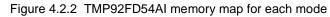

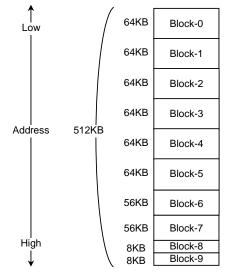

1) Memory capacity

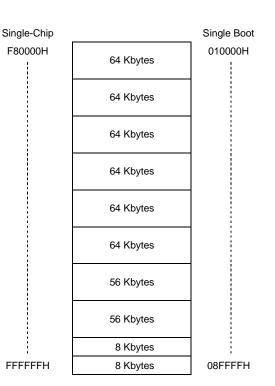

TMP92FD54AI contains a 4-Mbit (512K-byte) flash memory. This flash memory consists of 10 blocks (64 K-bytes  $\times$  6 blocks, 56 K-bytes  $\times$  2 blocks, 8 K-bytes  $\times$  2 blocks), each of which can be independently protected from being programmed or erased. The CPU accesses the flash memory using a 32-bit wide data bus. A writer rewrites the flash memory in units of 16 bits.

- 2) Flash memory access Interleaved access (2-1-1-1-clock access)

- 3) Program/erase time Programming time (including Verify):6 seconds per chip (typ.) 30 µs per long word (typ.)

Erase time (including Verify)

12 seconds per chip (typ.)

Note: The above values are typical times and do not include data transfer time. The actual time per chip varies according to the method used by the user to perform rewriting.

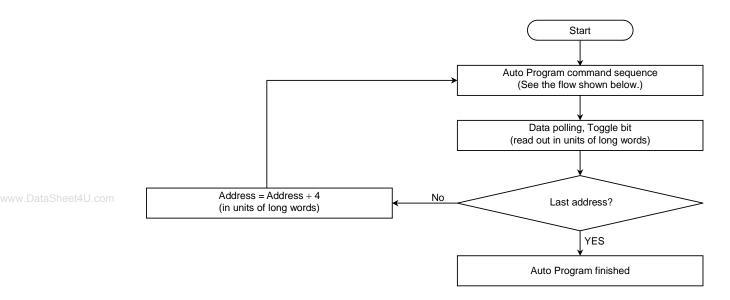

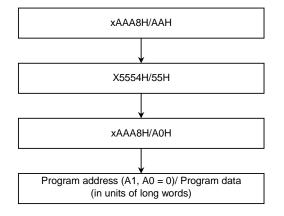

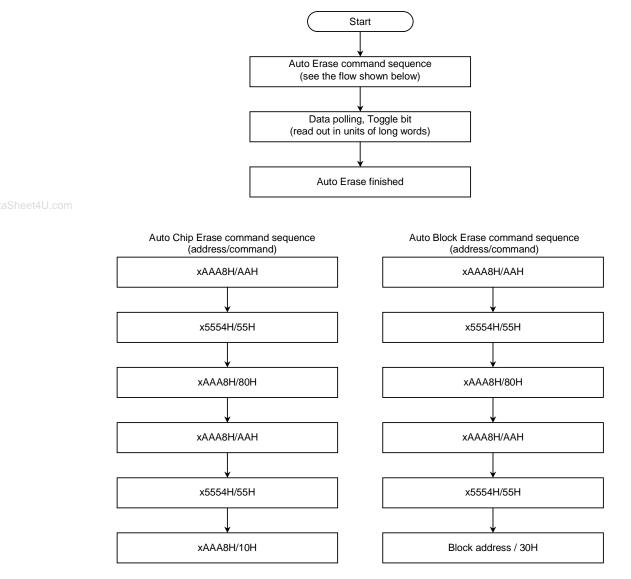

4) Programming methods

On-board programming mode, in which the memory can be rewritten while mounted on the user PCB.

- On-board programming mode 1) User Boot Mode Supports user-defined rewriting methods.

2) Single Boot Mode Supports rewriting by serial transfer (unique to Toshiba).

- 5) Rewriting method

With a few exceptions, the functions of the device's internal flash memory conform to JEDEC standards. Therefore, even if the user system uses flash memory as external memory, it can easily be adapted to use this LSI. Furthermore, since the device's flash memory has built-in circuits which can automatically write to the flash memory and erase the chip, the user does not have to code a program to perform the program and erase operations.

The Block Protect function, which inhibits writing to or erasing the flash memory, only supports software protection (i.e. protection by a command setting), and does not support hardware protection (i.e. protection by the application of a voltage of 12 V).

| JEDEC-based functions | Functions which have been changed, added or remove                                                                           |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

|                       | <changed> Block Protect (supports only software protection.)<br/><removed> Erase Resume/Suspend function</removed></changed> |  |  |

# 4.1.2 Block diagram of the flash unit

Figure 4.1.1 Block diagram of the flash unit

### 4.2 Operation Modes

TMP92FD54AI has three operation modes.

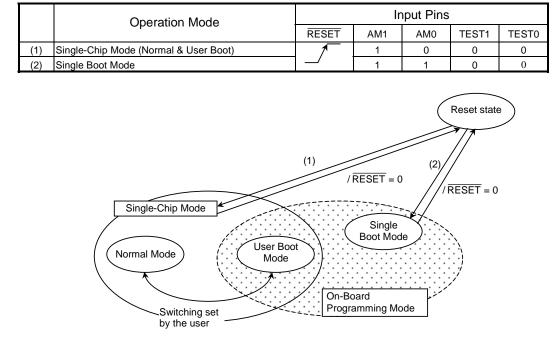

| Table 4.2.1 | Operation modes |

|-------------|-----------------|

|-------------|-----------------|

| Operation Mode Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <u>Single-Chip Mode</u> | After a reset the device restarts from the internal flash memory.<br>Single-Chip Mode is further sub-divided into the following two modes: Normal Mode and User Boot Mode.<br>The means for selecting between these two modes can be set by the user as desired. For example, it can<br>be set so that if Port $00 = 1$ , Normal Mode is selected, and if Port $00 = 0$ , User Boot Mode is selected. The<br>user application program must in corporate a routine to handle mode switching. |  |  |  |  |

| Normal Mode             | The user's application program is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| User Boot Mode          | The flash memory on the user PCB board is rewritten.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Single Boot Mode        | After a Reset the device starts up from the internal boot ROM (the mask ROM). The boot ROM has an<br>algorithm which allows memory on the user PCB to be rewritten via the device's serial port. The internal<br>flash memory can be rewritten by connecting the PCB to the external host via TMP92FD54AI's serial port<br>and transferring data using TMP92FD54AI data transfer protocol.                                                                                                  |  |  |  |  |

Of the modes listed in the table above, there are two operation modes in which the flash memory can be programmed: User Boot Mode and Single Boot Mode.

At User Boot Mode (in Single-Chip mode) and Single Boot Mode, the internal flash memory can be rewritten while mounted on the user PCB. These two modes are collectively referred to as On-Board Programming Mode.

The input pin levels on AM0, AM1, TEST0 and TEST1, which are set externally during a Reset, determine the operation mode - either Single-Chip Mode, Single-Boot Mode.

For all operation modes, the CPU will start operating in the selected mode on completion of the reset. The input pin levels are set before the reset is completed. Once the mode has been set, make sure that the input pin levels do not change during operation. The following table shows how each operation mode is set. The state diagram beneath the table shows the various possible mode transitions.

Table 4.2.2 Operation mode pin settings

Numbers in ( ) indicate the column row in the above table in which the input pin levels for the mode setting are shown.

Figure 4.2.1 Mode transition diagram

#### 4.2.1 Reset operation

To reset the device, hold the  $\overline{\text{RESET}}$  input Low (= 0) for at least 20 system clock periods while the power supply voltage is within the rated operating range and the internal high-frequency oscillator is oscillating stably. When the device is operating at 20 MHz, this period will by equal to 4 µs. For details please refer to the section entitled Reset Operation in TMP92CD54I User's Manual.

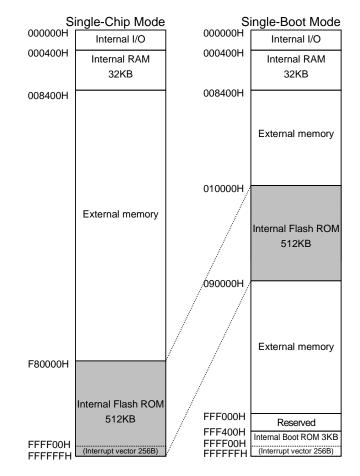

#### 4.2.2 Memory map for each mode

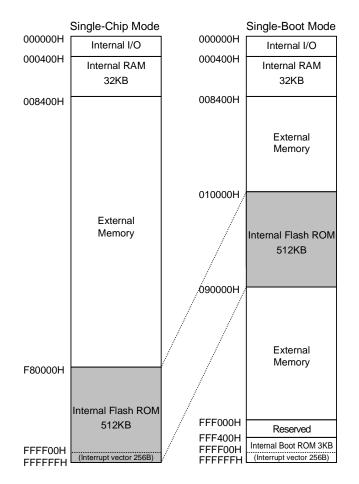

The memory map for the device varies according to the operation mode. The following diagram shows the memory map for each operation mode.

Figure 4.2.3 Block allocation

|         |         | Single-Chip Mode   | Single-Boot Mode   |

|---------|---------|--------------------|--------------------|

| Block-0 | (64 KB) | F80000H to F8FFFFH | 010000H to 01FFFFH |

| Block-1 | (64 KB) | F90000H to F9FFFFH | 020000H to 02FFFFH |

| Block-2 | (64 KB) | FA0000H to FAFFFFH | 030000H to 03FFFFH |

| Block-3 | (64 KB) | FB0000H to FBFFFFH | 040000H to 04FFFFH |

| Block-4 | (64 KB) | FC0000H to FCFFFH  | 050000H to 05FFFFH |

| Block-5 | (64 KB) | FD0000H to FDFFFFH | 060000H to 06FFFFH |

| Block-6 | (56 KB) | FE0000H to FEDFFFH | 070000H to 07DFFFH |

| Block-7 | (56 KB) | FEE000H to FFBFFFH | 07E000H to 08BFFFH |

| Block-8 | ( 8 KB) | FFC000H to FFDFFFH | 08C000H to 08DFFFH |

| Block-9 | ( 8 KB) | FFE000H to FFFFFH  | 08E000H to 08FFFFH |

| Table 4.2.3 | Block | address | range | by | mode |

|-------------|-------|---------|-------|----|------|

|-------------|-------|---------|-------|----|------|

## 4.3 On-Board Programming Mode (User-Boot and Single-Boot)

On-board Programming Mode allows flash memory to be rewritten while it is mounted on the user's target system board. There are two versions of this mode: Single Boot Mode, which supports the Toshiba proprietary method of rewriting via serial I/O, and User Boot Mode (in Single-Chip mode), which allows user-defined rewriting methods to be defined in Single-Chip Mode.

### 4.3.1 User Boot Mode (in Single-Chip Mode)

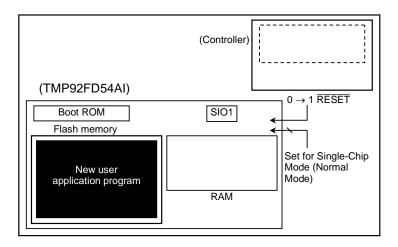

User Boot Mode enables a user-defined flash memory rewrite routine to be used. This mode is used when the data transfer bus which the user application flash memory rewrite program uses is not serial. Rewriting is performed in Single-Chip Mode. For this reason the operation mode within Single-Chip Mode must be changed, from Normal Mode (the mode in which the user application program normally operates) to User Boot Mode, in which mode the flash memory can be rewritten. This requires that a condition-judging program be incorporated into the user application reset-processing program.

Any mode-switching condition may be set using the device's I/Os as long as it is suitable for the user system. Also, the user's exclusive flash memory rewrite routine, for use in User Boot Mode, may be programmed into the user application in advance, so that it can be used to rewrite the flash memory after the device has entered User Boot Mode. Furthermore, since the processor cannot read data from the internal flash memory during an erase/program operation, the rewrite routine must be stored somewhere outside the flash memory so that it can be executed. While the on-chip flash memory is being rewritten in User Boot mode, all interrupts including the non-maskable interrupt must be disabled.

The pages which follow explain the procedure for rewriting the flash memory using two example case studies. In one case the rewrite routine is put into the internal flash memory (1-A); in the other the rewrite routine is transferred from an external source (1-B). For details of how to program/erase the flash memory, refer to Section 4.4, Programming/Erasing Flash Memory during on-Board Programming.

#### **User Boot Mode**

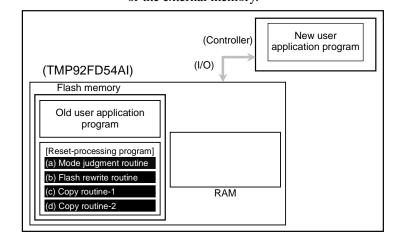

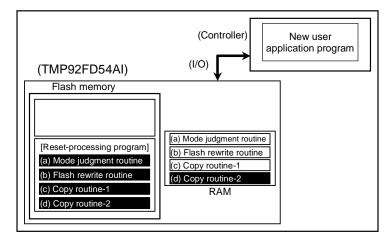

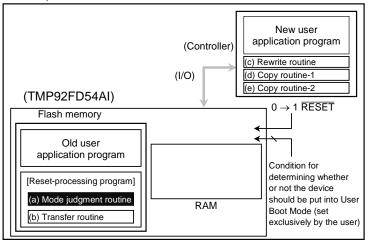

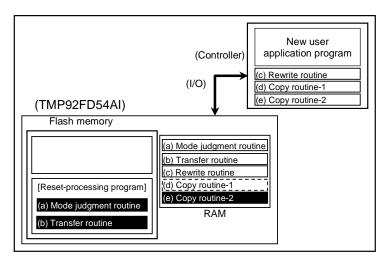

(1-A) Example procedure in which the rewrite routine is stored in the internal flash memory

#### (Step 1)

First, the conditions (e.g. the pin status) under which the program will enter User Boot Mode must be set and the I/O bus which the program will use to transfer data must be selected. Then a circuit must be designed and a corresponding program written. Before mounting this device on the board, the following four programs must be written into one of the blocks of the flash memory using a programmer or similar device.

- (a) Mode judgment routine: code to determine when rewriting of the device will commence

- (b) Flash rewrite routine: code to read the rewrite data from an external source and then rewrite the flash memory

- (c) Copy routine-1: code to copy (a) to (d) into the internal RAM or to external memory

- (d) Copy routine-2: code to copy (a) to (d) to the flash memory from the internal RAM or the external memory.

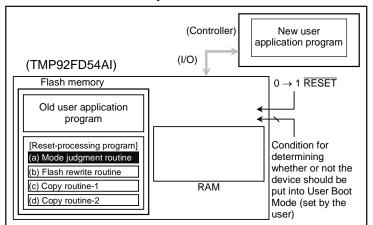

#### (Step 2)

The following explanation of the proceeding step assumes that the routines described above have been included in the Reset-processing program.

After a Reset the Reset-processing program must first determine whether or not the device should enter User Boot Mode. If the condition for entering User Boot Mode is true, the program must put the device into User Boot Mode, the mode in which the flash memory can be rewritten. (Once the device has entered User Boot Mode, no interrupts — not even NMIs — should be used.)

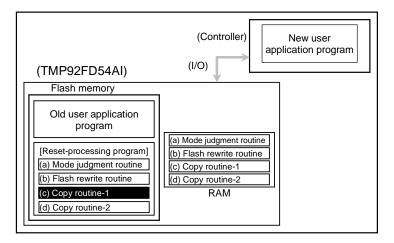

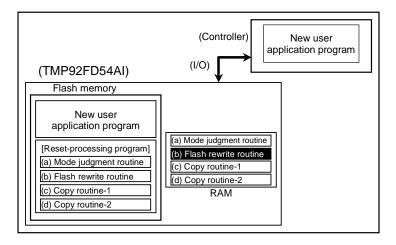

#### (Step 3)

After the device has entered User Boot Mode, (c), the copy routine, must copy (a) to (d), the flash rewrite routine, into the internal RAM or into external memory. (In the example shown below the routine is copied into the internal RAM.)

vw.DataSheet4U.com

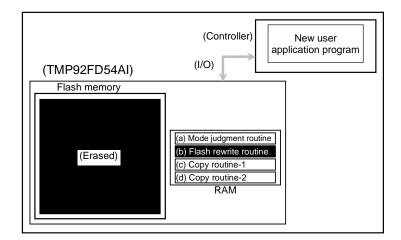

## (Step 4)

The program jumps to the rewrite routine in RAM, erases all blocks (chip-erase).

### (Step 5)

The copy routine-2 in the RAM is executed and writes (a) to (d) into the flash memory.

vw.DataSheet4U.com

### (Step 6)

Next, the rewrite routine in the RAM is executed and writes the new user application program into the erased area of the flash memory after loading it from the source of transfer (the controller).

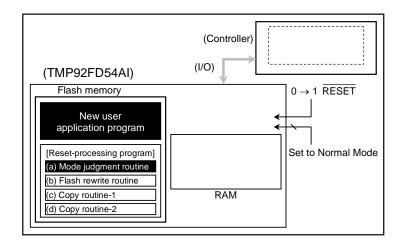

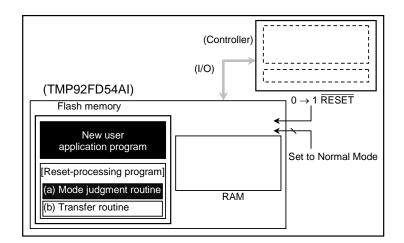

## (Step 7)

The  $\overline{\text{RESET}}$  input pin must be driven Low (= 0) to reset the device and to set it to Normal Mode. After de-assertion of the reset, the processor will start running the new user application program.

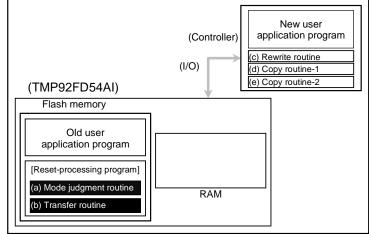

(1-B) Example procedure for when the rewrite routine is transferred from an external source.

(Step 1)

First, the condition (e.g. the pin status) under which the program will enter User Boot Mode must be set and the I/O bus which the program will use to transfer data must be selected. Then a circuit must be designed and a corresponding program written. Before mounting this device on the board, the following two programs must be written into one of the blocks of the flash memory using a programmer or similar device.

- (a) Mode judgment routine: Code to determine when rewriting of the device will commence

- (b) Transfer routine: Program for reading the rewrite program from an external source

In addition, the programs shown below should be present in the host:

- (c) Rewrite routine: Program for rewriting the flash memory

- (d) Copy routine-1: Code to copy (a) to (d) into the internal RAM or to the external ROM.

- (e) Copy routine-2

- Code to copy (a) to (d) into the flash memory from the internal RAM or the external ROM

(Step 2)

The following explanation of the proceeding step assumes that the routines described above have been included in the Reset processing program. After reset the Reset-processing program must first determine whether or not the device should enter User Boot Mode. If the condition for entering User Boot Mode is true, the program must put the device into User Boot Mode, the mode in which to the flash memory can be rewritten. (Once the device has entered User Boot Mode, no interrupts — not even NMIs — should be used.)

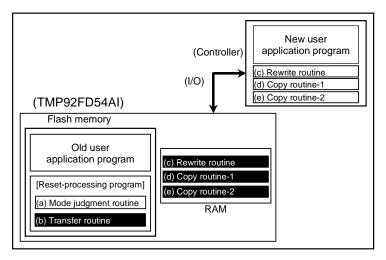

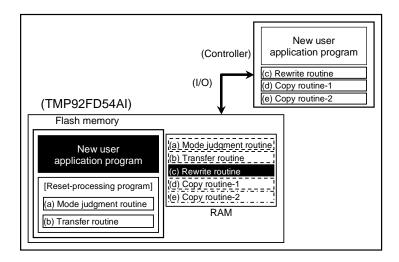

#### (*Step 3*)

After the device has entered User Boot Mode, (c) Rewrite routine, (d) Copy routine-1 and (e) Copy routine-2, must be loaded from the source of transfer (the controller) into the internal RAM or into external memory using (b), the transfer routine. (In the example shown below the routine is copied into the internal RAM.)

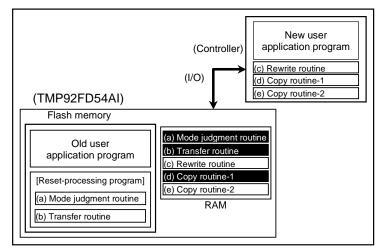

#### (Step 4)

The program jumps to the copy routine-1 in RAM, copy (a) and (b) into the internal RAM or into external memory. (In the example shown below the routine is copied into the internal RAM.).

# <u>TOSHIBA</u>

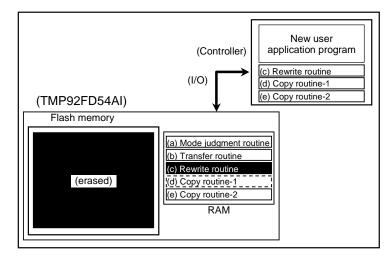

# (Step 5)

The rewrite routine in the RAM is executed, erase all block of the flash memory (Chip-erase).

vw.DataSheet4U.com

#### (Step 6)

The copy routine-2 in the RAM is executed, copy (a) and (b) into the flash memory.

### (Step 7)

Next, the rewrite routine in the RAM is executed and writes the new user application program into the erased area of the flash memory after loading it from the source of transfer (the controller).

ww.DataSheet4U.com

#### (Step 8)

The  $\overline{\text{RESET}}$  input pin must be driven Low (= 0) to reset the device and to set it to Normal Mode. After de-assertion of the reset, the processor will start running the new user application program.

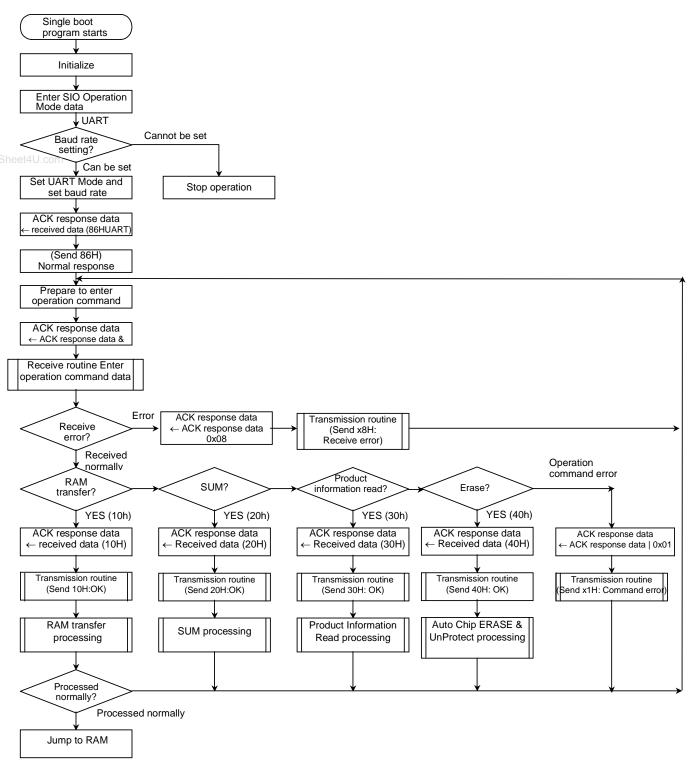

## 4.3.2 Single-Boot Mode

This mode involves activation of the internal boot ROM (mask ROM) so that the flash memory can be rewritten using a program stored in the boot ROM. In this mode the internal boot ROM is mapped into an area containing the interrupt vector table, in which the boot ROM program is executed. The flash memory is mapped into an address space different from the one into which the boot ROM is mapped (see Figure 4.2.2).

In Single-Boot Mode the flash memory is rewritten by serial transfer of commands and data.

First, the device's SIO (SIO1) and the external host are connected and the rewrite program is copied from the external host into the device's internal RAM; the rewrite program is then executed in RAM and the flash memory rewritten. The rewrite routine is initiated by sending commands and rewrite data from the host. The device must communicate with the host following the protocol described later. Before the program can be transferred into RAM, the user password is checked to ensure the security of the user ROM data. If the password does not match, the program is not transferred into RAM. Interrupts must be disabled when peripheral functions such as the SIO is utilized in Single Boot mode. Nonetheless, the code for an interrupt cause is recorded in the INTES1 register ; thus, for example, data receptions or transmissions in the SIO can be confirmed by keeping track of value changes of the INTES1 register. The NMI interrupt must be disabled at this time.

To prevent the contents of flash memory inadvertently rewritten in Single-Chip Mode (Normal Mode), it is recommended that, on completion of rewriting, write-protect be set for any blocks which the user wishes to protect. For details of how to program/erase the flash memory, please refer to Section 4.4, Programming/Erasing Flash Memory during On-Board Programming.

#### Single Boot Mode

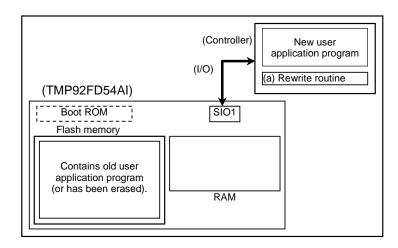

(2-A) Using the rewrite algorithm in the internal boot ROM

### (Step 1)

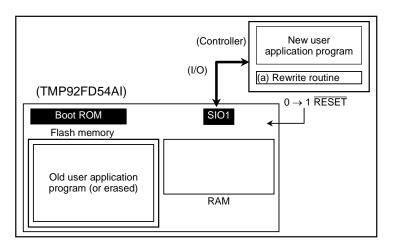

The state of the flash memory is not important; it may contain the old version of the user program or it may have been erased. Since the rewriting routine and rewrite data are transferred via SIO (SIO1), the device's SIO (SIO1) and the external controller should be connected on the board. The user must ensure that (a), the rewrite routine, is present on the controller.

### (Step 2)

To turn the boot ROM on, Reset must be de-asserted by setting the input pins accordingly. (a), the rewriting routine, must be transferred from the source (the controller) into the device via SIO. Before this is carried out, however, the password entered by the user must be checked against the password registered on the user application program. (When the flash memory has been erased, erase data ("0xFF"12byte) is used as the password.)

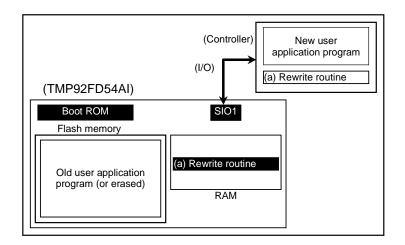

## (Step 3)

After the password has been checked, (a), the rewrite routine, must be transferred from the source (the controller). The boot ROM then loads the routine into the internal RAM. It must be ensured, however, that the routine is stored within the RAM address area 000400H to 006BFFH.

w.DataSheet4U.com

# (Step 4)

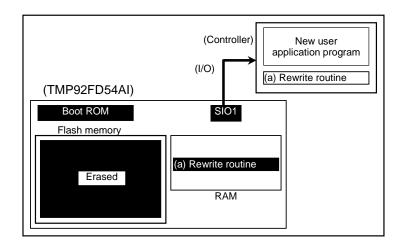

The CPU jumps to (a), the rewrite routine, in RAM and the rewrite routine erases the old user application program area (all the blocks at once).

## (Step 5)

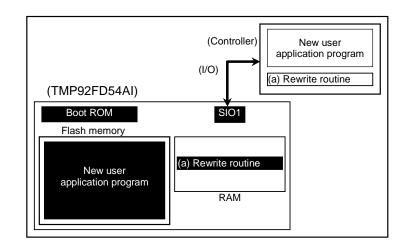

Next, the Rewrite routine in the RAM is executed and writes the new user application program into the erased area of the flash memory after loading it from the source of transfer (the controller). When the processor has finished writing the new user application program, write-protect for the user program area should be turn on.

In the example below the rewrite data is transferred from the same host via the same SIO as the rewrite routine. However, once normal program operation has started in RAM, any other data bus and any other transfer source may be used as desired. The user must design the board hardware and write the rewrite routine accordingly.

# (Step 6)

When writing to the device has been completed, turn the power to the board off and remove the cable connecting the device and host. To execute the new user application program, turn the power back on again and start the device in Single-Chip Mode (Normal Mode).

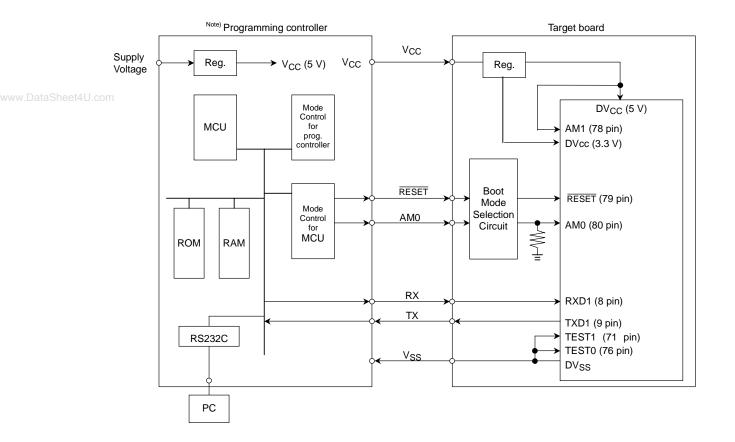

(1) Typical connection scheme for Single Boot Mode

In Single Boot Mode the flash memory is rewritten by means of a serial transfer. Therefore on-board programming is carried out by connecting the device's SIO (Channel1) and the controller (the programming tool) and sending commands from the controller to the target board. Figure 4.3.1 shows an example connection scheme for a programming controller and a target board.

Figure 4.3.1 Example of connection board and external controller in Single Boot Mode (with communication via UART)

#### (2) Mode settings

Before on-board programming can be performed, the device must be started up in Single Boot Mode. The input pins must be set as follows in order to start the device up in Single Boot Mode.

| AM0   | = 1                 |

|-------|---------------------|

| AM1   | = 1                 |

| TEST0 | = 0                 |

| TEST1 | = 0                 |

| RESET | $= 0 \rightarrow 1$ |

|       |                     |

ww.DataSheet4U.com

Set the  $\overline{\text{RESET}}$  input pin Low (= 0) and set the AM0, AM1, TEST0 and TEST1 pins as shown above. Then de-assert  $\overline{\text{RESET}}$  (i.e. set it to 1). The device will start up in Single Boot Mode.

#### (3) Memory map

Figure 4.3.2 compares the memory maps for Single-Chip Mode and Single-Boot Mode. As shown, in Single-Boot Mode the internal flash memory is mapped into 010000H to 08FFFFH. The boot ROM (mask ROM) is mapped into FFF400H to FFFFFFH.

Figure 4.3.2 Memory maps for Single-Chip Mode and Single-Boot Mode

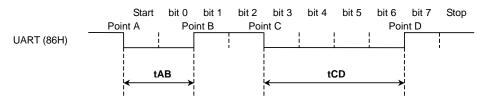

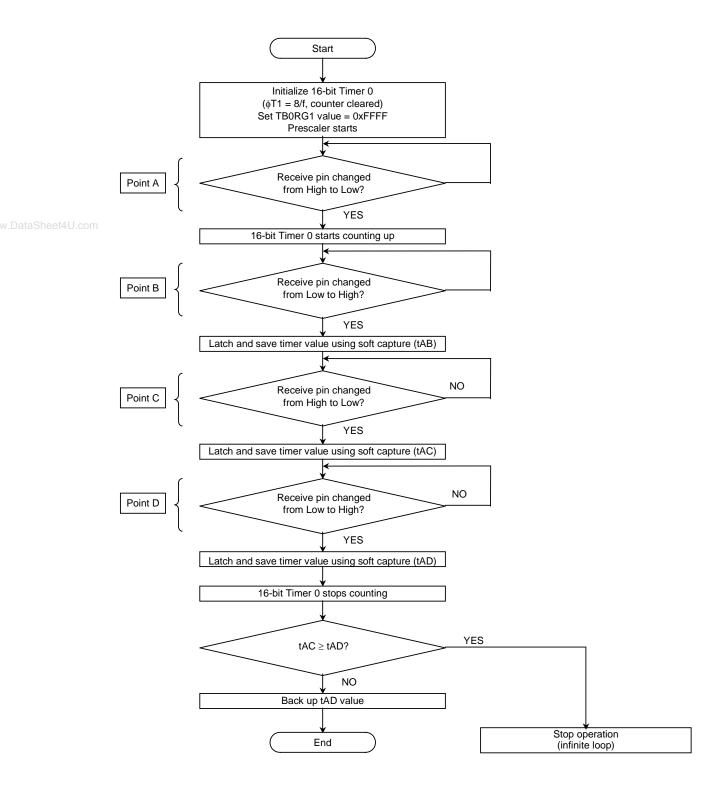

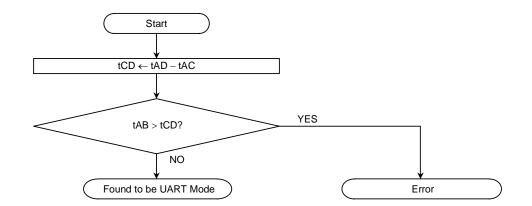

#### (4) Interface specifications

SIO communication specifications for Single Boot Mode are shown below. The device supports a serial operation mode: UART (Asynchronous). Before on-board programming can be executed, the programming controller must be set to the same communications format as the device side.

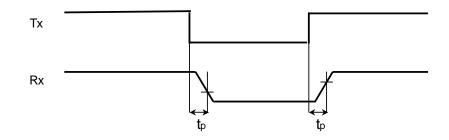

- Communicating in UART Mode

- Communications channel: SIO Channel1 Serial transfer mode: UART (Asynchronous) Mode, full-duplex communication Data length: 8 bits Parity bits: None STOP bits: 1 Baud rate: Desired baud rate (See Table 4.3.1(a))

www.DataSheet4U.com

| Tab             | Baud Rate Selection Table |       |      |      |      |

|-----------------|---------------------------|-------|------|------|------|

| Baud Rate (bps) | 38400                     | 19200 | 9600 | 4800 | 2400 |

| Pin                 | Pin                       |   |  |  |  |

|---------------------|---------------------------|---|--|--|--|

| Power supply pins   | DVCC (3.3 V)              | 0 |  |  |  |

|                     | DVSS                      | 0 |  |  |  |

| Mode-setting pin    | AM1, AM0,<br>TEST1, TEST0 | 0 |  |  |  |

| Reset pin           | RESET                     | 0 |  |  |  |

| Communications pins | TXD1                      | 0 |  |  |  |

|                     | RXD1                      | 0 |  |  |  |

Table 4.3.1(b) Pin connections

#### (5) Data transfer format

The operation commands and data transfer formats for each operation mode are shown in Table 4.3.2 to Table 4.3.67. For related information please refer to subsection (6), entitled *Boot program*, on page 37 of Section 4.3.2, *Single-Boot Mode*.

| Operation Command Data | Operation Mode              |

|------------------------|-----------------------------|

| 10H                    | RAM transfer                |

| 20H                    | Flash memory SUM            |

| 30H                    | Read product information    |

| 40H                    | Auto Chip Erase & UnProtect |

Table 4.3.2 Operation command data

|          | Number of<br>bytes<br>transferred | Data transferred from the<br>controller to the device           | Baud rate                                | Data transferred from the device to the controller                                                                                                                          |

|----------|-----------------------------------|-----------------------------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOOT ROM | 1st byte                          | Serial operation mode and baud rate<br>settings<br>For UART 86H | Desired baud<br>rate (Table<br>4.3.1(a)) | _                                                                                                                                                                           |

|          | 2nd byte                          | _                                                               |                                          | ACK response for Serial Operation Mode<br>For UART<br>If normal (can be set) 86H<br>(If the device determines that the baud<br>rate cannot be set, it will stop operating.) |

|          | 3rd byte                          | Operation command data (10H)                                    | [                                        | _                                                                                                                                                                           |

| im       | 4rth byte                         | _                                                               |                                          | ACK response for operation command *1<br>If normal 10H<br>If abnormal × 1H<br>If communications error occurs × 8H                                                           |

|          | 5th byte<br>∼                     | PASSWORD data (12 bytes)                                        |                                          | _                                                                                                                                                                           |

|          | 16th byte                         | (08FEF4H to 08FEFFH)                                            |                                          |                                                                                                                                                                             |

|          | 17th byte                         | CHECKSUM value for bytes 5 to 16                                |                                          |                                                                                                                                                                             |

|          | 18th byte                         |                                                                 |                                          | ACK response to CHECKSUM value *1<br>If normal 10H<br>If abnormal 11H<br>If communications error occurs 18H                                                                 |

|          | 19th byte                         | RAM storage start address 31 to 24                              |                                          | _                                                                                                                                                                           |

|          | 20th byte                         | RAM storage start address 23 to 16                              |                                          | _                                                                                                                                                                           |

|          | 21st byte                         | RAM storage start address 15 to 8                               |                                          | _                                                                                                                                                                           |

|          | 22nd byte                         | RAM storage start address 7 to 0                                |                                          | _                                                                                                                                                                           |

|          | 23rd byte                         | RAM storage bytes 15 to 8                                       |                                          | —                                                                                                                                                                           |

|          | 24th byte                         | RAM storage bytes 7 to 0                                        |                                          |                                                                                                                                                                             |

|          | 25th byte                         | CHECKSUM value for bytes 19 to 24                               |                                          |                                                                                                                                                                             |

|          | 26th byte                         | —                                                               |                                          | ACK response for CHECKSUM value *1<br>If normal 10H<br>If abnormal 11H<br>If communications error occurs 18H                                                                |

|          | 27th byte<br>~<br>mth byte        | RAM storage data                                                |                                          | _                                                                                                                                                                           |

|          | (m + 1) th byte                   | CHECKSUM value for bytes 27 to m                                |                                          |                                                                                                                                                                             |

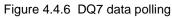

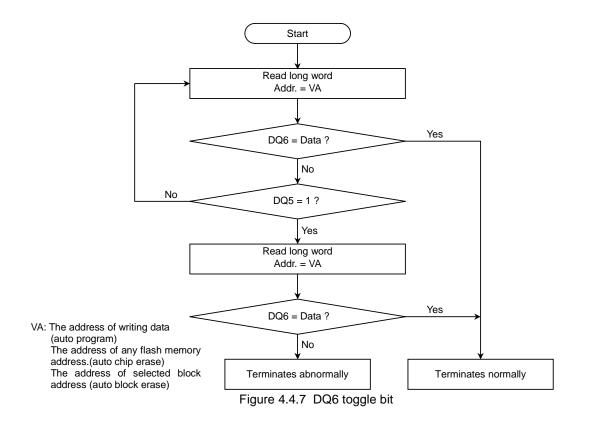

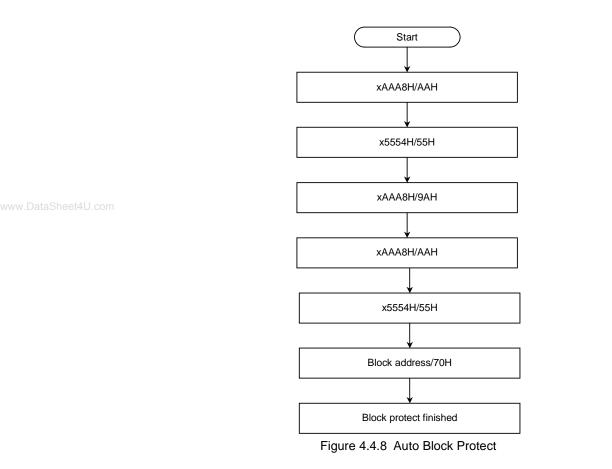

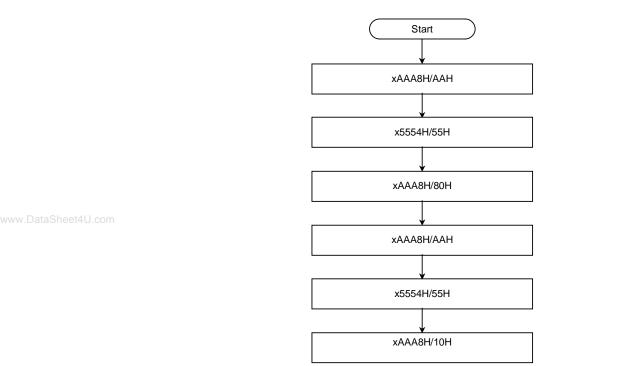

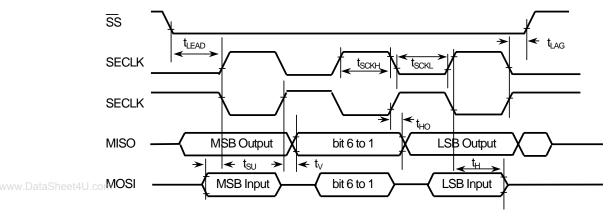

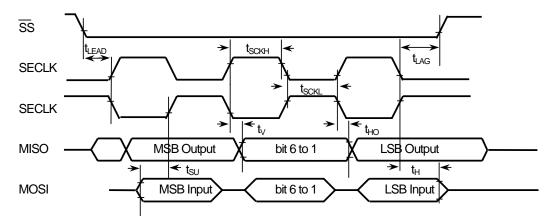

|          | (m + 2) th byte                   | _                                                               |                                          | ACK response for CHECKSUM value *1<br>If normal 10H<br>If abnormal 11H<br>If communications error occurs 18H                                                                |