# TOSHIBA

# TOSHIBA CORPORATION

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

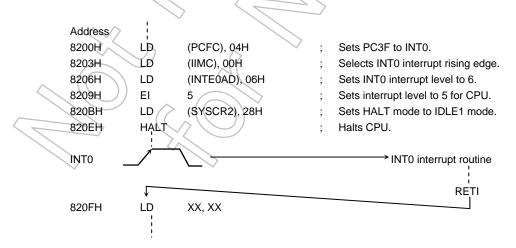

# \*\*CAUTION\*\* How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts = (INT0 to INT3, INTKEY, INTRTC, INTALM0 to INTALM4), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of  $f_{FPH}$ ) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# CMOS 32-bit Microcontrollers TMP92C820FG/JTMP92C820

# 1. Outline and Device Characteristics

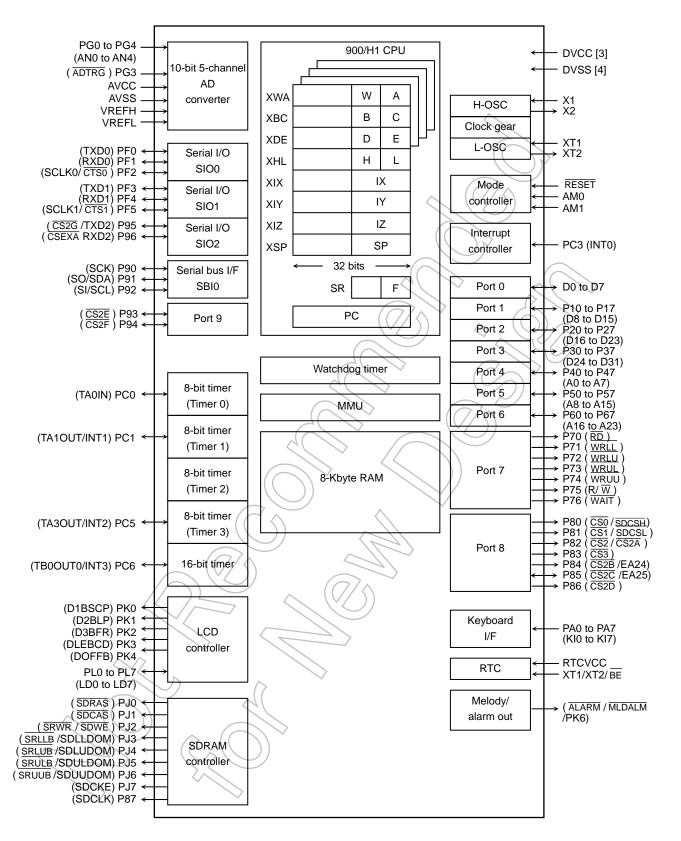

TMP92C820 is high-speed advanced 32-bit microcontroller developed for controlling equipment which processes mass data.

TMP92C820 is a microcontroller which has a high-performance CPU (900/H1 CPU) and various built-in I/Os. TMP92C820FG is housed in a 144-pin flat package. JTMP92C820 is a 144-pad chip product.

Device characteristics are as follows:

- (1) CPU: 32-bit CPU (900/H1 CPU)

- Compatible with TLCS-900, 900/L, 900/L1, 900/H's instruction code

- 16 Mbytes of linear address space

- General-purpose register and register banks

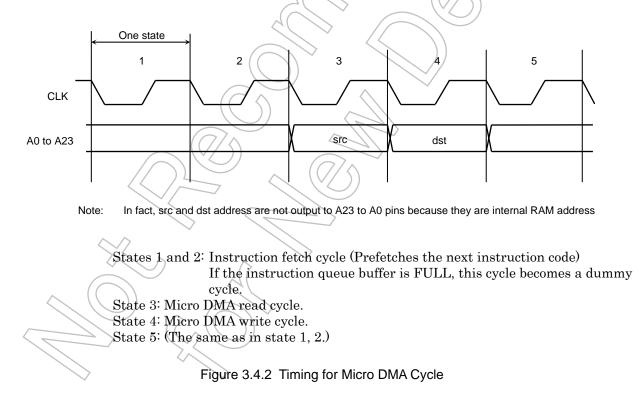

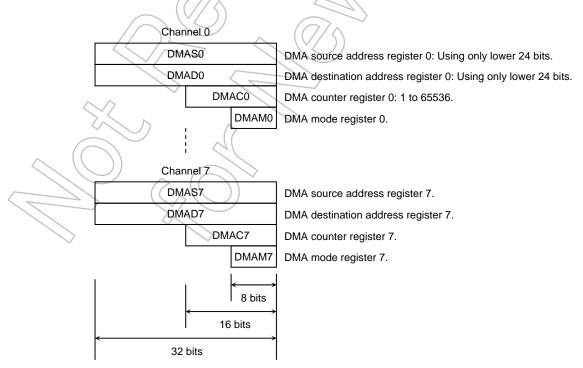

- Micro DMA: 8 channels (250 ns/4 bytes at fsys = 20 MHz, best case)

- (2) Minimum instruction execution time: 50 ns (at sys = 20 MHz)

# **RESTRICTIONS ON PRODUCT USE**

• The information contained herein is subject to change without notice. 021023\_D

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 021023\_C

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

2007-02-16

070208EBP

- (3) Internal memory

- Internal RAM: 8 Kbytes (can use for code section)

- Internal ROM: None

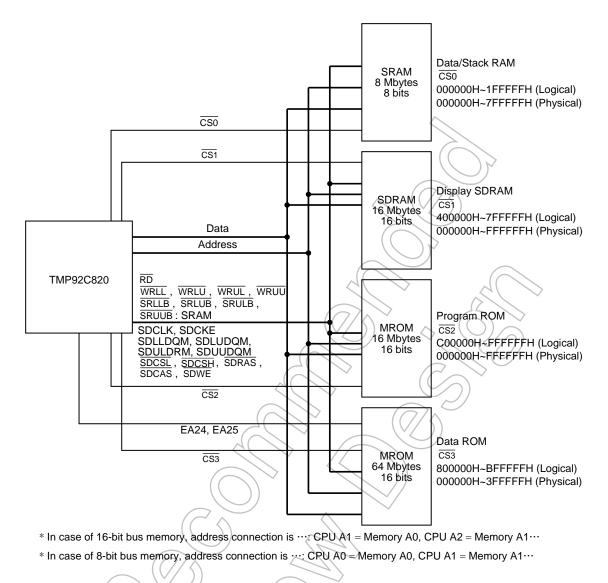

- (4) External memory expansion

- Expandable up to 136 Mbytes (Shared with program/data area)

- Can simultaneously support 8-/16-/32-bit width external data bus ..... Dynamic data bus sizing

- Separate bus system

- (5) Memory controller

- Chip select outputs: 4 channels

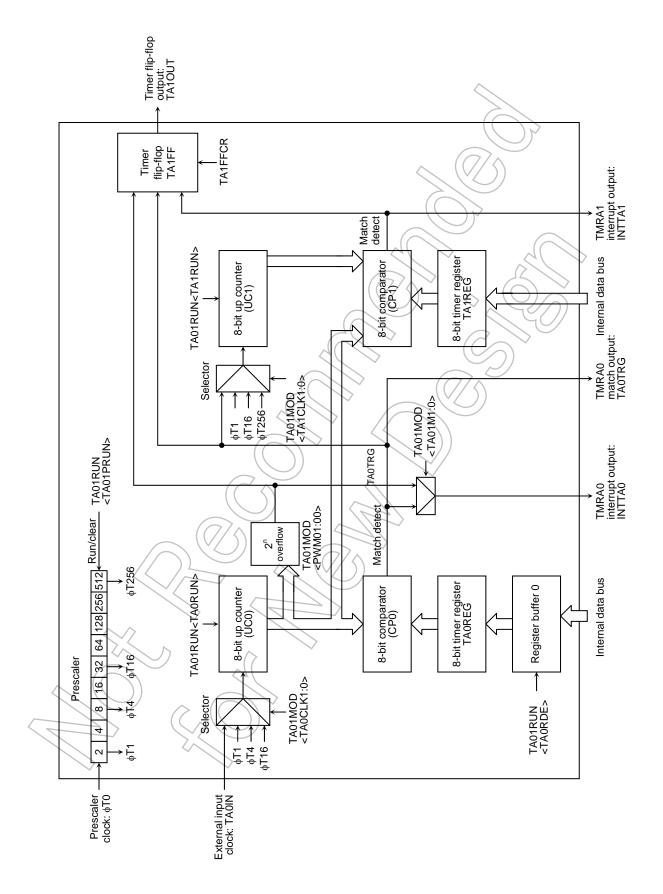

- (6) 8-bit timers: 4 channels

- (7) 16-bit timer/event counter: 1 channel

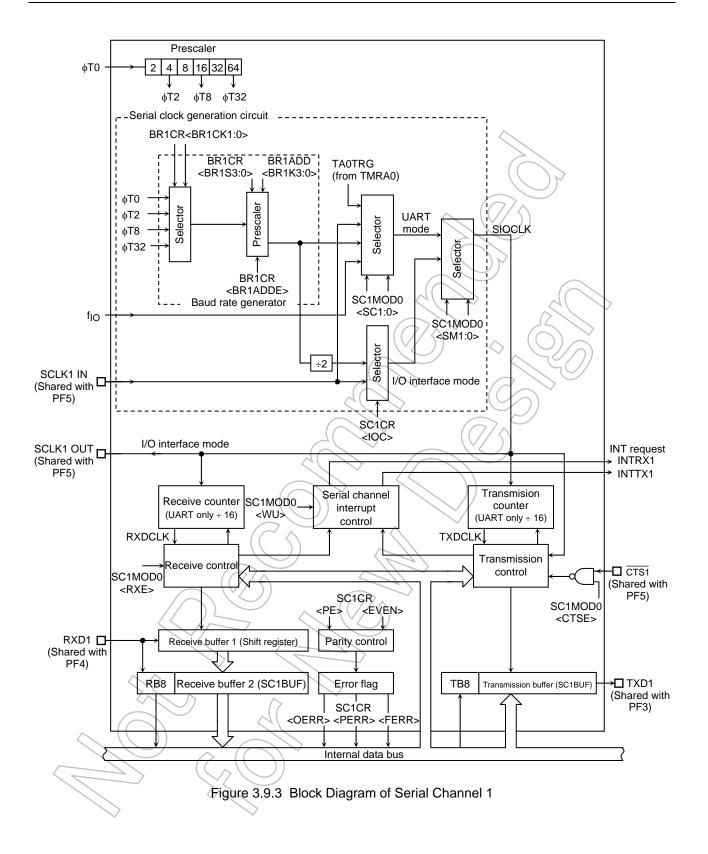

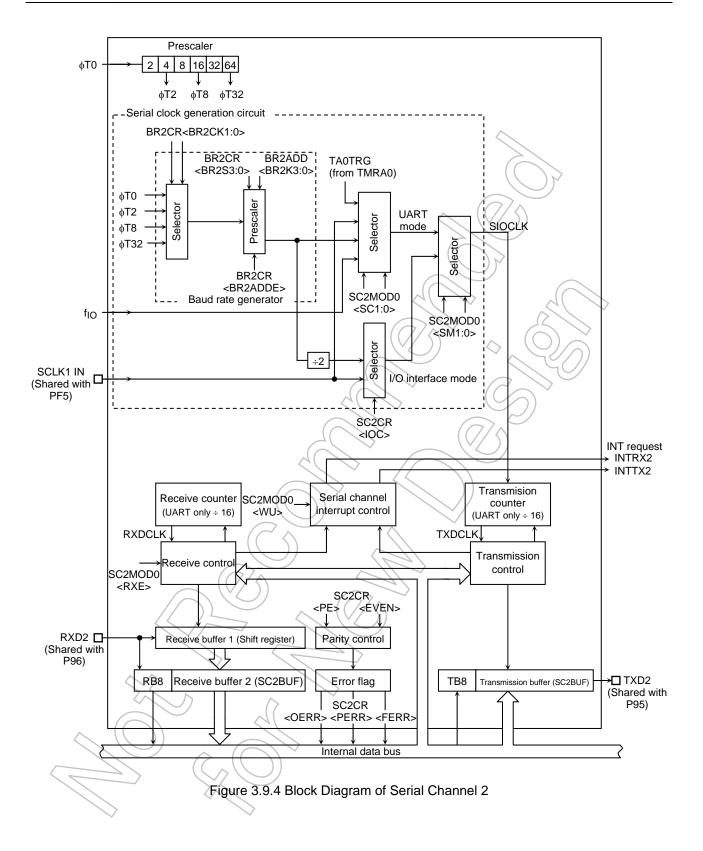

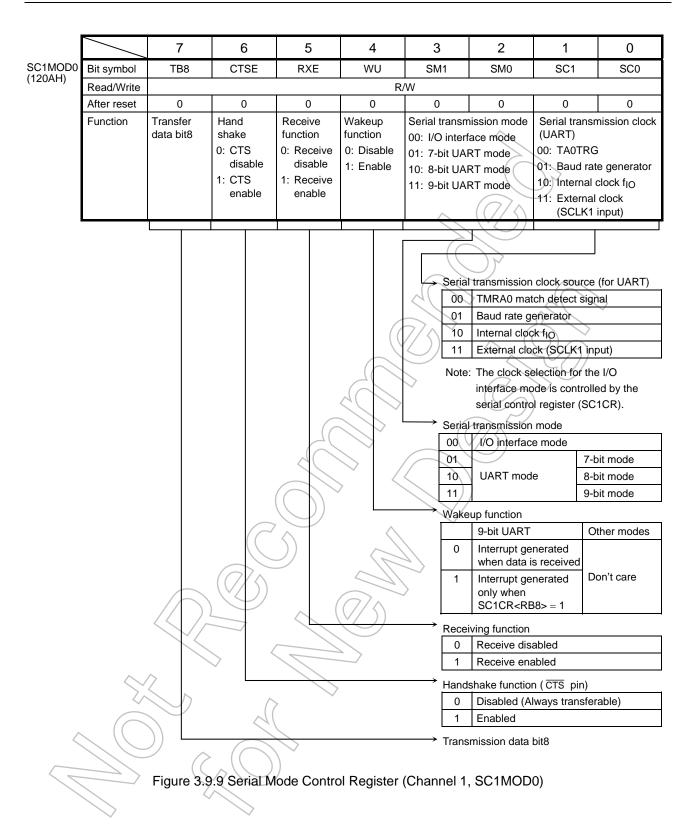

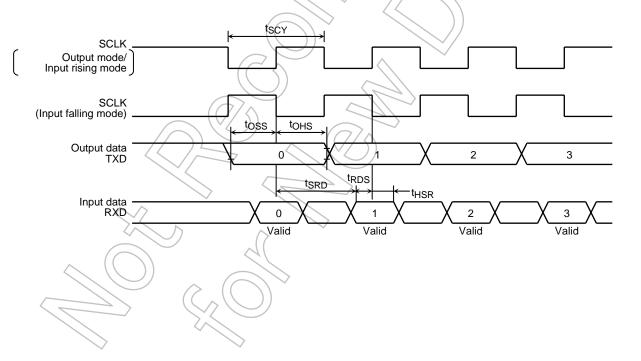

- (8) General-purpose serial interface: 3 channels

- UART/synchronous mode

- IrDA

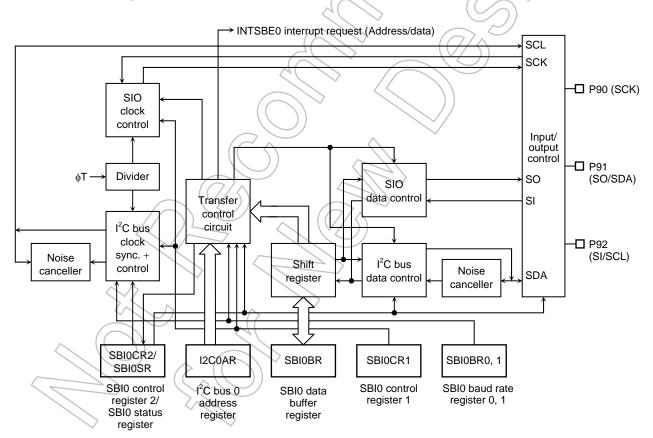

- (9) Serial bus interface: 1 channel

- I<sup>2</sup>C bus mode

- Clock synchronous select mode

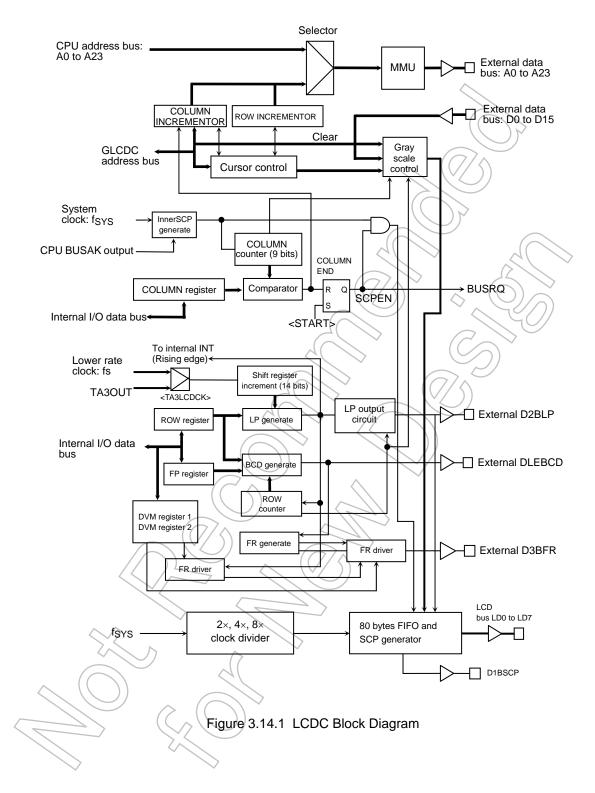

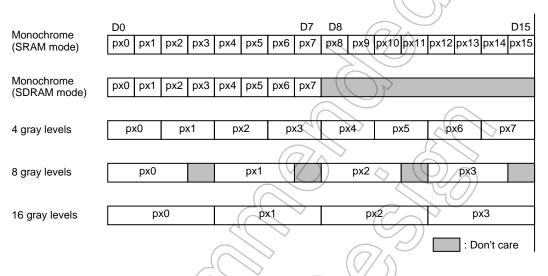

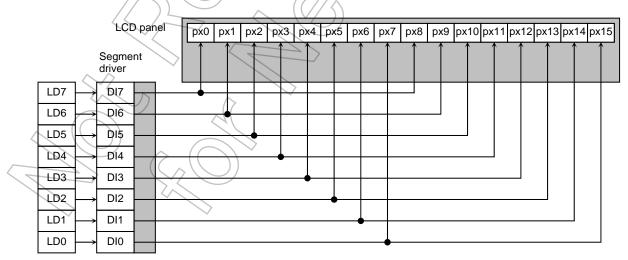

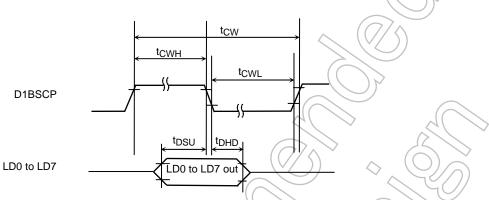

- (10) LCD controller

- Shift register/built-in RAM LCD driver

- Supported 16, 8 and 4 gray-levels and black and white

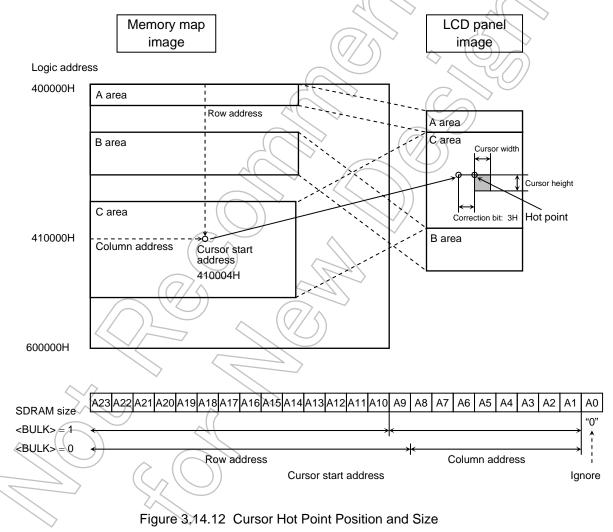

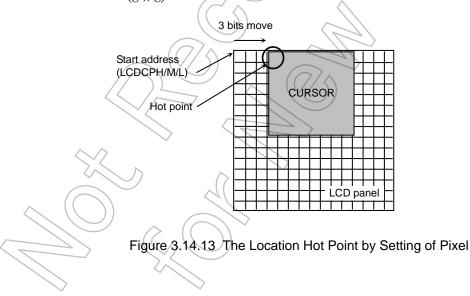

- Hardware blinking cursor

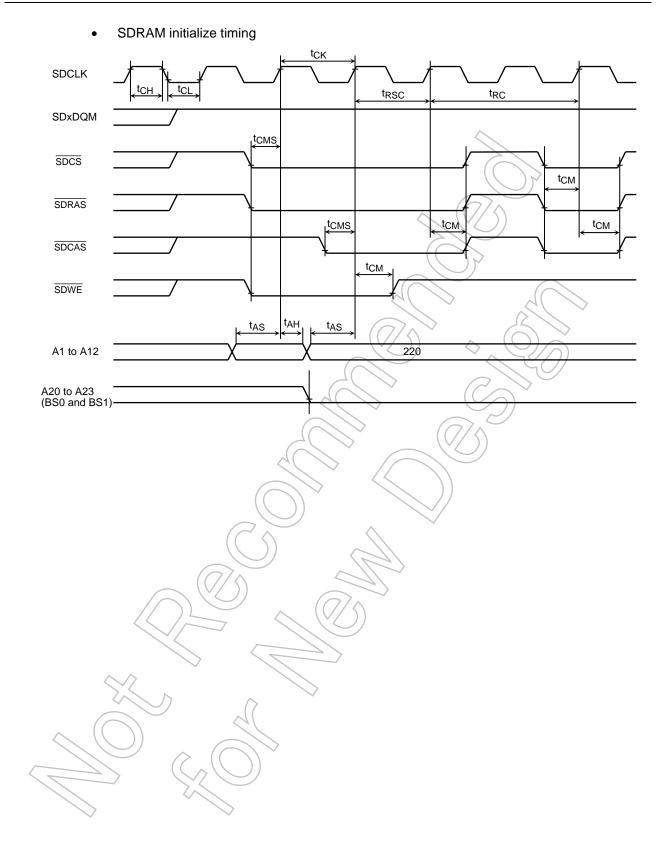

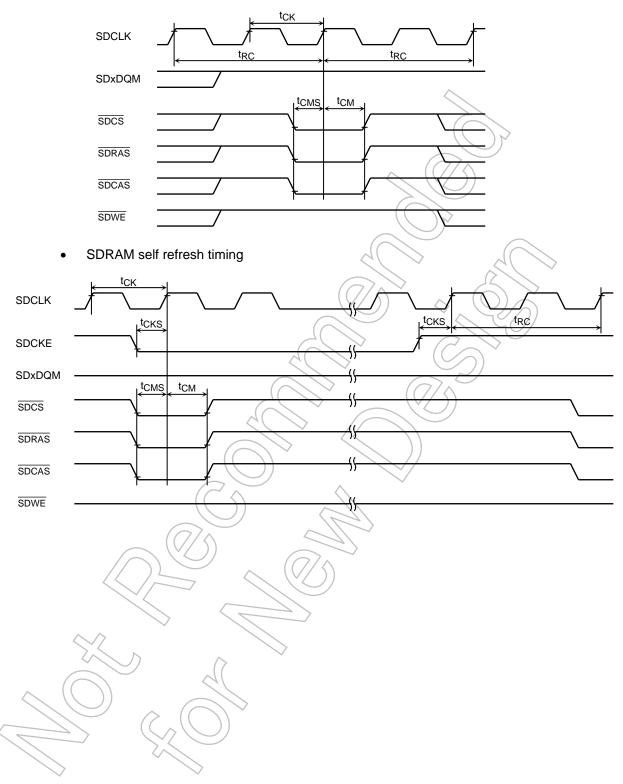

- (11) SDRAM controller

- Supported 16-M, 64-M and 128-Mbit SDRAM with 16-/32-bit data bus

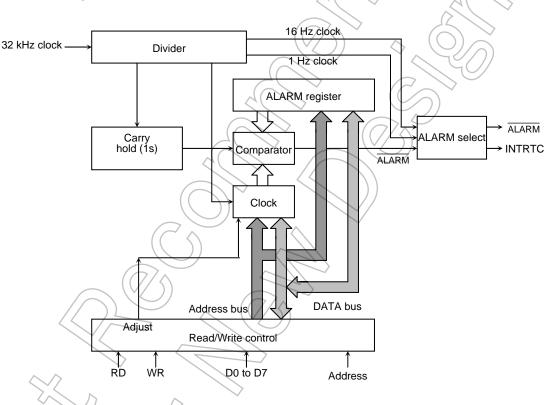

- (12) Timer for real-time clock (RTC)

- Based on TC8521A

- Separate the power supply

- (13) Key-on wakeup (Interrupt key input)

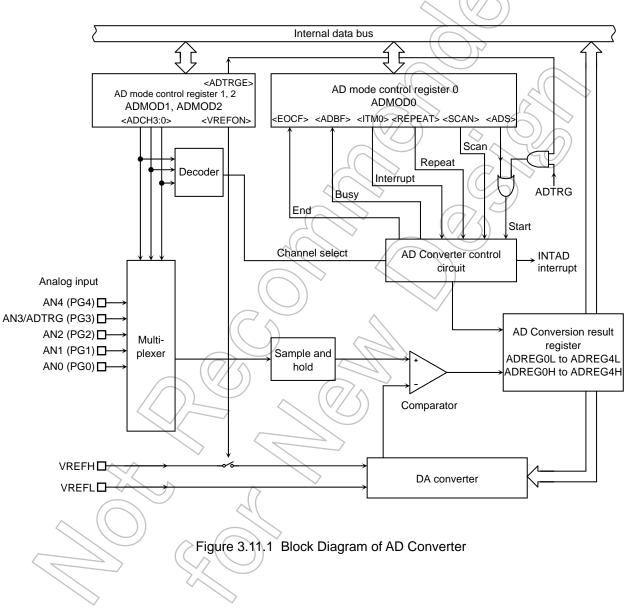

- (14) 10-bit AD converter: 5 channels

- (15) Watchdog timer

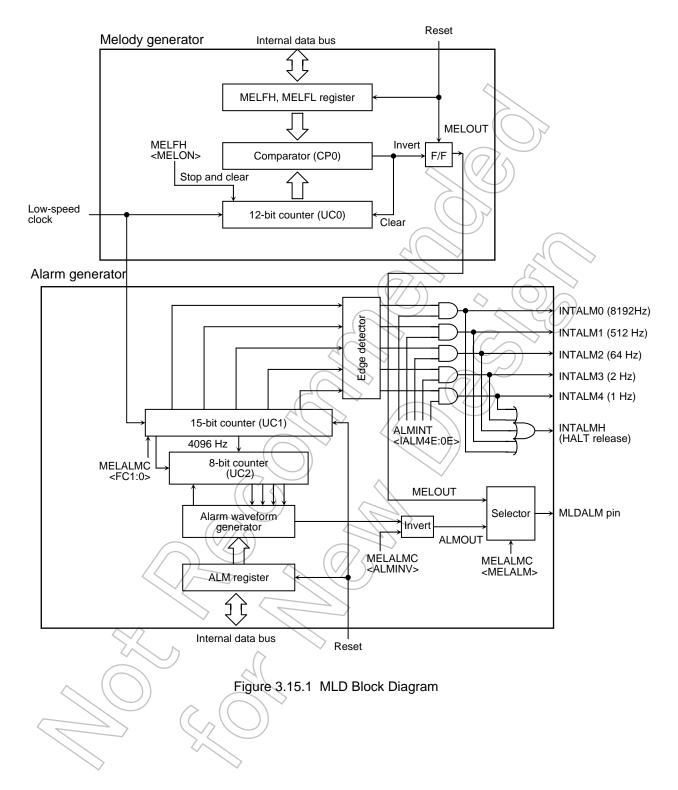

- (16) Melody/alarm generator

- Melody: Output of clock 4 to 5461 Hz

- Alarm: Output of the 8 kinds of alarm pattern

- Output of the 5 kinds of interval interrupt

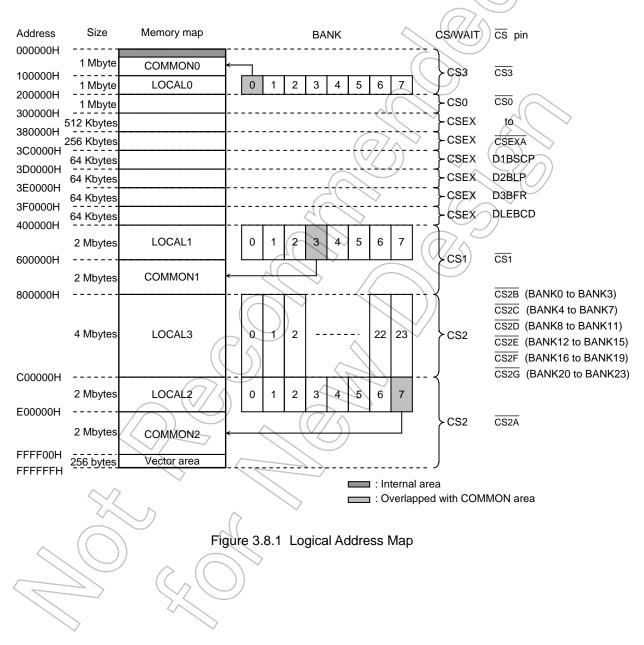

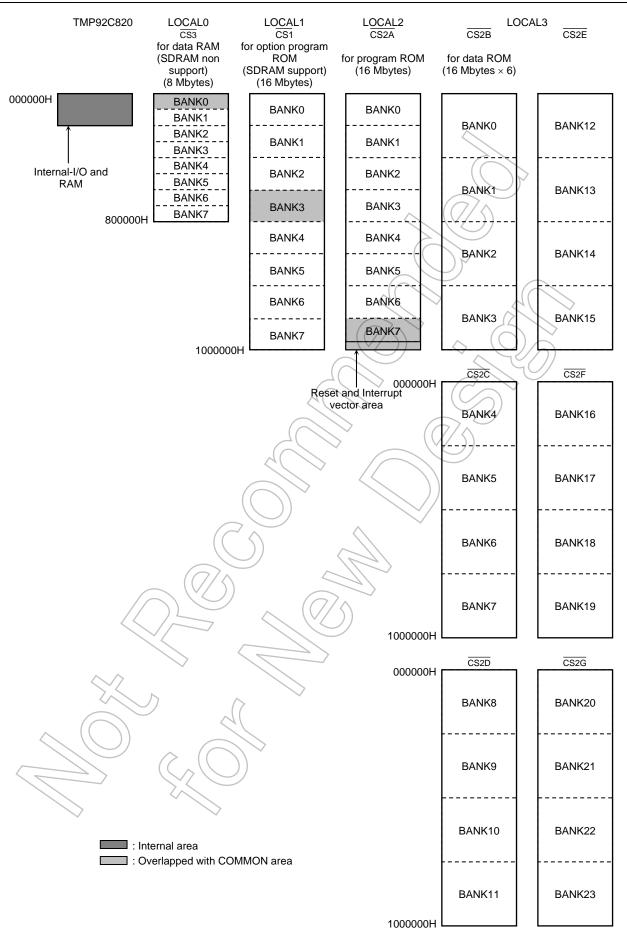

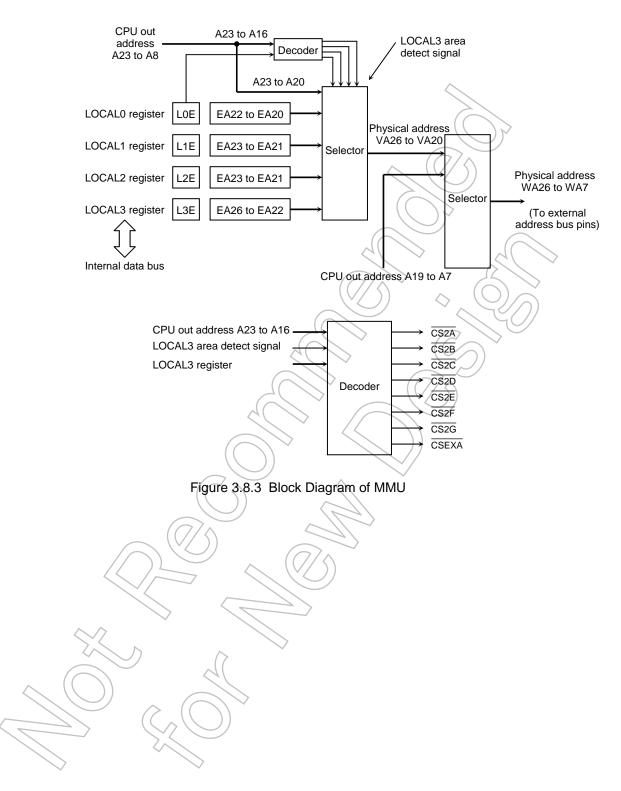

- (17) MMU

- Expandable up to 136 Mbytes (4 local areas/8 bank methods)

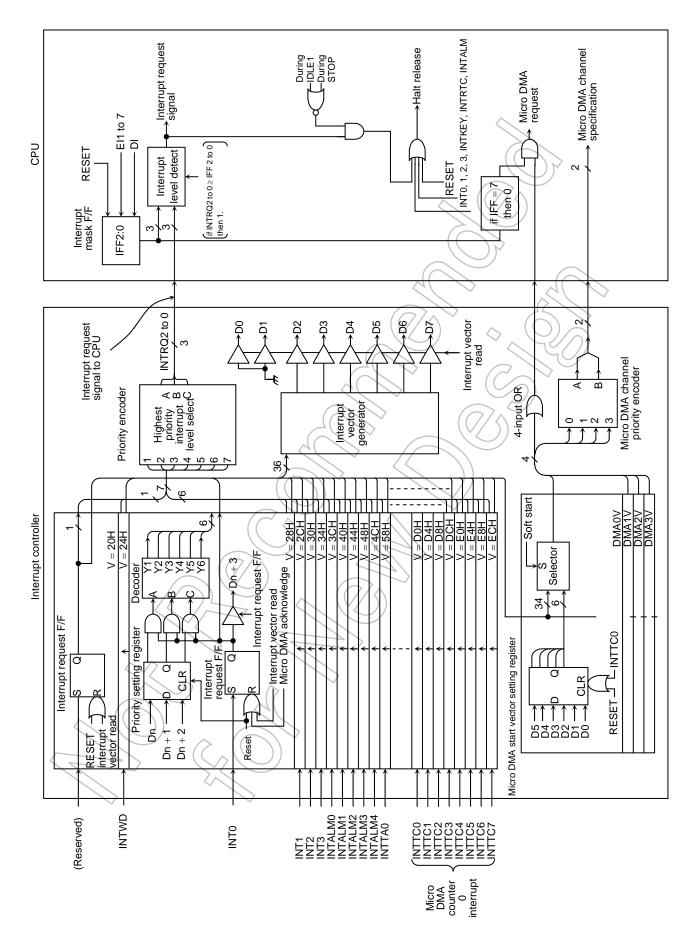

- (18) Interrupts: 45 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 31 internal interrupts: Seven selectable priority levels

- 5 external interrupts: Seven selectable priority levels (4-edge selectable)

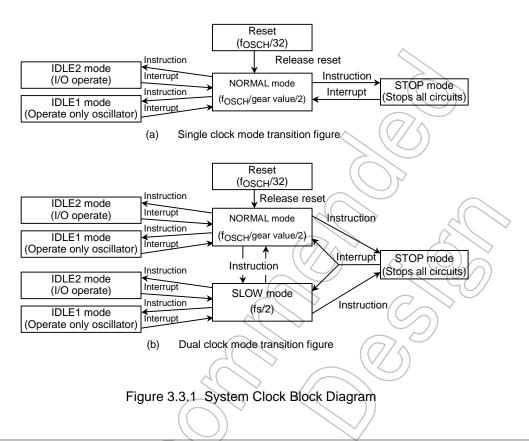

(19) Input/output ports: 83 pins (Except Data bus (16bit), Address bus (24bit) and RD pin)(20) Standby function

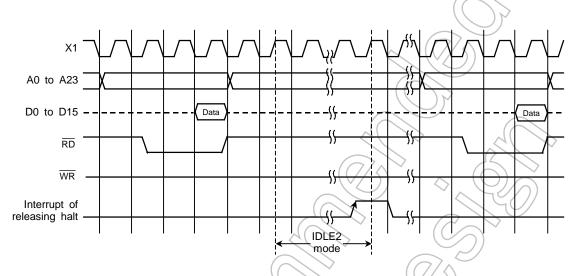

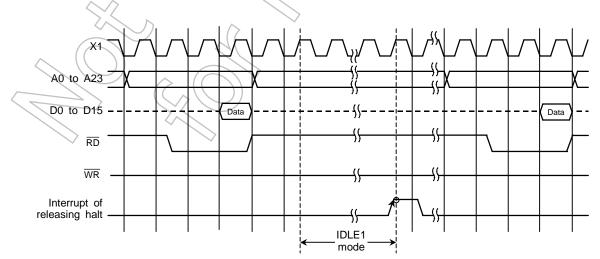

• Three HALT modes: IDLE2 (Programmable), IDLE1, STOP

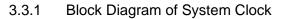

(21) Triple-clock controller

- Clock gear function: Select a high-frequency clock fc to fc/16

- RTC (fs = 32.768 kHz)

(22) Operating voltage

- DVCC = 3.0 to 3.6 V

- $\operatorname{RTCVCC} = 2.0 \text{ to } 3.6 \text{ V}$

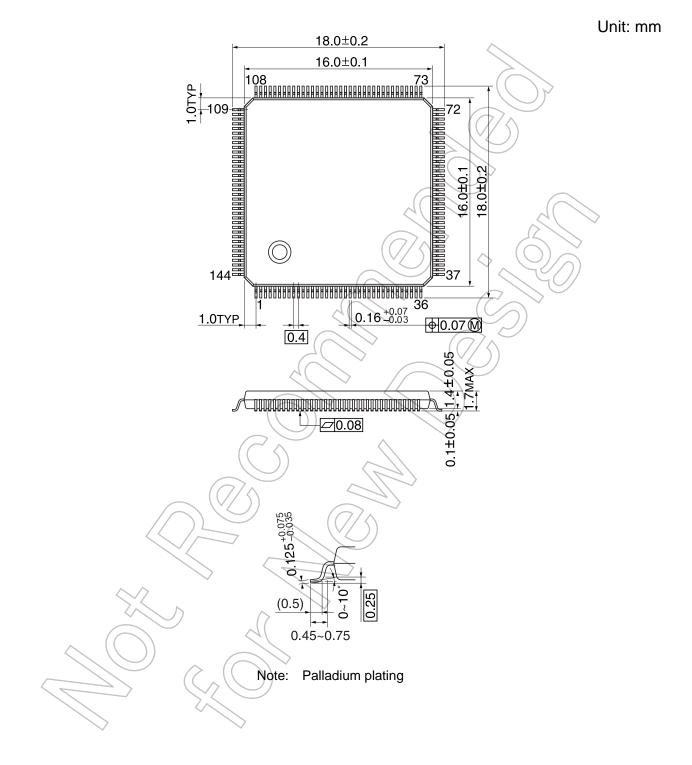

(23) Package

- 144-pin QFP (P-LQFP144-1616-0.40C)

- Chip form supply also available. For details, contact your local Toshiba sales representative

Figure 1.1 TMP92C820 Block Diagram

# 2. Pin Assignment and Functions

The assignment of input/output pins for the TMP92C820, their names and functions are as follows:

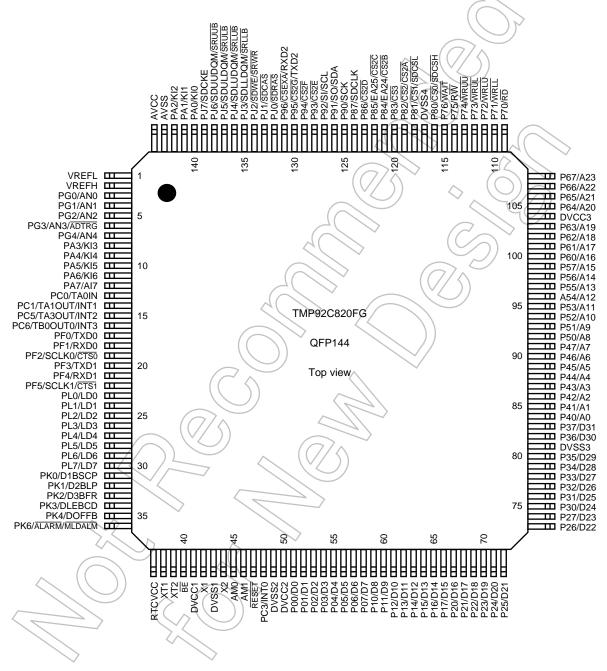

# 2.1 Pin Assignment

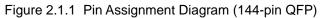

Figure 2.1.1 shows the pin assignment of the TMP92C820FG.

#### 2.2 PAD Layout

| Table 2.2.1 PAD Layout (144-pin chip) | Table 2.2.1 | PAD La | yout (1 | 44-pin | chip) |

|---------------------------------------|-------------|--------|---------|--------|-------|

|---------------------------------------|-------------|--------|---------|--------|-------|

| (Chip s    | size 4.68 mn | n × 4.68 |         |            | 2.1 PAD La | <b>J C C C C C C C C C C</b> |         | -)         |       |         | Unit: µm |

|------------|--------------|----------|---------|------------|------------|------------------------------|---------|------------|-------|---------|----------|

| Pin<br>No. | Name         | X Point  | Y Point | Pin<br>No. | Name       | X Point                      | Y Point | Pin<br>No. | Name  | X Point | Y Point  |

| 1          | VREFL        | -2213    | 1945    | 49         | DVSS2      | -440                         | -2213   | 97 <       | P55   | 2211    | 685      |

| 2          | VREFH        | -2213    | 1820    | 50         | DVCC2      | -340                         | -2213   | 98         | P56   | 2211    | 789      |

| 3          | PG0          | -2213    | 1694    | 51         | P00        | -240                         | -2213   | 99         | P57   | 2211    | 894      |

| 4          | PG1          | -2213    | 1568    | 52         | P01        | -140                         | -2213   | 100        | P60   | 2211    | 1000     |

| 5          | PG2          | -2213    | 1460    | 53         | P02        | -40                          | -2213   | 101        | P61   | 2211    | 1107     |

| 6          | PG3          | -2213    | 1353    | 54         | P03        | 59                           | -2213   | 102        | P62   | 2211    | 1213     |

| 7          | PG4          | -2213    | 1249    | 55         | P04        | 160                          | -2213   | 103        | P63   | 2211    | 1321     |

| 8          | PA3          | -2213    | 1050    | 56         | P05        | 260                          | -2213   | 104        | DVCC3 | 2211    | 1430     |

| 9          | PA4          | -2213    | 946     | 57         | P06        | 360                          | -2213   | 105)       | P64   | 2211    | 1546     |

| 10         | PA5          | -2213    | 842     | 58         | P07        | 460                          | -2213   | 106        | P65   | 2211    | 1672     |

| 11         | PA6          | -2213    | 739     | 59         | P10        | 561                          | -2213   | 107        | P66   | 2211    | 1798     |

| 12         | PA7          | -2213    | 635     | 60         | P11        | 661                          | -2213   | 108        | P67   | 2211    | 1924     |

| 13         | PC0          | -2213    | 531     | 61         | P12        | 761                          | -2213   | 109        | P70   | 1925    | 2211     |

| 14         | PC1          | -2213    | 427     | 62         | P13        | 861                          | -2213   | 110        | P71   | 1800    | 2211     |

| 15         | PC5          | -2213    | 326     | 63         | P14        | 961                          | -2213   | 111        | P72   | 1675    | 2211     |

| 16         | PC6          | -2213    | 224     | 64         | P15        | 1062                         | -2213   | 112        | _P73  | 1558    | 2211     |

| 17         | PF0          | -2213    | 123     | 65         | P16        | 1162                         | -2213   | 113        | P74   | 1448    | 2211     |

| 18         | PF1          | -2213    | 23      | 66         | P17 🔇      | 1263                         | -2213   | 114        | P75   | 1346    | 2211     |

| 19         | PF2          | -2213    | -77     | 67         | P20        | 1363                         | -2213   | 115        | P76   | 1243    | 2211     |

| 20         | PF3          | -2213    | -179    | 68         | P21        | 1474                         | -2213   | ( (116 <   | P80   | 1141    | 2211     |

| 21         | PF4          | -2213    | -284    | 69         | P22        | 1589                         | -2213   | 117        | DVSS4 | 1038    | 2211     |

| 22         | PF5          | -2213    | -388    | 70         | P23        | 1702                         | -2213   | 118        | P81   | 937     | 2211     |

| 23         | PL0          | -2213    | -493    | 71         | P24        | 1814                         | -2213   | 119        | P82   | 835     | 2211     |

| 24         | PL1          | -2213    | -598    | 72 (       | P25        | 1926                         | -2213   | / 120      | P83   | 734     | 2211     |

| 25         | PL2          | -2213    | -704    | 73         | P26        | 2211                         | -1924   | 121        | P84   | 633     | 2211     |

| 26         | PL3          | -2213    | -809    | 74         | P27        | 2211                         | –1799   | 122        | P85   | 532     | 2211     |

| 27         | PL4          | -2213    | -914    | 75         | P30        | 2211                         | -1674   | 123        | P86   | 431     | 2211     |

| 28         | PL5          | -2213    | -1024   | 76         | P31        | 2211                         | -1548   | 124        | P87   | 330     | 2211     |

| 29         | PL6          | -2213    | -1132   | 7/77       | P32        | 2211                         | -1426   | 125        | P90   | 229     | 2211     |

| 30         | PL7          | -2213    | -1243   | 78         | P33        | 2211                         | -1311   | 126        | P91   | 128     | 2211     |

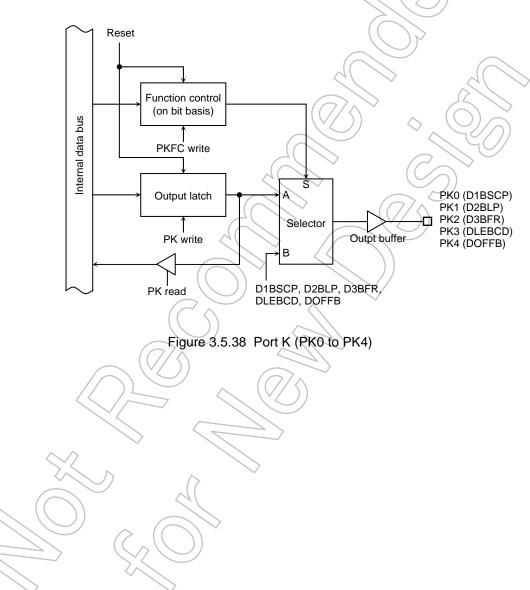

| 31         | PK0          | -2213    | -1354   | 79         | P34        | 2211                         | -1199   | 127        | P92   | 28      | 2211     |

| 32         | PK1          | -2213    | -1464   | 7 80       | P35        | 2211                         | -1087   | 128        | P93   | -72     | 2211     |

| 33         | PK2          | -2213    | -1576   | 81         | DVSS3      | 2211                         | -975    | 129        | P94   | -173    | 2211     |

| 34         | PK3          | -2213    | -1701   | 82 🗸       | P36        | 2211                         | -864    | 130        | P95   | -274    | 2211     |

| 35         | PK4          | -2213    | -1826   | 83         | P37        | 2211                         | -757    | 131        | P96   | -375    | 2211     |

| 36         | PK6          | -2213    | -1953   | 84         | P40        | 2211                         | -648    | 132        | PJ0   | -477    | 2211     |

| 37         | RTCVCC       | -1962    |         | 85         | P41        | 2211                         | -541    | 133        | PJ1   | -580    | 2211     |

| 38         | XT1          | -1851    | -2213   | 86         | P42        | 2211                         | -435    | 134        | PJ2   | -684    | 2211     |

| 39         | XT2 ((       | -1574    | -2213   | 87         | P43        | 2211                         | -332    | 135        | PJ3   | -788    | 2211     |

| 40         | BE           | -1466    | -2213   | 88         | P44        | 2211                         | -228    | 136        | PJ4   | -892    | 2211     |

| 41         | DVCC1        | -1360    | -2213   | 89)        | P45        | 2211                         | -128    | 137        | PJ5   | -996    | 2211     |

| 42         | X1           | -1257    | -2213   | 90         | P46        | 2211                         | -28     | 138        | PJ6   | -1101   | 2211     |

| 43         | DVSS1        | -1057    | -2213   | 91         | P47        | 2211                         | 71      | 139        | PJ7   | -1208   | 2211     |

| 44         | X2 🔪         | -957     | -2213   | 92         | P50        | 2211                         | 171     | 140        | PA0   | -1319   | 2211     |

| 45         | AM0          | -840     | -2213   | 93         | P51        | 2211                         | 272     | 141        | PA1   | -1430   | 2211     |

| 46         | AM1          | -740     | -2213   | 94         | P52        | 2211                         | 374     | 142        | PA2   | -1555   | 2211     |

| 47         | RESET        | -640     | -2213   | 95         | P53        | 2211                         | 477     | 143        | AVSS  | -1828   | 2211     |

| 48         | PC3          | -540     | -2213   | 96         | P54        | 2211                         | 581     | 144        | AVCC  | -1955   | 2211     |

# 2.3 Pin Names and Functions

The following table shows the names and functions of the input/output pins.

Table 2.3.1 Pin Names and Functions (1/3)

| Pin Names                          | Number of<br>Pins | I/O              | Functions                                                                                           |

|------------------------------------|-------------------|------------------|-----------------------------------------------------------------------------------------------------|

| D0 to D7                           | 8                 | I/O              | Data: Data bus 0 to 7.                                                                              |

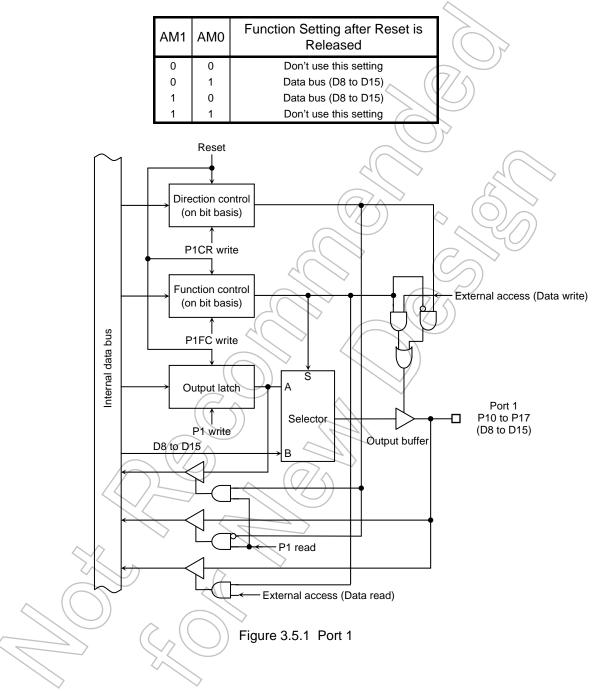

| P10 to P17                         | 8                 | I/O              | Port 1: I/O port. Input or output specifiable in units of bits.                                     |

| D8 to D15                          |                   | I/O              | Data: Data bus 8 to 15.                                                                             |

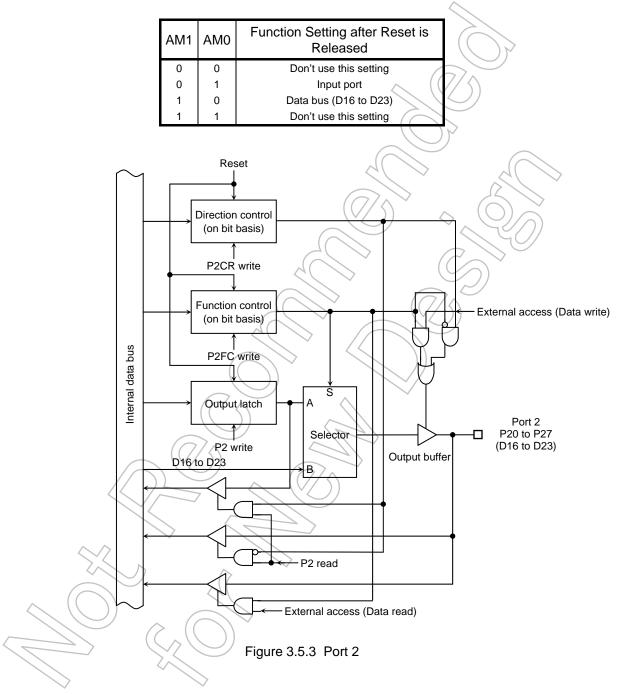

| P20 to P27                         | 8                 | I/O              | Port 2: I/O port. Input or output specifiable in units of bits.                                     |

| D16 to D23                         |                   | I/O              | Data: Data bus 16 to 23.                                                                            |

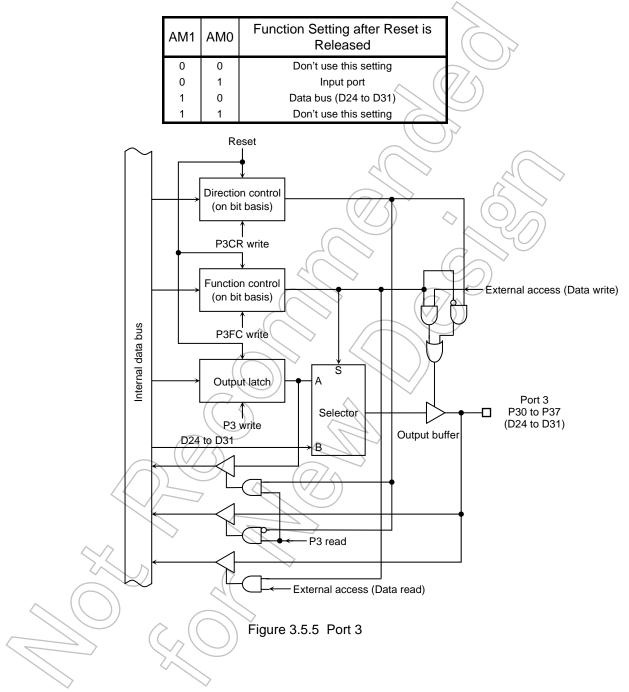

| P30 to P37                         | 8                 | I/O              | Port 3: I/O port. Input or output specifiable in units of bits.                                     |

| D24 to D31                         |                   | I/O              | Data: Data bus 24 to 31.                                                                            |

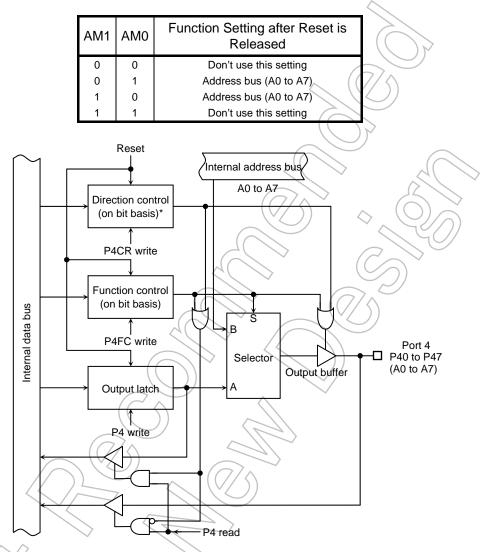

| P40 to P47                         | 8                 | I/O              | Port 4: I/O port. Input or output specifiable in units of bits.                                     |

| A0 to A7                           |                   | Output           | Address: Address bus 0 to 7.                                                                        |

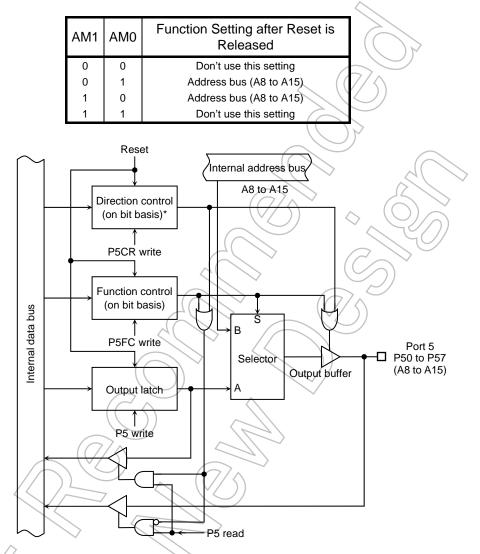

| P50 to P57                         | 8                 | I/O              | Port 5: I/O port. Input or output specifiable in units of bits.                                     |

| A8 to A15                          |                   | Output           | Address: Address bus 8 to 15.                                                                       |

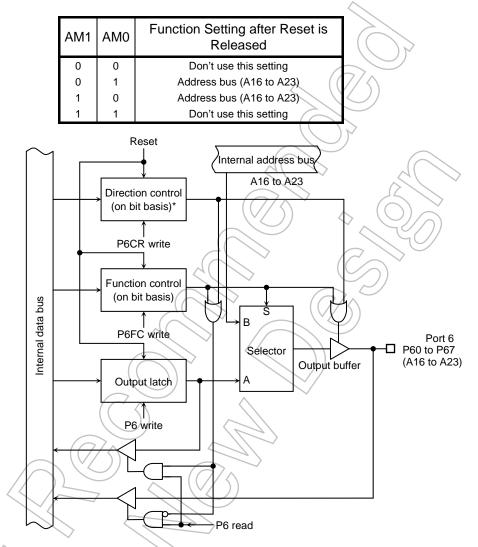

| P60 to P67                         | 8                 | I/O              | Port 6: I/O port. Input or output specifiable in units of bits.                                     |

| A16 to A23                         |                   | Output           | Address: Address bus 16 to 23.                                                                      |

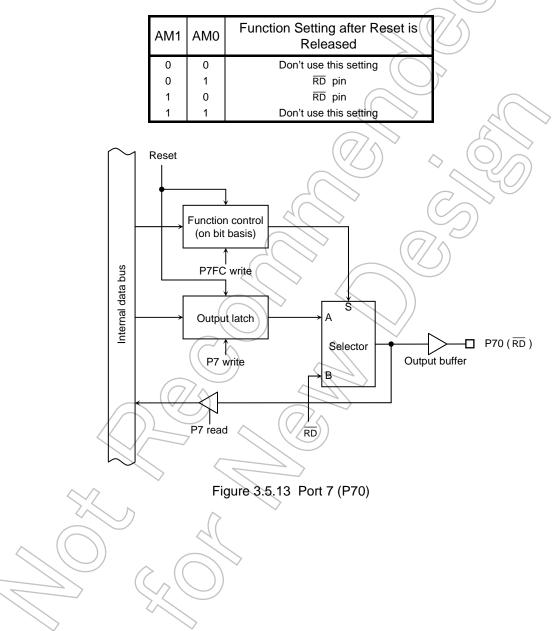

| P70<br>RD                          | 1                 | Output           | Port 70: Output port                                                                                |

|                                    |                   | Output           | Read: Outputs strobe signal to read external memory.                                                |

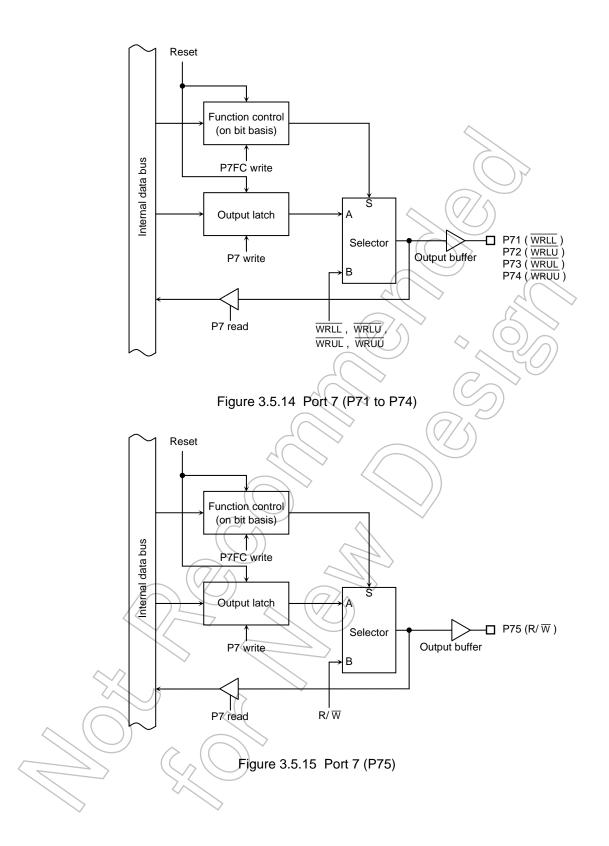

| P71<br>WRLL                        | 1                 | Output           | Port 71: Output port                                                                                |

|                                    |                   | Output           | Write: Output strobe signal for writing data on pins D0 to D7.                                      |

| P72                                | 1                 | Output           | Port 72: Output port                                                                                |

| WRLU                               |                   | Output           | Write: Output strobe signal for writing data on pins D8 to D15.                                     |

| P73                                | 1                 | Output           | Port 73: Output port                                                                                |

| WRUL                               |                   | Output           | Write: Output strobe signal for writing data on pins D16 to D23.                                    |

| P74                                | 1                 | Output           | Port 74: Output port                                                                                |

| WRUU                               |                   | Output           | Write: Output strobe signal for writing data on pins D24 to D31.                                    |

| P75                                | 1                 | Output           | Port 75: Output port                                                                                |

| R/W                                |                   | Output           | Read/Write: 1 represents read or dummy cycle; 0 represents write cycle.                             |

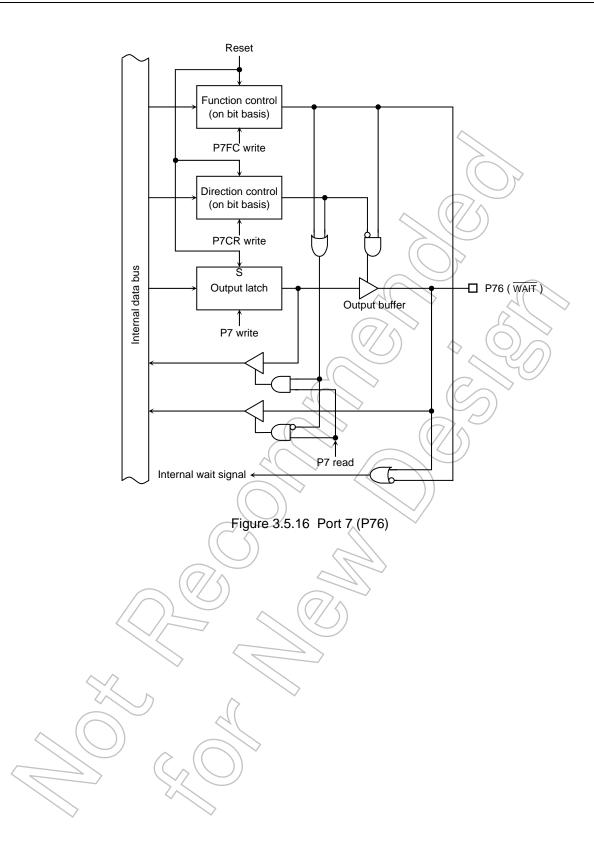

| P76                                | 1                 | I/O              | Port 76: VO port                                                                                    |

| WAIT                               |                   | Input            | Wait: Signal used to request CPU bus wait.                                                          |

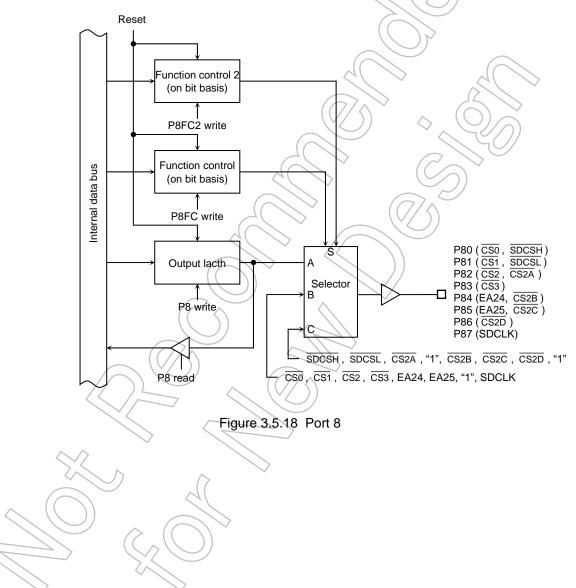

| P80<br><u> CS0</u>                 |                   | Output           | Port 80: Output port                                                                                |

| SDCSH                              | 1                 | Output           | Chip select 0: Outputs "low" when address is within specified address area.                         |

|                                    |                   | Output           | Chip select for SDRAM: Outputs "0" when address is within SDRAM upper-address area.                 |

| P81<br><u> CS1</u>                 |                   | Output           | Port 81: Output port                                                                                |

|                                    | 1                 | Output           | Chip select 1: Outputs "low" when address is within specified address area.                         |

|                                    | $\sim$            | Output           | Chip select for SDRAM: Outputs "0" when address is within SDRAM lower-address area.                 |

| P82<br><u>CS2</u>                  |                   | Output           | Port 82: Output port                                                                                |

| CS2<br>CS2A                        |                   | Output           | Chip select 2: Outputs "low" when address is within specified address area.                         |

|                                    | (( ))             | Output           | Expand chip select 2A: Outputs "0" when address is within specified address area.                   |

| P83<br><del> <u>C</u>S3<br/></del> |                   | Output<br>Output | Port 83: Output port<br>Chip select 3: Outputs "low" when address is within specified address area. |

| P84                                |                   |                  |                                                                                                     |

| EA24                               |                   | Output<br>Output | Port 84: Output port<br>Chip select 24: Outputs "0" when address is within specified address area.  |

| CS2B                               |                   | Output           | Expand chip select 2B: Outputs "0" when address is within specified address area.                   |

| P85                                | $\searrow$        | Output           | Port 85: Output port                                                                                |

| EA25                               | 1                 | Output           | Chip select 25: Outputs "0" when address is within specified address area.                          |

| CS2C                               | 1                 | Output           | Expand chip select 2C: Outputs "0" when address is within specified address area.                   |

| P86                                |                   | Output           | Port 86: Output port                                                                                |

| CS2D                               | 1                 | Output           | Expand chip select 2D: Outputs "0" when address is within specified address area.                   |

| P87                                |                   | Output           | Port 87: Output port                                                                                |

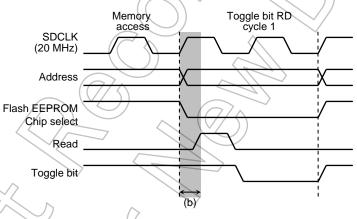

| SDCLK                              | 1                 | Output           | Clock for SDRAM                                                                                     |

|                                    |                   | Jaipui           |                                                                                                     |

ADTRG

Input

| Pin Names      | Number of<br>Pins                                     | I/O     | Functions                                                                                   |

|----------------|-------------------------------------------------------|---------|---------------------------------------------------------------------------------------------|

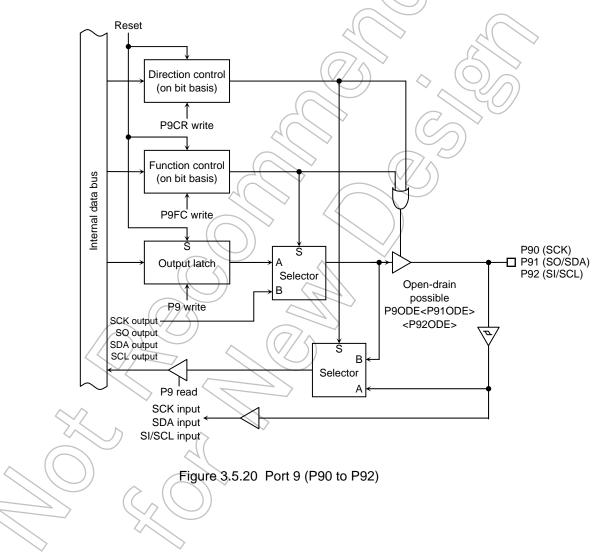

| P90            |                                                       | I/O     | Port 90: I/O port                                                                           |

| SCK            | 1                                                     | I/O     | Serial bus interface clock I/O data at SIO mode.                                            |

| P91            |                                                       | I/O     | Port 91: I/O port                                                                           |

| SO             |                                                       | Output  | Serial bus interface send data at SIO mode.                                                 |

| SDA            | 1                                                     | I/O     | Serial bus interface send/receive data at I <sup>2</sup> C mode.                            |

|                |                                                       | 1 1     | (Open drain/output mode by programmable.)                                                   |

| P92            |                                                       | I/O     | Port 92: I/O port                                                                           |

| SI             | _                                                     | Input   | Serial bus interface receive data at SIO mode.                                              |

| SCL            | 1                                                     | Ι/Ο     | Serial bus interface clock I/O data at I <sup>2</sup> C mode.                               |

|                |                                                       | 1 1     | (Open drain/output mode by programmable.)                                                   |

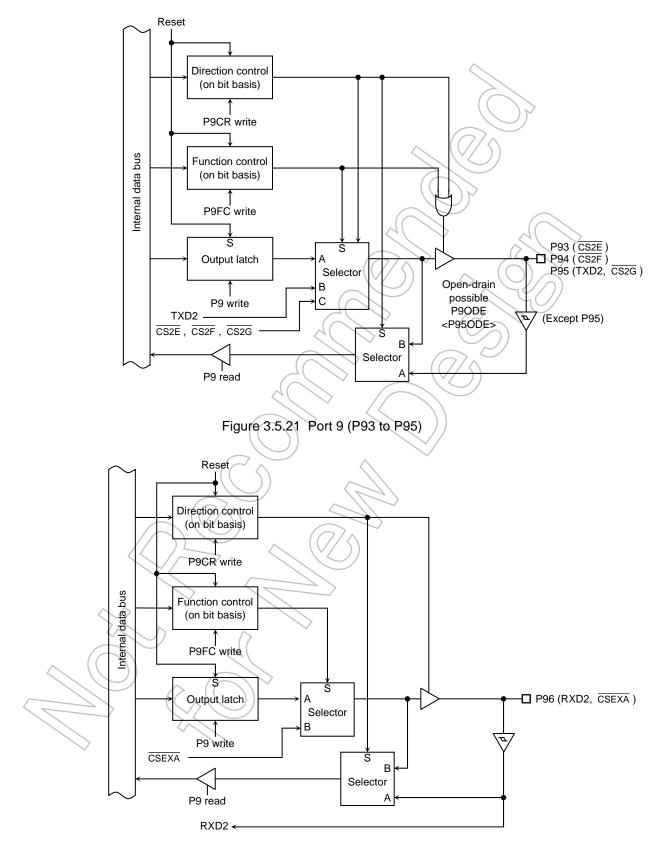

| P93            |                                                       | I/O     | Port 93: I/O port                                                                           |

| CS2E           | 1                                                     | Output  | Expand chip select 2E: Outputs "0" when address is within specified address area.           |

| P94            |                                                       | I/O     | Port 94: I/O port                                                                           |

| CS2F           | 1                                                     | Output  | Expand chip select 2F: Outputs "0" when address is within specified address area.           |

| P95            | ł – – ł                                               | I/O     | Port 95: Output port                                                                        |

| CS2G           | 1                                                     | Output  | Expand chip select 2G: Outputs "0" when address is within specified address area.           |

| TXD2           | '                                                     | Output  | Serial transmission data 2. Open drain/output pin by programmable.                          |

| P96            | <b>├</b> ────┦                                        | I/O     | Port 96: Output port                                                                        |

| RXD2           | 1                                                     | Input   | Serial receive data 2.                                                                      |

| CSEXA          | '                                                     | Output  | Expand chip select EXA: Outputs "0" when address is within specified address area.          |

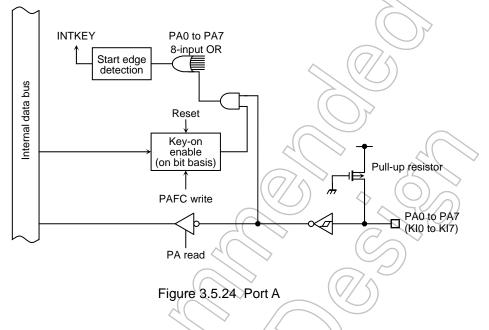

| PA0 to PA7     | łł                                                    | · ·     |                                                                                             |

| KI0 to KI7     |                                                       | Input   | A0 to A7 port: Pin used to input ports.                                                     |

|                | 8                                                     | Input   | Key input 0 to 7: Pin used of key-on wakeup 0 to 7.                                         |

| 200            | łł                                                    |         | (Schmitt input, with pull-up resistor.)                                                     |

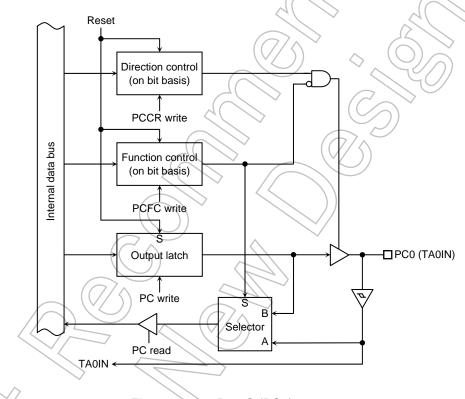

| PC0<br>TA0IN   | 1                                                     | I/O     | Port C0: I/O port                                                                           |

|                | <b>∤</b> ∤                                            | Input   | 8-bit timer 0 input: Timer 0 input.                                                         |

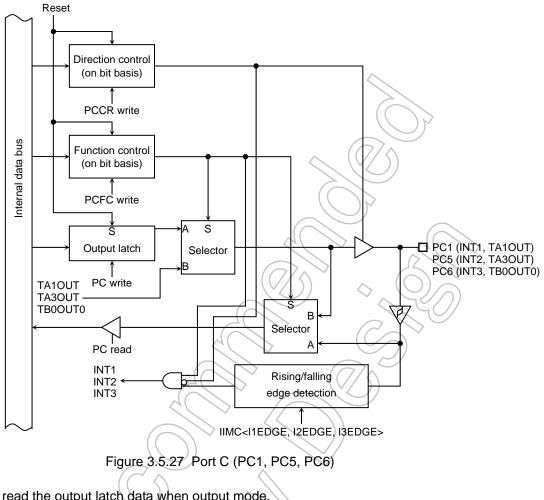

| PC1            |                                                       | I/O     | Port C1: I/O port                                                                           |

| INT1<br>TA1OUT | 1                                                     | Input   | Interrupt request pin1 : Interrupt request pin with programmable rising /falling edge.      |

|                | <b> </b>                                              | Output  | 8-bit timer 1 output: Timer 1 output.                                                       |

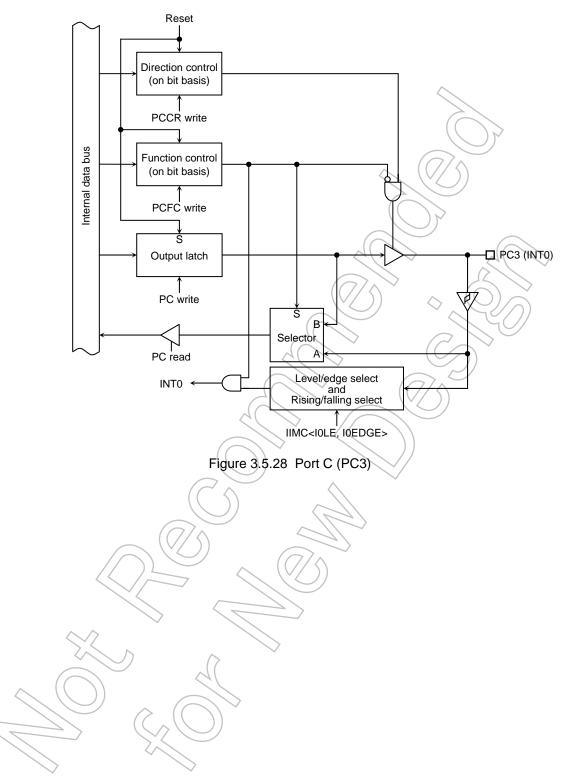

| PC3            | 1                                                     | I/O     | Port C3: I/O port                                                                           |

| INT0           | ļļ                                                    | Input   | Interrupt request pin 0: Interrupt request pin with programmable level/rising/falling edge. |

| PC5            |                                                       | 1/0     | Port C5: I/O port                                                                           |

| INT2           | 1                                                     | Input   | Interrupt request pin 2 : Interrupt request pin with programmable rising /falling edge.     |

| TA3OUT         |                                                       | Output  | 8-bit timer 3 output: Timer 3 output.                                                       |

| PC6            |                                                       | WQ <    | Port C6: I/O port                                                                           |

| INT3           | 1                                                     | Input   | Interrupt request pin 3: Interrupt request pin with programmable rising /falling edge.      |

| TB0OUT0        |                                                       | Output  | Timer B0 output.                                                                            |

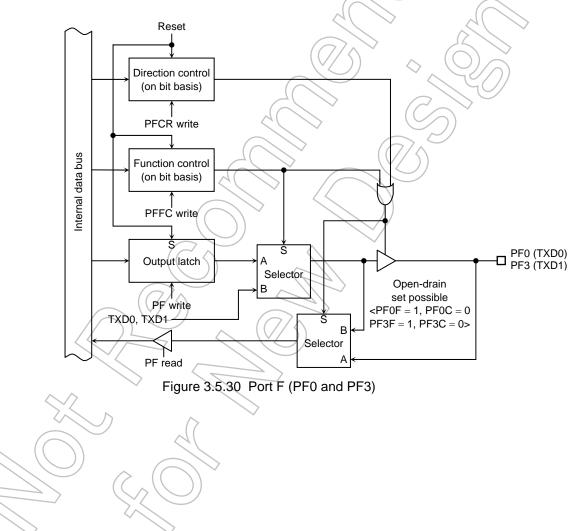

| PF0            |                                                       | I/O     | Port F0: I/O port                                                                           |

| TXD0           |                                                       | Output  | Serial 0 send data: Open drain/output pin by programmable.                                  |

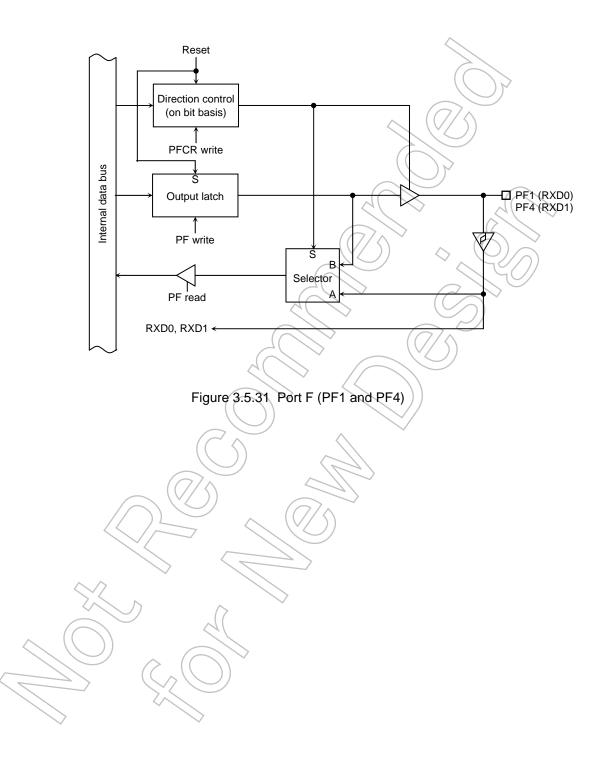

| PF1            |                                                       | 1/0     | Port F1: 1/O port                                                                           |

| RXD0           | $\left  \begin{array}{c} (( \ )) \end{array} \right $ | Input   | Serial 0 receive data.                                                                      |

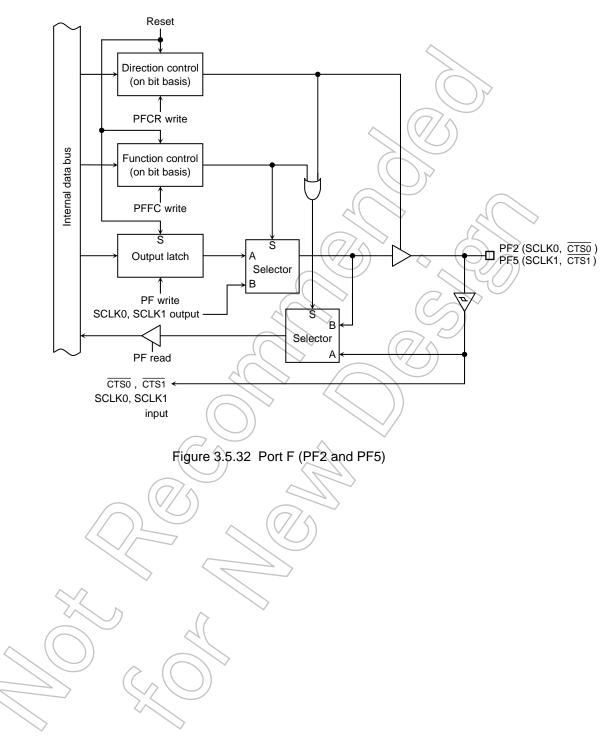

| PF2            |                                                       | I/O 🔿   | Port F2: I/Q port                                                                           |

| SCLK0          |                                                       | I/O ( 🤇 | Serial 0 clock I/O.                                                                         |

| CTS0           |                                                       | Input   | Serial 0 data send enable (Clear to send).                                                  |

| PF3            |                                                       | I/O     | Port F3: I/O port                                                                           |

| TXD1           | 1                                                     | Output  | Serial 1 send data: Open drain/output pin by programmable.                                  |

| PF4            |                                                       | I/O     | Port F4: I/O port                                                                           |

| RXD1           | 1                                                     | Input   | Serial 1 receive data.                                                                      |

| PF5            |                                                       | I/O     | Port F5: I/O port                                                                           |

| SCLK1          | 1                                                     | 1/O     | Serial 1 clock I/O.                                                                         |

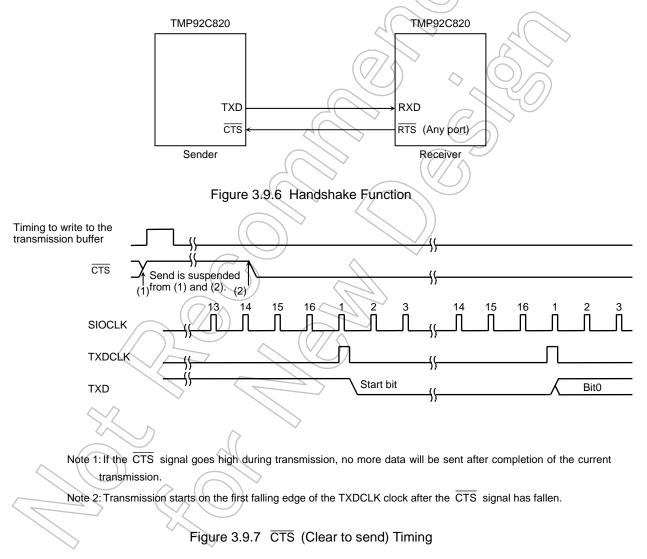

| CTS1           | '                                                     | Input   | Serial 1 data send enable (Clear to send).                                                  |

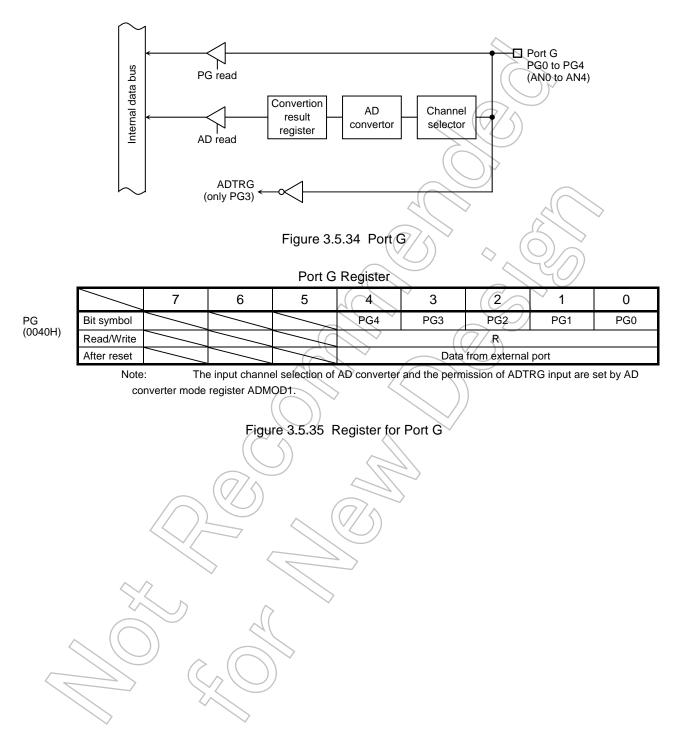

| PG0 to PG4     |                                                       | Input   | Port G0 to G4 port: Pin used to input ports.                                                |

| AN0 to AN4     | 5                                                     |         | Analog input 0 to 4: Pin used to Input to AD conveter.                                      |

| ADTRG          | 5                                                     | Input   | Analog input 0 to 4. Fin used to input to AD conveter.                                      |

| Table 2.3.1 P | Pin Names and | Functions ( | 2/3) |

|---------------|---------------|-------------|------|

|---------------|---------------|-------------|------|

AD trigger: Signal used to request AD start (with used to PG3).

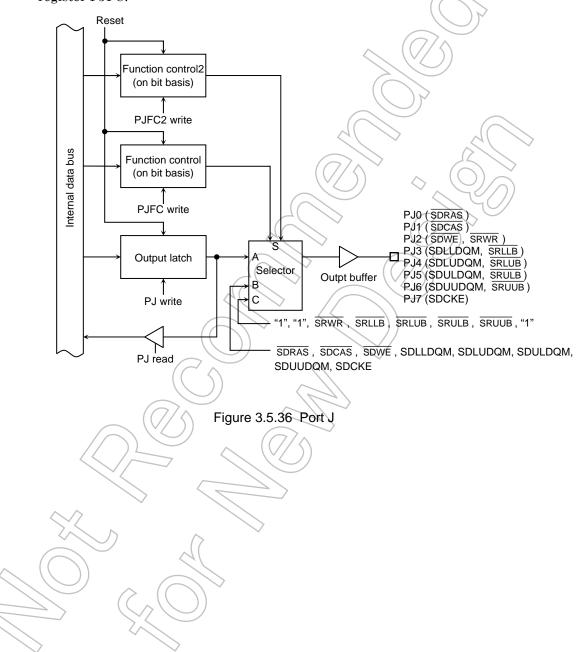

| PJ0       Output       Port J0: Output port         SDRAS       1       Output       Row address strobe for SDRAM: Outputs "0" when address is within         PJ1       Output       Port J1: Output port         SDCAS       1       Output       Port J1: Output port         Output       Output       Column address strobe for SDRAM: Outputs "0" when address is with area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SDRAS         Output         Row address strobe for SDRAM: Outputs "0" when address is within           PJ1         Output         Port J1: Output port           SDCAS         1         Output         Column address strobe for SDRAM: Outputs "0" when address is with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| SDCAS         1         Output         Column address strobe for SDRAM: Outputs "0" when address is with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SDRAM address area. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | hin SDRAM address   |

| PJ2 Output Port J2: Output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| SDWE         1         Output         Write enable for SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | )                   |

| SRWR         Output         Write for SRAM: Strobe signal for writing data .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

| PJ3 Output Port J3: Output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| SDLLDQM 1 Output Data enable for SDRAM on pins D0 to D7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                     |

| SRLLB Output Data enable for SRAM on pins D0 to D7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| PJ4 Output Port J4: Output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\frown$            |

| SDLUDQM 1 Output Data enable for SDRAM on pins D8 to D15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |

| SRLUB Output Data enable for SRAM on pins D8 to D15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |

| PJ5 Output Port J5: Output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\leq$              |

| SDULDQM 1 Output Data enable for SDRAM on pins D16 to D23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\sum ($            |

| SRULB Output Data enable for SRAM on pins D16 to D23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2/))                |

| PJ6 Output Port J6: Output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| SDUUDQM         1         Output         Data enable for SDRAM on pins D24 to D32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\checkmark$        |

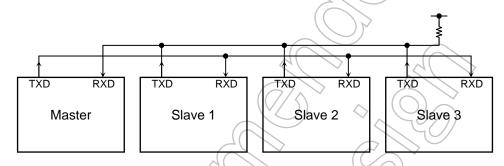

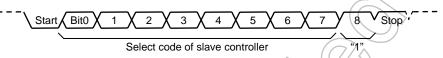

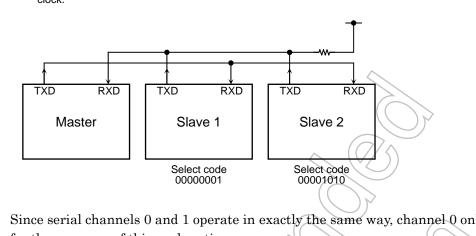

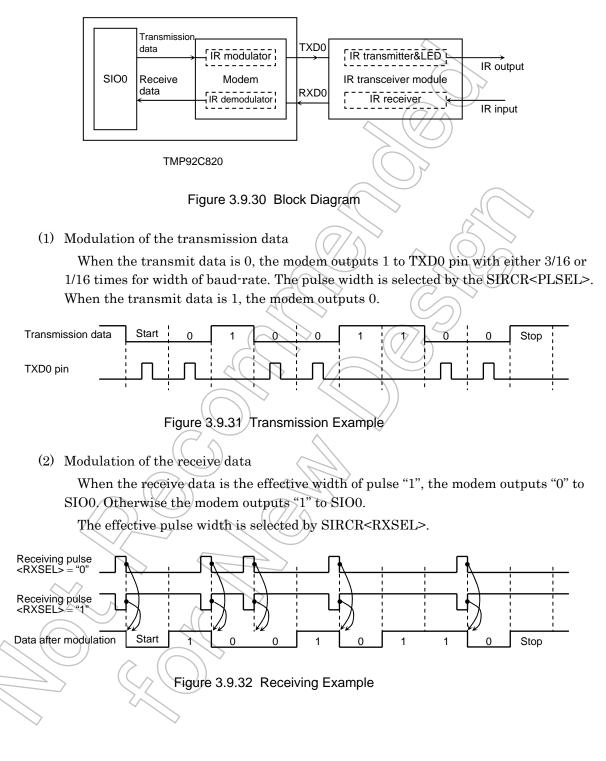

| SRUUB Output Data enable for SRAM on pins D24 to D32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |