# **TOSHIBA**

**TOSHIBA Original CMOS 16-Bit Microcontroller**

# TLCS-900/L1 Series

**TMP91CW28**

www.DataSheet4U.com

# **TOSHIBA CORPORATION**

Semiconductor Company

# **Preface**

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

Low-Voltage, Low-Power

# CMOS 16-Bit Microcontroller TMP91CW28FG

# 1. Outline

The TMP91CW28 is a high-speed, high-performance 16-bit microcontroller suitable for low-voltage, low-power applications.

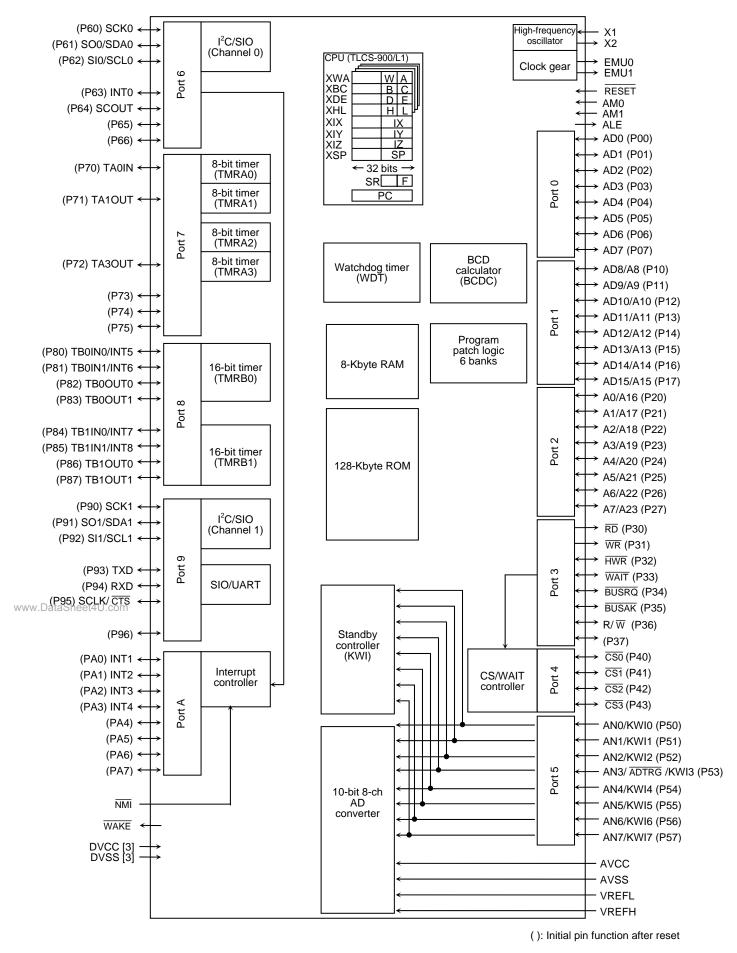

The TMP91CW28FG comes in a 100-pin mini flat package. Features of the TMP91CW28FG include the following:

- (1) High-speed 16-bit CPU (900/L1 CPU)

- Instruction set is upwardly assembly code compatible with the TLCS-90

- 16-Mbyte linear address space

- Architecture based on general-purpose registers and register banks

- 16-bit multiply/divide instructions and bit transfer/arithmetic instructions

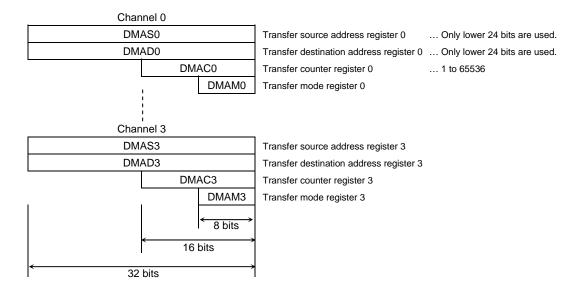

- 4-channel micro DMA (1.6 μs/2 bytes at 10 MHz)

- (2) Minimum instruction execution time: 400 ns (at 10 MHz)

- (3) 8-Kbyte on-chip RAM 128-Kbyte on-chip ROM

#### **RESTRICTIONS ON PRODUCT USE**

060116EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as www.DataShset4forthnin the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk, 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from

its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

021023\_C

- The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_s

91CW28-1 2006-03-24

- (4) External memory expansion

- 16-Mbyte off-chip address space for code and data

- External bus interface with dynamic bus sizing for 8-bit and 16-bit data ports

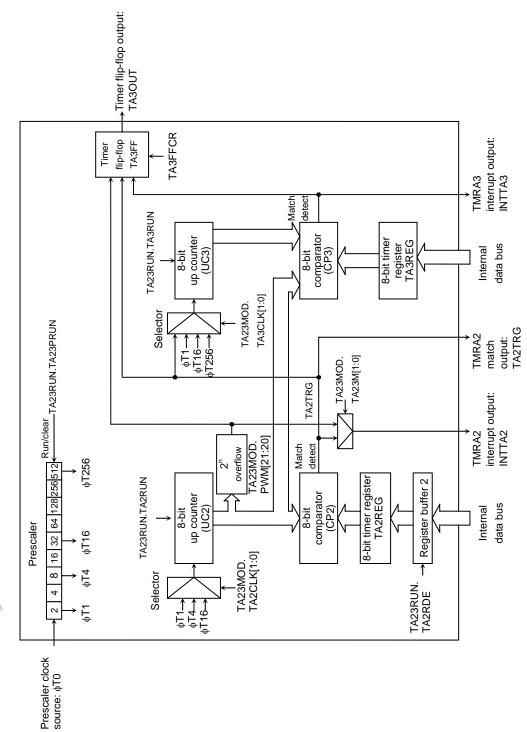

- (5) 4-channel 8-bit timer

- (6) 2-channel 16-bit timer

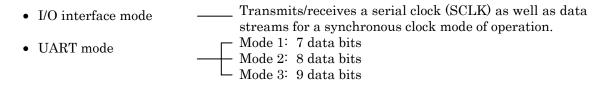

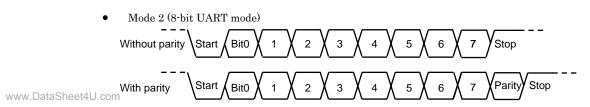

- (7) 1-channel general-purpose serial interface

- · Both UART and synchronous transfer modes are supported

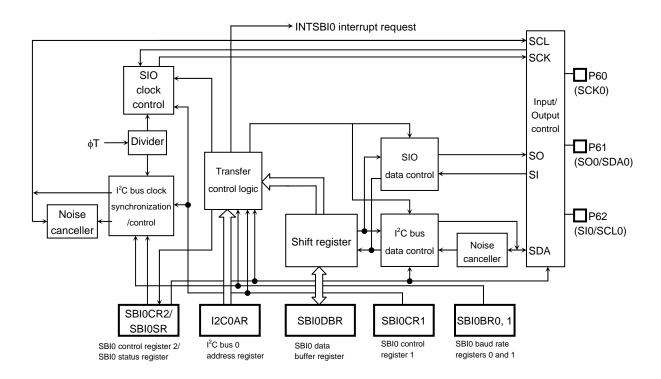

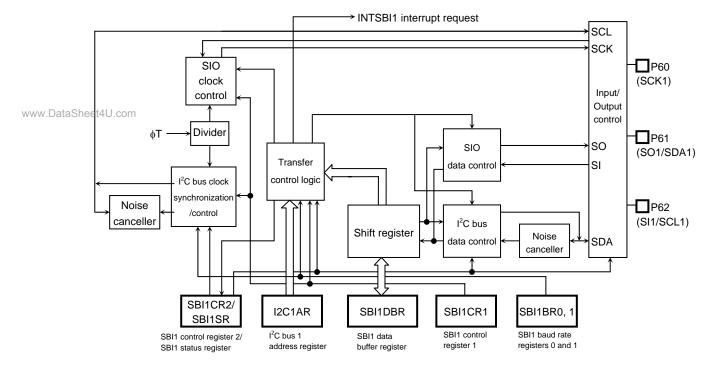

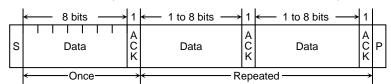

- (8) 2-channel serial bus interface Either I<sup>2</sup>C bus mode or clock-synchronous mode can be selected

- (9) 8-channel 10-bit AD converter (with internal sample/hold)

- (10) Watchdog timer

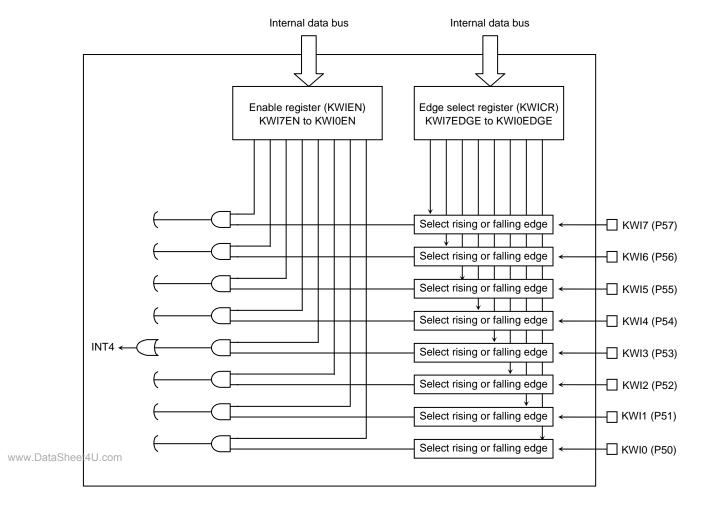

- (11) Key wakeup interrupt with 8-bit inputs

- (12) WAKE output pin

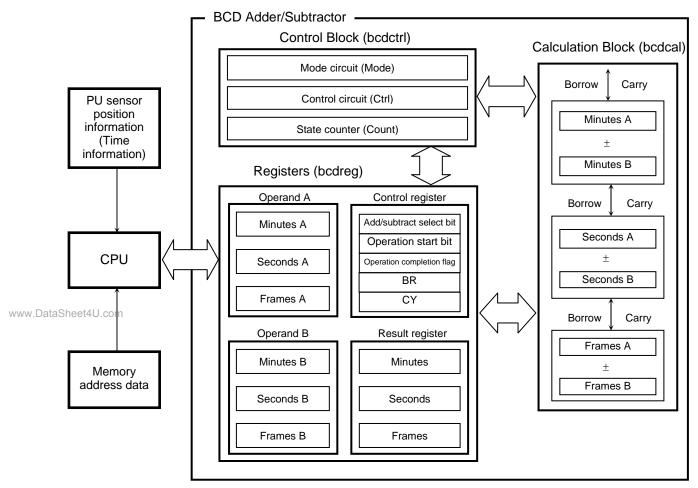

- (13) BCD adder/subtracter

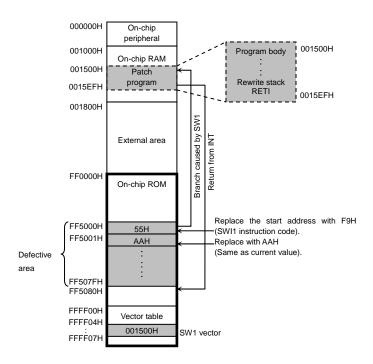

- (14) Program patch logic

- 6 banks of registers

- (15) 4-channel chip select/wait controller

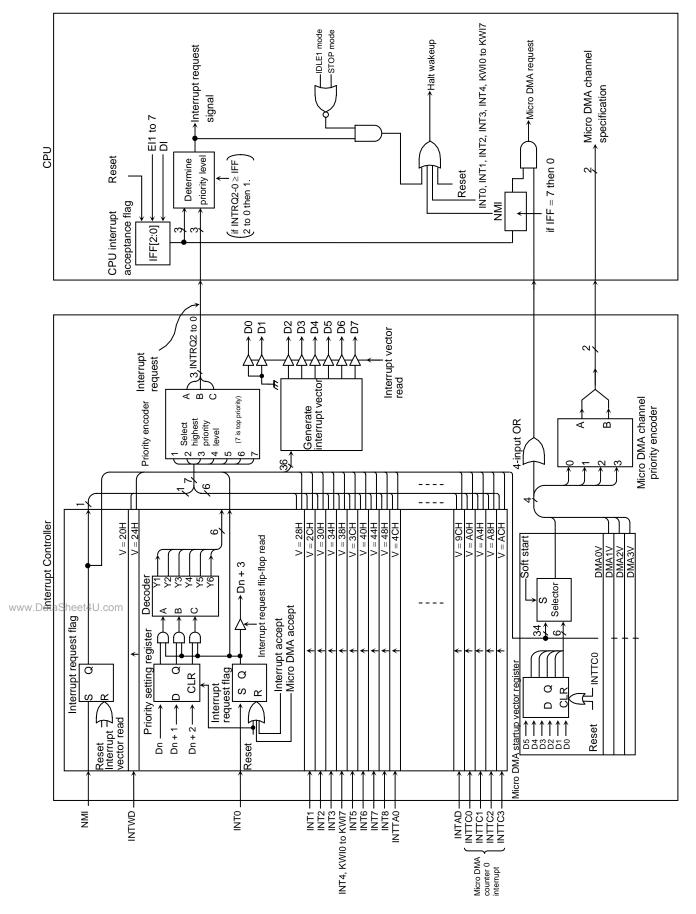

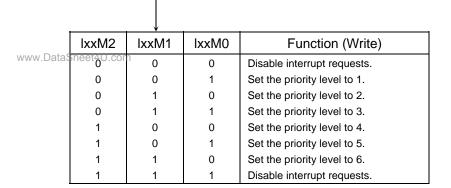

- (16) 48 interrupt sources

- 9 CPU interrupts: Triggered by software interrupt instruction or upon the execution of an undefined instruction

- 21 internal interrupts: 7 priority levels

- 18 external interrupts: 7 priority levels (16 interrupts supporting selection of triggering edge)

- (17) 80-pin input/output ports

- (18) Standby modes

- Three HALT modes: Programmable IDLE2, IDLE1, STOP

- (19) Clock control

- Clock gear: Changes the frequency of high-frequency clock within the range from fc to fc/16

- (20) Operating voltage range: 1.8 to 2.6 V (fc max = 10 MHz)

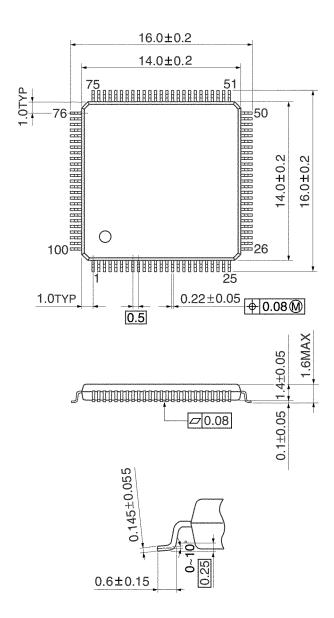

- (21) Package: P-LQFP100-1414-0.50F

TOSHIBA www.Datasheetau.com

Figure 1.1 TMP91CW28 Block Diagram

91CW28-3 2006-03-24

TOSHIBA www.batasheetau.com

# 2. Signal Descriptions

This section contains pin assignments for the TMP91CW28 as well as brief descriptions of the TMP91CW28 input and output signals.

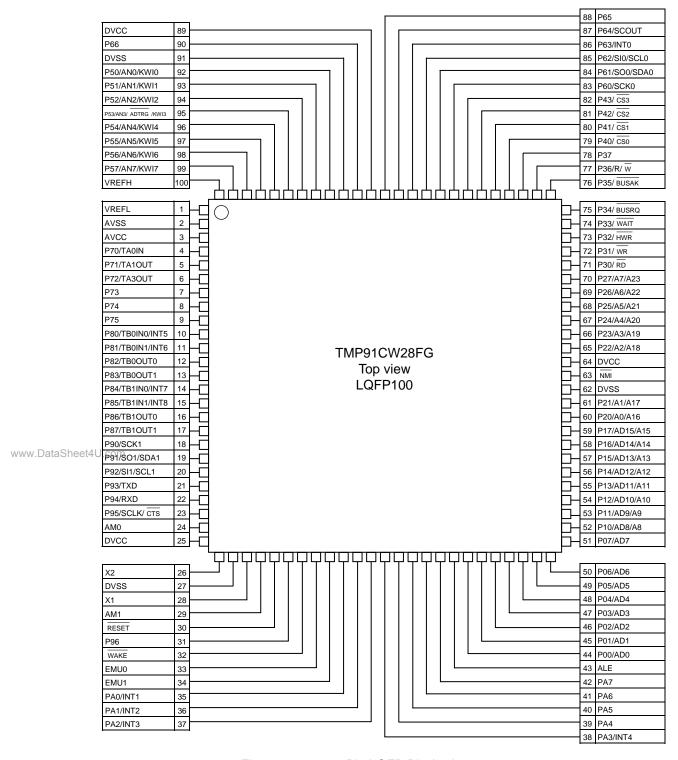

# 2.1 Pin Assignment

The following illustrates the TMP91CW28FG pin assignment.

Figure 2.1.1 100-Pin LQFP Pin Assignment

91CW28-4 2006-03-24

# 2.2 Pin Usage Information

Table 2.2.1 to 2.2.4 list the input and output pins of the TMP91CW28, including alternate pin names and functions for multi-function pins.

Table 2.2.1 Pin Names and Functions (1/4)

|                      |                |        | riii Nailles and i dilctions (1/4)                                                                                                                                                                                                                                                                                                   |

|----------------------|----------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | Number of Pins | I/O    | Functions                                                                                                                                                                                                                                                                                                                            |

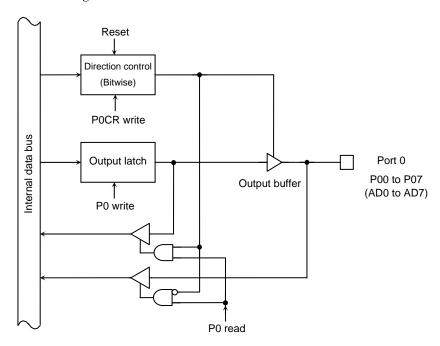

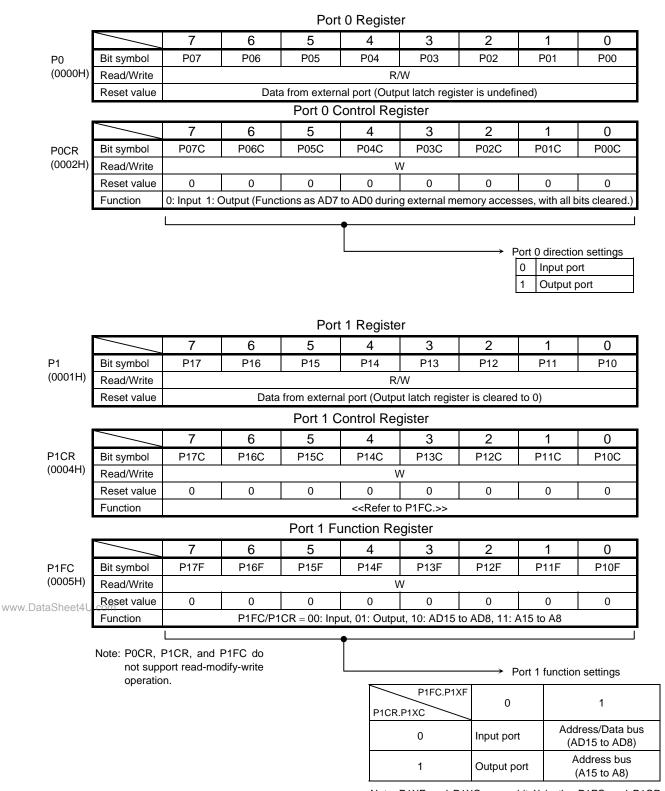

| P00 to P07           | 8              | I/O    | Port 0: Individually programmable as input or output                                                                                                                                                                                                                                                                                 |

| AD0 to AD7           |                | I/O    | Address/data (Lower): Bits 0 to 7 of the address/data bus                                                                                                                                                                                                                                                                            |

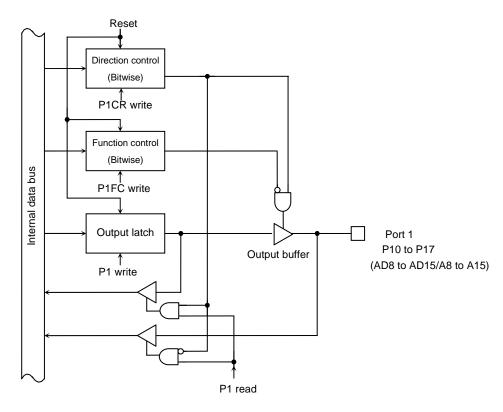

| P10 to P17           | 8              | I/O    | Port 1: Individually programmable as input or output                                                                                                                                                                                                                                                                                 |

| AD8 to AD15          |                | I/O    | Address/data (Upper): Bits 8 to 15 of the address/data bus                                                                                                                                                                                                                                                                           |

| A8 to A15            |                | Output | Address: Bits 8 to 15 of the address bus                                                                                                                                                                                                                                                                                             |

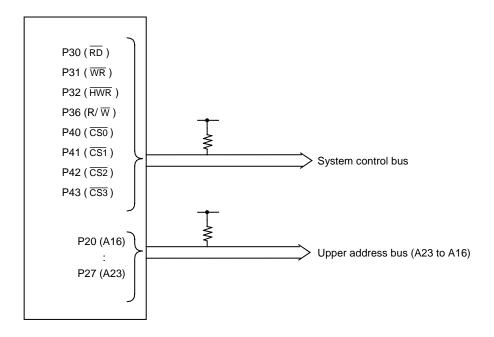

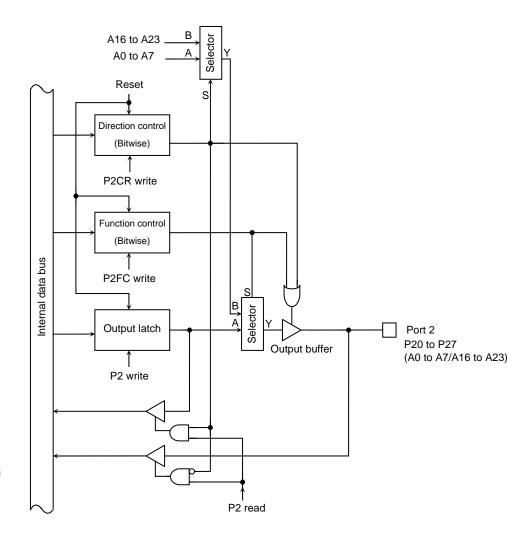

| P20 to P27           | 8              | I/O    | Port 2: Individually programmable as input or output                                                                                                                                                                                                                                                                                 |

| A0 to A7             |                | Output | Address: Bits 0 to 7 of the address bus                                                                                                                                                                                                                                                                                              |

| A16 to A23           |                | Output | Address: Bits 16 to 23 of the address bus                                                                                                                                                                                                                                                                                            |

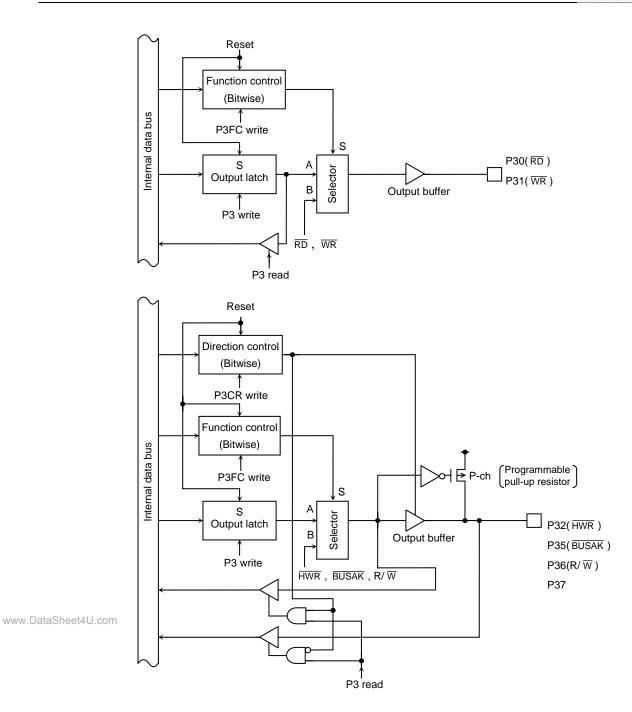

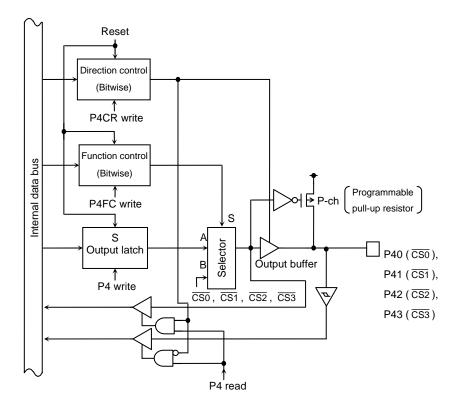

| P30                  | 1              | Output | Port 30: Output only                                                                                                                                                                                                                                                                                                                 |

| RD                   |                | Output | Read strobe: Asserted during a read operation from an external memory device                                                                                                                                                                                                                                                         |

|                      |                |        | Also asserted during a read from internal memory if P3.P30 = 0 and P3FC.P30F = 1                                                                                                                                                                                                                                                     |

| P31                  | 1              | Output | Port 31: Output only                                                                                                                                                                                                                                                                                                                 |

| $\overline{WR}$      |                | Output | Write strobe: Asserted during a write operation on AD0 to AD7                                                                                                                                                                                                                                                                        |

| P32                  | 1              | I/O    | Port 32: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

| HWR                  |                | Output | Higher write strobe: Asserted during a write operation on AD8 to AD15                                                                                                                                                                                                                                                                |

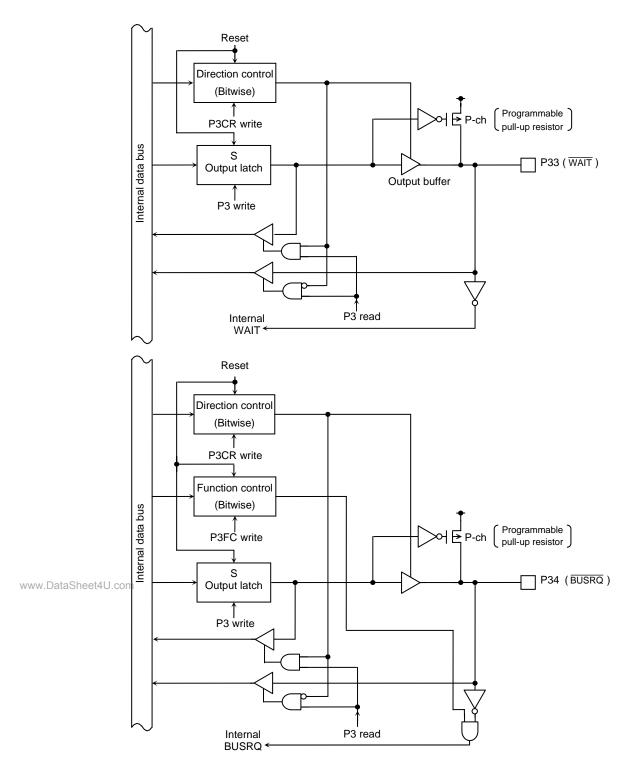

| P33                  | 1              | I/O    | Port 33: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

| WAIT                 |                | Input  | Wait: Causes the CPU to suspend external bus activity ((1 + N) wait states)                                                                                                                                                                                                                                                          |

| P34                  | 1              | I/O    | Port 34: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

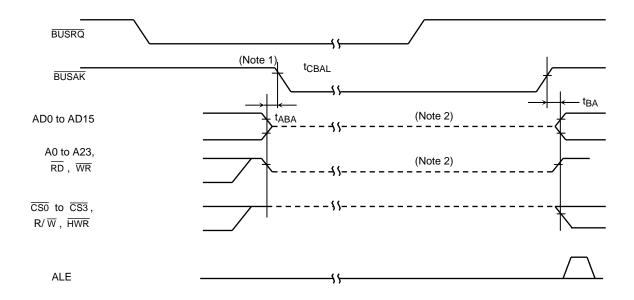

| BUSRQ                |                | Input  | Bus request: Asserted to request that the AD0 to AD15, A0 to A23, $\overline{\text{RD}}$ , $\overline{\text{WR}}$ , $\overline{\text{HWR}}$ , R/ $\overline{\text{W}}$ , and $\overline{\text{CS0}}$ to $\overline{\text{CS3}}$ pins be placed in high-impedance state (for external DMAC)                                           |

| P35                  | 1              | I/O    | Port 35: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

| BUSAK                |                | Output | Bus acknowledge: Indicates that the AD0 to AD15, A0 to A23, $\overline{\text{RD}}$ , $\overline{\text{WR}}$ , $\overline{\text{HWR}}$ , R/ $\overline{\text{W}}$ , and $\overline{\text{CS0}}$ to $\overline{\text{CS3}}$ pins have been placed in high-impedance state in response to $\overline{\text{BUSRQ}}$ (for external DMAC) |

| P36<br>taSheet4U.com | 1              | I/O    | Port 36: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

| R/W                  |                | Output | Read/write: Indicates the direction of data transfer on the bus: 1 = Read or dummy cycle, 0 = Write cycle                                                                                                                                                                                                                            |

| P37                  | 1              | I/O    | Port 37: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

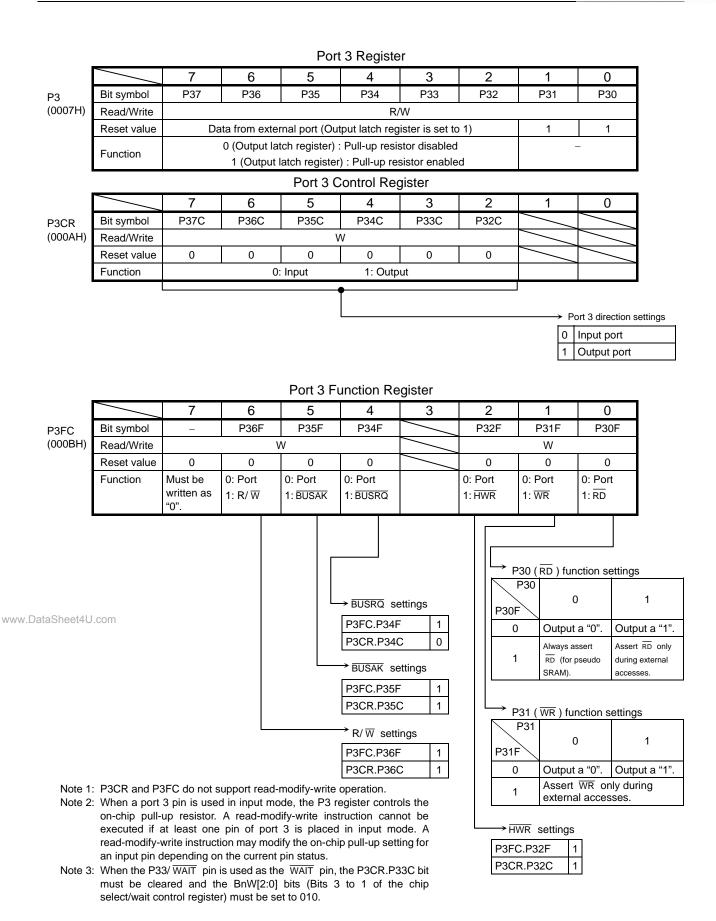

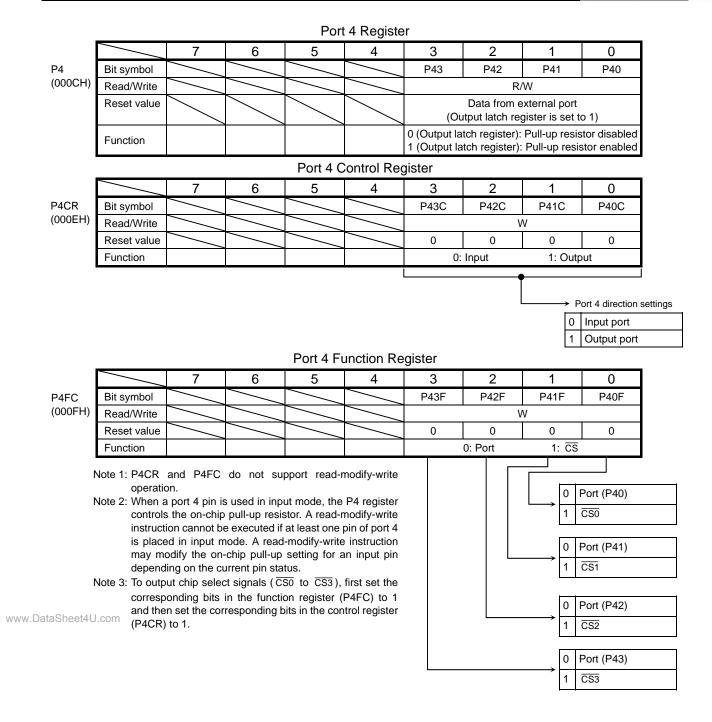

| P40                  | 1              | I/O    | Port 40: Programmable as input or output (with internal pull-up resistor)                                                                                                                                                                                                                                                            |

| CS0                  |                | Output | Chip select 0: Asserted low to enable external devices at programmed addresses                                                                                                                                                                                                                                                       |

www.Date

Note: An external DMA controller configured with the BUSRQ and BUSAK pins cannot access the on-chip memory and peripheral functions of the TMP91CW28.

Table 2.2.2 Pin Names and Functions (2/4)

| Pin Name     | Number of Pins | I/O    | Functions                                                                                                               |

|--------------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| P41          | 1              | I/O    | Port 41: Programmable as input or output (with internal pull-up resistor)                                               |

| CS1          |                | Output | Chip select 1: Asserted low to enable external devices at programmed addresses                                          |

| P42          | 1              | I/O    | Port 42: Programmable as input or output (with internal pull-up resistor)                                               |

| CS2          |                | Output | Chip select 2: Asserted low to enable external devices at programmed addresses                                          |

| P43          | 1              | I/O    | Port 43: Programmable as input or output (with internal pull-up resistor)                                               |

| CS3          |                | Output | Chip select 3: Asserted low to enable external devices at programmed addresses                                          |

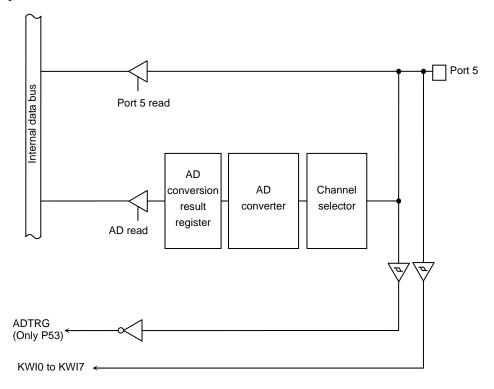

| P50 to P57   | 8              | Input  | Port 5: Input only                                                                                                      |

| AN0 to AN7   |                | Input  | Analog input: Input to the on-chip AD converter                                                                         |

| ADTRG        |                | Input  | AD trigger: Starts an AD conversion (multiplexed with P53)                                                              |

| KWI0 to KWI7 |                | Input  | Key wakeup input (multiplexed with P50 to P57)                                                                          |

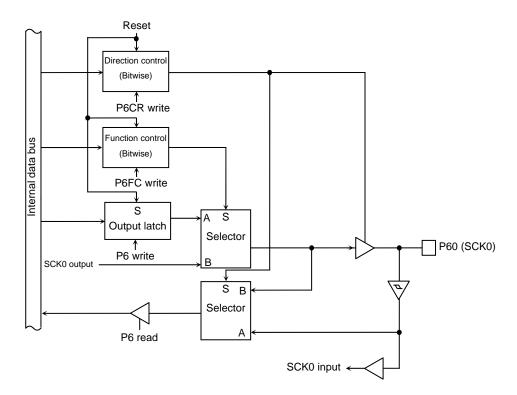

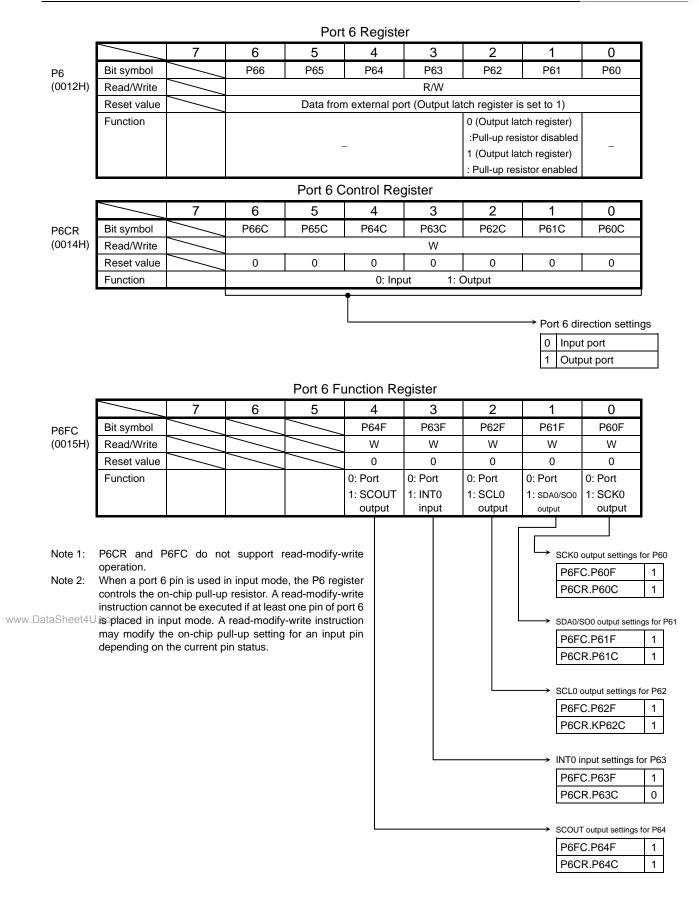

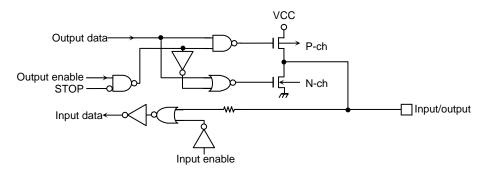

| P60          | 1              | I/O    | Port 60: Programmable as input or output                                                                                |

| SCK0         |                | I/O    | Clock input/output pin when serial bus interface 0 is in SIO mode                                                       |

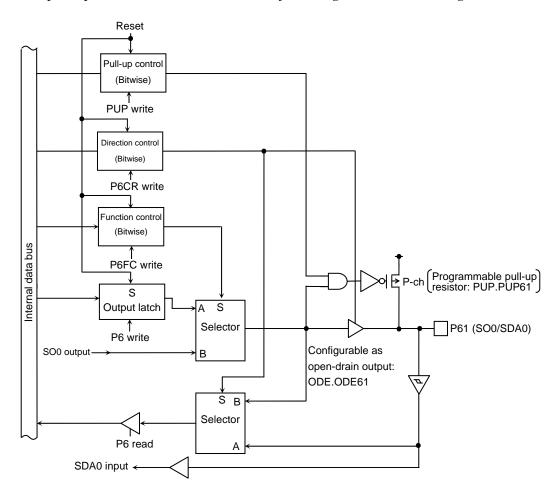

| P61          | 1              | I/O    | Port 61: Programmable as input or output (with internal pull-up resistor)                                               |

| SO0          |                | Output | Data transmit pin when serial bus interface 0 is in SIO mode                                                            |

| SDA0         |                | I/O    | Data transmit/receive pin when serial bus interface 0 is in I <sup>2</sup> C mode; programmable as an open-drain output |

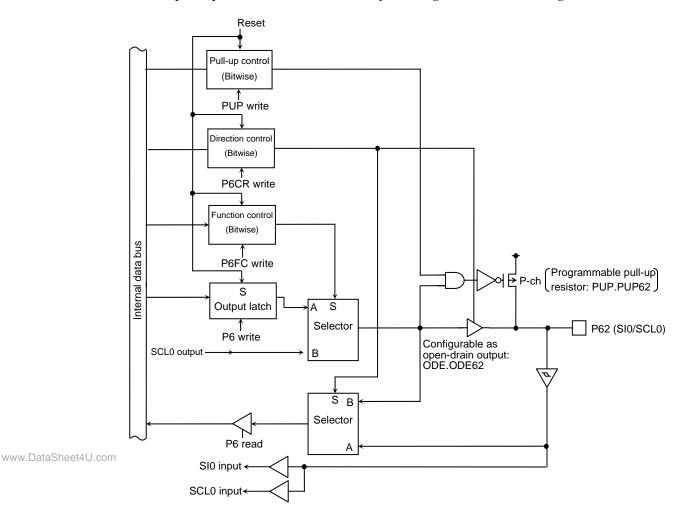

| P62          | 1              | I/O    | Port 62: Programmable as input or output (with internal pull-up resistor)                                               |

| SI0          |                | Input  | Data receive pin when serial bus interface 0 is in SIO mode                                                             |

| SCL0         |                | I/O    | Clock input/output pin when serial bus interface 0 is in I <sup>2</sup> C mode; programmable as an open-drain output    |

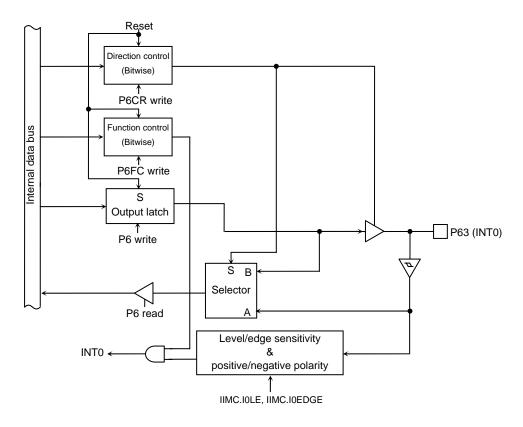

| P63          | 1              | I/O    | Port 63: Programmable as input or output                                                                                |

| INT0         |                | Input  | Interrupt request 0: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive                    |

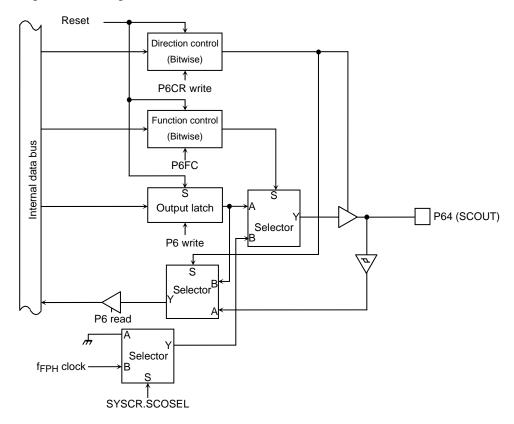

| P64          | 1              | I/O    | Port 64: Programmable as input or output                                                                                |

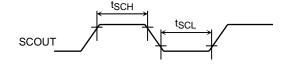

| SCOUT        |                | Output | System clock output: Drives out fFPH clock                                                                              |

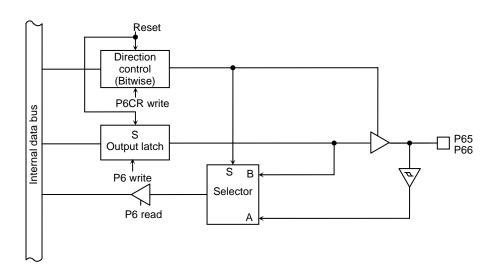

| P65          | 1              | I/O    | Port 65: Programmable as input or output                                                                                |

| P66          | 1              | I/O    | Port 66: Programmable as input or output                                                                                |

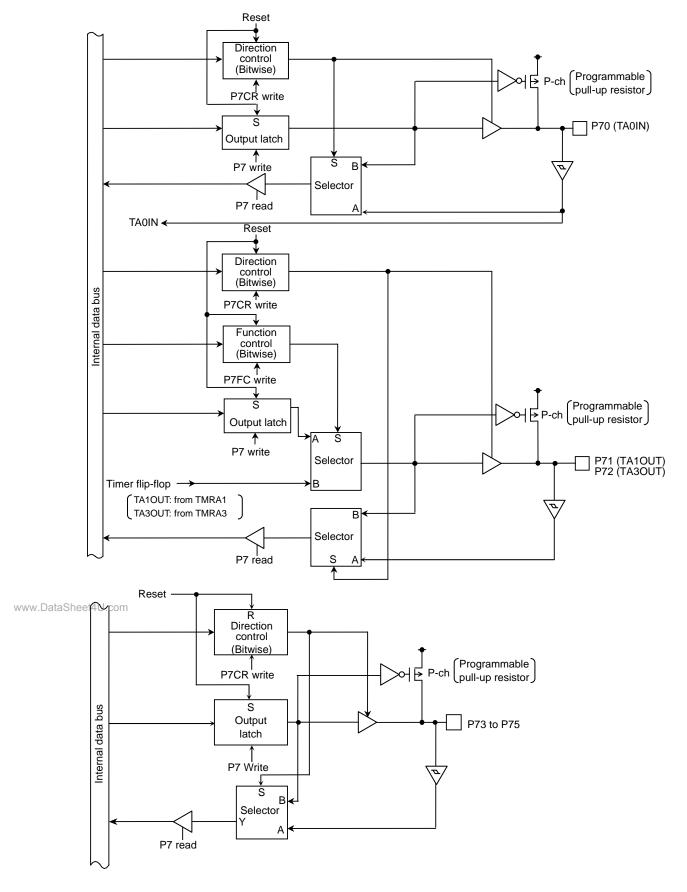

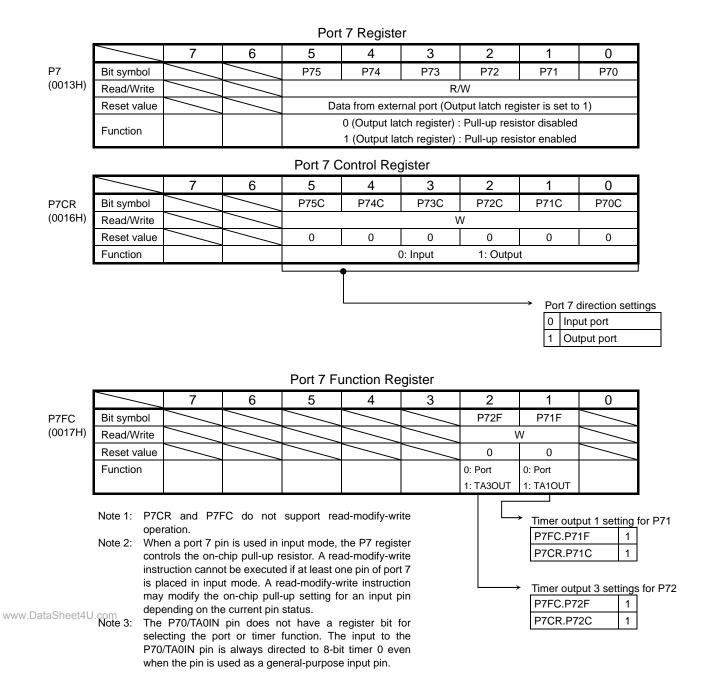

| P70          | 1              | I/O    | Port 70: Programmable as input or output (with internal pull-up resistor)                                               |

| TA0IN        |                | Input  | 8-bit timer 0 input: Input to timer 0                                                                                   |

| P71          | 1              | I/O    | Port 71: Programmable as input or output (with internal pull-up resistor)                                               |

| heatour m    |                | Output | 8-bit timer 1 output: Output from either timer 0 or timer 1                                                             |

| P72          | 1              | I/O    | Port 72: Programmable as input or output (with internal pull-up resistor)                                               |

| TA3OUT       |                | Output | 8-bit timer 3 output: Output from either timer 2 or timer 3                                                             |

www.Data

Table 2.2.3 Pin Names and Functions (3/4)

| Pin Name             | Number of Pins | I/O    | Functions                                                                                                               |

|----------------------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------|

| P73                  | 1              | I/O    | Port 73: Programmable as input or output (with internal pull-up resistor)                                               |

| P74                  | 1              | I/O    | Port 74: Programmable as input or output (with internal pull-up resistor)                                               |

| P75                  | 1              | I/O    | Port 75: Programmable as input or output (with internal pull-up resistor)                                               |

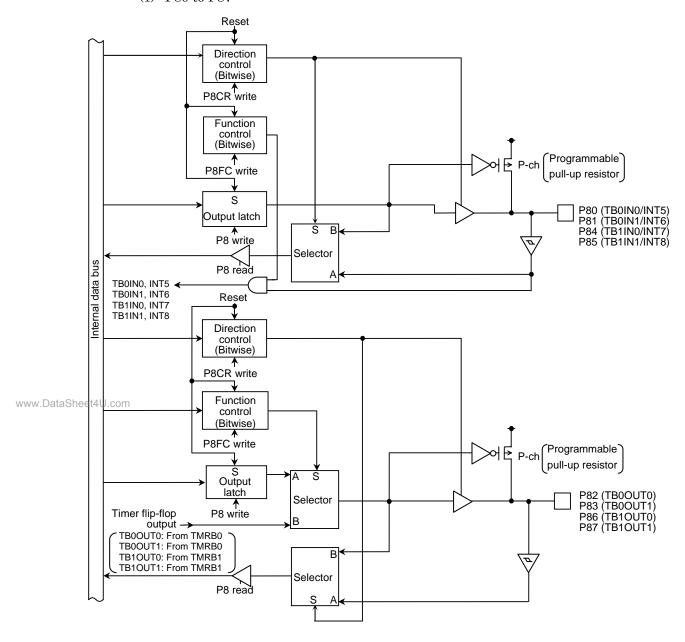

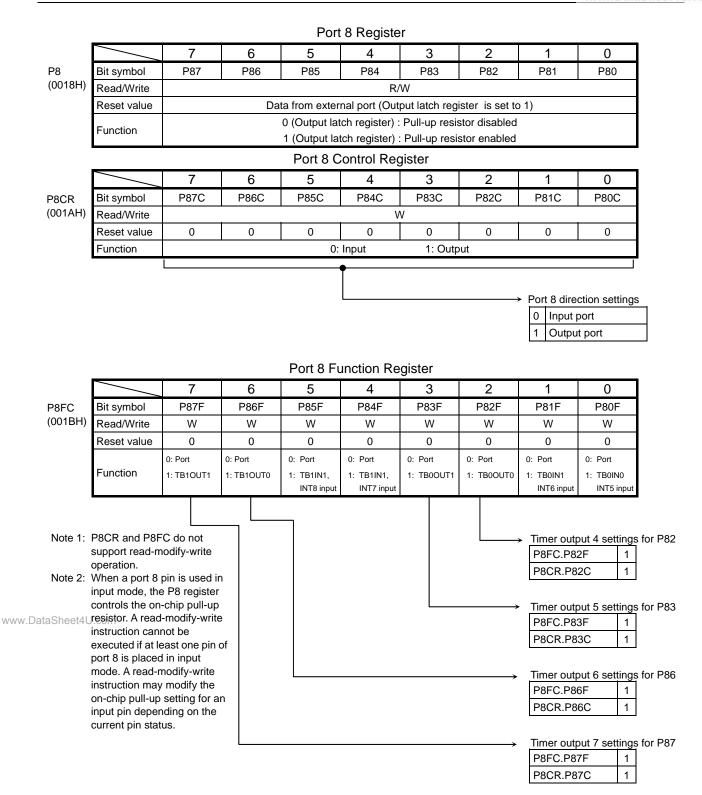

| P80                  | 1              | I/O    | Port 80: Programmable as input or output (with internal pull-up resistor)                                               |

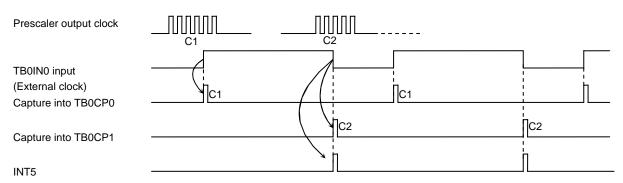

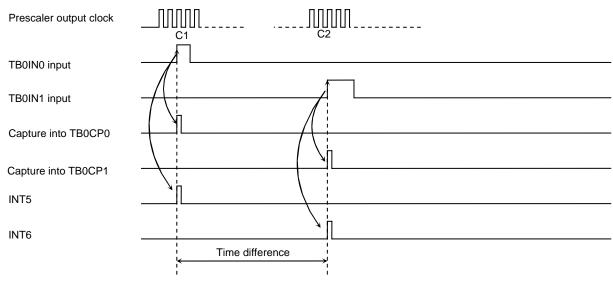

| TB0IN0               |                | Input  | 16-bit timer 0 input 0: Count/capture trigger input to 16-bit timer 0                                                   |

| INT5                 |                | Input  | Interrupt request 5: Programmable to be rising-edge or falling-edge sensitive                                           |

| P81                  | 1              | I/O    | Port 81: Programmable as input or output (with internal pull-up resistor)                                               |

| TB0IN1               |                | Input  | 16-bit timer 0 input 1: Count/capture trigger input to 16-bit timer 0                                                   |

| INT6                 |                | Input  | Interrupt request 6: Rising-edge sensitive                                                                              |

| P82                  | 1              | I/O    | Port 82: Programmable as input or output (with internal pull-up resistor)                                               |

| TB0OUT0              |                | Output | 16-bit timer 0 output 0: Output from 16-bit timer 0                                                                     |

| P83                  | 1              | I/O    | Port 83: Programmable as input or output (with internal pull-up resistor)                                               |

| TB0OUT1              |                | Output | 16-bit timer 0 output 1: Output from 16-bit timer 0                                                                     |

| P84                  | 1              | I/O    | Port 84: Programmable as input or output (with internal pull-up resistor)                                               |

| TB1IN0               |                | Input  | 16-bit timer 1 input 0: Count/capture trigger input to 16-bit timer 1                                                   |

| INT7                 |                | Input  | Interrupt request 7: Programmable to be rising-edge or falling-edge sensitive                                           |

| P85                  | 1              | I/O    | Port 85: Programmable as input or output (with internal pull-up resistor)                                               |

| TB1IN1               |                | Input  | 16-bit timer 1 input 1: Count/capture trigger input to 16-bit timer 1                                                   |

| INT8                 |                | Input  | Interrupt request 8: Rising-edge sensitive                                                                              |

| P86                  | 1              | I/O    | Port 86: Programmable as input or output (with internal pull-up resistor)                                               |

| TB1OUT0              |                | Output | 16-bit timer 1 output 0: Output from 16-bit timer 1                                                                     |

| P87                  | 1              | I/O    | Port 87: Programmable as input or output (with internal pull-up resistor)                                               |

| TB1OUT1              |                | Output | 16-bit timer 1 output 1: Output from 16-bit timer 1                                                                     |

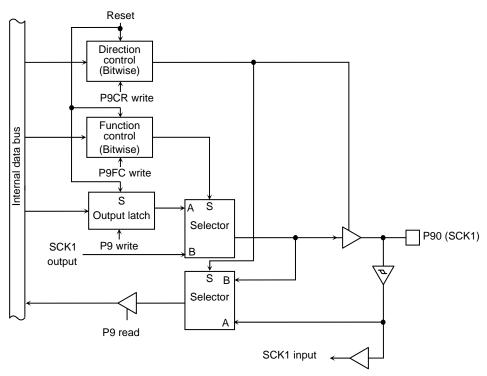

| P90                  | 1              | I/O    | Port 90: Programmable as input or output                                                                                |

| SCK1                 |                | I/O    | Clock input/output pin when serial bus interface 1 is in SIO mode                                                       |

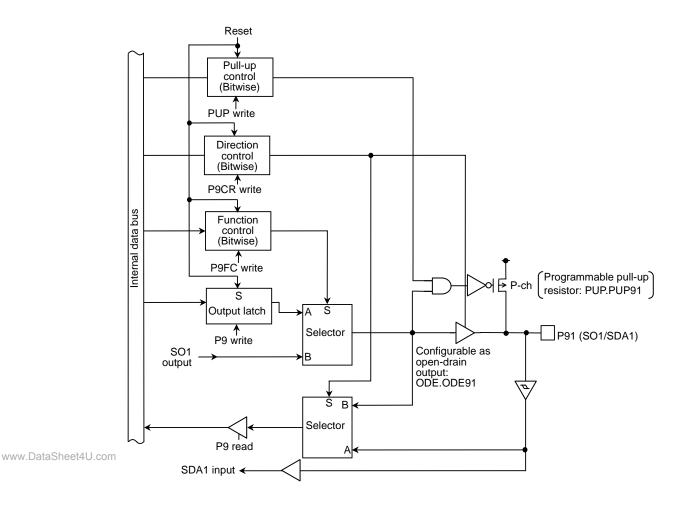

| P91                  | 1              | I/O    | Port 91: Programmable as input or output (with internal pull-up resistor)                                               |

| SO1                  |                | Output | Data transmit pin when serial bus interface 1 is in SIO mode                                                            |

| SDA1                 |                | I/O    | Data transmit/receive pin when serial bus interface 1 is in I <sup>2</sup> C mode; programmable as an open-drain output |

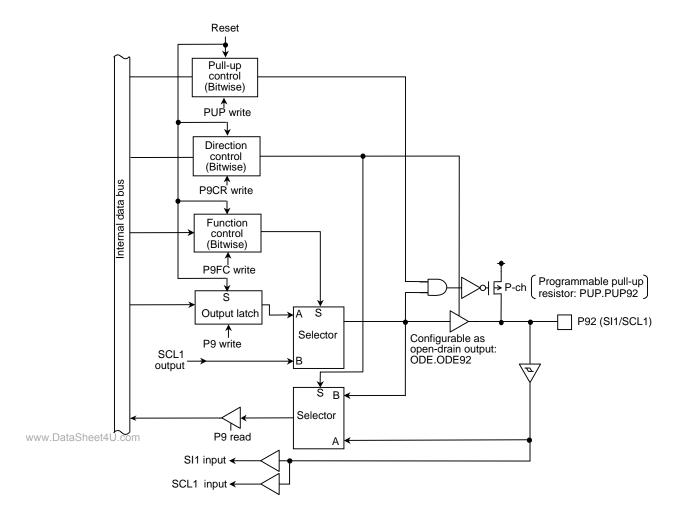

| P92                  | 1              | I/O    | Port 92: Programmable as input or output (with internal pull-up resistor)                                               |

| SI1                  |                | Input  | Data receive pin when serial bus interface 1 is in SIO mode                                                             |

| SCL1<br>\$heet4U.com |                | I/O    | Clock input/output pin when serial bus interface 1 is in I <sup>2</sup> C mode; programmable as an open-drain output    |

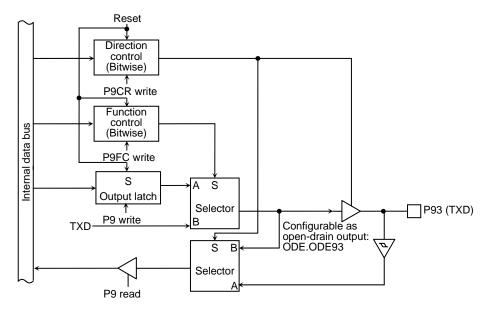

| P93                  | 1              | I/O    | Port 93: Programmable as input or output                                                                                |

| TXD                  |                | Output | Serial transmit data: Programmable as an open-drain output                                                              |

www.Data

Table 2.2.4 Pin Names and Functions (4/4)

| Pin Name     | Number of Pins | I/O    | Functions                                                                                                                                |

|--------------|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------|

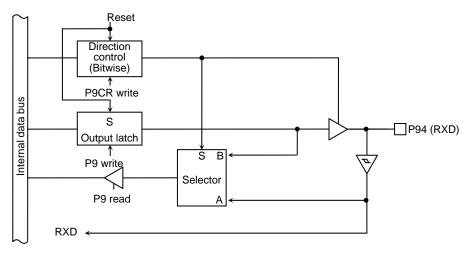

| P94          | 1              | I/O    | Port 94: Programmable as input or output                                                                                                 |

| RXD          |                | Input  | Serial receive data                                                                                                                      |

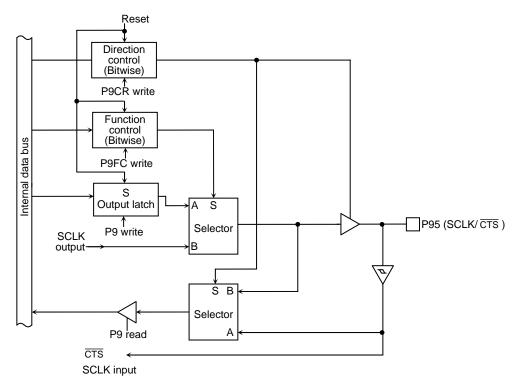

| P95          | 1              | I/O    | Port 95: Programmable as input or output                                                                                                 |

| SCLK         |                | I/O    | Serial clock input/output                                                                                                                |

| CTS          |                | Input  | Serial clear-to-send                                                                                                                     |

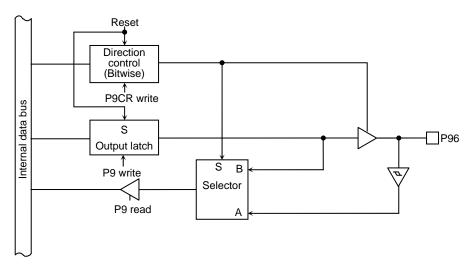

| P96          | 1              | I/O    | Port 96: Programmable as input or output                                                                                                 |

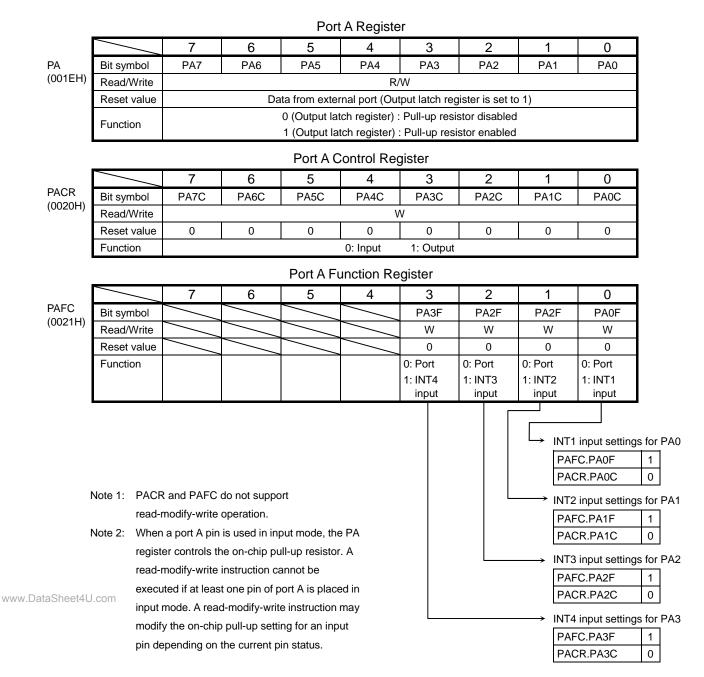

| PA0 to PA3   | 4              | I/O    | Ports A0 to A3: Individually programmable as input or output (with internal pull-up resistor)                                            |

| INT1 to INT4 |                | Input  | Interrupt request 1 to 4: Individually programmable to be rising-edge or falling-edge sensitive                                          |

| PA4 to PA7   | 4              | I/O    | Ports A4 to A7: Individually programmable as input or output (with internal pull-up resistor)                                            |

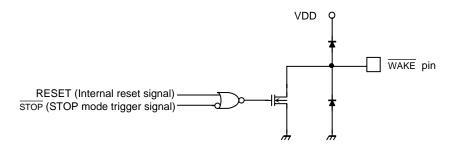

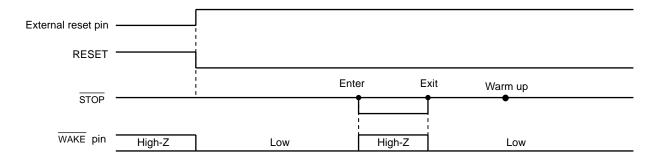

| WAKE         | 1              | Output | STOP mode monitor output This pin drives low when the CPU is operating; the pin is in high-impedance state during reset or in STOP mode. |

| ALE          | 1              | Output | Address latch enable (This pin can be disabled in order to reduce noise.)                                                                |

| NMI          | 1              | Input  | Nonmaskable interrupt request: Causes an NMI interrupt on the falling edge; programmable to be rising-edge sensitive                     |

| AM0 to AM1   | 2              | Input  | Both AM0 and AM1 should be held at logic 1.                                                                                              |

| EMU0         | 1              | Output | Test pin. This pin should be left open.                                                                                                  |

| EMU1         | 1              | Output | Test pin. This pin should be left open.                                                                                                  |

| RESET        | 1              | Input  | Reset (with internal pull-up resistor): Initializes the whole TMP91CW28.                                                                 |

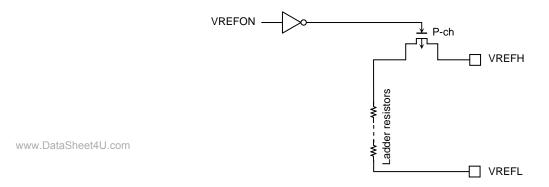

| VREFH        | 1              | Input  | Input pin for high reference voltage for the AD converter                                                                                |

| VREFL        | 1              | Input  | Input pin for low reference voltage for the AD converter                                                                                 |

| AVCC         | 1              |        | Power supply pin for the AD converter                                                                                                    |

| AVSS         | 1              |        | Ground pin for the AD converter                                                                                                          |

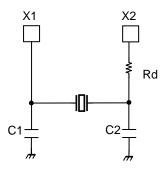

| X1/X2        | 2              | I/O    | Connection pins for a crystal oscillator                                                                                                 |

| DVCC         | 3              |        | Power supply pins. The DVCC pins should be connected to power supply.                                                                    |

| DVSS         | 3              |        | Ground pins. The DVSS pins should be connected to ground.                                                                                |

Note: All pins that have built-in pull-up resistors (other than the RESET pin) can be disconnected from the built-in pull-up resistor by software.

TOSHIBA www.DataSheetau.com

# 3. Operation

This section describes the functions and basic operation of each block constituting the TMP91CW28.

See also section 7, "Points of Note and Restrictions" for an explanation of precautions and restrictions for individual blocks.

#### 3.1 CPU

The TMP91CW28 contains a high-performance 16-bit CPU called the 900/L1. For a detailed description of the CPU, refer to "TLCS-900/L1 CPU" in the preceding chapter.

Functions unique to the TMP91CW28, which are not covered in "TLCS-900/L1 CPU", are described below.

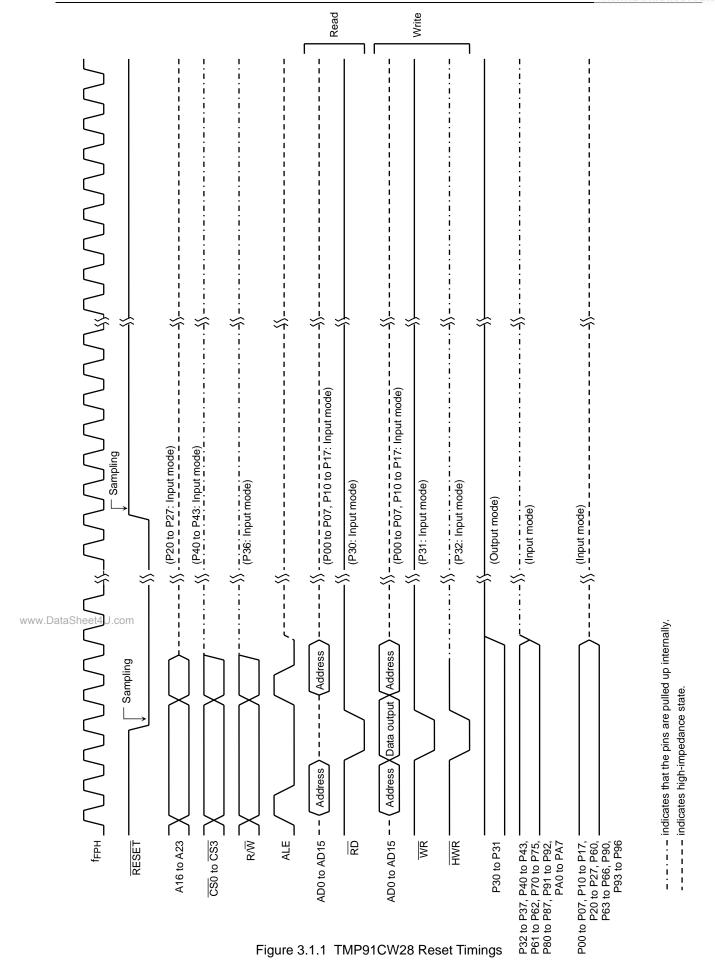

#### 3.1.1 Reset Operation

When resetting the TMP91CW28 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then set the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks (32  $\mu$ s at 10 MHz).

Thus, when turn on the switch, be set to the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks.

Clock gear is initialized 1/16 mode by reset operation. It means that the system clock mode fsys is set to fc/32 (=  $fc/16 \times 1/2$ ).

The CPU performs the following operations as a result of a reset:

Set the program counter (PC) according to the reset vectors stored at addresses FFFF00H to FFFF02H

PC [7:0]  $\leftarrow$  Value at FFFF00H

PC [15:8]  $\leftarrow$  Value at FFFF01H

PC [23:16]  $\leftarrow$  Value at FFFF02H

- Set the stack pointer (XSP) to 100H.

- Set the IFF2 to IFF0 bits of the status register (SR) to 111 (Setting the interrupt level mask register to level 7).

- Set the MAX bit of the status register (SR) to 1 (Selecting maximum mode).

- Clear the RFP2 to RFP0 bits of the status register (SR) to 000 (Selecting register bank0).

After a reset, the CPU starts executing instructions according to the set PC. CPU internal registers other than the above are not modified.

The on-chip I/O peripherals, ports and other pins are initialized as follows upon a reset.

- All on-chip I/O peripheral registers are initialized.

- All port pins, including those multiplexed with on-chip peripheral functions, are configured as either general-purpose inputs or general-purpose outputs.

- The ALE pin is placed in high-impedance state.

Note: A reset operation does not affect the contents of the on-chip RAM or the CPU registers other than PC, SR and XSP.

Figure 3.1.1 shows TMP91CW28 reset timings.

www.DataSheet4U.com

91CW28-9 2006-03-24

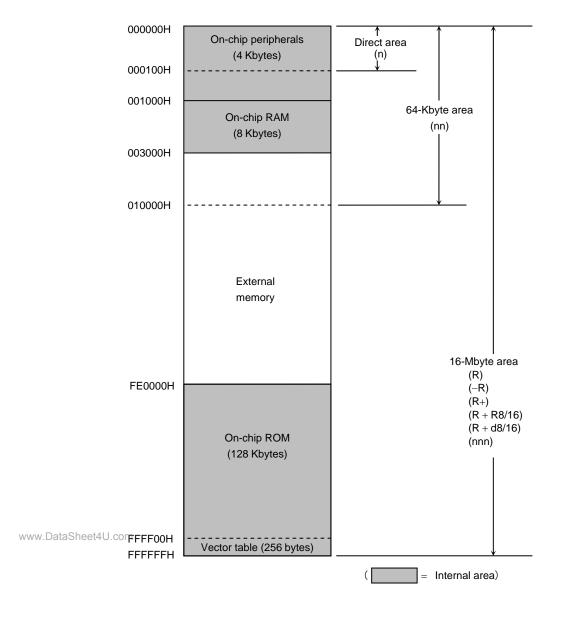

# 3.2 Memory Map

Figure 3.2.1 shows memory assignment for the TMP91CW28.

Figure 3.2.1 Memory Map

TOSHIBA www.batasheetau.com

# 3.3 Standby Control and Noise Reduction

The TMP91CW28 incorporates clock gear, standby control and noise reduction circuits to minimize power consumption as well as noise.

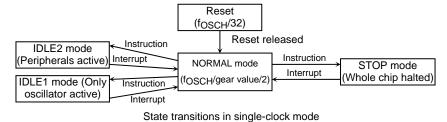

The TMP91CW28 only supports single-clock mode, in which it operates off of the clock supplied from the X1 and X2 pins.

Figure 3.3.1 shows state transitions in single-clock mode.

Figure 3.3.1 State Transitions in Single-clock Mode

f<sub>OSCH</sub>: Clock frequency supplied via the X1 and X2 pins f<sub>FPH</sub>: Clock frequency selected by the GEAR[2:0] bit in the SYSCR1 f<sub>SYS</sub>: System clock frequency, created by dividing f<sub>FPH</sub> by two 1 state: One period of f<sub>SYS</sub>

**TOSHIBA**

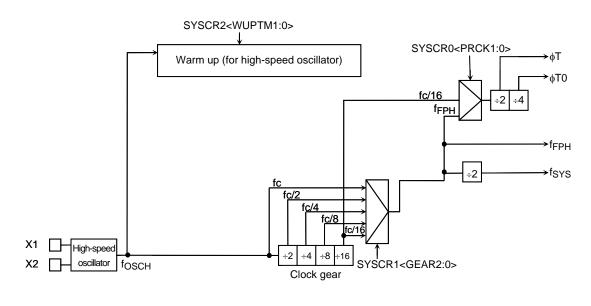

# 3.3.1 Clock Source Block Diagram

Figure 3.3.2 Clock and Standby Block Diagram

# 3.3.2 SFR Descriptions

|         |             | 7               | 6                   | 5                         | 4               | 3                               | 2                            | 1                    | 0             |  |

|---------|-------------|-----------------|---------------------|---------------------------|-----------------|---------------------------------|------------------------------|----------------------|---------------|--|

| SYSCR0  | Bit symbol  | _               | -                   | -                         | -               | -                               | -                            | PRCK1                | PRCK0         |  |

| (00E0H) | Read/Write  |                 |                     | W                         |                 |                                 |                              | R/W                  |               |  |

|         | Reset value | 1               | 0                   | 1                         | 0               | 0                               | 0                            | 0                    | 0             |  |

|         | Function    | Must be         | Must be             | Must be                   | Must be         | written as                      | Must be                      | Prescaler cl         | ock select    |  |

|         |             | written as "1". | written as          | written as                | written as "0". |                                 | written as                   | 00: f <sub>FPH</sub> |               |  |

|         |             | 1.              | "0".                | "1".                      | 0.              |                                 | "0".                         | 01: Reserv           | ed            |  |

|         |             |                 |                     |                           |                 |                                 |                              | 10: fc/16            |               |  |

|         |             |                 |                     |                           |                 |                                 |                              | 11: Reserv           | ed            |  |

| SYSCR1  | Bit symbol  |                 |                     |                           |                 | _                               | GEAR2                        | GEAR1                | GEAR0         |  |

| (00E1H) | Read/Write  |                 |                     |                           |                 | W                               |                              | R/W                  |               |  |

|         | Reset value |                 |                     |                           |                 | 0                               | 1                            | 0                    | 0             |  |

|         | Function    |                 |                     |                           |                 | Must be                         | High-speed clock gear select |                      |               |  |

|         |             |                 |                     |                           |                 | written as "0".                 | 000: High-speed clock        |                      |               |  |

|         |             |                 |                     |                           |                 |                                 | 001: High-s                  | speed clock /:       | 2             |  |

|         |             |                 |                     |                           |                 |                                 | 010: High-speed clock /4     |                      |               |  |

|         |             |                 |                     |                           |                 |                                 | 011: High-speed clock /8     |                      |               |  |

|         |             |                 |                     |                           |                 |                                 | 100: High-speed clock /16    |                      |               |  |

|         |             |                 |                     |                           |                 |                                 | 101: Reser                   | ved                  |               |  |

|         |             |                 |                     |                           |                 |                                 | 110: Reser                   | ved                  |               |  |

|         |             |                 |                     |                           |                 |                                 | 111: Reser                   | ved                  |               |  |

| SYSCR2  | Bit symbol  |                 | SCOSEL              | WUPTM1                    | WUPTM0          | HALTM1                          | HALTM0                       |                      | DRVE          |  |

| (00E2H) | Read/Write  |                 | R/W                 | R/W                       | R/W             | R/W                             | R/W                          |                      | R/W           |  |

|         | Reset value |                 | 0                   | 1                         | 0               | 1                               | 1                            |                      | 0             |  |

|         | Function    |                 | SCOUT               | Oscillator wa             | ırm-up time     | HALT mode                       | e select                     |                      | 1: Pins are   |  |

|         |             |                 | output              | 00: Reserved              |                 | 00: Reserved                    |                              |                      | driven in     |  |

|         |             |                 | 0: Low              | 01: 2 <sup>8</sup> /input |                 | 01: STOP mode<br>10: IDLE1 mode |                              |                      | STOP<br>mode. |  |

|         |             |                 | level               |                           | it frequency    |                                 |                              | moue.                |               |  |

|         |             |                 | 1: f <sub>FPH</sub> | 11: 2 <sup>16</sup> /inpu | it frequency    | 11: IDLE2 i                     | mode                         |                      |               |  |

Note 1: Bits7 to 2 of the SYSCR0, bits7 to 4 of the SYSCR1 and bits7 and 1 of the SYSCR2 are read as undefined. Note 2: When the on-chip SBI is used, the prescaler select register, SYSCR0.PRCK[1:0], must be set to 00 (f<sub>FPH</sub>).

Figure 3.3.3 Clock-related SFRs

|         |             | 7                                                                      | 6                   | 5                   | 4                   | 3                           | 2                            | 1                   | 0                   |  |  |

|---------|-------------|------------------------------------------------------------------------|---------------------|---------------------|---------------------|-----------------------------|------------------------------|---------------------|---------------------|--|--|

| EMCCR0  | Bit symbol  | PROTECT                                                                | 1                   | -                   | -                   | ALEEN                       | EXTIN                        | -                   | -                   |  |  |

| (00E3H) | Read/Write  | R                                                                      | R/W                 | R/W                 | R/W                 | R/W                         | R/W                          | R/W                 | R/W                 |  |  |

|         | Reset value | 0                                                                      | 0                   | 1                   | 0                   | 0                           | 0                            | 1                   | 1                   |  |  |

|         | Function    | Protection<br>flag<br>0: Disabled<br>1: Enabled                        | Must be set to "0". | Must be set to "1". | Must be set to "0". | 1: ALE<br>output<br>enabled | 1: External clock used as fc | Must be set to "1". | Must be set to "1". |  |  |

| EMCCR1  | Bit symbol  | -                                                                      |                     |                     |                     |                             |                              |                     |                     |  |  |

| (00E4H) | Read/Write  |                                                                        |                     |                     | V                   | V                           |                              |                     |                     |  |  |

|         | Reset value |                                                                        |                     |                     | =                   | =                           |                              |                     |                     |  |  |

|         | Function    | On writes: 1FH: Protection disabled Other than 1FH: Protection enabled |                     |                     |                     |                             |                              |                     |                     |  |  |

Figure 3.3.4 Noise-related SFRs

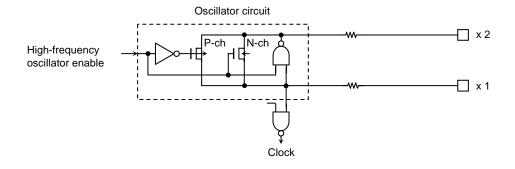

## 3.3.3 System Clock Control Section

The system clock control section generates system clock pulses (f<sub>SYS</sub>) that are supplied to the CPU core and on-chip peripherals. It accepts the fc clock pulses, output from the high-speed oscillator, and uses the SYSCR1.GEAR[2:0] bits to gear down the high-speed clock frequency to fc, fc/2, fc/4, fc/8, or fc/16, thus enabling reduction in power consumption.

A system reset initializes the SYSCR1.GEAR[2:0] bits to 100, putting the TMP91CW28 in single-clock mode. The system clock frequency (fsys) is geared down to fc/32 (= fc/16  $\times$  1/2). For example, if a 10 MHz crystal is connected between the X1 and X2 pins, the fsys clock operates at 0.3125 MHz.

#### (1) Changing the clock gear

The clock gear select register SYSCR1.GEAR[2:0] can be used to set f<sub>FPH</sub> to fc, fc/2, fc/4, fc/8 or fc/16. Gearing down f<sub>FPH</sub> results in smaller power consumption.

The following shows an example of changing the clock gear:

# Example:

```

Gearing down the high-speed clock frequency

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0000B ; Changes system clock f<sub>SYS</sub> to fc/2.

X: Don't care

```

There is one thing to remember when changing the clock gear value.

The clock gear can be changed by the programming of the GEAR[2:0] bits of the SYSCR1, as shown in the above example. It takes a few clock cycles for a gear change to take effect. Therefore, one or more instructions following the instruction that changed the clock gear value may be executed using the old clock gear value. If subsequent instructions need be executed with a new clock gear value, a dummy instruction (one that executes a write cycle, as shown below) should be inserted after the instruction that modifies the clock gear value.

```

Example:

SYSCR1 EQU 00E1H

LD (SYSCR1), XXXX0001B ; Changes f<sub>SYS</sub> to fc/4.

LD (DUMMY), 00H ; Dummy instruction.

Instructions that need be executed with a new clock gear value

```

## (2) Internal clock output

The fFPH internal clock can be driven out from the P64/SCOUT pin.

The P64/SCOUT pin is configured as SCOUT (System clock output) by programming the port 6 registers as follows: P6CR.P64C = 1 and P6FC.P64F = 1. The output clock is selected through the SYSCR2.SCOSEL bit.

Table 3.3.1 shows the pin states in each clocking mode when the P64/SCOUT pin is configured as SCOUT.

Table 3.3.1 SCOUT Output States

| Mode         | NORMAL                     | HALT Modes       |               |             |  |  |  |

|--------------|----------------------------|------------------|---------------|-------------|--|--|--|

| SCOUT Select | NORMAL                     | IDLE2            | IDLE1         | STOP        |  |  |  |

| SCOSEL = 0   |                            | A low level i    | s driven out. |             |  |  |  |

| SCOSEL = 1   | The f <sub>FPH</sub> clock | k is driven out. | Held at eit   | her 1 or 0. |  |  |  |

#### 3.3.4 Prescaler Clock Control Section

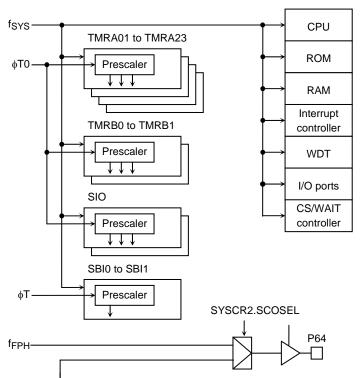

The on-chip peripherals (TMRA01 to TMRA23, TMRB0, TMRB1, SIO, SBI0 and SBI1) have a clock prescaler.

The prescaler clock source ( $\phi T$ ,  $\phi T0$ ) can be selected from either fFPH or fc/16 through the PRCK[1:0] bits of the SYSCR0. The selected clock frequency (fFPH or fc/16) is divided by two or four before being supplied to the prescaler.

When the on-chip SBI is used, PRCK[1:0] must be cleared to 00.

#### 3.3.5 Noise Cancellers

The TMP91CW28 incorporates circuits providing the following features in order to reduce electromagnetic interference (EMI) and improve electromagnetic susceptibility (EMS):

- (1) Canceling double-drive operation of the high-speed oscillator

- (2) Disabling output from the ALE pin

- (3) Preventing software or system lockups

These features can be selected using the EMCCR0 and EMCCR1 registers.

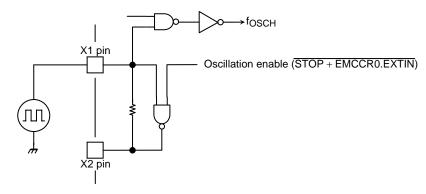

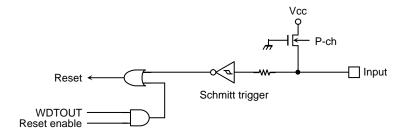

(1) Canceling double-drive operation of the high-speed oscillator

#### Purpose:

To prevent malfunction due to noise coming through the X2 pin that is open when an external oscillator is used, with double-drive operation not required.

#### Block diagram:

www.DataSheet4U.com

#### Description:

Setting the EXTIN bit of the EMCCR0 to 1 causes the high-speed oscillator to stop oscillation and operate as a buffer, with the X2 pin driven high.

A system reset initializes the EXTIN bit to 0.

Note: Do not write EMCCR0<EXTIN> = "1" when using external resonator.

2006-03-24

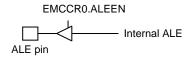

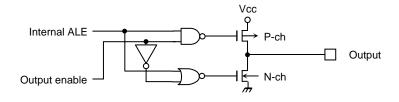

# (2) Disabling output from the ALE pin

## Purpose:

To prevent unwanted clock noise from being driven out when no external area is accessed.

## Block diagram:

## Description:

Clearing the ALEEN bit of the EMCCR0 to 0 disables the output buffer of the ALE pin, placing the pin into high-impedance state.

A system reset initializes the ALEEN bit to 0.

When accessing an external area, set ALEEN to 1 before attempting to access the area.

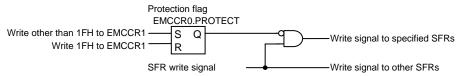

(3) Preventing software or system lockups using a protection register

#### Purpose:

To prevent software or system lockups that may occur due to incoming noise.

Applying protection causes specified SFRs to be write-protected, thus preventing the system recovery routine from becoming unfetchable, for example, if the system clock stops or a memory control register (CS/WAIT controller) is modified.

#### Applicable SFRs

- 1. CS/WAIT controller B0CS, B1CS, B2CS, B3CS, BEXCS, MSAR0, MSAR1, MSAR2, MSAR3, MAMR0, MAMR1, MAMR2, MAMR3

- 2. Clock gear (Only EMCCR1 can be written.) SYSCR0, SYSCR1, SYSCR2, EMCCR0

## Block diagram:

#### Description:

Writing any code other than 1FH to the EMCCR1 register enables protection, thus preventing specified SFRs from being written.

Writing 1FH to the EMCCR1 register cancels protection. The state of protection can be determined by reading the PROTECT bit of the EMCCR0.

A system reset cancels protection.

# 3.3.6 Standby Control Section

# (1) HALT mode

Executing the HALT instruction causes the TMP91CW28 to enter one of the HALT modes – IDLE2, IDLE1 or STOP – as specified by the SYSCR2.HALTM[1:0] bits.

The characteristics of the IDLE2, IDLE1 and STOP modes are as follows.

a. IDLE2: The CPU stops.

On-chip peripherals can be selectively enabled and disabled through use of a register bit in an SFR, as shown in Table 3.3.2.

Table 3.3.2 IDLE2 Mode Register Settings

| Peripheral | SFR            |

|------------|----------------|

| TMRA01     | TA01RUN.I2TA01 |

| TMRA23     | TA23RUN.I2TA23 |

| TMRB0      | TB0RUN.I2TB0   |

| TMRB1      | TB1RUN.I2TB1   |

| SIO        | SC0MOD1.I2S0   |

| SBI0       | SBI0BR0.I2SBI0 |

| SBI1       | SBI1BR0.I2SBI1 |

| ADC        | ADMOD1.I2AD    |

| WDT        | WDMOD.I2WDT    |

- b. IDLE1: Only the on-chip oscillator is operational.

- c. STOP: The whole TMP91CW28 stops.

Table 3.3.3 shows the operation of each circuit block in HALT modes.

Table 3.3.3 TMP91CW28 Circuit Blocks in HALT Modes

|              |       | 10010 01010 1111      | 1 0101120 Olloak Blooks III 1            | , ter medee       |                                   |  |

|--------------|-------|-----------------------|------------------------------------------|-------------------|-----------------------------------|--|

|              |       | HALT Mode             | IDLE2                                    | IDLE1             | STOP                              |  |

| www.DataShee | t4U.c | com SYSCR2.HALTM[1:0] | 11                                       | 10                | 01                                |  |

|              |       | CPU                   |                                          | OFF               |                                   |  |

|              | 쏭     | I/O ports             | Holding the states when the HAL executed | T instruction was | See Table 3.3.6<br>to Table 3.3.9 |  |

|              | block | TMRA, TMRB            |                                          |                   |                                   |  |

|              | cuit  | SIO, SBI              | Selectable programmatically on           |                   |                                   |  |

|              | Cir   | ADC                   | a block-by-block basis                   | OFF               |                                   |  |

|              |       | WDT                   |                                          |                   |                                   |  |

|              |       | Interrupt controller  | ON                                       |                   |                                   |  |

## (2) Wakeup signaling

There are two ways to exit a HALT mode: An interrupt request or reset signal. Availability of wakeup signaling depends on the settings of the interrupt mask level bits, IFF[2:0], of the CPU status register (SR) and the current HALT mode (See Table 3.3.4).

#### • Wakeup via interrupt signaling

The operation upon return from a HALT mode varies, depending on the interrupt priority level programmed before executing the HALT instruction. If the interrupt priority level is greater than or equal to the processor's interrupt mask level, execution resumes with the interrupt service routine. Upon completion of the interrupt service routine, program execution resumes with the instruction immediately following the HALT instruction. If the interrupt priority level is less than the processor's interrupt mask level, the HALT mode is not terminated. (Nonmaskable interrupts are always serviced upon return from a HALT mode, regardless of the current interrupt mask level.)

Only interrupts INT0 to INT4 can, however, terminate a HALT mode even if the interrupt priority level is less than the processor's interrupt mask level. In that case, program execution resumes with the instruction immediately following the HALT instruction, without executing the interrupt service routine. The interrupt request flag remains set.

#### Wakeup via reset signaling

Reset signaling always brings the TMP91CW28 out of any HALT mode. A wakeup from STOP mode must allow sufficient time for the oscillator to restart and stabilize (See Table 3.3.5).

A reset does not affect the contents of the on-chip RAM, but initializes everything else, whereas an interrupt preserves all internal states that were in effect before the HALT mode was entered.

|           |           | Interrupt Masking               | Unmasked<br>(Request_level≥     |       |            | Masked Interrupt (Request_level < mask_level) |       |                 |  |  |

|-----------|-----------|---------------------------------|---------------------------------|-------|------------|-----------------------------------------------|-------|-----------------|--|--|

|           |           | HALT Mode                       | Programmable IDLE2              | IDLE1 | STOP       | Programmable IDLE2                            | IDLE1 | STOP            |  |  |

|           |           | NMI                             | •                               | •     | <b>*</b> 1 | -                                             | -     | _               |  |  |

|           |           | INTWDT                          | •                               | ×     | ×          | -                                             | -     | _               |  |  |

| ces       |           | INT0 to 4 (Note 1)              | •                               | •     | <b>*</b> 1 | 0                                             | 0     | o <sup>*1</sup> |  |  |

| sonrces   | S         | INT5 to INT8                    | ♦ (Note 2)                      | ×     | ×          | ×                                             | ×     | ×               |  |  |

|           | nterrupts | INTTA0 to INTTA3                | •                               | ×     | ×          | ×                                             | ×     | ×               |  |  |

| signaling | nter      | INTTB00 to 01, 10, 11, OF0, OF1 | •                               | ×     | ×          | ×                                             | ×     | ×               |  |  |

|           |           | INTRX, INTTX                    | •                               | ×     | ×          | ×                                             | ×     | ×               |  |  |

| Wakeup    |           | INTSBI0 to 1                    | •                               | ×     | ×          | ×                                             | ×     | ×               |  |  |

| ×         |           | INTAD                           | •                               | ×     | ×          | ×                                             | ×     | ×               |  |  |

|           |           | INTBCD                          | •                               | ×     | ×          | ×                                             | ×     | ×               |  |  |

|           |           | RESET                           | Initializes the whole TMP91CW28 |       |            |                                               |       |                 |  |  |

Table 3.3.4 Wakeup Signaling Sources and Wakeup Operations

- ♦: Execution resumes with the interrupt service routine. (RESET initializes the whole TMP91CW28.)

- o: Execution resumes with the instruction immediately following the HALT instruction. The interrupt is left pending.

- x: Cannot be used to exit a HALT mode.

- -: These combinations are not possible because nonmaskable interrupts are assigned a highest priority level (7).

- \*1: The TMP91CW28 exits the HALT mode after the warm-up period timer expires.

- Note 1: If the interrupt request level is greater than the mask level, an INT0 interrupt signal which is programmed as level-sensitive must be held high until interrupt processing begins. Otherwise, the interrupt will not be serviced successfully.

- Note 2: When external INT5 to INT8 interrupts are used in programmable IDLE2 mode, 16-bit timer run register bits TB0RUN.I2TB0 and TB1RUN.I2TB1 must be set to 1.

${\tt www.DataSheet 4U. \ref{thm:mode:example} \ of \ exiting \ a \ HALT \ mode:}$

820FH

ĹD

XX, XX

When using an edge-sensitive INT0 interrupt to exit IDLE1 mode Address 8200H LD (PAFC), 01H Set PA0 to INT0. 8203H LD (IIMC), 00H Set INT0 interrupt to rising-edge sensitive. 8206H ΙD (INTE0AD), 06H Set INT0 interrupt priority level to 6. 8209H ΕI Set CPU interrupt priority level to 5. 820BH LD (SYSCR2), 28H Select IDLE1 mode. 820EH HALT Stop CPU. INT0 → INT0 interrupt service routine RETI

## (3) Operation in HALT modes

#### a. IDLE2 mode

In IDLE2 mode, the CPU stops executing instructions and only the on-chip peripherals enabled with the IDLE2 setting bits in respective SFRs are operational.

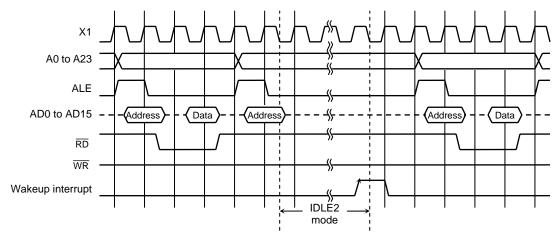

Figure 3.3.5 shows example timings for exiting IDLE2 mode with an interrupt.

Figure 3.3.5 Example Timings for Exiting a HALT Mode with an Interrupt (in IDLE2 mode)

#### b. IDLE1 mode

In IDLE1 mode, the system clock stops while only the on-chip oscillator is active. Interrupt requests are sampled asynchronously with the system clock in a halt state but the HALT mode is exited in synchronization with the system clock.

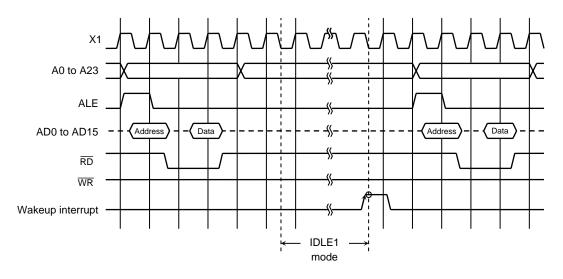

Figure 3.3.6 shows example timings for exiting IDLE1 mode with an interrupt.

Figure 3.3.6 Example Timings for Exiting a HALT Mode with an Interrupt (in IDLE1 mode)

#### STOP mode

$01(2^8)$

25.6 μs

In STOP mode, the whole TMP91CW28 stops, including the on-chip oscillator. Pin states in STOP mode depend on the setting of the SYSCR2.DRVE bit, as shown in Table 3.3.6 to Table 3.3.9.

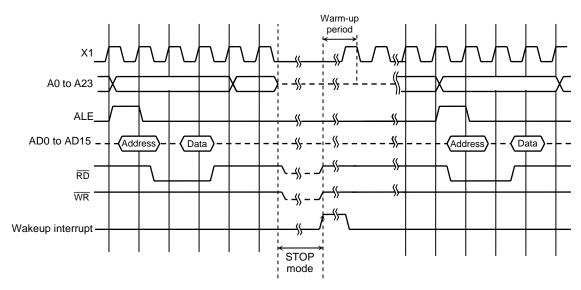

Upon detection of wakeup signaling, the warm-up period timer should be activated to allow sufficient time for the oscillator to restart and stabilize before exiting STOP mode. After that, the system clock output can restart. The warm-up period is chosen through the SYSCR2.WUPTM[1:0] bits, as shown in Table 3.3.5.

Figure 3.3.7 shows example timings for exiting STOP mode with an interrupt.

Figure 3.3.7 Example Timings for Exiting a HALT Mode with an Interrupt (in STOP mode)

Table 3.3.5 Example Warm-up Period Settings (when exiting STOP mode)

10 (2<sup>14</sup>)

1.6384 ms

at f<sub>OSCH</sub> = 10 MHz SYSCR2.WUPTM[1:0] 11 (2<sup>16</sup>)

6.5536 ms

Table 3.3.6 Input Buffer State Table (1/2)

|                         |                | <u>'</u>        | able 3.3.       | o input L  |                 |              | ,                   |            |                   |            |

|-------------------------|----------------|-----------------|-----------------|------------|-----------------|--------------|---------------------|------------|-------------------|------------|

|                         |                |                 | ı               |            | Inp             | ut Buffer St |                     |            |                   |            |

|                         |                |                 | When th         |            |                 | T Mode       | In HALT Mode (STOP) |            |                   |            |

| Port Name               | Input Function | <b>.</b>        | Operating       |            | (IDLE2/IDLE1)   |              | <drve> = 1</drve>   |            | <drve> = 0</drve> |            |

| 1 of Name               | Name           | During<br>Reset | When<br>Used as | When       | When<br>Used as | When         | When<br>Used as     | When       | When<br>Used as   | When       |

|                         |                |                 | Function        | Used as    | Function        | Used as      | Function            | Used as    | Function          | Used as    |

|                         |                |                 | Pin             | Input Port | Pin             | Input Port   | Pin                 | Input Port | Pin               | Input Port |

| P00 to P07              | AD0 to AD7     |                 |                 |            |                 |              |                     |            |                   |            |

| P10 to P17              | AD8 to AD15    |                 |                 |            |                 |              |                     |            |                   |            |

| 1 10 10 17              | A8 to A15      | OFF             | ON              | ON (*3)    | OFF             |              | OFF                 |            | OFF               |            |

| P20 to P27              | A0 to A7       | <b>.</b> .      |                 | 0.1 ( 0)   |                 | OFF          |                     | OFF        |                   |            |

| 1 20 10 1 27            | A16 to A23     |                 |                 |            |                 |              |                     |            |                   |            |

| P32 (*1)                | -              |                 | -               |            | -               |              | -                   |            | -                 |            |

| P33 (*1)                | WAIT           |                 | ON              |            | OFF             |              | OFF                 |            | OFF               | OFF        |

| P34 (*1)                | BUSRQ          |                 | 011             |            | ON              |              | ON                  |            | <b>0</b> 11       |            |

| P35 (*1)                | -              |                 |                 | _          |                 |              |                     |            |                   |            |

| P36 (*1)                | -              | ON              |                 | ON         |                 |              |                     |            |                   |            |

| P37 (*1)                | -              |                 | =               |            | _               |              | -                   |            | =                 |            |

| P40 to P43              | _              |                 |                 |            |                 |              |                     |            |                   |            |

| (*1)                    | ****           |                 |                 |            |                 |              |                     |            |                   |            |

| P50 (*2)                | AN0            | OFF             |                 |            |                 |              |                     |            |                   |            |

|                         | KWI0           |                 |                 |            |                 |              |                     |            |                   |            |

| P51 (*2)                | AN1            | ON              |                 |            |                 |              |                     |            |                   |            |

|                         | KWI1           | OFF             |                 |            |                 |              |                     |            |                   |            |

| P52 (*2)                | AN2            | ON              |                 |            |                 |              |                     |            |                   |            |

|                         | KWI2           | OFF             |                 |            |                 |              |                     |            |                   |            |

| DEG (**0)               | AN3            | ON              |                 |            |                 |              |                     |            |                   |            |

| P53 (*2)                | ADTRG          | OFF             |                 | ON (**0)   |                 |              |                     |            | ON                | ON         |

|                         | KWI3           | OFF             |                 | ON (*3)    |                 |              |                     |            | ON                | ON         |

| P54 (*2)                | AN4            | ON              |                 |            |                 |              |                     |            |                   |            |

|                         | KWI4           | OFF             | ON              |            | ON              | ON           | ON                  | ON         |                   |            |

| P55 (*2)                | AN5            | ON              | -               |            |                 |              |                     |            |                   |            |

|                         | KWI5           | OFF             |                 |            |                 |              |                     |            |                   |            |

| Sheet4U com<br>P56 (*2) | AN6            | ON              | -               |            |                 |              |                     |            |                   |            |

|                         | KWI6           | OFF             | -               |            |                 |              |                     |            |                   |            |

| P57 (*2)                | AN7            | ON              | -               |            |                 |              |                     |            |                   |            |

| P60                     | KWI7           | OFF             | -               |            |                 |              |                     |            |                   |            |

|                         | SCK0<br>SDA0   |                 |                 |            |                 |              |                     |            |                   |            |

| P61 (*1)                | SIO            |                 |                 |            |                 |              |                     |            | OFF               | OFF        |

| P62 (*1)                | SCL0           |                 |                 |            |                 |              |                     |            |                   |            |

| P63                     | INT0           |                 |                 |            |                 |              |                     |            | ON                | ON         |

| P63                     | - INTO         | ON              |                 | ON         |                 |              |                     |            | ON                | ON         |

| P64<br>P65              | -              | J.,             |                 |            | _               |              | _                   |            | _                 |            |

| P65                     |                | -               | _               |            | =               |              | _                   |            | =                 |            |

| P70 (*1)                | TA0IN          |                 | ON              |            | ON              |              | ON                  |            | OFF               | OFF        |

|                         | IAUIN          |                 | ON              |            | ON              |              | ON                  |            | OFF               |            |

| P71 to P75              |                |                 |                 |            |                 |              |                     |            |                   |            |

ON: The buffer is always turned on. A current flows the input buffer if the input pin is not driven.

OFF: The buffer is always turned off.

-: Not applicable.

\*1: Port having a pull-up/pull-down resistor.

\*2: AIN input does not cause a current to flow through the buffer.

\*3: The buffer is turned on if read port.

www.Data

Table 3.3.7 Input Buffer State Table (2/2)

| -                     |                        |      | able 3.3.       | / Input E                          | suffer Sta                    | te Table (                         | (2/2)                         |                                    |                               |                                    |                              |

|-----------------------|------------------------|------|-----------------|------------------------------------|-------------------------------|------------------------------------|-------------------------------|------------------------------------|-------------------------------|------------------------------------|------------------------------|

|                       |                        |      |                 |                                    | Inp                           | out Buffer St                      | ate                           |                                    |                               |                                    |                              |

|                       |                        |      |                 | e CPU is                           | In HAL                        | T Mode                             |                               | In HALT Mode (STOP)                |                               |                                    |                              |

| Port Name             | Input Function<br>Name | D    |                 | rating                             |                               | (IDLE2/IDLE1)                      |                               | E> = 1                             |                               | $\langle DRVE \rangle = 0$         |                              |

| Forthame              |                        | Name | During<br>Reset | When<br>Used as<br>Function<br>Pin | When<br>Used as<br>Input Port | When<br>Used as<br>Function<br>Pin | When<br>Used as<br>Input Port | When<br>Used as<br>Function<br>Pin | When<br>Used as<br>Input Port | When<br>Used as<br>Function<br>Pin | When<br>Used as<br>Input Por |

| P80 (*1)              | TB0IN0                 |      |                 |                                    |                               |                                    |                               |                                    |                               |                                    |                              |

| F60 (*1)              | INT5                   |      | ON              |                                    | ON                            |                                    | ON                            |                                    | OFF                           | ı                                  |                              |

| D04 (±4)              | TB0IN1                 |      | ON              |                                    | ON                            |                                    | ON                            |                                    | OFF                           |                                    |                              |

| P81 (*1)              | INT6                   |      |                 |                                    |                               |                                    |                               |                                    |                               |                                    |                              |

| P82 (*1)              | -                      |      |                 |                                    | _                             |                                    |                               |                                    |                               |                                    |                              |

| P83 (*1)              | -                      |      | _               |                                    |                               |                                    | _                             |                                    |                               |                                    |                              |

| P84 (*1)              | TB1IN0                 |      |                 |                                    |                               |                                    |                               |                                    |                               |                                    |                              |

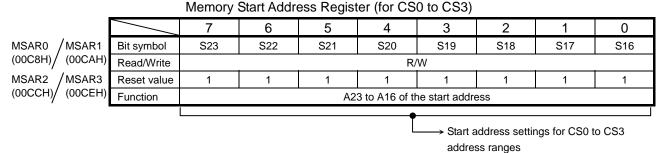

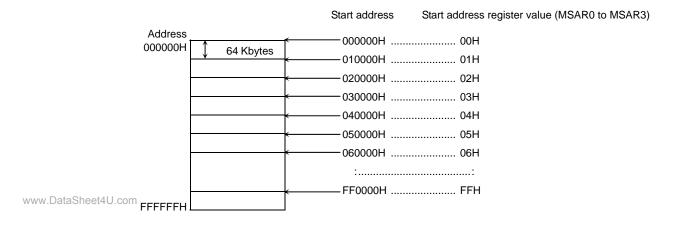

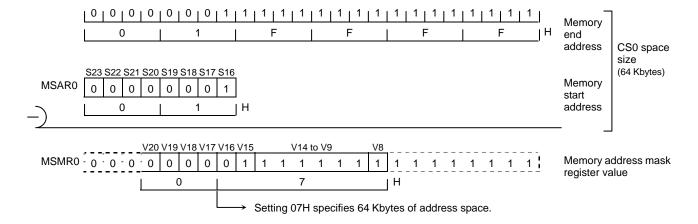

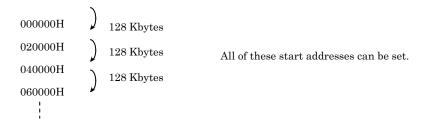

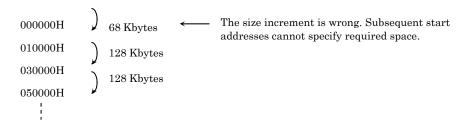

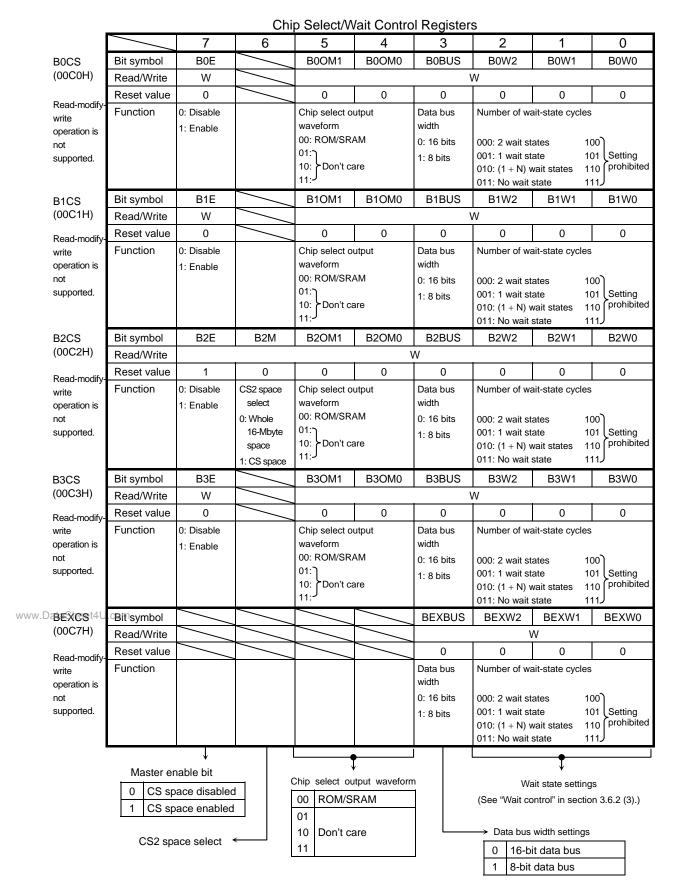

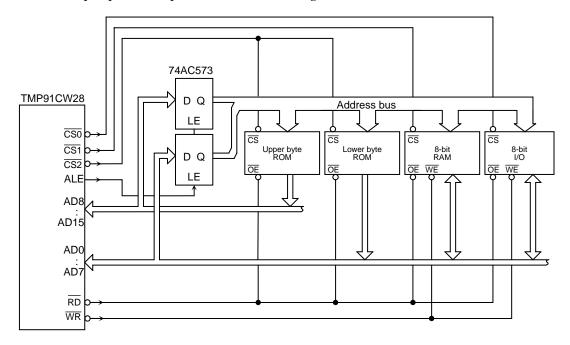

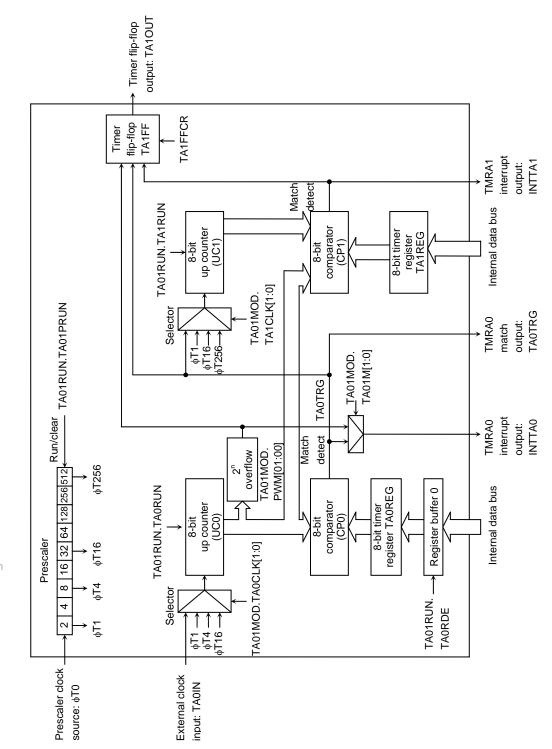

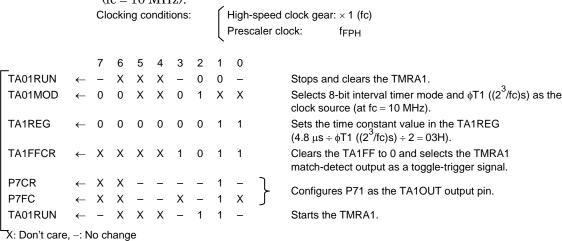

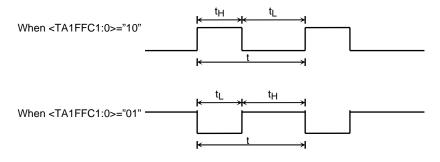

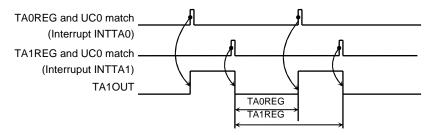

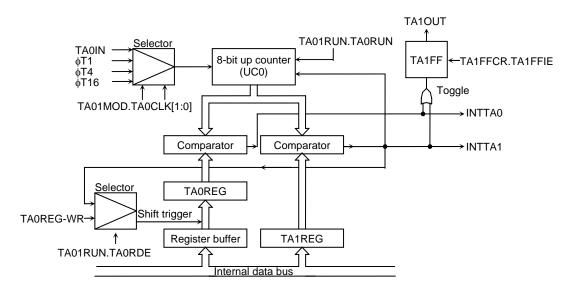

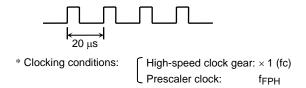

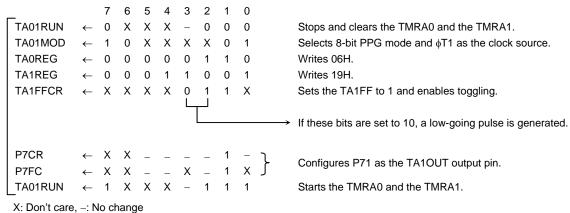

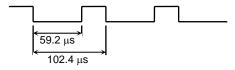

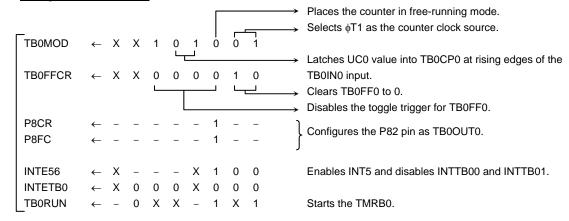

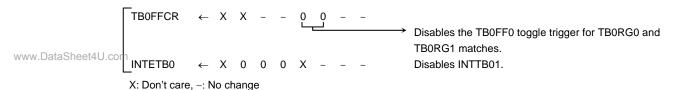

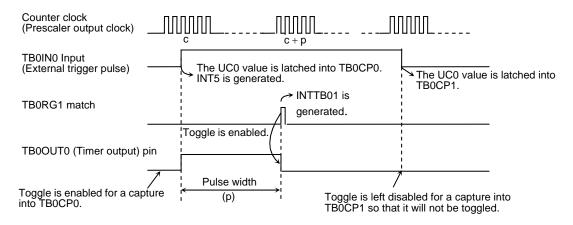

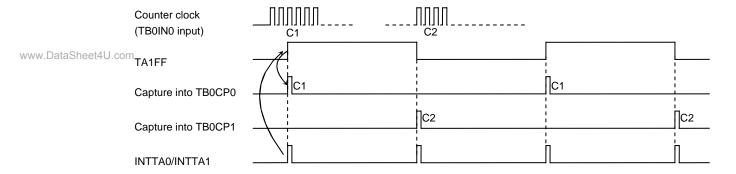

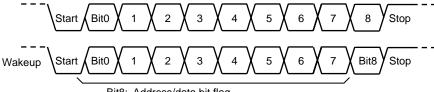

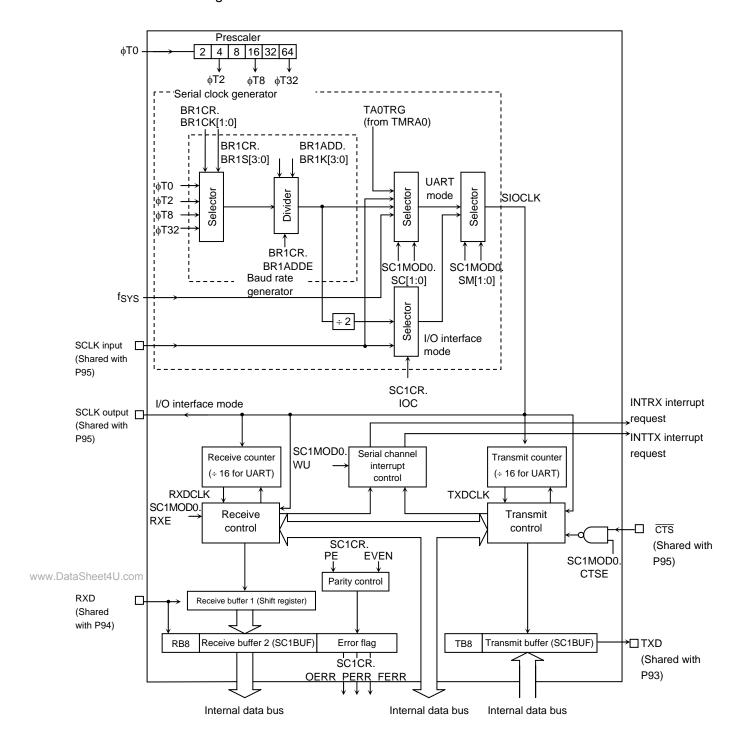

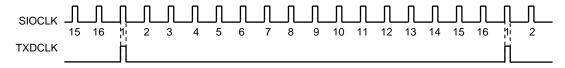

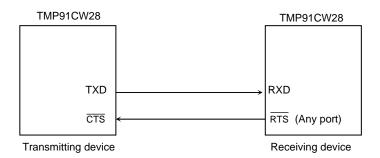

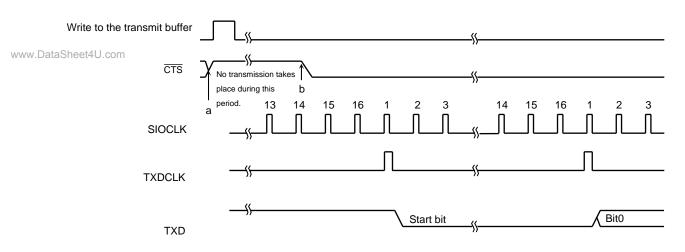

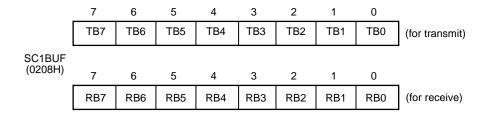

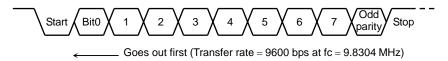

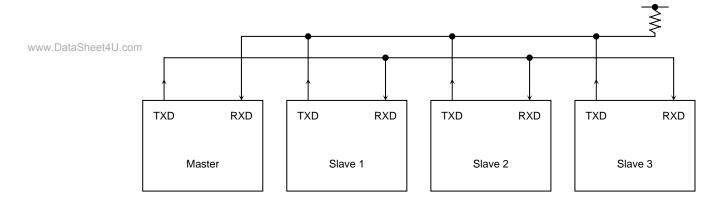

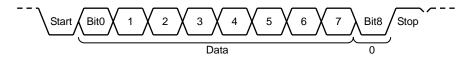

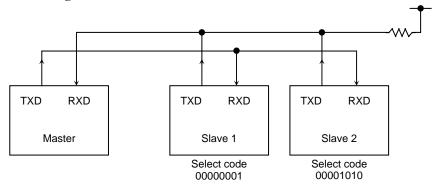

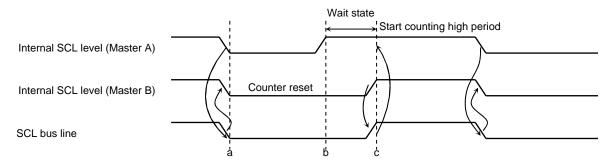

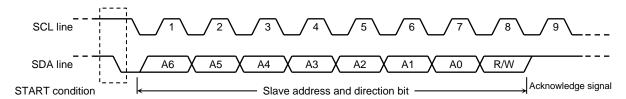

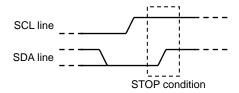

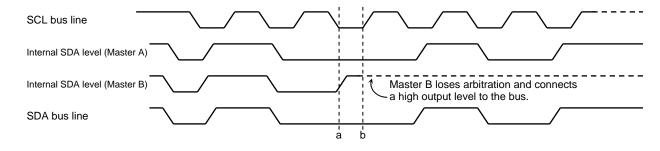

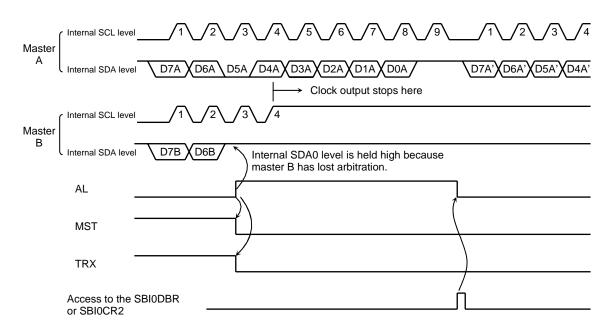

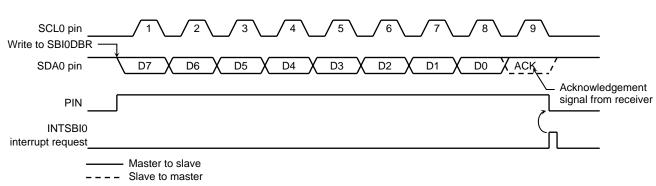

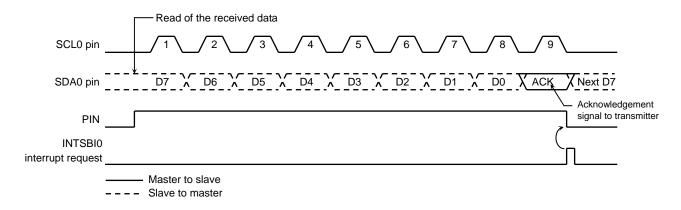

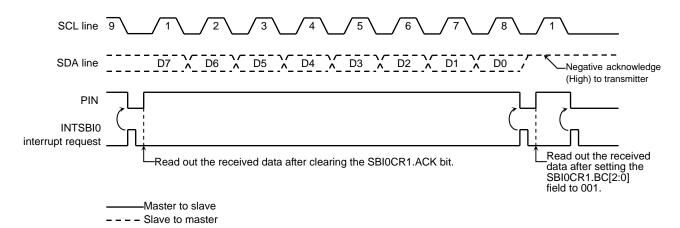

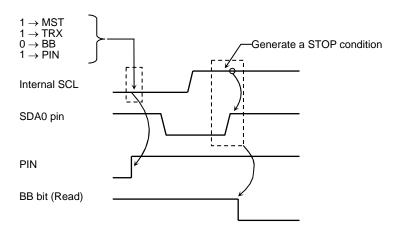

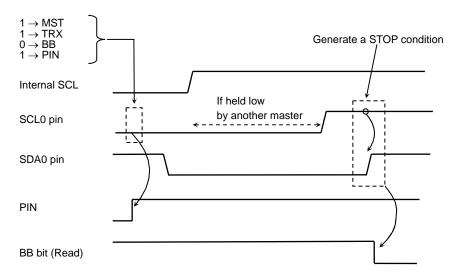

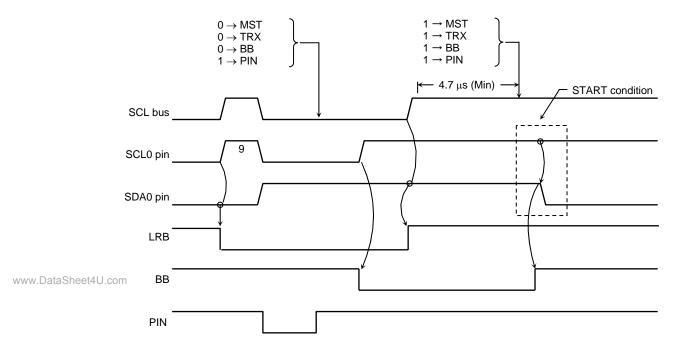

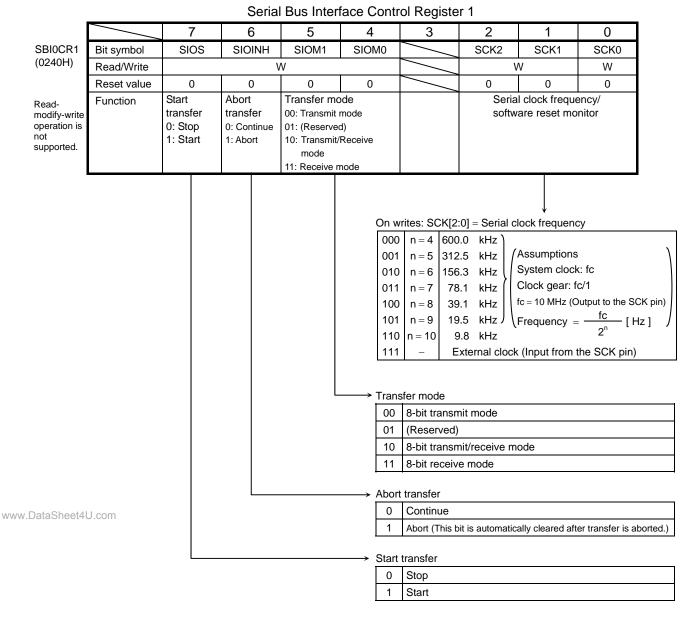

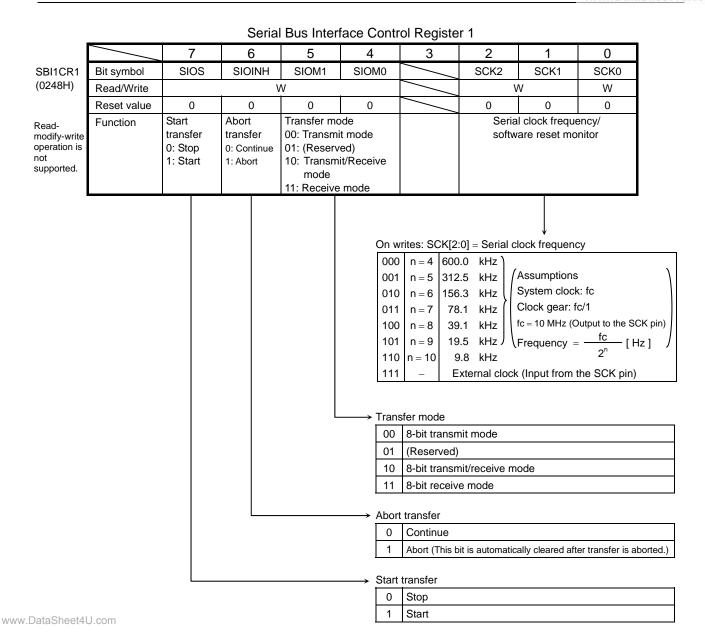

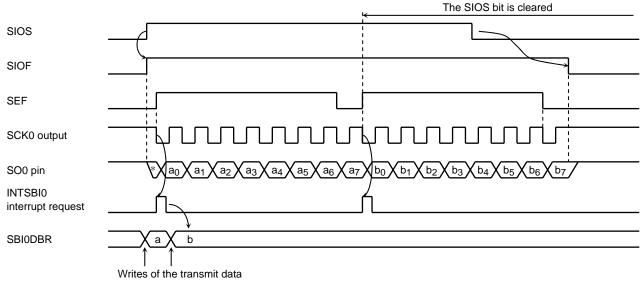

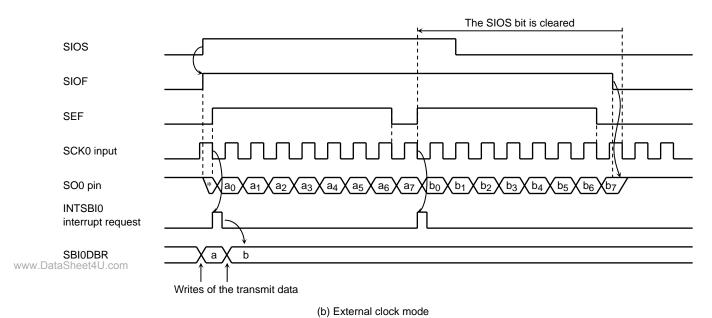

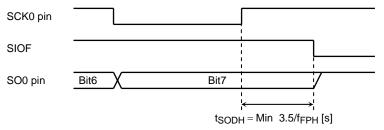

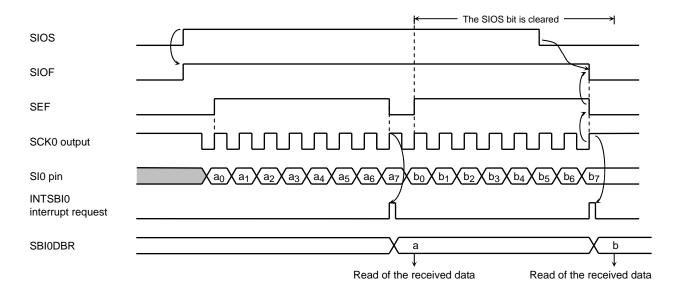

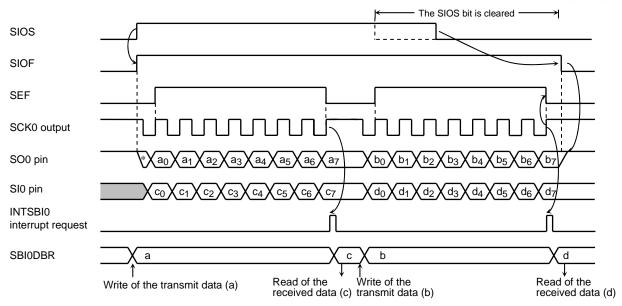

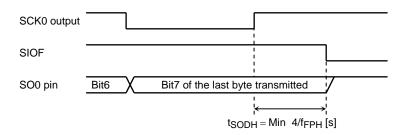

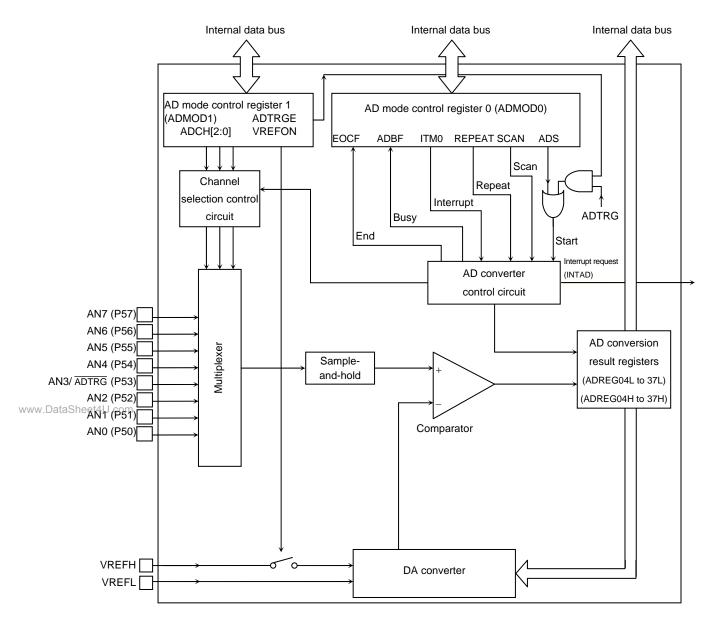

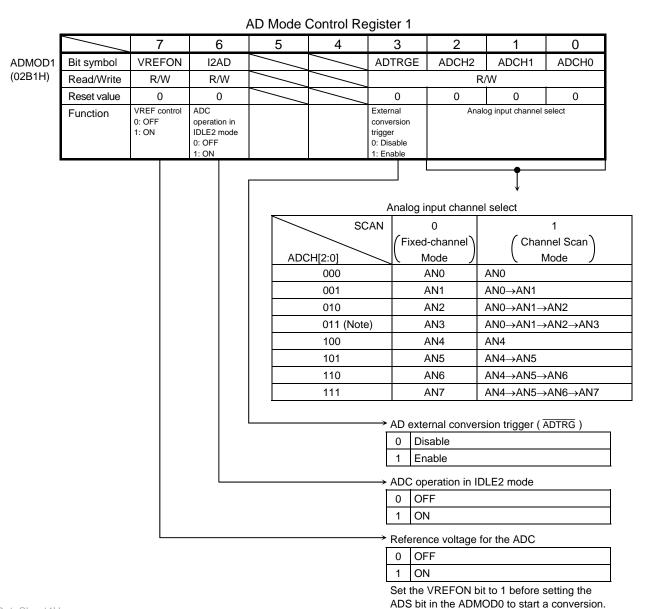

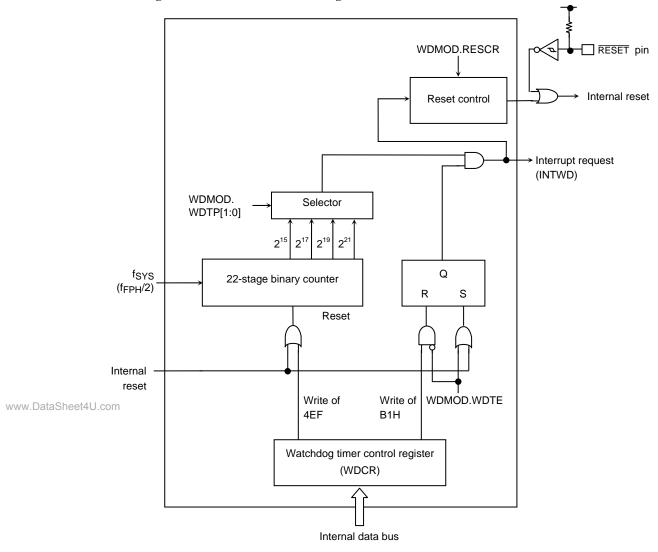

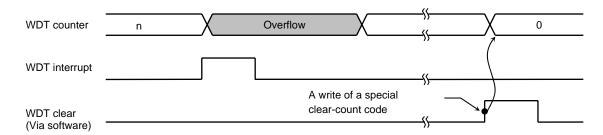

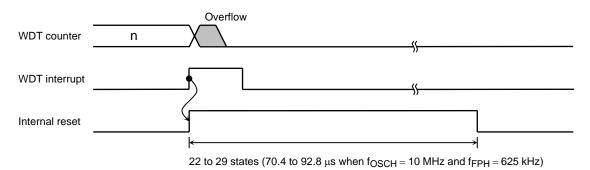

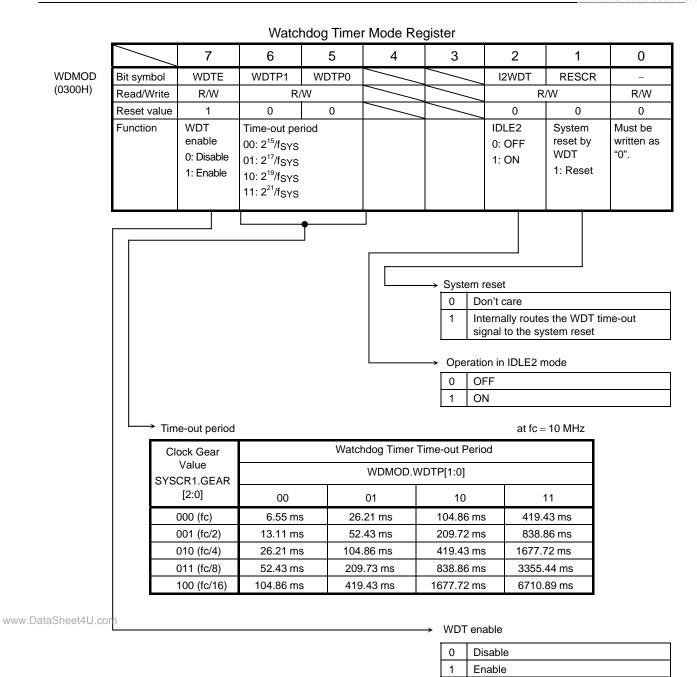

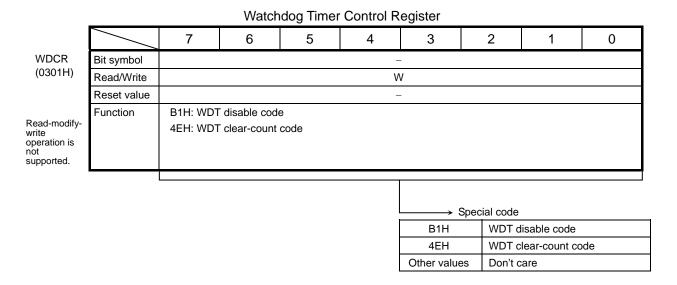

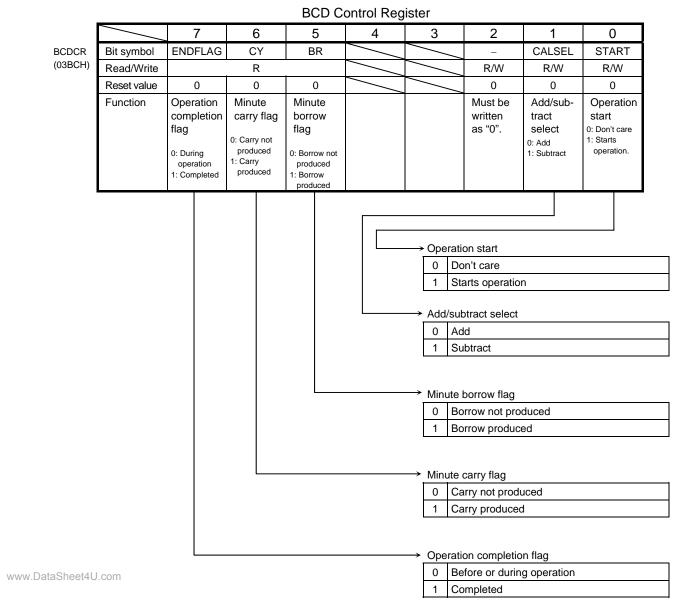

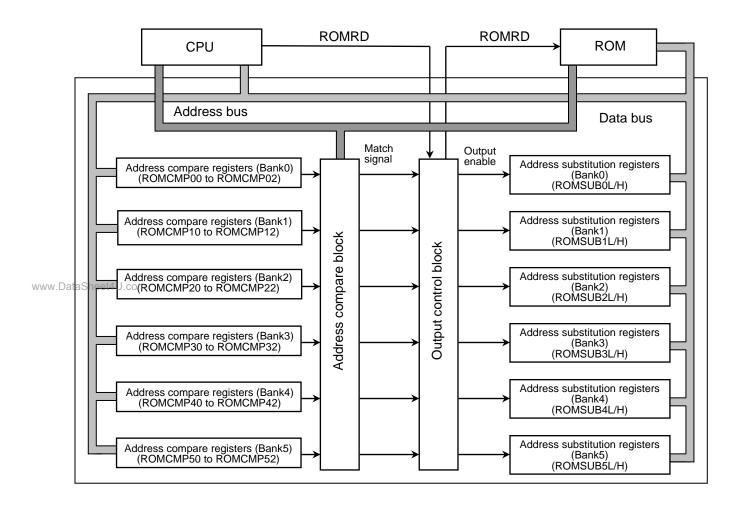

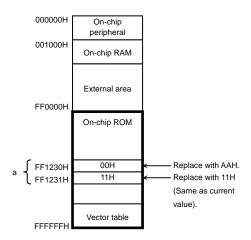

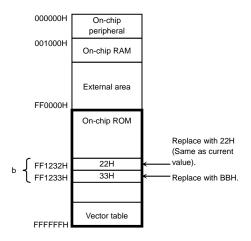

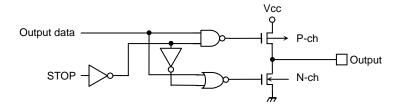

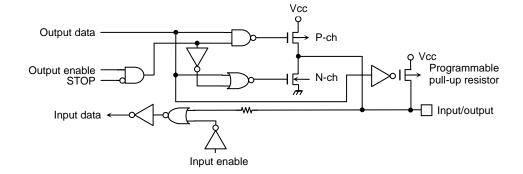

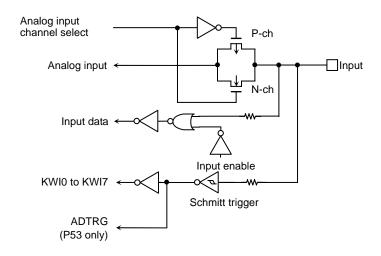

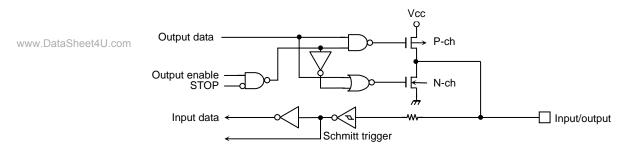

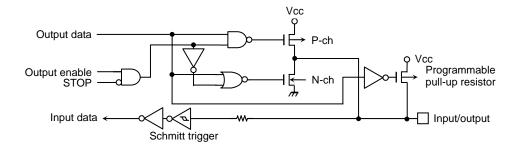

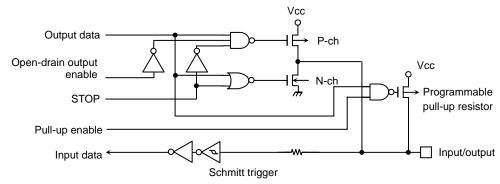

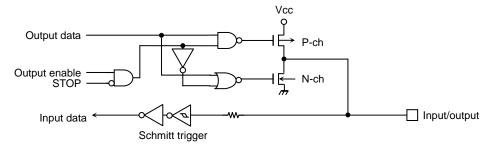

| F04 (*1)              | INT7                   |      | ON              |                                    | ON                            |                                    | ON                            |                                    | OFF                           |                                    |                              |