# **TMD2620**

## **Proximity Sensor Module**

#### **General Description**

The device is an advanced proximity sensor. The slim module incorporates an IR LED and factory calibrated LED driver. The proximity detection feature provides object detection (e.g. mobile device screen to user's ear) by photodiode detection of reflected IR energy (sourced by the integrated LED).

Detect/release events are interrupt driven, and occur when proximity result crosses upper and/or lower threshold settings.

The proximity engine features offset adjustment registers to compensate for unwanted IR energy reflection at the sensor. Proximity results are further improved by automatic ambient light subtraction.

Ordering Information and Content Guide appear at end of datasheet.

Figure 1: **Added Value of Using TMD2620**

| Benefits                                                                  | Features                                                                                   |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Reduced board space requirements and<br>enables low-profile system design | <ul> <li>Small footprint and low profile package</li> <li>3.10 x 2.00 x 1.00 mm</li> </ul> |

| Reduced power consumption                                                 | <ul> <li>0.18μm process technology with 1.8V I<sup>2</sup>C bus</li> </ul>                 |

#### **Applications**

The TMD2620 is ideal for mobile phone touch screen disable.

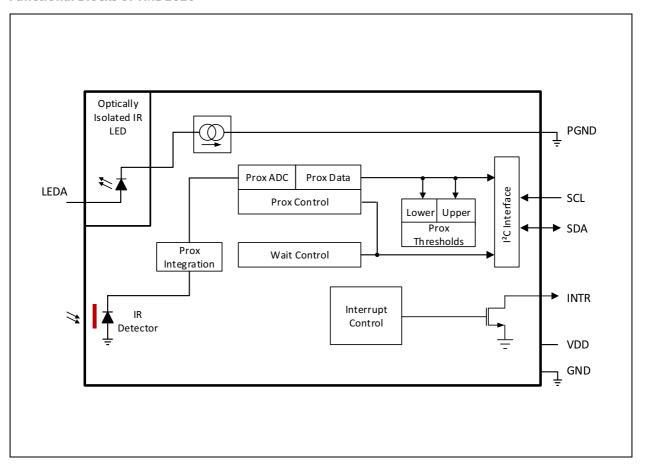

## **Block Diagram**

The functional blocks of this device are shown below:

Figure 2: Functional Blocks of TMD2620

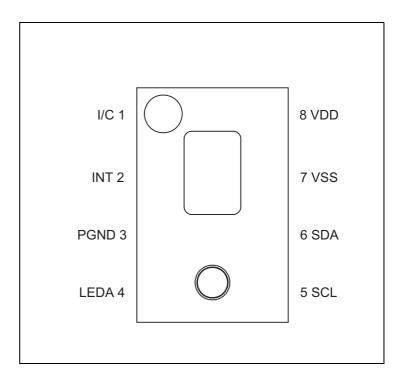

# **Pin Assignment**

Figure 3: TMD2620 Pinout (Top View)

Figure 4: Pin Description

| Pin Number | Pin Name | Description                                 |  |

|------------|----------|---------------------------------------------|--|

| 1          | I/C      | Internal connection. Connect to ground.     |  |

| 2          | INT      | Interrupt. Open drain output (active low)   |  |

| 3          | PGND     | Ground for LED current sink and I/O buffers |  |

| 4          | LEDA     | LED anode                                   |  |

| 5          | SCL      | I <sup>2</sup> C serial clock input         |  |

| 6          | SDA      | I <sup>2</sup> C serial data I/O terminal   |  |

| 7          | VSS      | Ground. All voltages are referenced to GND  |  |

| 8          | VDD      | Supply voltage                              |  |

Datasheet, PublicPage 3[v2-00] 2023-Feb-23Document Feedback

## **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings

| Symbol             | Parameter                                                  | Min     | Max | Units |

|--------------------|------------------------------------------------------------|---------|-----|-------|

| VDD                | Supply voltage                                             | -0.3    | 2.2 | V     |

| LEDA               | Supply voltage                                             | -0.3    | 3.6 | V     |

| V <sub>IO</sub>    | Digital I/O terminal voltage                               | -0.3    | 3.6 | V     |

| (SDA, INT)         | Output terminal current                                    | -1      | 20  | mA    |

| T <sub>STRG</sub>  | Storage temperature range                                  | -40     | 85  | °C    |

| I <sub>SCR</sub>   | Input current (latch up immunity) JEDEC JESD78D Nov 2011   | CLASS 1 |     |       |

| ESD <sub>HBM</sub> | Electrostatic discharge HBM<br>S-001-2014                  | ±2      | V   |       |

| ESD <sub>CDM</sub> | Electrostatic discharge CDM<br>JEDEC JESD22-C101F Oct 2013 | ±       | V   |       |

Page 4

Document Feedback

[v2-00] 2023-Feb-23

#### **Electrical Characteristics**

Figure 6:

**Recommended Operating Conditions**

| Symbol            | Parameter                          | Min | Тур | Max | Units |

|-------------------|------------------------------------|-----|-----|-----|-------|

| $V_{DD}$          | Supply voltage                     | 1.7 | 1.8 | 2.0 | V     |

| V <sub>LEDA</sub> | Voltage supplied to LEDA pin       |     | 3.3 |     | V     |

| T <sub>A</sub>    | Operating free-air temperature (1) | -30 |     | 85  | °C    |

#### Note(s):

1. While the device is operational across the temperature range, performance will vary with temperature. Operational characteristics are at 25°C, unless otherwise noted.

Figure 7: Operating Characteristics,  $V_{DD} = 1.8 \text{ V}$ ,  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise noted)

| Symbol           | Parameter                           | Conditions                       | Min  | Тур | Max  | Units |

|------------------|-------------------------------------|----------------------------------|------|-----|------|-------|

| f <sub>OSC</sub> | Oscillator frequency                |                                  |      | 8.0 |      | MHz   |

| IDD              | Supply current <sup>(1)</sup>       | Idle state<br>(PON=1, PEN=0) (2) |      | 30  |      | μΑ    |

|                  |                                     | Sleep state (3)                  |      | 0.7 | 5.0  | μΑ    |

| VOL              | INT, SDA output low voltage         | 6 mA sink current                |      |     | 0.6  | ٧     |

| ILEAK            | Leakage current, SDA, SCL, INT pins |                                  | -5   |     | 5    | μΑ    |

| VIH              | SCL, SDA input high voltage         |                                  | 1.26 |     |      | V     |

| VIL              | SCL, SDA input low voltage          |                                  |      |     | 0.54 | V     |

#### Note(s):

- 1. Values are shown at the VDD pin and do not include current through the IR LED.

- 2. Idle state occurs when PON=1 and all functions are not enabled.

- 3. Sleep state occurs when PON = 0 and I<sup>2</sup>C bus is idle. If Sleep state has been entered as the result of operational flow, SAI = 1, PON will remain high.

Datasheet, PublicPage 5[v2-00] 2023-Feb-23Document Feedback

Figure 8: Proximity Optical Characteristics of TMD2620

| Parameter                                                  | Conditions                                                                                                                                                                                                                                | Min | Тур | Max | Unit   |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| Part to part variation <sup>(1)</sup>                      | Conditions: PGAIN = 2 (4x) PLDRIVE = 8 (54mA) PPULSE = 15 (16 pulses) PPULSE_LEN = 1 (16µs) d=23mm round target 30mm target distance                                                                                                      | 75  | 100 | 125 | %      |

| Response, absolute                                         | Basic proximity measurement (2) Conditions: PGAIN = 2 (4x), PLDRIVE = 7(48mA) PPULSE = 15 (16 pulses) PPULSE_LEN = 2 (16\mus) Target material: 90% reflective surface of Kodak gray card Target Size: 100mm x 100mm Target Distance: 60mm | 82  | 103 | 123 | Counts |

| Response, no target using offset values from 0xE6 and 0xE7 | PGAIN = 2 (4x) ILEDDRIVE = 16 (102mA) PPULSE = 16 (17 Pulses) Pulse Length = 2 (16µs)                                                                                                                                                     | 0   |     | 10  |        |

| Noise/Signal <sup>(3)</sup>                                | PGAIN = 2 (4x) IRLEDDRIVE = 8 (54mA) PPULSE = 15 (16 pulses) PPULSE_LEN = 1 (8µs) d=23mm round target 30mm target distance                                                                                                                |     |     | 1   | %      |

#### Note(s):

- $1. \ Production \ tested \ result \ is \ the \ average \ of \ 5 \ readings \ expressed \ relative \ to \ a \ calibrated \ response.$

- 2. Representative result by characterization.

- 3. Production tested result is the average of 20 readings divided by the average response.

Page 6Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

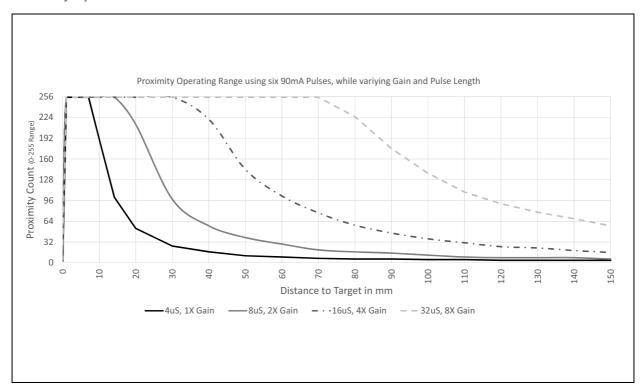

Figure 9: Proximity Operation

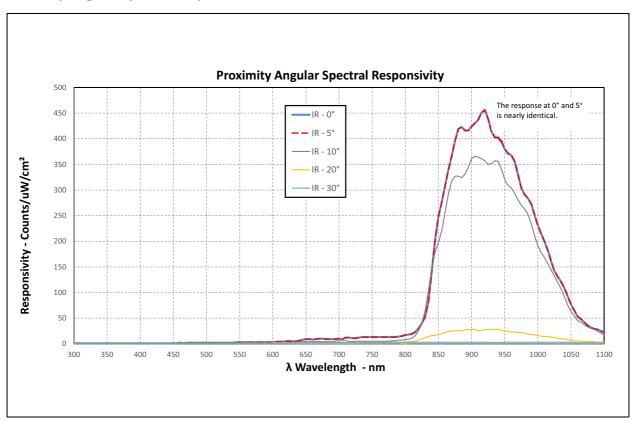

Figure 10: Proximity Angular Spectral Response

Datasheet, PublicPage 7[v2-00] 2023-Feb-23Document Feedback

# **Register Description**

#### Device address is 0x29.

Figure 11: Register Overview

| Address | Register Name | R/W   | Register Function                       | Reset Value |

|---------|---------------|-------|-----------------------------------------|-------------|

| 0x80    | ENABLE        | R/W   | Enables states and interrupts           | 0x00        |

| 0x82    | PRATE         | R/W   | Proximity sample rate                   | 0x1F        |

| 0x83    | WTIME         | R/W   | Wait time                               | 0x00        |

| 0x88    | PILT          | R/W   | Proximity interrupt low threshold       | 0x00        |

| 0x8A    | PIHT          | R/W   | Proximity interrupt high threshold      | 0x00        |

| 0x8C    | PERS          | R/W   | Proximity interrupt persistence filters | 0x00        |

| 0x8D    | CFG0          | R/W   | WTIME configuration                     | 0x80        |

| 0x8E    | PCFG0         | R/W   | Proximity pulse width and count         | 0x4F        |

| 0x8F    | PCFG1         | R/W   | Proximity gain and LED current          | 0x80        |

| 0x91    | REVID         | R     | Revision ID                             |             |

| 0x92    | ID            | R     | Device ID                               | 0xD4        |

| 0x93    | STATUS        | R, SC | Device status register one              | 0x00        |

| 0x9C    | PDATA         | R     | Proximity ADC data register MSBs        | 0x00        |

| 0x9E    | REVID2        | R     | Reserved                                | 0x00        |

| 0x9F    | CFG2          | R/W   | Configuration register two              | 0x00        |

| 0xAB    | CFG3          | R/W   | Configuration register three            | 0x0C        |

| 0xC0    | POFFSET_L     | R/W   | Proximity offset value                  | 0x00-0xFF   |

| 0xC1    | POFFSET_H     | R/W   | Proximity offset sign                   | 0x00-0xFF   |

| 0xD7    | CALIB         | R/W   | Calibration control                     | 0x00        |

| 0xD9    | CALIBCFG      | R/W   | Calibration configuration               | 0x00        |

| 0xDC    | CALIBSTAT     | R/W   | Calibration status bit                  | 0x00        |

| 0xDD    | INTENAB       | R/W   | Interrupt enables                       | 0x00        |

### Register Access:

- R = Read Only

- W = Write Only

- R/W = Read or Write

- SC = Self Clearing after access

Page 8

Document Feedback

## **ENABLE Register (0x80)**

Figure 12: **ENABLE Register**

| Add   | r: 0x80  | ENABLE |      | ENABLE                                                                                                                                                                                   |

|-------|----------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field | Name     | Reset  | Type | Description                                                                                                                                                                              |

| 7:4   | Reserved | 0      | RW   | Reserved                                                                                                                                                                                 |

| 3     | wen      | 0      | RW   | Wait Enable. This bit activates the wait feature. Writing a one actives the wait timer. Writing a zero disables the wait timer.                                                          |

| 2     | pen      | 0      | RW   | Proximity Detect Enable. This field activates the proximity detection.                                                                                                                   |

| 1     | Reserved | 0      | RW   | Reserved                                                                                                                                                                                 |

| 0     | pon      | 0      | RW   | Power On. This field activates the internal oscillator to permit the timers and ADC channels to operate. Writing a one activates the oscillator. Writing a zero disables the oscillator. |

The Mode/Parameter fields should be written before pen is asserted. The function pen require pon to be asserted for the respective function to operate correctly.

## PRATE Register (0x82)

Figure 13: **PRATE** Register

| Addr  | : 0x82 |       |      | PRATE                                                                                                                                          |

|-------|--------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Field | Name   | Reset | Type | Description                                                                                                                                    |

| 7:0   | prate  | 0x1F  | RW   | When averaging is turned on, this register defines the time between proximity measurements. The time will be 88µs times this register's value. |

**Datasheet, Public** Page 9 Document Feedback

## WTIME Register (0x83)

Figure 14: WTIME Register

| Addr  | :0x83  |       | WTIME |                          |                            |              |              |   |                |

|-------|--------|-------|-------|--------------------------|----------------------------|--------------|--------------|---|----------------|

| Field | Name   | Reset | Туре  |                          | Description                |              |              |   |                |

|       |        |       |       | Wait Time. Eight bit val | ue that specifies the time | 2            |              |   |                |

|       |        |       |       | Value                    | Wait Cycles                | Wait Time    |              |   |                |

|       |        | 0x00  | 0x00  | 0x00                     | 0x00                       | 0x00 RW      | 0x00         | 1 | 2.81ms/ 33.8ms |

| 7:0   | wtime  |       |       |                          |                            |              | 0x01         | 2 | 5.6ms/ 67.6ms  |

| 7.0   | willie |       |       |                          |                            |              |              |   |                |

|       |        |       |       |                          |                            | 63           | 180ms/ 2.16s |   |                |

|       |        |       |       |                          |                            |              |              |   |                |

|       |        |       |       | 0xff                     | 255                        | 721ms/ 8.65s |              |   |                |

The wait timer is implemented with a down counter with 0x00 as the terminal count. Loading 0x00 will generate a 2.81ms wait time, loading 0x01 will generate a 5.6ms wait time, and so forth; by asserting wlong, in register 0x8D the wait time is given in multiples of 33.8ms (12x).

Page 10Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

#### PILT Register (0x88)

Figure 15: PILT Register

| Addr  | :: 0x88 |       |      | PILT                                |

|-------|---------|-------|------|-------------------------------------|

| Field | Name    | Reset | Type | Description                         |

| 7:0   | pilt    | 0     | RW   | Proximity ADC Channel Low Threshold |

This register provides the low interrupt threshold. If the value generated by the proximity channel is below the low threshold specified and the PPERS value is reached, the pint bit is asserted which will assert the INT pin if pien is set.

#### PIHT Register (0x8A)

Figure 16: PIHT Register

| Addr  | : 0x8A |       |      | PIHT                                 |

|-------|--------|-------|------|--------------------------------------|

| Field | Name   | Reset | Туре | Description                          |

| 7:0   | piht   | 0     | RW   | Proximity ADC Channel High Threshold |

This register provides the high interrupt threshold. If the value generated by the proximity channel is above the high threshold specified and the PPERS value is reached, the pint bit is asserted which will assert the INT pin if pien is set.

Datasheet, PublicPage 11[v2-00] 2023-Feb-23Document Feedback

#### PERS Register (0x8C)

This register controls the interrupt filtering capabilities of the device. Configurable filtering is provided to allow interrupts to be generated after a proximity cycle or if the integration cycle has produced a result that is outside of the values specified by threshold register for some specified number of times.

Figure 17: PERS Register

| Addr: 0x8C |          | PERS  |      |              |                                                |  |

|------------|----------|-------|------|--------------|------------------------------------------------|--|

| Field      | Name     | Reset | Type |              | Description                                    |  |

|            |          |       |      | Proximity Pe | ersistence Filtering                           |  |

|            |          |       |      | Value        | Interrupt generated when                       |  |

|            |          | 0     | RW   | 0            | Every proximity cycle                          |  |

| 7:4        | ppors    |       |      | 1            | Any proximity value outside of threshold range |  |

| 7.4        | ppers    |       |      | 2            | 2 consecutive proximity values out of range    |  |

|            |          |       |      | 3            | 3 consecutive proximity values out of range    |  |

|            |          |       |      |              |                                                |  |

|            |          |       |      | 15           | 15 consecutive proximity values out of range   |  |

| 3:0        | Reserved | 0     | RW   | Reserved     |                                                |  |

## CFG0 Register (0x8D)

Figure 18: CFG0 Register

| Addr: 0x8D |          | CFG0  |      |                                                                                                                   |  |  |

|------------|----------|-------|------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Field      | Name     | Reset | Type | Description                                                                                                       |  |  |

| 7:3        | Reserved | 10000 | RW   | Reserved. Must be set to 10000.                                                                                   |  |  |

| 2          | wlong    | 0     | RW   | Wait Long. When asserted, the wait cycle is increased by a factor 12x from that programmed in the WTIME register. |  |  |

| 1:0        | Reserved | 0 0   | RW   | Reserved. Must be set to 00.                                                                                      |  |  |

Page 12Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

# PCFG0 Register (0x8E)

Figure 19: PCFG0 Register

| Addr: 0x8E |             | PCFG0 |                        |                                       |                  |  |  |

|------------|-------------|-------|------------------------|---------------------------------------|------------------|--|--|

| Field      | Name        | Reset | Reset Type Description |                                       |                  |  |  |

|            |             |       |                        | Proximity Pulse Length                |                  |  |  |

|            |             |       |                        | Value                                 | Pulse Length     |  |  |

| 7:6        | ppulse_len  | 1     | RW                     | 0                                     | 4µs              |  |  |

| 7.0        | ppuise_ieii | 1     | KVV                    | 1                                     | 8µs              |  |  |

|            |             |       |                        | 2                                     | 16μs             |  |  |

|            |             |       |                        | 3                                     | 32μs             |  |  |

|            |             | 15    | RW                     | Maximum Number of Pulses in Proximity |                  |  |  |

|            |             |       |                        | Value                                 | Number of Pulses |  |  |

|            |             |       |                        | 0                                     | 1                |  |  |

| 5:0        | ppulse      |       |                        | 1                                     | 2                |  |  |

|            |             |       |                        | 2                                     | 3                |  |  |

|            |             |       |                        |                                       |                  |  |  |

|            |             |       |                        | 63                                    | 64               |  |  |

# PCFG1 Register (0x8F)

Figure 20: PCFG1 Register

| Addr: 0x8F |          | PCFG1 |      |                                                                                        |                                 |  |  |

|------------|----------|-------|------|----------------------------------------------------------------------------------------|---------------------------------|--|--|

| Field      | Name     | Reset | Type | Description                                                                            |                                 |  |  |

|            |          |       |      | Proximity Gain Control. Sets the                                                       | gain of the proximity receiver. |  |  |

|            |          |       |      | Value                                                                                  | Gain Value                      |  |  |

| 7:6        | pgain    | 2     | RW   | 0                                                                                      | 1x                              |  |  |

| 7.0        | pgain    | 2     | LVV  | 1                                                                                      | 2x                              |  |  |

|            |          |       |      | 2                                                                                      | 4x                              |  |  |

|            |          |       |      | 3                                                                                      | 8x                              |  |  |

| 5          | Reserved | 0     | RW   | Reserved                                                                               |                                 |  |  |

|            |          |       |      | Proximity LED Drive Strength. Th of 6mA, this is the nominal value the trim procedure. |                                 |  |  |

|            |          |       |      | Value                                                                                  | LED Current                     |  |  |

| 4:0        | pldrive  | 0     | RW   | 0                                                                                      | 6mA                             |  |  |

|            |          |       |      | 1                                                                                      | 12mA                            |  |  |

|            |          |       |      |                                                                                        |                                 |  |  |

|            |          |       |      | 31                                                                                     | 192mA                           |  |  |

# REVID Register (0x91)

Figure 21: REVID Register

| Addr: 0x91 |          | REVID |      |                                |  |  |

|------------|----------|-------|------|--------------------------------|--|--|

| Field      | Name     | Reset | Type | Description                    |  |  |

| 7:3        | Reserved | 0     | RO   | Reserved                       |  |  |

| 2:0        | rev_id   |       | RO   | Revision Number Identification |  |  |

Page 14Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

# ID Register (0x92)

Figure 22: ID Register

| Addr: 0x92 |          | ID    |                            |                  |         |  |  |

|------------|----------|-------|----------------------------|------------------|---------|--|--|

| Field      | Name     | Reset | Type                       | Type Description |         |  |  |

|            |          |       | Part Number Identification |                  |         |  |  |

| 7:2        | ID       | 0x35  | RO                         | Value            | Meaning |  |  |

|            |          |       |                            | 110101           | TMD2620 |  |  |

| 1:0        | Reserved | 00    | RO                         | Reserved         |         |  |  |

## **STATUS Register (0x93)**

Figure 23: STATUS Register

| Ad    | Addr: 0x93          |       | STATUS |                                                                                                                                                                                                                                                       |  |  |  |

|-------|---------------------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Field | Name                | Reset | Type   | Description                                                                                                                                                                                                                                           |  |  |  |

| 7     | Reserved            | 0     | R, SC  | Reserved                                                                                                                                                                                                                                              |  |  |  |

| 6     | psat                | 0     | R, SC  | Proximity Saturation. Indicates that an ambient- or reflective-saturation event occurred during a previous proximity cycle. Writing a 1 will clear this status flag; to enable clear-by-read function, the register CFG3.int_read_clear must be set 1 |  |  |  |

| 5     | pint                | 0     | R, SC  | Proximity Interrupt. Indicates that the device is asserting a proximity interrupt. Writing a 1 will clear this status flag; to enable clear-by-read function, the register CFG3.int_read_clear must be set 1                                          |  |  |  |

| 4     | Reserved            | 0     | R, SC  | Reserved                                                                                                                                                                                                                                              |  |  |  |

| 3     | cint                | 0     | R, SC  | Calibration Interrupt. Writing a 1 will clear this status flag; to enable clear-by-read function, the register CFG3.int_read_ clear must be set 1                                                                                                     |  |  |  |

| 2     | zint                | 0     | R, SC  | Zero Detection Interrupt. Writing a 1 will clear this status flag. Enable clear-byread with CFG3                                                                                                                                                      |  |  |  |

| 1     | psat_<br>reflective | 0     | R, SC  | psat interrupt is from reflective light saturation writing a 1 to psat or psat_reflective will clear this status flag; to enable clear-by-read function, the register CFG3.int_read_clear must be set 1                                               |  |  |  |

| 0     | psat_<br>ambient    | 0     | R, SC  | psat interrupt is from ambient light or idac threshold saturation writing a 1 to psat or psat_ambient will clear this status flag; to enable clear-by-read function, the register CFG3.int_read_clear must be set 1                                   |  |  |  |

STATUS flags are reset with reading from STATUS address, or with writing 1 to dedicated bits of STATUS address.

## PDATA Register (0x9C)

Figure 24: PDATA Register

| Addr: 0x9C |       | PDATA |      |                                                  |  |

|------------|-------|-------|------|--------------------------------------------------|--|

| Field      | Name  | Reset | Type | Description                                      |  |

| 7:0        | pdata | 0     | RO   | This register contains the 8-bit proximity data. |  |

Page 16Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

## **REVID2 Register (0x9E)**

Figure 25: **REVID2 Register**

| <b>A</b> | Addr: 0x9E |       | REVID2 |                                 |  |  |  |

|----------|------------|-------|--------|---------------------------------|--|--|--|

| Field    | Name       | Reset | Type   | Description                     |  |  |  |

| 7:4      | Reserved   | 0     | RO     | Reserved                        |  |  |  |

| 3:0      | aux_id     | 0     | RO     | Auxiliary Identification (0x00) |  |  |  |

## CFG3 Register (0xAB)

Figure 26: **CFG3 Register**

| Ac    | Addr: 0xAB     |       | CFG3  |            |                                                                                                                                                                        |                                      |                            |  |  |

|-------|----------------|-------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------|--|--|

| Field | Name           | Reset | Туре  |            |                                                                                                                                                                        | Descriptio                           | n                          |  |  |

| 7     | int_read_clear | 0     | RW    | reset afte | If set to 1, interrupt flags in STATUS register (0x93) are reset after I <sup>2</sup> C reads to the STATUS register; otherwise the interrupt flags will not be reset. |                                      |                            |  |  |

| 6:5   | Reserved       | 0     | R, SC | Reserved   | l. Set to 0.                                                                                                                                                           |                                      |                            |  |  |

|       |                |       |       | oximity cy | pt: Power down<br>cle if an interrup                                                                                                                                   | the device at the end<br>ot has been |                            |  |  |

|       |                |       |       | PON        | SAI                                                                                                                                                                    | INT<br>(low active)                  | Oscillator                 |  |  |

|       |                |       |       | 0          | х                                                                                                                                                                      | х                                    | OFF                        |  |  |

| 4     | sai            | 0     | RW    | 1          | 0                                                                                                                                                                      | х                                    | ON                         |  |  |

|       |                |       |       | 1          | 1                                                                                                                                                                      | 1                                    | ON                         |  |  |

|       |                |       |       | 1          | 1                                                                                                                                                                      | 0                                    | OFF<br>(SAI induced sleep) |  |  |

|       |                |       |       |            |                                                                                                                                                                        | up" the device froupt register 0x93  | om SAI-sleep is by<br>3.   |  |  |

| 3:0   | Reserved       | 1100  | RW    | Reserved   | l. Set to 11                                                                                                                                                           | 00.                                  |                            |  |  |

#### Note(s):

1. SAI does not modify any register bits directly, it rather uses the interrupt signal to turn OFF the oscillator.

**Datasheet, Public** Page 17 [v2-00] 2023-Feb-23 Document Feedback

## POFFSET\_L Register (0xC0)

Figure 27: POFFSET\_L Register

| Addr: 0xC0 |           | POFFSET_L |       |                                                       |  |

|------------|-----------|-----------|-------|-------------------------------------------------------|--|

| Field      | Name      | Reset     | Type  | Description                                           |  |

| 7:0        | poffset_l | 0x00-0xFF | R, SC | Offset compensation for proximity channel (magnitude) |  |

## POFFSET\_H Register (0xC1)

Figure 28: **POFFSET\_H Register**

| Addr: 0xC1 |           | POFFSET_H |       |                                                  |  |

|------------|-----------|-----------|-------|--------------------------------------------------|--|

| Field      | Name      | Reset     | Type  | Description                                      |  |

| 0          | poffset_h | 0x00-0xFF | R, SC | Offset compensation for proximity channel (sign) |  |

## **CALIB Register (0xD7)**

Figure 29: **CALIB** Register

| Addr: 0xD7 |                        | CALIB |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|------------|------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field      | Name                   | Reset | Type  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 7:6        | Reserved               | 0     | RO    | Reserved. Set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 5          | electrical_calibration | 0     | RW_SM | If set, do electrical offset calibration (diodes disabled) instead of optical. Otherwise, do optical calibration. In either case, the result is stored in the POFFSET_L/H registers. This flag is cleared after calibration is completed.  This flag is redundant, software could just: set gdiode_disab=0xf set concap_intinn=1 start calibration. However, since electrical calibration is done automatically at the first time PON gets asserted, the function is there anyway, so it's made available to the user here. |  |

| 4:1        | Reserved               | 0     | WS_SC | Reserved. Set to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 0          | start_offset_calib     | 0     | RW_SM | Start Offset Calibration. The result is stored in the POFFSET registers. The calib_finished flag is asserted afterwards. Calibration can be stopped by writing a 0 to this bit.                                                                                                                                                                                                                                                                                                                                             |  |

Page 18 Datasheet, Public

# CALIBCFG Register (0xD9)

Figure 30: CALIBCFG Register

|       | Addr: 0xD9                  | CALIBCFG |      |                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                    |  |

|-------|-----------------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field | Name                        | Reset    | Туре | Description                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                    |  |

|       |                             |          |      | ADC target during binary search                                                                                                                                                                                                                                                                   |                                                                                                                                                                                    |  |

|       |                             | 0x2      |      | Value                                                                                                                                                                                                                                                                                             | Target                                                                                                                                                                             |  |

|       |                             |          |      | 0                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                  |  |

|       |                             |          |      | 1                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                  |  |

|       |                             |          |      | 2                                                                                                                                                                                                                                                                                                 | 3                                                                                                                                                                                  |  |

|       | binsrch_target              |          |      | 3                                                                                                                                                                                                                                                                                                 | 7                                                                                                                                                                                  |  |

|       |                             |          | RW   | 4                                                                                                                                                                                                                                                                                                 | 15                                                                                                                                                                                 |  |

| 7:5   |                             |          |      | 5                                                                                                                                                                                                                                                                                                 | 31                                                                                                                                                                                 |  |

| 7.5   |                             |          |      | 6                                                                                                                                                                                                                                                                                                 | 63                                                                                                                                                                                 |  |

|       |                             |          |      | 7                                                                                                                                                                                                                                                                                                 | 127                                                                                                                                                                                |  |

|       |                             |          |      | Note: This target is relative<br>the circuit, a 10-bit target i<br>lowest 2 bits are always ign<br>zero during binary search<br>In hardware, this defines a<br>ignore when comparing to<br>target=4 (target=15) mean<br>ADC are AND'ed with 0xffo<br>zero. Only values 16 or large<br>ADC values. | is used (x4) of which the<br>nored when checking for<br>and zero detection.<br>mask of which bits to<br>o zero. e.g. binsrch_<br>ns that values from the<br>co before comparing to |  |

| 4     | Reserved                    | 1        | RW   | Reserved. Set to 1.                                                                                                                                                                                                                                                                               |                                                                                                                                                                                    |  |

| 3     | prox_auto_offset_<br>adjust | 0        | SC   | This bit enables an automate offset used in proximity meset, when a measurement 0xC0 will be decremented will be set, bit 2 in 0xDC.                                                                                                                                                              | easurements. If this bit is returns zero, the value of                                                                                                                             |  |

Datasheet, PublicPage 19[v2-00] 2023-Feb-23Document Feedback

| Addr: 0xD9 |              | CALIBCFG |        |                                                                                                                                                                  |             |  |

|------------|--------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| Field      | Name         | Reset    | Type   | Description                                                                                                                                                      |             |  |

|            | prx_data_avg | 0        | R_PUSH | Prox data calculation is done by averaging consecutive windows of constant size. At the end of the window, PDATA is updated. Typical use case is HRM measurement |             |  |

| 2:0        |              |          |        | Value                                                                                                                                                            | Window Size |  |

|            |              |          |        | 0                                                                                                                                                                | disable     |  |

|            |              |          |        | 1                                                                                                                                                                | 2           |  |

|            |              |          |        | 2                                                                                                                                                                | 4           |  |

|            |              |          |        | 3                                                                                                                                                                | 8           |  |

|            |              |          |        | 4                                                                                                                                                                | 16          |  |

|            |              |          |        | 5                                                                                                                                                                | 32          |  |

|            |              |          |        | 6                                                                                                                                                                | 64          |  |

|            |              |          |        | 7                                                                                                                                                                | 128         |  |

# CALIBSTAT Register (0xDC)

Figure 31: CALIBSTAT Register

| Addr: 0xDC |                 | CALIBSTAT |      |                                                                                                                                                    |  |

|------------|-----------------|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Field      | Name            | Reset     | Type | Description                                                                                                                                        |  |

| 7:3        | Reserved        | 0         |      | Reserved                                                                                                                                           |  |

| 2          | offset_adjusted | 0         | SC   | This bit is a flag that the automatic proximity offset adjustment has changed the offset in register 0xDC. See 0xD9 for "prox_auto_offset_adjust". |  |

| 1          | Reserved        | 0         |      | Reserved                                                                                                                                           |  |

| 0          | calib_finished  | 0         | R/W  | Offset calibration has finished. Clear bit by writing '1' to it. Bit generates interrupt if cien is asserted.                                      |  |

Page 20Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

# INTENAB Register (0xDD)

Figure 32: INTENAB Register

| Addr: 0xDD |       | INTENAB |                  |                                                                   |  |

|------------|-------|---------|------------------|-------------------------------------------------------------------|--|

| Field      | Name  | Reset   | Type Description |                                                                   |  |

| 6          | psien | 0       | RW               | Writing '1' to this bit enables psat.                             |  |

| 5          | pien  | 0       | RW               | Writing '1' to this bit enables prox interrupt.                   |  |

| 3          | cien  | 0       | RW               | Writing '1' to this bit enables calibration interrupt.            |  |

| 2          | zien  | 0       | RW               | Writing '1' to this bit enables zero_detection/offset_adjustment. |  |

Datasheet, PublicPage 21[v2-00] 2023-Feb-23Document Feedback

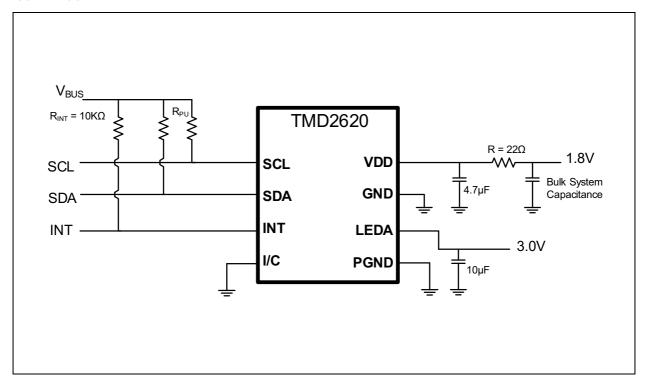

## **Application Information**

Figure 33:

Typical Application Hardware Circuit

#### Note(s):

- 1. Place the  $4.7\mu F$  and  $10\mu F$  capacitors within 5mm of the module.

- 2. The value of the I<sup>2</sup>C pull up resistors RPU should be based on the 1.8V bus voltage, system bus speed and trace capacitance.

- 3. The bulk capacitor can affect the stability of a regulated supply output and should be chosen with the regulator characteristics in mind.

- ${\bf 4.\,GND\,and\,PGND\,should\,be\,connected\,to\,the\,same\,solid\,ground\,plane\,as\,close\,to\,the\,device\,as\,possible.}$

Page 22Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

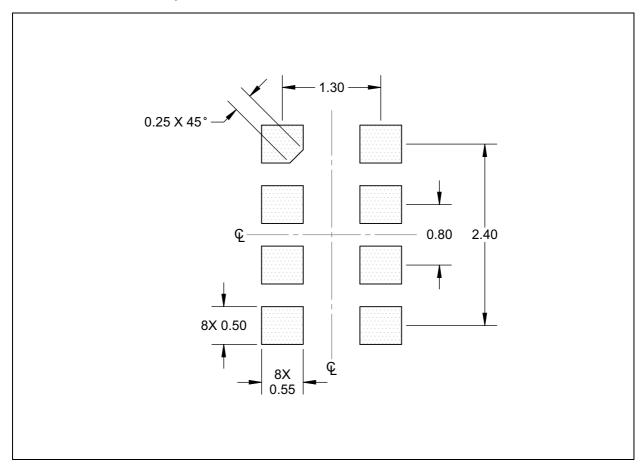

# **PCB Pad Layout**

Figure 34: **Recommended PCB Pad Layout**

#### Note(s):

- 1. All linear dimensions are in millimeters.

- 2. Dimension tolerances are 0.05mm unless otherwise noted.

- 3. This drawing is subject to change without notice.

**Datasheet, Public** Page 23 Document Feedback

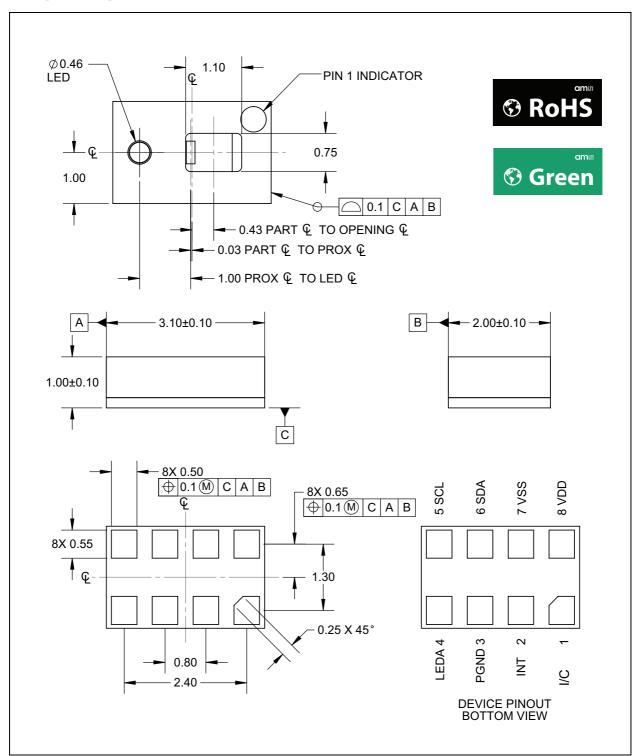

# **Packaging Mechanical Data**

Figure 35: Package Drawing

#### Note(s):

- 1. All linear dimensions are in millimeters.

- 2. Dimension tolerances are 0.05mm unless otherwise noted.

- 3. Contact finish is Au.

- 4. This package contains no lead (Pb).

- 5. This drawing is subject to change without notice.

Page 24Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

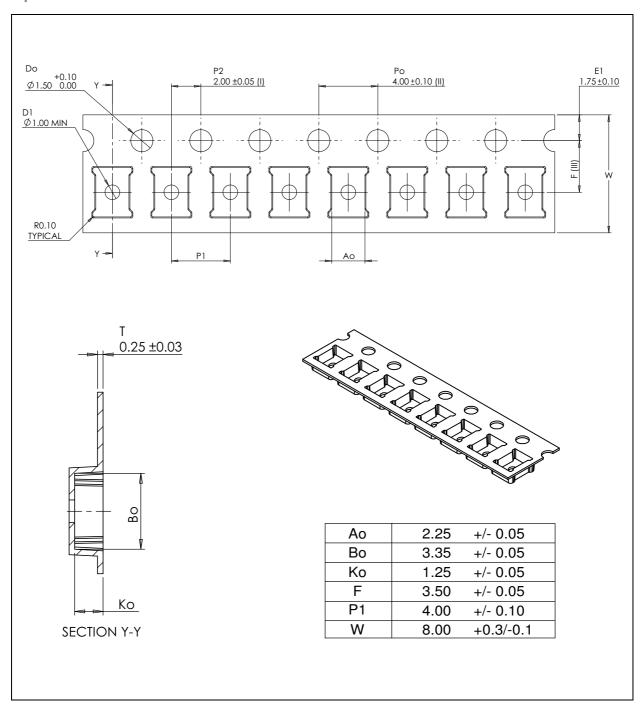

## **Tape & Reel Information**

Figure 36: **Tape & Reel Information**

#### Note(s):

- 1. Measured from centreline of sprocket hole to centreline of pocket.

- 2. Cumulative tolerance of 10 sprocket holes is  $\pm$  0.20.

- 3. Measured from centreline of sprocket hole to centreline of pocket.

- 4. Other material available.

**Datasheet, Public** Page 25 [v2-00] 2023-Feb-23 **Document Feedback**

# Soldering & Storage Information

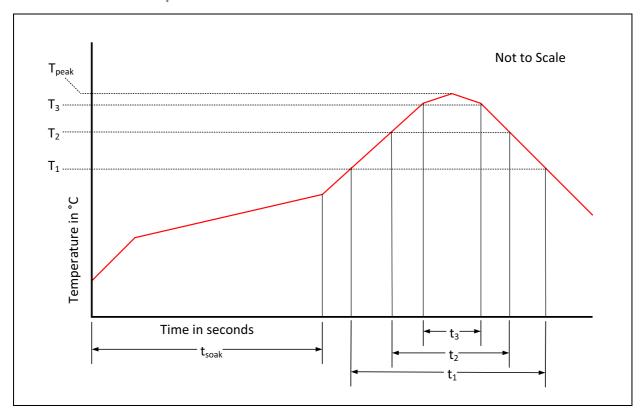

The module has been tested and has demonstrated an ability to be reflow soldered to a PCB substrate.

The solder reflow profile describes the expected maximum heat exposure of components during the solder reflow process of product on a PCB. Temperature is measured on top of component. The components should be limited to a maximum of three passes through this solder reflow profile.

Figure 37: Solder Reflow Profile

| Parameter                                              | Reference         | Device         |

|--------------------------------------------------------|-------------------|----------------|

| Average temperature gradient in preheating             |                   | 2.5°C/s        |

| Soak time                                              | t <sub>soak</sub> | 2 to 3 minutes |

| Time above 217°C (T <sub>1</sub> )                     | t <sub>1</sub>    | Max 60 s       |

| Time above 230°C (T <sub>2</sub> )                     | t <sub>2</sub>    | Max 50 s       |

| Time above T <sub>peak</sub> – 10 °C (T <sub>3</sub> ) | t <sub>3</sub>    | Max 10 s       |

| Peak temperature in reflow                             | $T_{peak}$        | 260℃           |

| Temperature gradient in cooling                        |                   | Max -5°C/s     |

Figure 38: Solder Reflow Profile Graph

Page 26Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

#### **Storage Information**

#### **Moisture Sensitivity**

Optical characteristics of the device can be adversely affected during the soldering process by the release and vaporization of moisture that has been previously absorbed into the package. To ensure the package contains the smallest amount of absorbed moisture possible, each device is baked prior to being dry packed for shipping.

Devices are dry packed in a sealed aluminized envelope called a moisture-barrier bag with silica gel to protect them from ambient moisture during shipping, handling, and storage before use.

#### Shelf Life

The calculated shelf life of the device in an unopened moisture barrier bag is 24 months from the date code on the bag when stored under the following conditions:

· Shelf Life: 24 months

• Ambient Temperature: <40°C

• Relative Humidity: <90%

Rebaking of the devices will be required if the devices exceed the 24 months shelf life or the Humidity Indicator Card shows that the devices were exposed to conditions beyond the allowable moisture region.

#### Floor Life

The module has been assigned a moisture sensitivity level of MSL 3. As a result, the floor life of devices removed from the moisture barrier bag is 168 hours from the time the bag was opened, provided that the devices are stored under the following conditions:

· Floor Life: 168 hours

Ambient Temperature: <30°C</li>

• Relative Humidity: <60%

If the floor life or the temperature/humidity conditions have been exceeded, the devices must be rebaked prior to solder reflow or dry packing.

#### **Rebaking Instructions**

When the shelf life or floor life limits have been exceeded, rebake at 50°C for 12 hours.

Page 27[v2-00] 2023-Feb-23Document Feedback

## **Ordering & Contact Information**

Figure 39: Ordering Information

| Ordering Code | Package | I <sup>2</sup> C Addr | Delivery Form | Delivery Quantity |

|---------------|---------|-----------------------|---------------|-------------------|

| TMD26203      | Module  | 29h                   | 3.30mm reel   | 5000 pcs/reel     |

| TMD26203M     | Module  | 29h                   | 3.30mm reel   | 1000 pcs/reel     |

Buy our products or get free samples online at:

www.ams.com/Products

Technical Support is available at:

www.ams.com/Technical-Support

Provide feedback about this document at:

www.ams.com/Document-Feedback

For further information and requests, e-mail us at:

ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/Contact

#### Headquarters

ams-OSRAM AG Tobelbader Strasse 30 8141 Premstaetten Austria, Europe

Tel: +43 (0) 3136 500 0 Website: www.ams.com

Page 28Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

#### **RoHS Compliant & ams Green** Statement

RoHS: The term RoHS compliant means that ams-OSRAM AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories plus additional 4 substance categories (per amendment EU 2015/863), including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

ams Green (RoHS compliant and no Sb/Br/Cl): ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material) and do not contain Chlorine (Cl not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams-OSRAM AG knowledge and belief as of the date that it is provided. ams-OSRAM AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams-OSRAM AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams-OSRAM AG and ams-OSRAM AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

**Datasheet, Public** Page 29 **Document Feedback**

#### **Copyrights & Disclaimer**

Copyright ams-OSRAM AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams-OSRAM AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams-OSRAM AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams-OSRAM AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams-OSRAM AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams-OSRAM AG for each application. This product is provided by ams-OSRAM AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams-OSRAM AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams-OSRAM AG rendering of technical or other services.

Page 30Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

## **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                               |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                                 |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the design, validation or qualification phase of development. The performance and parameters shown in this document are preliminary without any warranty and are subject to change without notice                  |

| Datasheet                | Production      | Information in this datasheet is based on products in ramp-up to full production or full production which conform to specifications in accordance with the terms of ams-OSRAM AG standard warranty as given in the General Terms of Trade                                |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which conform to specifications in accordance with the terms of ams-OSRAM AG standard warranty as given in the General Terms of Trade, but these products have been superseded and should not be used for new designs |

Datasheet, Public Page 31 [v2-00] 2023-Feb-23 **Document Feedback**

## **Revision Information**

| Changes from 1-02 (2021-Jun-02) to current revision 2-00 (2023-Feb-23) | Page |

|------------------------------------------------------------------------|------|

| Added Description for aux_id                                           | 17   |

| Updated Shelf Life to 24 months                                        | 27   |

#### Note(s):

- 1. Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

- 2. Correction of typographical errors is not explicitly mentioned.

Page 32Datasheet, PublicDocument Feedback[v2-00] 2023-Feb-23

#### **Content Guide**

- **General Description** 1

- 1 **Applications**

- 2 **Block Diagram**

- 3 **Pin Assignment**

- 4 **Absolute Maximum Ratings**

- 5 **Electrical Characteristics**

- 8 **Register Description**

- ENABLE Register (0x80) 9

- 9 PRATE Register (0x82)

- WTIME Register (0x83) 10

- 11 PILT Register (0x88)

- 11 PIHT Register (0x8A)

- 12 PERS Register (0x8C)

- 12 CFG0 Register (0x8D) 13

- PCFG0 Register (0x8E)

- PCFG1 Register (0x8F) 14

- 14 REVID Register (0x91)

- ID Register (0x92)

- STATUS Register (0x93) 16

- PDATA Register (0x9C)

- REVID2 Register (0x9E) 17

- 17 CFG3 Register (0xAB)

- 18 POFFSET\_L Register (0xC0)

- 18 POFFSET H Register (0xC1)

- CALIB Register (0xD7) 18

- 19 CALIBCFG Register (0xD9)

- 20 CALIBSTAT Register (0xDC)

- 21 INTENAB Register (0xDD)

- 22 Application Information

- 23 PCB Pad Layout

- 24 Packaging Mechanical Data

- 25 Tape & Reel Information

- 26 Soldering & Storage Information

- 27 Storage Information

- 27 Moisture Sensitivity

- 27 Shelf Life

- Floor Life 27

- **Rebaking Instructions** 27

- 28 Ordering & Contact Information

- 29 **RoHS Compliant & ams Green Statement**

- 30 Copyrights & Disclaimer

- **Document Status**

- 32 Revision Information

**Datasheet, Public** Page 33 [v2-00] 2023-Feb-23 **Document Feedback**