- Organization:

- TM8SK64JPN . . . 8 388 608 x 64 Bits

- Single 3.3-V Power Supply (±10% Tolerance)

- Designed for 66-MHz 4-Clock Systems

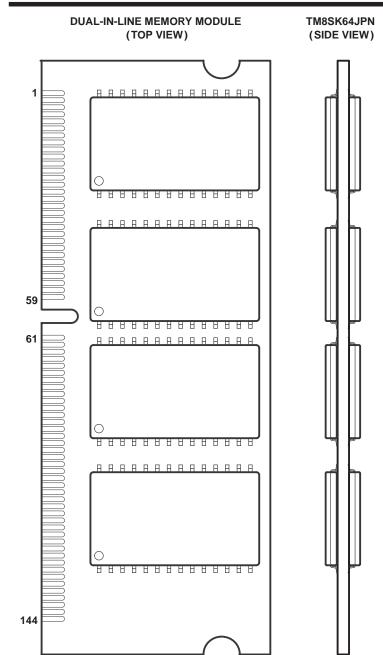

- JEDEC 144-Pin Small Outline Dual-In-Line Memory Module (SODIMM) Without Buffer for Use With Socket

- Uses Eight 64M-Bit Synchronous Dynamic RAMs (SDRAMs) (8M × 8-Bit) in Plastic Thin Small-Outline Packages (TSOPs)

- Byte-Read/Write Capability

- Performance Ranges:

- High-Speed, Low-Noise, Low-Voltage TTL (LVTTL) Interface

- Read Latencies 2 and 3 Supported

- Support Burst-Interleave and Burst-Interrupt Operations

- Burst Length Programmable to 1, 2, 4, and 8

- Four Banks for On-Chip Interleaving (Gapless Access)

- Ambient Temperature Range 0°C to 70°C

- Gold-Plated Contacts

- Pipeline Architecture

- Serial Presence Detect (SPD) Using EEPROM

|               | CLOCK | RONOUS<br>CYCLE<br>ME | ACCESS TIME<br>CLOCK TO<br>OUTPUT |        | REFRESI<br>INTERVA |  |

|---------------|-------|-----------------------|-----------------------------------|--------|--------------------|--|

|               | tCK3  | tCK2                  | tAC3                              | tAC2   | tREF               |  |

| '8SK64.IPN-10 | 10 ns | 15 ns                 | 7.5 ns                            | 7.5 ns | 64 ms              |  |

#### description

The TM8SK64JPN is a 64M-byte, 144-pin SODIMM. The SODIMM is composed of eight TMS664814DGE, 8388608 x 8-bit SDRAMs, each in a 400-mil, 54-pin plastic thin small-outline package (TSOP) mounted on a substrate with decoupling capacitors. See the TMS664814 data sheet (literature number SMOS695).

#### operation

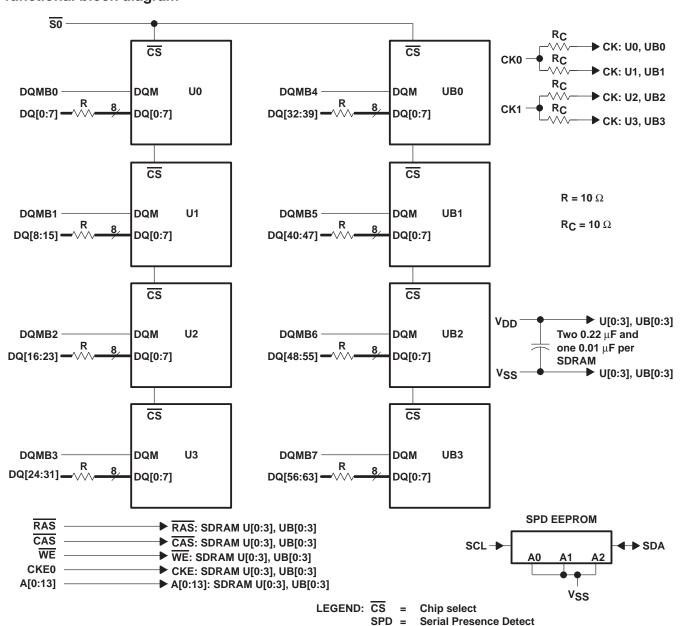

The TM8SK64JPN operates as eight TMS664814DGE devices that are connected as shown in the functional block diagram.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SMMS717 - JULY 1998

| PIN NOMENCLATURE |                       |  |  |  |

|------------------|-----------------------|--|--|--|

| A[0:11]          | Row-Address Inputs    |  |  |  |

| A[0:8]           | Column-Address Inputs |  |  |  |

| A13/BA0          | Bank Select Zero      |  |  |  |

| A12/BA1          | Bank Select One       |  |  |  |

| CAS              | Column-Address Strobe |  |  |  |

| CKE0             | Clock Enable          |  |  |  |

| CK[0:1]          | System Clock          |  |  |  |

| DQ[0:63]         | Data In/Data Out      |  |  |  |

| DQMB[0:7]        | Data in/Data Out      |  |  |  |

|                  | Mask Enable           |  |  |  |

| NC               | No Connect            |  |  |  |

| RAS              | Row-Address Strobe    |  |  |  |

| S0               | Chip Select           |  |  |  |

| SCL              | SPD Clock             |  |  |  |

| SDA              | SPD Address/Data      |  |  |  |

| $V_{DD}$         | 3.3-V Supply          |  |  |  |

| $v_{SS}$         | Ground                |  |  |  |

| WE               | Write Enable          |  |  |  |

## **Pin Assignments**

|     | PIN             |     | PIN       |     | PIN             |     | PIN             |

|-----|-----------------|-----|-----------|-----|-----------------|-----|-----------------|

| NO. | NAME            | NO. | NAME      | NO. | NAME            | NO. | NAME            |

| 1   | V <sub>SS</sub> | 37  | DQ8       | 73  | NC              | 109 | A9              |

| 2   | V <sub>SS</sub> | 38  | DQ40      | 74  | CK1             | 110 | A12/BA1         |

| 3   | DQ0             | 39  | DQ9       | 75  | VSS             | 111 | A10             |

| 4   | DQ32            | 40  | DQ41      | 76  | VSS             | 112 | A11             |

| 5   | DQ1             | 41  | DQ10      | 77  | NC              | 113 | $V_{DD}$        |

| 6   | DQ33            | 42  | DQ42      | 78  | NC              | 114 | $V_{DD}$        |

| 7   | DQ2             | 43  | DQ11      | 79  | NC              | 115 | DQMB2           |

| 8   | DQ34            | 44  | DQ43      | 80  | NC              | 116 | DQMB6           |

| 9   | DQ3             | 45  | $V_{DD}$  | 81  | $V_{DD}$        | 117 | DQMB3           |

| 10  | DQ35            | 46  | $V_{DD}$  | 82  | $V_{DD}$        | 118 | DQMB7           |

| 11  | $V_{DD}$        | 47  | DQ12      | 83  | DQ16            | 119 | V <sub>SS</sub> |

| 12  | $V_{DD}$        | 48  | DQ44      | 84  | DQ48            | 120 | V <sub>SS</sub> |

| 13  | DQ4             | 49  | DQ13      | 85  | DQ17            | 121 | DQ24            |

| 14  | DQ36            | 50  | DQ45      | 86  | DQ49            | 122 | DQ56            |

| 15  | DQ5             | 51  | DQ14      | 87  | DQ18            | 123 | DQ25            |

| 16  | DQ37            | 52  | DQ46      | 88  | DQ50            | 124 | DQ57            |

| 17  | DQ6             | 53  | DQ15      | 89  | DQ19            | 125 | DQ26            |

| 18  | DQ38            | 54  | DQ47      | 90  | DQ51            | 126 | DQ58            |

| 19  | DQ7             | 55  | VSS       | 91  | VSS             | 127 | DQ27            |

| 20  | DQ39            | 56  | $V_{SS}$  | 92  | $V_{SS}$        | 128 | DQ59            |

| 21  | $V_{SS}$        | 57  | NC        | 93  | DQ20            | 129 | $V_{DD}$        |

| 22  | V <sub>SS</sub> | 58  | NC        | 94  | DQ52            | 130 | $V_{DD}$        |

| 23  | DQMB0           | 59  | NC        | 95  | DQ21            | 131 | DQ28            |

| 24  | DQMB4           | 60  | NC        | 96  | DQ53            | 132 | DQ60            |

| 25  | DQMB1           | 61  | CK0       | 97  | DQ22            | 133 | DQ29            |

| 26  | DQMB5           | 62  | CKE0      | 98  | DQ54            | 134 | DQ61            |

| 27  | $V_{DD}$        | 63  | $V_{DD}$  | 99  | DQ23            | 135 | DQ30            |

| 28  | $V_{DD}$        | 64  | $V_{DD}$  | 100 | DQ55            | 136 | DQ62            |

| 29  | A0              | 65  | RAS       | 101 | $V_{DD}$        | 137 | DQ31            |

| 30  | А3              | 66  | CAS       | 102 | $V_{DD}$        | 138 | DQ63            |

| 31  | A1              | 67  | WE        | 103 | A6              | 139 | V <sub>SS</sub> |

| 32  | A4              | 68  | NC        | 104 | A7              | 140 | VSS             |

| 33  | A2              | 69  | <u>S0</u> | 105 | A8              | 141 | SDA             |

| 34  | A5              | 70  | NC        | 106 | A13/BA0         | 142 | SCL             |

| 35  | VSS             | 71  | NC        | 107 | V <sub>SS</sub> | 143 | $V_{DD}$        |

| 36  | V <sub>SS</sub> | 72  | NC        | 108 | VSS             | 144 | $V_{DD}$        |

#### small-outline dual-in-line memory module and components

The small-outline dual-in-line memory module and components include:

- PC substrate: 1,10 ± 0,1 mm (0.04 inch) nominal thickness

- Bypass capacitors: Multilayer ceramic

- Contact area: Nickel plate and gold plate over copper

### functional block diagram

SMMS717 - JULY 1998

##

NOTE 1: All voltage values are with respect to VSS.

## recommended operating conditions

|          |                                         | MIN  | NOM | MAX                   | UNIT |

|----------|-----------------------------------------|------|-----|-----------------------|------|

| $V_{DD}$ | Supply voltage                          | 3    | 3.3 | 3.6                   | V    |

| VSS      | Supply voltage                          |      | 0   |                       | V    |

| VIH      | High-level input voltage                | 2    |     | V <sub>DD</sub> + 0.3 | V    |

| VIH-SPD  | High-level input voltage for SPD device | 2    |     | 5.5                   | V    |

| $V_{IL}$ | Low-level input voltage                 | -0.3 |     | 0.8                   | V    |

| TA       | Operating ambient temperature           | 0    |     | 70                    | °C   |

## capacitance over recommended ranges of supply voltage and ambient temperature, f = 1 MHz (see Note 2)<sup>‡</sup>

|                       | PARAMETER                                                           | MIN | MAX | UNIT |

|-----------------------|---------------------------------------------------------------------|-----|-----|------|

| C <sub>i(CK)</sub>    | Input capacitance, CK input                                         | 2.5 | 4   | pF   |

| C <sub>i(AC)</sub>    | Input capacitance, address and control inputs: A0-A13, RAS, CAS, WE | 2.5 | 5   | pF   |

| C <sub>i(CKE)</sub>   | Input capacitance, CKE input                                        |     | 5   | pF   |

| Co                    | Output capacitance                                                  | 4   | 6.5 | pF   |

| C <sub>i(DQMBx)</sub> | Input capacitance, DQMBx input                                      | 2.5 | 5   | pF   |

| C <sub>i(Sx)</sub>    | Input capacitance, Sx input                                         | 2.5 | 5   | pF   |

| C <sub>i/o(SDA)</sub> | Input/output capacitance, SDA input                                 |     | 9   | pF   |

| C <sub>i(SPD)</sub>   | Input capacitance, SPD inputs (except SDA)                          |     | 7   | pF   |

<sup>‡</sup> Specifications in this table represent a single SDRAM device.

NOTE 2:  $V_{DD} = 3.3 \text{ V} \pm 0.3 \text{ V}$ . Bias on pins under test is 0 V.

SMMS717 - JULY 1998

## electrical characteristics over recommended ranges of supply voltage and ambient temperature (unless otherwise noted) (see Note 3)<sup>†</sup>

|                    | PARAMETER                                                 | TEST CONDIT                                                                                                   | IONS                | MIN | MAX | UNIT |

|--------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|------|

| VOH                | High-level output voltage                                 | $I_{OH} = -2 \text{ mA}$                                                                                      |                     | 2.4 |     | V    |

| VOL                | Low-level output voltage                                  | $I_{OL} = 2 \text{ mA}$                                                                                       |                     |     | 0.4 | V    |

| Ц                  | Input current (leakage)                                   | 0 V < V <sub>I</sub> < V <sub>DD</sub> + 0.3 V,<br>All other pins = 0 V to V <sub>DD</sub>                    |                     |     | ±10 | μΑ   |

| IO                 | Output current (leakage)                                  | 0 V < V <sub>O</sub> < V <sub>DD</sub> + 0.3 V,<br>Output disabled                                            |                     |     | ±10 | μА   |

| laa.               | Operating current                                         | Burst length = 1,<br>t <sub>RC</sub> ≥ t <sub>RC</sub> MIN                                                    | CAS latency = 2     |     | 105 | mA   |

| ICC1               | Operating current IOH/IOL = 0 mA, (see Notes 4, 5, and 6) |                                                                                                               | CAS latency = 3     |     | 115 | mA   |

| ICC2P              | Drackers standby current in newer days made               | CKE $\leq$ V <sub>IL</sub> MAX, t <sub>CK</sub> = 15 ns                                                       | (see Note 7)        |     | 1   | mA   |

| ICC2PS             | Precharge standby current in power-down mode              | CKE and CK ≤ V <sub>IL</sub> MAX, t <sub>CK</sub>                                                             | = ∞ (see Note 8)    |     | 1   | mA   |

| I <sub>CC2N</sub>  | Precharge standby current in nonpower-down                | CKE $\geq$ V <sub>IH</sub> MIN, t <sub>CK</sub> = 15 ns                                                       | (see Note 7)        |     | 40  | mA   |

| I <sub>CC2NS</sub> | mode                                                      | $t_{CK} = \infty$ (see Note 8)                                                                                |                     |     | 5   | mA   |

| I <sub>CC3P</sub>  |                                                           | CKE $\leq$ V <sub>IL</sub> MAX, t <sub>CK</sub> = 15 ns                                                       | (see Notes 4 and 7) |     | 8   | mA   |

| ICC3PS             | Active standby current in power-down mode                 | CKE and CK ≤ V <sub>IL</sub> MAX, t <sub>CK</sub> (see Notes 4 and 8)                                         | = ∞                 |     | 8   | mA   |

| I <sub>CC3N</sub>  |                                                           | CKE $\geq$ V <sub>IH</sub> MIN, t <sub>CK</sub> = 15 ns                                                       | (see Notes 4 and 7) |     | 60  | mA   |

| ICC3NS             | Active standby current in nonpower-down mode              | CKE $\geq$ V <sub>IH</sub> MIN, CK $\leq$ V <sub>IL</sub> MAX, t <sub>CK</sub> = $\infty$ (see Notes 4 and 8) |                     |     | 10  | mA   |

| laa.               | Durat ourrant                                             | Page burst, I <sub>OH</sub> /I <sub>OL</sub> = 0 mA<br>All banks activated,                                   | CAS latency = 2     |     | 140 | mA   |

| ICC4               | Burst current                                             | n <sub>CCD</sub> = one cycle<br>(see Notes 9 and 10)                                                          | CAS latency = 3     |     | 200 | mA   |

| la a -             | Autovofrach aurrent                                       | $t_{RC} \le t_{RC} MIN$                                                                                       | CAS latency = 2     |     | 150 | mA   |

| ICC5               | Autorefresh current                                       | (see Notes 5 and 8)                                                                                           | CAS latency = 3     |     | 150 | mA   |

| I <sub>CC6</sub>   | Self-refresh current                                      | CKE ≤ V <sub>IL</sub> MAX                                                                                     |                     |     | 2   | mA   |

<sup>†</sup> Specifications in this table represent a single SDRAM device.

NOTES: 3. All specifications apply to the device after power-up initialization. All control and address inputs must be stable and valid.

- 4. Only one bank is activated.

- 5. t<sub>RC</sub> ≥ t<sub>RC</sub> MIN

- 6. Control and address inputs change state twice during t<sub>RC</sub>.

- 7. Control and address inputs change state once every 30 ns.

- 8. Control and address inputs do not change state (stable).

- 9. Control and address inputs change state once every cycle.

- 10. Continuous burst access, n<sub>CCD</sub> = 1 cycle

SMMS717 - JULY 1998

## ac timing requirements†‡

|                  |                                                                                                          |                 | MIN | MAX      | UNIT |

|------------------|----------------------------------------------------------------------------------------------------------|-----------------|-----|----------|------|

| t <sub>CK2</sub> | Cycle time, CK                                                                                           | CAS latency = 2 | 15  |          | ns   |

| t <sub>CK3</sub> | Cycle time, CK                                                                                           | CAS latency = 3 | 10  |          | ns   |

| <sup>t</sup> CH  | Pulse duration, CK high                                                                                  |                 | 3   |          | ns   |

| tCL              | Pulse duration, CK low                                                                                   |                 | 3   |          | ns   |

| tAC2             | Access time, CK high to data out (see Note 11)                                                           | CAS latency = 2 |     | 7.5      | ns   |

| t <sub>AC3</sub> | Access time, CK high to data out (see Note 11)                                                           | CAS latency = 3 |     | 7.5      | ns   |

| <sup>t</sup> OH  | Hold time, CK high to data out                                                                           |                 | 3   |          | ns   |

| t <sub>LZ</sub>  | Delay time, CK high to DQ in low-impedance state (see Note 12)                                           |                 | 2   |          | ns   |

| <sup>t</sup> HZ  | Delay time, CK high to DQ in high-impedance state (see Note 13)                                          |                 |     | 10       | ns   |

| t <sub>IS</sub>  | Setup time, address, control, and data input                                                             |                 | 2   |          | ns   |

| tIH              | Hold time, address, control, and data input                                                              |                 | 1   |          | ns   |

| tCESP            | Power down/self-refresh exit time                                                                        | 10              |     | ns       |      |

| tRAS             | Delay time, ACTV command to DEAC or DCAB command                                                         |                 | 50  | 100000   | ns   |

| tRC              | Delay time, ACTV, MRS, REFR, or SLFR to ACTV, MRS, REFR, or SLFR c                                       | ommand          | 80  |          | ns   |

| tRCD             | Delay time ACTV command to READ, READ-P, WRT, or WRT-P command                                           | (see Note 14)   | 30  |          | ns   |

| t <sub>RP</sub>  | Delay time, DEAC or DCAB command to ACTV, MRS, REFR, or SLFR command                                     |                 |     |          | ns   |

| t <sub>RRD</sub> | Delay time, ACTV command in one bank to ACTV command in the other bank                                   |                 |     |          | ns   |

| tRSA             | Delay time, MRS command to ACTV, MRS, REFR, or SLFR command                                              |                 |     |          | ns   |

| <sup>t</sup> APR | Final data out of READ-P operation to ACTV, MRS, SLFR, or REFR command t <sub>RP</sub> – (CL-1)          |                 |     | −1)* tCK | ns   |

| tAPW             | Final data in of WRT-P operation to ACTV, MRS, SLFR, or REFR command t <sub>RP</sub> + 1 t <sub>CK</sub> |                 |     | ns       |      |

| tŢ               | Transition time                                                                                          |                 |     | 5        | ms   |

<sup>†</sup> All references are made to the rising transition of CK unless otherwise noted.

- NOTES: 11. t<sub>AC</sub> is referenced from the rising transition of CK that precedes the data-out cycle. For example, the first data out t<sub>AC</sub> is referenced from the rising transition of CK that is read latency (one cycle after the READ command). Access time is measured at output reference level 1.4 V.

- 12. t<sub>1</sub> z is measured from the rising transition of CK that is read latency (one cycle after the READ command).

- 13. t<sub>HZ</sub> (max) defines the time at which the outputs are no longer driven and is not referenced to output voltage levels.

- 14. For read or write operations with automatic deactivate, t<sub>RCD</sub> must be set to satisfy minimum t<sub>RAS</sub>.

<sup>‡</sup> Specifications in this table represent a single SDRAM device.

SMMS717 - JULY 1998

## clock timing requirements†‡

|                   |                                                                                 | MIN | MAX | UNIT   |

|-------------------|---------------------------------------------------------------------------------|-----|-----|--------|

| tREF              | Refresh interval                                                                |     | 64  | ms     |

| nCCD              | Delay time, READ or WRT command to an interrupting command                      | 1   |     | cycles |

| nCDD              | Delay time, $\overline{CS}$ low or high to input enabled or inhibited           | 0   |     | cycles |

| nCLE              | Delay time, CKE high or low to CLK enabled or disabled                          | 1   | 1   | cycles |

| nCWL              | Delay time, final data in of WRT operation to READ, READ-P, WRT, or WRT-P       | 1   |     | cycles |

| nDID              | Delay time, ENBL or MASK command to enabled or masked data in                   |     | 0   | cycles |

| n <sub>DOD</sub>  | Delay time, ENBL or MASK command to enabled or masked data out                  | 2   | 2   | cycles |

| n <sub>HZP2</sub> | Delay time, DEAC or DCAB, command to DQ in high-impedance state CAS latency = 2 |     | 2   | cycles |

| nHZP3             | Delay time, DEAC or DCAB, command to DQ in high-impedance state CAS latency = 3 |     | 3   | cycles |

| nWCD              | Delay time, WRT command to first data in                                        | 0   | 0   | cycles |

| n <sub>WR</sub>   | Delay time, final data in of WRT operation to DEAC or DCAB command              | 1   |     | cycle  |

<sup>&</sup>lt;sup>†</sup> All references are made to the rising transition of CK unless otherwise noted.

<sup>‡</sup> A CK cycle can be considered as contributing to a timing requirement for those parameters defined in cycle units only when not gated by CKE (those CK cycles occurring during the time when CKE is asserted low).

#### serial presence detect

The serial presence detect (SPD) is contained in a 2K-bit serial EEPROM located on the module. The SPD nonvolatile EEPROM contains various data such as module configuration, SDRAM organization, and timing parameters (see Table 1). Only the first 128 bytes are programmed by Texas Instruments, while the remaining 128 bytes are available for customer use. Programming is done through an IIC bus using the clock (SCL) and data (SDA) signals. All Texas Instruments modules comply with the current JEDEC SPD standards. See the Texas Instruments *Serial Presence Detect Technical Reference* (literature number SMMU001) for further details. Table 1 lists the SPD contents.

**Table 1. Serial Presence Detect Data**

| BYTE<br>NO. | DESCRIPTION OF FUNCTION                                                        | ITEM                                                                               | DATA |

|-------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------|

| 0           | Defines number of bytes written into serial memory during module manufacturing | 128 bytes                                                                          | 80h  |

| 1           | Total number of bytes of SPD memory device                                     | 256 bytes                                                                          | 08h  |

| 2           | Fundamental memory type (FPM, EDO, SDRAM,)                                     | SDRAM                                                                              | 04h  |

| 3           | Number of row addresses on this assembly                                       | 12                                                                                 | 0Ch  |

| 4           | Number of column addresses on this assembly                                    | 9                                                                                  | 09h  |

| 5           | Number of module rows on this assembly                                         | 1 bank                                                                             | 01h  |

| 6           | Data width of this assembly                                                    | 64 bits                                                                            | 40h  |

| 7           | Data width continuation                                                        |                                                                                    | 00h  |

| 8           | Voltage interface standard of this assembly                                    | LVTTL                                                                              | 01h  |

| 9           | SDRAM cycle time at maximum supported CAS latency (CL), CL = X                 | t <sub>CK</sub> = 10 ns                                                            | A0h  |

| 10          | SDRAM access from clock at CL = X                                              | t <sub>AC</sub> = 7.5 ns                                                           | 75h  |

| 11          | SODIMM configuration type (non-parity, parity, error correcting code [ECC])    | Non-Parity                                                                         | 00h  |

| 12          | Refresh rate/type                                                              | 15.6 μs/<br>self-refresh                                                           | 80h  |

| 13          | SDRAM width, primary DRAM                                                      | x8                                                                                 | 08h  |

| 14          | Error-checking SDRAM data width                                                | N/A                                                                                | 00h  |

| 15          | Minimum clock delay, back-to-back random column addresses                      | 1 CK cycle                                                                         | 01h  |

| 16          | Burst lengths supported                                                        | 1, 2, 4, and 8                                                                     | 0Fh  |

| 17          | Number of banks on each SDRAM device                                           | 4 banks                                                                            | 04h  |

| 18          | CAS latencies supported                                                        | 2, 3                                                                               | 06h  |

| 19          | CS latency                                                                     | 0                                                                                  | 01h  |

| 20          | Write latency                                                                  | 0                                                                                  | 01h  |

| 21          | SDRAM module attributes                                                        | Non-buffered/<br>Non-registered                                                    | 00h  |

| 22          | SDRAM device attributes: general                                               | V <sub>DD</sub> tolerance = (±10%) Burst read/write, precharge all, auto precharge | 0Eh  |

| 23          | Minimum clock cycle time at $CL = X - 1$                                       | t <sub>CK</sub> = 15 ns                                                            | F0h  |

SMMS717 - JULY 1998

### serial presence detect (continued)

**Table 1. Serial Presence Detect Data (Continued)**

| BYTE<br>NO. | DESCRIPTION OF FUNCTION                           | ITEM                      | DATA    |

|-------------|---------------------------------------------------|---------------------------|---------|

| 24          | Maximum data-access time from clock at CL = X - 1 | $t_{AC} = 7.5 \text{ ns}$ | 75h     |

| 25          | Minimum clock cycle time at $CL = X - 2$          | N/A                       | 00h     |

| 26          | Maximum data-access time from clock at CL = X − 2 | N/A                       | 00h     |

| 27          | Minimum row-precharge time                        | t <sub>RP</sub> = 30 ns   | 1Eh     |

| 28          | Minimum row-active to row-active delay            | t <sub>RRD</sub> = 20 ns  | 14h     |

| 29          | Minimum RAS-to-CAS delay                          | t <sub>RCD</sub> = 30 ns  | 1Eh     |

| 30          | Minimum RAS pulse width                           | t <sub>RAS</sub> =50 ns   | 32h     |

| 31          | Command and address signal input setup time       | $t_{IS} = 2 \text{ ns}$   | 20h     |

| 32          | Command and address signal input hold time        | t <sub>IH</sub> = 1 ns    | 10h     |

| 33          | Data signal input setup time                      | t <sub>IS</sub> = 2 ns    | 20h     |

| 34          | Data signal input hold time                       | t <sub>IH</sub> = 1 ns    | 10h     |

| 35-61       | Superset features (may be used in the future)     |                           |         |

| 62          | SPD revision                                      | Rev. 1.2                  | 12h     |

| 63          | Checksum for byte 0 – 62                          | 14                        | 0Eh     |

| 64-71       | Manufacturer's JEDEC ID code per JEP-106E         | 97                        | 970000h |

| 72          | Manufacturing location <sup>†</sup>               | TBD                       |         |

| 73          | Manufacturer's part number                        | Т                         | 54h     |

| 74          | Manufacturer's part number                        | M                         | 4Dh     |

| 75          | Manufacturer's part number                        | 8                         | 38h     |

| 76          | Manufacturer's part number                        | S                         | 53h     |

| 77          | Manufacturer's part number                        | K                         | 4Bh     |

| 78          | Manufacturer's part number                        | 6                         | 36h     |

| 79          | Manufacturer's part number                        | 4                         | 34h     |

| 80          | Manufacturer's part number                        | J                         | 4Ah     |

| 81          | Manufacturer's part number                        | Р                         | 50h     |

| 82          | Manufacturer's part number                        | N                         | 4Eh     |

| 83          | Manufacturer's part number                        | -                         | 2Dh     |

| 84          | Manufacturer's part number                        | 1                         | 31h     |

| 85          | Manufacturer's part number                        | 0                         | 30h     |

| 86-90       | Manufacturer's part number                        | SPACE                     | 20h     |

| 91          | Die revision code <sup>†</sup>                    | TBD                       |         |

| 92          | PCB revision code <sup>†</sup>                    | TBD                       |         |

| 93-94       | Manufacturing date <sup>†</sup>                   | TBD                       |         |

| 95-98       | Assembly serial number <sup>†</sup>               | TBD                       |         |

| 99-125      | Manufacturer-specific data <sup>†</sup>           | TBD                       |         |

| 126         | Clock frequency                                   | 66 MHz                    | 66h     |

| 127         | SDRAM component and clock interconnection details | 199                       | C7h     |

| 128–166     | System integrator's specific data <sup>‡</sup>    | TBD                       |         |

| 167–255     | Open                                              |                           |         |

<sup>†</sup> TBD indicates values are determined at manufacturing time and are module dependent.

<sup>&</sup>lt;sup>‡</sup> These TBD values are determined and programmed by the customer (optional).

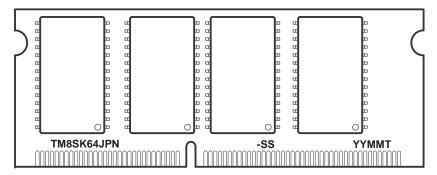

## device symbolization (TM8SK64JPN)

YY = Year Code

MM = Month Code

T = Assembly Site Code

-SS = Speed Code

NOTE A: Location of symbolization may vary.

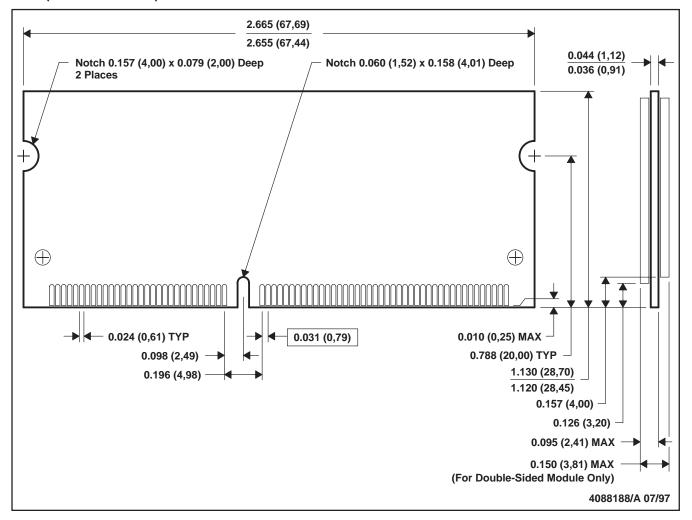

#### **MECHANICAL DATA**

### BDQ (R-SODIMM-N144)

#### SMALL OUTLINE DUAL IN-LINE MEMORY MODULE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Falls within JEDEC MO-190

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated