**tenx** reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. **tenx** does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. **tenx** products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses **tenx** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **tenx** and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that **tenx** was negligent regarding the design or manufacture of the part.

## AMENDMENT HISTORY

| Version | Date      | Description                                                                                                    |

|---------|-----------|----------------------------------------------------------------------------------------------------------------|

| 0.90    | Feb, 2017 | New release.                                                                                                   |

| 0.91    | Aug, 2017 | <ol> <li>FRC accuracy &amp; Temp. curve</li> <li>Add Tiny current description</li> <li>Other detail</li> </ol> |

| 0.92    | May, 2018 | <ol> <li>Add package DIP-20, QFN-20</li> <li>CFGW descript update</li> </ol>                                   |

# CONTENTS

| AM  | END                 | MENT HISTORY                                                       | 2  |

|-----|---------------------|--------------------------------------------------------------------|----|

| TM  | 52 <sub>Serie</sub> | s F52xx FAMILY                                                     | 5  |

| GEN | NERA                | AL DESCRPTION                                                      | 6  |

| BLC | <b>)CK</b>          | DIAGRAM                                                            | 6  |

| FEA | TUR                 | ES                                                                 | 7  |

| PIN | ASS                 | IGNMENT1                                                           | 0  |

| PIN | DES                 | CRIPTION1                                                          | 1  |

| PIN | SUM                 | IMARY1                                                             | 2  |

| FUN | ICTI                | ONAL DESCRIPTION1                                                  | 3  |

| 1.  | CPU                 | J Core                                                             | 3  |

|     | 1.1                 | Accumulator (ACC)                                                  | 3  |

|     | 1.2                 | B Register (B)1                                                    | 3  |

|     | 1.3                 | Stack Pointer (SP)                                                 |    |

|     | 1.4<br>1.5          | Dual Data Pointer (DPTRs)    1      Program Status Word (PSW)    1 |    |

| 2   |                     |                                                                    |    |

| 2.  |                     | nory1                                                              |    |

|     | 2.1<br>2.2          | Program Memory                                                     |    |

| 2   |                     | /er                                                                |    |

|     |                     |                                                                    |    |

| 4.  | Res                 | et2                                                                |    |

|     | 4.1                 | Power on Reset                                                     |    |

|     | 4.2<br>4.3          | External Pin Reset                                                 |    |

|     | 4.5<br>4.4          | Watchdog Timer Reset                                               |    |

|     | 4.5                 | Low Voltage Reset                                                  |    |

| 5.  | Clo                 | ck Circuitry and Operation Mode2                                   |    |

|     | 5.1                 | System Clock2                                                      |    |

|     | 5.2                 | Operation Mode                                                     | 27 |

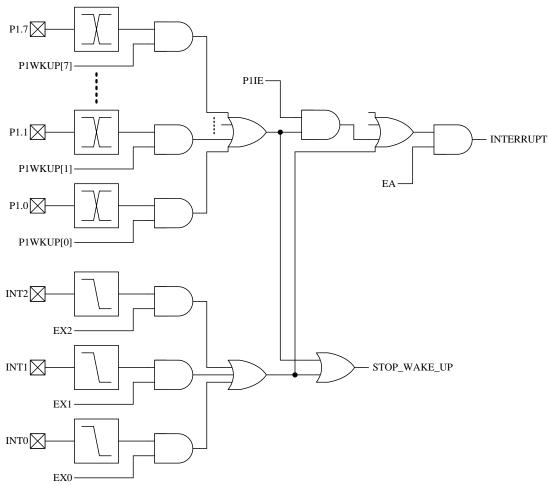

| 6.  | Inte                | rrupt and Wake-up2                                                 | 28 |

|     | 6.1                 | Interrupt Enable and Priority Control                              | 28 |

|     | 6.2                 | Pin Interrupt                                                      |    |

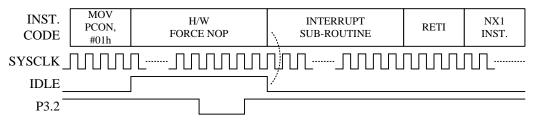

|     | 6.3                 | Idle Mode Wake up and Interrupt                                    |    |

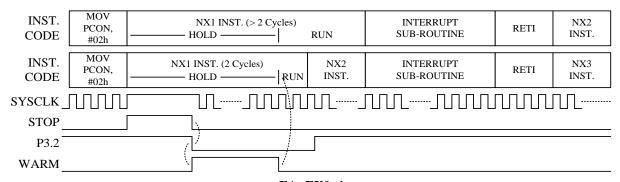

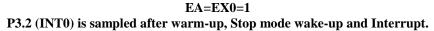

|     | 6.4                 | Stop Mode Wake up and Interrupt                                    |    |

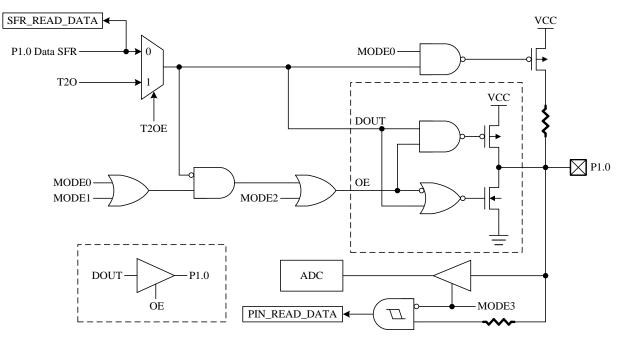

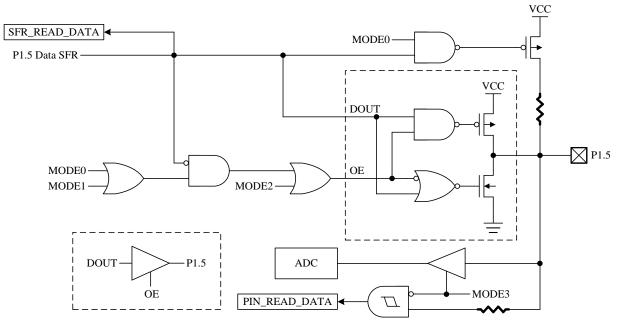

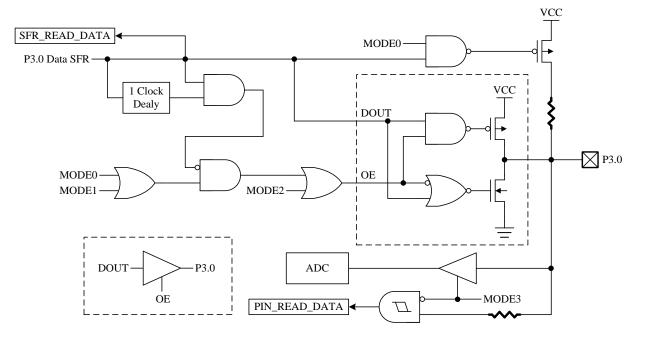

| 7.  | I/O                 | Ports                                                              | 4  |

|     | 7.1                 | Port1 & P2.1~P2.0 & P3.6~P3.0                                      |    |

|     | 7.2                 | P3.7                                                               | 0  |

| 8.                                             | Timers4                                                                                                                                                                                                                                                                     | 1                                 |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|                                                | 8.1       Timer0/Timer1/Timer2                                                                                                                                                                                                                                              |                                   |

| 9.                                             | UART                                                                                                                                                                                                                                                                        | 6                                 |

| 10                                             | . PWMs                                                                                                                                                                                                                                                                      | 8                                 |

| 11                                             | ADC                                                                                                                                                                                                                                                                         | 1                                 |

|                                                | 11.1 ADC Channels511.2 ADC Conversion Time511.3 VBG Voltage Conversion5                                                                                                                                                                                                     | 2                                 |

| 12                                             | In Circuit Emulation (ICE) Mode                                                                                                                                                                                                                                             | 5                                 |

| SFR                                            | & CFGW MAP                                                                                                                                                                                                                                                                  | 5                                 |

| SFR                                            | & CFGW DESCRIPTION                                                                                                                                                                                                                                                          | 8                                 |

|                                                |                                                                                                                                                                                                                                                                             |                                   |

| INST                                           | <b>GRUCTION SET</b>                                                                                                                                                                                                                                                         | 7                                 |

|                                                | GRUCTION SET       6         CTRICAL CHARACTERISTICS       7                                                                                                                                                                                                                |                                   |

|                                                |                                                                                                                                                                                                                                                                             | 0                                 |

| ELE                                            | CTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                     | <b>0</b><br>0                     |

| <b>ELE</b><br>1.                               | CTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                     | 0<br>0<br>0                       |

| <b>ELE</b><br>1.<br>2.                         | CTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                     | <b>0</b><br>0<br>0                |

| ELE<br>1.<br>2.<br>3.                          | CTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                     | <b>0</b><br>0<br>1<br>1           |

| ELE<br>1.<br>2.<br>3.<br>4.<br>5.              | CTRICAL CHARACTERISTICS       7         Absolute Maximum Ratings       7         DC Characteristics       7         Clock Timing       7         Reset Timing Characteristics       7                                                                                       | 0<br>0<br>1<br>1<br>2             |

| ELE<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.        | CTRICAL CHARACTERISTICS       7         Absolute Maximum Ratings       7         DC Characteristics       7         Clock Timing       7         Reset Timing Characteristics       7         ADC Electrical Characteristics       7                                        | <b>0</b><br>0<br>1<br>1<br>2<br>2 |

| ELE<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>PAC | CTRICAL CHARACTERISTICS       7         Absolute Maximum Ratings       7         DC Characteristics       7         Clock Timing       7         Reset Timing Characteristics       7         ADC Electrical Characteristics       7         Characteristics Graphs       7 | 0<br>0<br>1<br>1<br>2<br>5        |

## TM52<sub>Series</sub> F52xx FAMILY

## **Common Features**

| CPU               | MTP/Flash<br>Program<br>Memory  | RAM<br>Bytes    | Dual<br>Clock            | Operation<br>Mode            | Timer0<br>Timer1<br>Timer2 | UART   | Real-time<br>Timer3 | LVD  | LVR                  |

|-------------------|---------------------------------|-----------------|--------------------------|------------------------------|----------------------------|--------|---------------------|------|----------------------|

| Fast 8051<br>(2T) | 4K~16K<br>With IAP,<br>ISP, ICP | 256<br>~<br>768 | SXT<br>SRC<br>FXT<br>FRC | Fast<br>Slow<br>Idle<br>Stop | 8051 St                    | andard | 15-bit              | 2.3V | 1.8V<br>2.3V<br>2.9V |

*Note:* IAP, ISP only for Flash type program memory

## **Family Members Features**

| P/N         | Program<br>Memory | RAM<br>Bytes | IO Pin | PWM             | SAR<br>ADC      | Touch<br>Key | LCD  | LED  | SPI | Others |

|-------------|-------------------|--------------|--------|-----------------|-----------------|--------------|------|------|-----|--------|

| TM52-M5254  | MTP               | 256          | 18     | (8+2)-bit       | 12-bit          | _            |      |      |     |        |

| TM52-M5258  | 4K Bytes          | 230          | 10     | x2              | 12-ch           | 14-ch        |      |      | _   | _      |

| TM52-M5250  | Flash<br>4K Bytes | 256          | 18     | (8+2)-bit<br>x2 | 12-bit<br>12-ch | _            | _    | _    | _   | _      |

| TM52-F5264C | Flash             | 256          | 22     | (8+2)-bit       | 12-bit          | _            |      |      | Yes |        |

| TM52-F5268C | 8K Bytes          | 230          |        | x2              | 12-ch           | 14-ch        | _    |      | 105 | _      |

| TM52-F5274C | Flash             | 510          | 20     | (8+2)-bit       | 12-bit          | _            | 4 10 | 4 10 | \$7 |        |

| TM52-F5278C | 8K Bytes          | 512          | 30     | x2              | 12-ch           | 14-ch        | 4x18 | 4x18 | Yes | _      |

| TM52-F5273B | Flash             | 768          | 30     | (8+2)-bit       | 12-bit          | _            | 420  | 0-16 | Vaa |        |

| TM52-F5276B | 16K Bytes         | /08          | 30     | x2              | 12-ch           | 16-ch        | 4x20 | 8x16 | Yes | _      |

| TM52-F5288C | Flash             | 510          | 42     | (8+2)-bit       | 12-bit          | _            | 920  | 020  | Yes |        |

| TM52-F5284C | 16K Bytes         | 512          | 42     | x2              | 12-ch           | 12-ch        | 8x20 | 8x20 | res | _      |

| P/N                  | Operation |             | peration Cur<br>V=1, PWRS |             | Max. System Clock (Hz) |             |             |        |         |

|----------------------|-----------|-------------|---------------------------|-------------|------------------------|-------------|-------------|--------|---------|

| <b>F</b> /1 <b>N</b> | Voltage   | Fast<br>FRC | Slow<br>SRC               | Idle<br>SRC | Stop                   | SXT         | SRC         | FXT    | FRC     |

| TM52-M5254           | 1.9~5.5V  | 2.0mA       | 21 4                      | 5 2 1       | <0.1.u.A               | 32K         | 80K         | 6M     | 7.37M   |

| TM52-M5258           | 1.9~J.J V | 2.0IIIA     | 21µA                      | 5.2µA       | <0.1µA                 | 32 <b>K</b> | OUK         | UIVI   | 1.3/111 |

| TM52-F5250           | 2.0~5.5V  | 3mA         | 1mA                       | 6µA         | 3μΑ                    | 32K         | 24K         | 14.74M | 9.83M   |

| TM52-F5264C          | 2.0~5.5V  | 2.5mA       | 12µA                      | 611 Å       | 3µA                    | 32K         | 24K         | 8M     | 7.37M   |

| TM52-F5268C          | 2.0~J.J v | 2.JIIIA     | 12µA                      | 6µA         | <i>σμΑ</i>             | JZK         | 24 <b>N</b> | 0111   | 7.37111 |

| TM52-F5274C          | 2.0~5.5V  | 2.5mA       | 10 4                      | 6.1. 1      | 2 1                    | 32K         | 24K         | 8M     | 7.37M   |

| TM52-F5278C          | 2.0~3.3 V | 2.JIIIA     | 12µA                      | 6µA         | 3μΑ                    | JZK         | 24 <b>N</b> | 0171   | 1.3/111 |

| TM52-F5273B          | 105517    | 0 5 mm A    | 10 4                      | 6 A         | 2 4                    | 2017        | 2412        | 101/   | 0.021/  |

| TM52-F5276B          | 1.8~5.5V  | 2.5mA       | 12µA                      | 6µA         | 3μΑ                    | 32K         | 24K         | 10M    | 9.83M   |

| TM52-F5288C          | 1055      | 2.2mm A     | 22 4                      | 1 5 1       | < 0.1. A               | 2017        | 90V         | 8M     | 7 27 1  |

| TM52-F5284C          | 1.9~5.5V  | 2.3mA       | 22μΑ                      | 4.5µA       | $< 0.1 \mu A$          | 32K         | 80K         | OIVI   | 7.37M   |

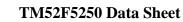

## **GENERAL DESCRPTION**

$TM52_{Series}$  F5250 are versions of a new, fast 8051 architecture for an 8-bit microcontroller single chip with an instruction set fully compatible with industry standard 8051, C language development platform, and retains most 8051 peripheral function block. Typically, the TM52 executes instructions six times faster than the traditional 8051 architecture.

The **TM52-F5250** provides improved performance, lower cost and fast time-to-market by integrating features on the chip, including 4K Bytes Flash program memory, 256 Bytes SRAM, Low Voltage Reset (LVR), Low Voltage Detector (LVD), dual clock power saving operation mode, 8051 standard UART and Timer0/1/2, real time Timer3, 2 set (8+2)-bit PWMs, 12 channels 12-bit A/D Convertor and Watchdog Timer. Its high reliability and low power consumption feature can be widely applied in consumer and home appliance products.

## **BLOCK DIAGRAM**

## **FEATURES**

## 1. Standard 8051 Instruction set, fast machine cycle

• Executes instructions six times faster than the traditional 8051

## 2. 4K Bytes Flash Program Memory

- Support "In Circuit Programming" (ICP) or "In System Programming" (ISP) for the Flash code

- Byte Write "In Application Programming" (IAP) mode is convenient as Data EEPROM access

- Code Protection Capability

## 3. Total 256 Bytes SRAM

• 256 Bytes IRAM in the 8051 internal data memory area

## 4. Four System Clock type Selections

- Fast clock from 1~14.746 MHz Crystal

- Fast clock from Internal RC (9.83 MHz)

- Slow clock from 32768 Hz Crystal

- Slow clock from Internal RC (24 KHz)

- System clock can be divided by 1/2/4/16 option

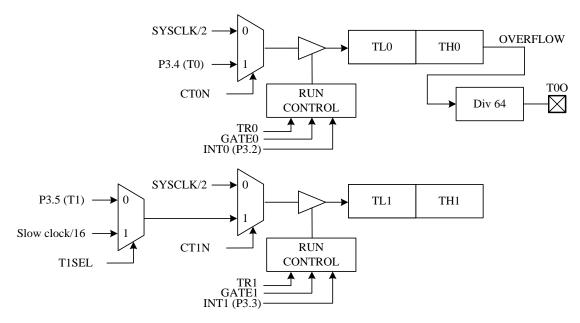

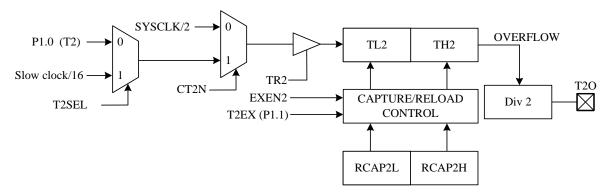

## 5. 8051 Standard Timer – Timer0/1/2

- 16-bit Timer0, also supports T0O clock output for Buzzer application

- 16-bit Timer1, also supports Slow clock/16 input counting

- 16-bit Timer2, also supports Slow clock/16 input counting and T2O clock output

## 6. 15-bit Time3

- Clock source is Slow clock

- Interrupt period can be clock divided by 32768/16384/8192/128 option

## 7. 8051 Standard UART

• One Wire UART option can be used for ISP or other application

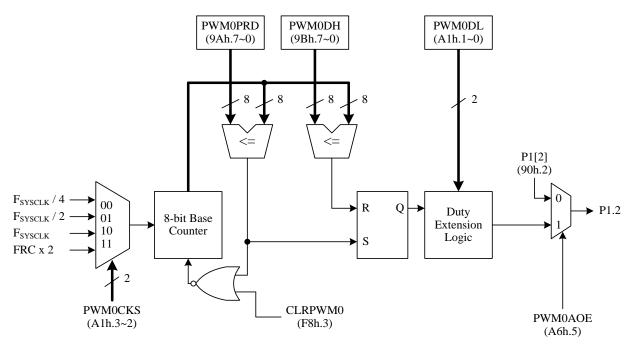

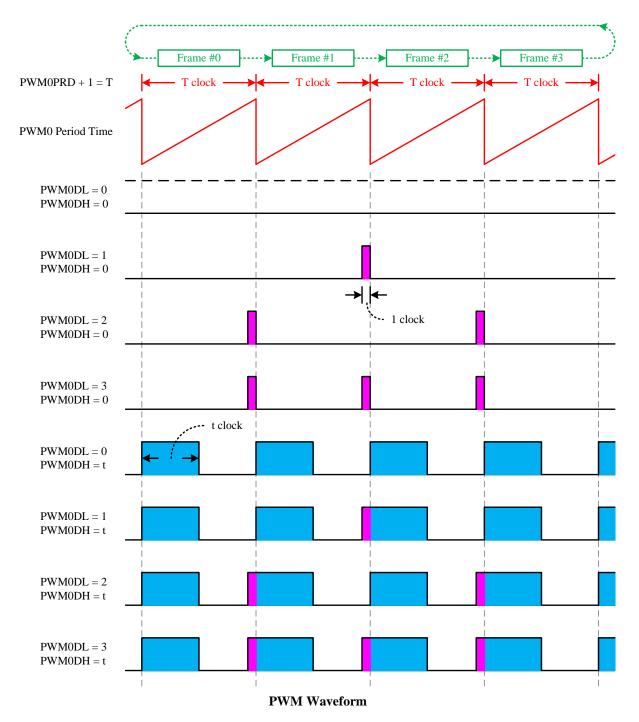

## 8. Two independent "8+2" bits PWMs with prescaler/period-adjustment

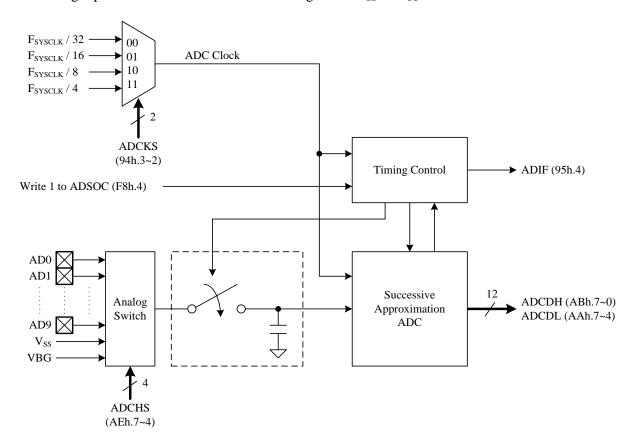

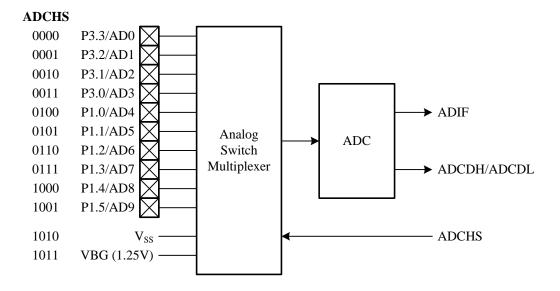

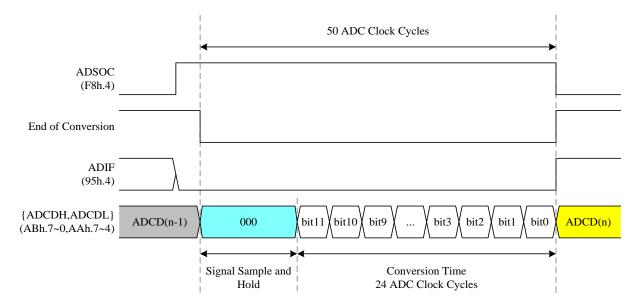

## 9. 12-bit ADC with 10 Channels External Pin Input and 2 Channels Internal Reference Voltage

## 10. 10 Sources, 4-level Priority Interrupt

- Timer0/Timer1/Timer2/Timer3 Interrupt

- INT0/INT1 Falling-Edge/Low-Level Interrupt

- Port1 Pin Change Interrupt

- UART TX/RX Interrupt

- P3.7 (INT2) Interrupt

- ADC Interrupt

## 11. Pin Interrupt can Wake up CPU from Power-Down (Stop) mode

- P3.2/P3.3 (INT0/INT1) Interrupt & Wake-up

- P3.7 (INT2) Interrupt & Wake-up

- Each Port1 pin can be defined as Interrupt & Wake-up pin (by pin change)

## 12. Max. 18 Programmable I/O pins

- CMOS Output

- Pseudo-Open-Drain, or Open-Drain Output

- Schmitt Trigger Input

- Pin Pull-up can be Enable or Disable

## 13. Independent RC Oscillating Watchdog Timer

• 360ms/180ms/90ms/45ms Selectable WDT Timeout options

## **14. Five types Reset**

- Power on Reset

- Selectable External Pin Reset

- Software Command Reset

- Selectable Watchdog Timer Reset

- Selectable Low Voltage Reset

## 15. 4-level Low Voltage Reset

• 2.0V/2.3V/2.9V/3.5V

## **16. 1-level Low Voltage Detect**

• 2.3V (can be disabled)

## **17. Four Operation Modes**

• Fast/Slow/Idle/Stop Mode

## 18. Operating Voltage and Current

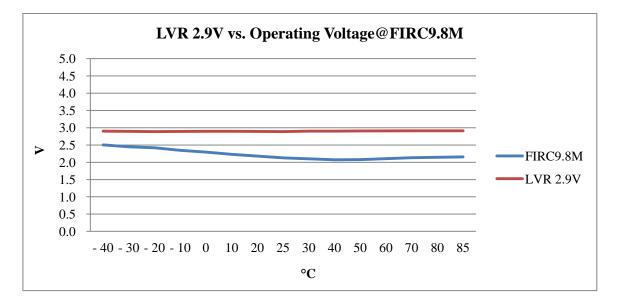

- $V_{CC}=3.5V \sim 5.5V @ F_{SYSCLK}=14.746 MHz$

- $V_{CC}=2.9V \sim 5.5V @ F_{SYSCLK}=9.8 MHz$

- $V_{CC}=2.3V \sim 5.5V @F_{SYSCLK}=5 MHz$

- $V_{CC}=2.0V \sim 5.5V @F_{SYSCLK}=2.5 MHz$

- I<sub>CC</sub>=4mA @Fast mode, F<sub>SYSCLK</sub>=9.8 MHz, V<sub>CC</sub>=5V

- I<sub>CC</sub>=1mA @Slow mode, F<sub>SYSCLK</sub>=32 KHz, V<sub>CC</sub>=3V

- $I_{CC}=6\mu A$  @Idle mode,  $F_{SYSCLK}=32$  KHz,  $V_{CC}=3V$

- $I_{CC}=3\mu A$  @Stop mode,  $V_{CC}=3V$

## **19. Operating Temperature Range**

• -40°C ~ +85°C

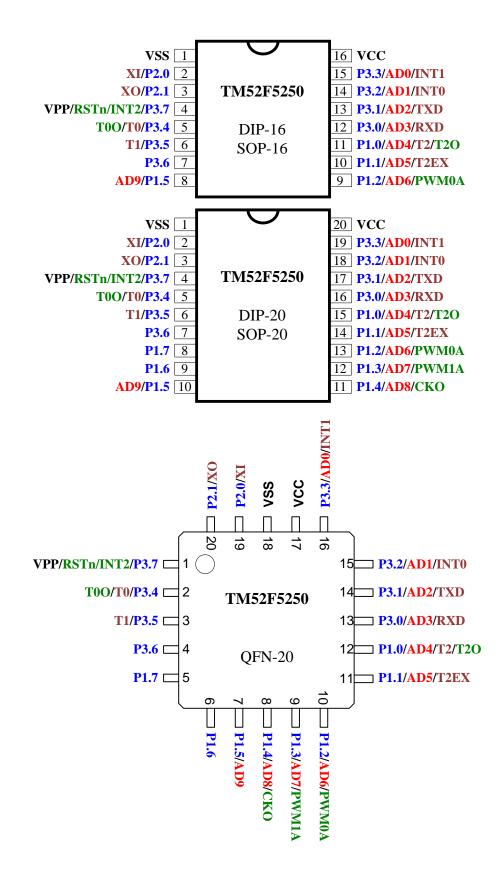

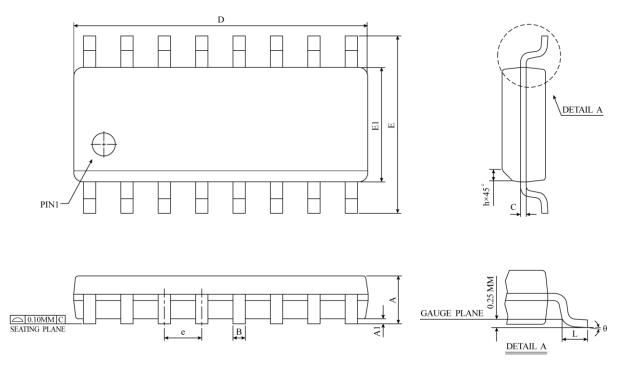

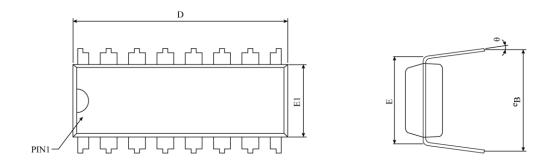

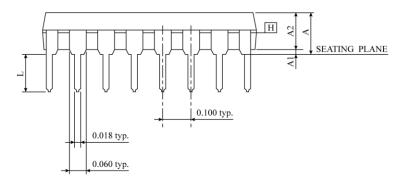

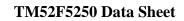

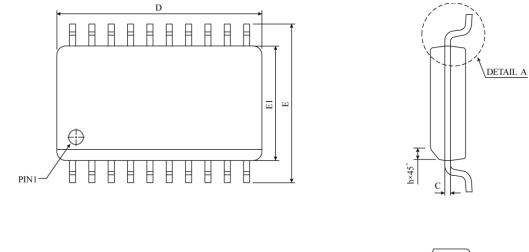

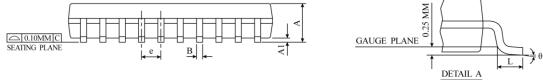

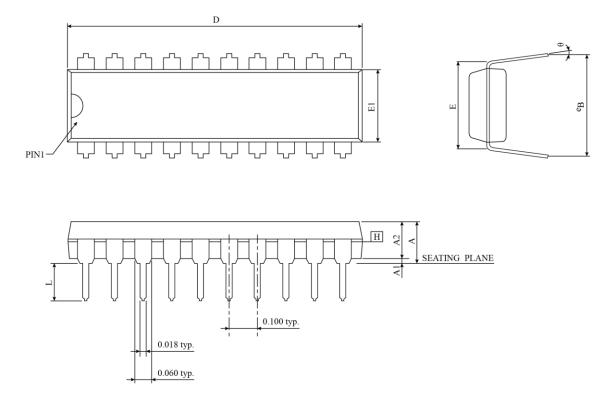

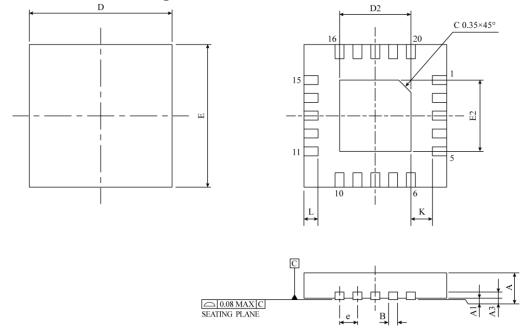

## 20. Package Types

- DIP 16-pin (300 mil)

- SOP 16-pin (150 mil)

- DIP 20-pin (300 mil)

- SOP 20-pin (300 mil)

- QFN-20 (4\*4\*0.75-0.5mm)

## PIN ASSIGNMENT

## PIN DESCRIPTION

| Name         | In/Out | Pin Description                                                                                                                                                                                                |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1.0~P1.7    | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "open-drain" output. Pull-up resistors are assignable by software. These pin's level change can wake up CPU from Idle/Stop mode. |

| P2.0~P2.1    | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "open-drain" output. Pull-up resistors are assignable by software.                                                               |

| P3.0~P3.2    | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "pseudo open drain" output. Pull-up resistors are assignable by software.                                                        |

| P3.3~P3.6    | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "open-drain" output. Pull-up resistors are assignable by software.                                                               |

| P3.7         | I/O    | Bit-programmable I/O port for Schmitt-trigger input or "open-drain" output. Pull-up resistor is fix enable.                                                                                                    |

| INT0, INT1   | Ι      | External low level or falling edge Interrupt input, Idle/Stop mode wake up input.                                                                                                                              |

| INT2         | Ι      | External falling edge Interrupt input, Idle/Stop mode wake up input.                                                                                                                                           |

| RXD          | I/O    | UART Mode0 transmit & receive data, Mode1/2/3 receive data                                                                                                                                                     |

| TXD          | I/O    | UART Mode0 transmit clock, Mode1/2/3 transmit data. In One Wire UART mode, this pin transmits and receives serial data.                                                                                        |

| T0, T1, T2   | Ι      | Timer0, Timer1, Timer2 event count pin input                                                                                                                                                                   |

| TOO          | 0      | Timer0 overflow divided by 64 output                                                                                                                                                                           |

| T2O          | 0      | Timer2 overflow divided by 2 output                                                                                                                                                                            |

| СКО          | 0      | System Clock divided by 2 output                                                                                                                                                                               |

| T2EX         | Ι      | Timer2 external trigger input                                                                                                                                                                                  |

| PWM0<br>PWM1 | 0      | 8+2 bit PWM output                                                                                                                                                                                             |

| AD0~AD9      | Ι      | ADC input                                                                                                                                                                                                      |

| RSTn         | Ι      | External active low reset input, Pull-up resistor is fixed enable                                                                                                                                              |

| XI, XO       | _      | Crystal/Resonator oscillator connection for system clock                                                                                                                                                       |

| VPP          | Ι      | Flash programming high voltage input                                                                                                                                                                           |

| VCC, VSS     | Р      | Power input pin and ground                                                                                                                                                                                     |

## PIN SUMMARY

## TM52F5250

| Pin        | Num        | ber    |                    |      |                 | Input   |                | (    | Dutpu  | t    | Alte | rnate | Func | ction | Misc    |

|------------|------------|--------|--------------------|------|-----------------|---------|----------------|------|--------|------|------|-------|------|-------|---------|

| SOP/DIP-20 | DIP/SOP-16 | QFN-20 | Pin Name           | Type | Pull-up Control | Wake up | Ext. Interrupt | P.P. | P.O.D. | 0.D. | ADC  | UART  | PWM  | Timer |         |

| 1          | 1          | 18     | VSS                | Р    |                 |         |                |      |        |      |      |       |      |       |         |

| 2          | 2          | 19     | XI/P2.0            | I/O  | 0               |         |                | •    |        | •    |      |       |      |       | Crystal |

| 3          | 3          | 20     | XO/P2.1            | I/O  | 0               |         |                | •    |        | •    |      |       |      |       | Crystal |

| 4          | 4          | 1      | VPP/RSTn/INT2/P3.7 | I/O  | $\odot$         | •       | •              |      |        | •    |      |       |      |       | Reset   |

| 5          | 5          | 2      | T0/T0O P3.4        | I/O  | 0               |         |                | ٠    |        | •    |      |       |      | •     |         |

| 6          | 6          | 3      | T1/P3.5            | I/O  | 0               |         |                | •    |        | •    |      |       |      | •     |         |

| 7          | 7          | 4      | РЗ.6               | I/O  | 0               |         |                | •    |        | •    |      |       |      |       |         |

| 8          | _          | 5      | P1.7               | I/O  | 0               | •       |                | •    |        | •    |      |       |      |       |         |

| 9          | _          | 6      | P1.6               | I/O  | 0               | •       |                | •    |        | •    |      |       |      |       |         |

| 10         | 8          | 7      | AD9/P1.5           | I/O  | 0               | •       |                | •    |        | •    | •    |       |      |       |         |

| 11         | _          | 8      | CKO/AD8/P1.4       | I/O  | 0               | •       |                | •    |        | •    | •    |       |      |       |         |

| 12         | _          | 9      | PWM1/AD7/P1.3      | I/O  | 0               | •       |                | •    |        | •    | •    |       | •    |       |         |

| 13         | 9          | 10     | PWM0/AD6/P1.2      | I/O  | 0               | •       |                | •    |        | •    |      |       | •    |       |         |

| 14         | 10         | 11     | T2EX/AD5/P1.1      | I/O  | 0               | •       |                | •    |        | •    | •    |       |      | •     |         |

| 15         | 11         | 12     | T2/T2O/AD4/P1.0    | I/O  | 0               | •       |                | •    |        | •    | •    |       |      | •     |         |

| 16         | 12         | 13     | RXD/AD3/P3.0       | I/O  | 0               |         |                | •    | •      |      | •    | •     |      |       |         |

| 17         | 13         | 14     | TXD/AD2/P3.1       | I/O  | 0               |         |                | •    | •      |      | •    | •     |      |       |         |

| 18         | 14         | 15     | INT0/AD1/P3.2      | I/O  | 0               | •       | •              | •    | •      |      | •    |       |      |       |         |

| 19         | 15         | 16     | INT1/AD0/P3.3      | I/O  | 0               | •       | •              | •    |        | •    | •    |       |      |       |         |

| 20         | 16         | 17     | VCC                | Р    |                 |         |                |      |        |      |      |       |      |       |         |

Symbol:

P.P. = Push-Pull Output

O.D. = Open Drain

P.O.D. = Pseudo Open Drain

## PS:

1.  $\odot$  3.7 Pull up resistor is fix enable

2. O Port1, P2.0, P2.1, Port3 these pins control Pull up resistor by operation modes

## FUNCTIONAL DESCRIPTION

## 1. CPU Core

In the 8051 architecture, the C programming language is used as a development platform. The TM52 device features a fast 8051 core in a highly integrated microcontroller, allowing designers to be able to achieve improved performance compared to a classic 8051 device. TM52 series microcontrollers provide a complete binary code with standard 8051 instruction set compatibility, ensuring an easy migration path to accelerate the development speed of system products. The CPU core includes an ALU, a program status word (PSW), an accumulator (ACC), a B register, a stack point (SP), DPTRs, a programming counter, an instruction decoder, and core special function registers (SFRs).

## **1.1 Accumulator (ACC)**

This register provides one of the operands for most ALU operations. Accumulators are generally referred to as A or Acc and sometimes referred to as Register A. In this document, the accumulator is represented as "A" or "ACC," including the instruction table. The accumulator, as its name suggests, is used as a general register to accumulate the intermediate results of a large number of instructions. The accumulator is the most important and frequently used register to complete arithmetic and logical operations. It holds the intermediate results of most arithmetic and logic operations and assists in data transportation.

| SFR E0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC     | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

E0h.7~0 ACC: Accumulator

## **1.2 B Register (B)**

The "B" register is very similar to the ACC and may hold a 1 Byte value. This register provides the second operand for multiply or divide instructions. Otherwise, it may be used as a scratch pad register. The B register is only used by two 8051 instructions, MUL and DIV. When A is to be multiplied or divided by another number, the other number is stored in B. For MUL and DIV instructions, it is necessary that the two operands are in A and B.

## ex: DIV AB

When this instruction is executed, data inside A and B are divided, and the answer is stored in A.

| SFR F0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| В       | B.7   | B.6   | B.5   | B.4   | B.3   | B.2   | B.1   | B.0   |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

F0h.7~0 **B:** B register

#### **1.3 Stack Pointer (SP)**

The SP register contains the Stack Pointer. The Stack Pointer is used to load the program counter into memory during LCALL and ACALL instructions and is used to retrieve the program counter from memory in RET and RETI instructions. The stack may also be saved or loaded using PUSH and POP instructions, which also increment and decrement the Stack Pointer. The Stack Pointer points to the top location of the stack.

| SFR 81h | Bit 7 | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|---------|-------|-----------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| SP      |       | SP              |       |       |       |       |       |       |  |  |  |  |

| R/W     |       | R/W             |       |       |       |       |       |       |  |  |  |  |

| Reset   | 0     | 0 0 0 0 0 1 1 1 |       |       |       |       |       |       |  |  |  |  |

| 011 7 0 |       |                 |       |       |       |       |       |       |  |  |  |  |

81h.7~0 **SP:** Stack Point

#### 1.4 Dual Data Pointer (DPTRs)

TM52 device has two DPTRs, which share the same SFR address. Each DPTR is 16 bits in size and consists of two registers: the DPTR high byte (DPH) and the DPTR low byte (DPL). The DPTR is used for 16-bit-address external memory accesses, for offset code byte fetches, and for offset program jumps. Setting the DPSEL control bit allows the program code to switch between the two physical DPTRs.

| SFR 82h | Bit 7        | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|---------|--------------|-----------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| DPL     |              | DPL             |       |       |       |       |       |       |  |  |  |  |

| R/W     |              | R/W             |       |       |       |       |       |       |  |  |  |  |

| Reset   | 0            | 0 0 0 0 0 0 0 0 |       |       |       |       |       |       |  |  |  |  |

| 00h 7 0 | DDI . Data I | oint low but    |       |       |       |       |       |       |  |  |  |  |

82h.7~0 **DPL:** Data Point low byte

| SFR 83h | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |  |

|---------|---------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

| DPH     |         | DPH   |       |       |       |       |       |       |  |  |  |  |  |

| R/W     |         | R/W   |       |       |       |       |       |       |  |  |  |  |  |

| Reset   | 0       | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |

| 021 7 0 | DDU D I |       |       |       |       |       |       |       |  |  |  |  |  |

83h.7~0 **DPH:** Data Point high byte

| SFR F8h | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3          | Bit 2 | Bit 1 | Bit 0 |

|---------|--------|--------|-------|-------|----------------|-------|-------|-------|

| AUX1    | CLRWDT | CLRTM3 | _     | ADSOC | <b>CLRPWM0</b> | T2SEL | T1SEL | DPSEL |

| R/W     | R/W    | R/W    |       | R/W   | R/W            | R/W   | R/W   | R/W   |

| Reset   | 0      | 0      |       | 0     | 0              | 0     | 0     | 0     |

F8h.0 **DPSEL:** Active DPTR Select

## **1.5 Program Status Word (PSW)**

This register contains status information resulting from CPU and ALU operations. The PSW affected by instructions is listed below.

| Instruction |   | Flag |    |

|-------------|---|------|----|

| instruction | С | OV   | AC |

| ADD         | Х | Х    | Х  |

| ADDC        | Х | Х    | Х  |

| SUBB        | Х | Х    | Х  |

| MUL         | 0 | Х    |    |

| DIV         | 0 | Х    |    |

| DA          | Х |      |    |

| RRC         | Х |      |    |

| RLC         | Х |      |    |

| SETB C      | 1 |      |    |

| Instruction |   | Flag |    |

|-------------|---|------|----|

| Instruction | С | OV   | AC |

| CLR C       | 0 |      |    |

| CPL C       | Х |      |    |

| ANL C, bit  | Х |      |    |

| ANL C, /bit | Х |      |    |

| ORL C, bit  | Х |      |    |

| ORL C, /bit | Х |      |    |

| MOV C, bit  | Х |      |    |

| CJNE        | Х |      |    |

|             |   |      |    |

A "0" means the flag is always cleared, a "1" means the flag is always set and an "X" means that the state of the flag depends on the result of the operation.

| SFR D0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| PSW     | CY    | AC    | F0    | RS1   | RS0   | OV    | F1    | Р     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

D0h.7 **CY:** ALU carry flag

D0h.6 AC: ALU auxiliary carry flag

D0h.5 **F0:** General purpose user-definable flag

- D0h.4~3 **RS1, RS0:** The contents of (RS1, RS0) enable the working register banks as:

- 00: Bank 0 (00h~07h)

- 01: Bank 1 (08h~0Fh)

- 10: Bank 2 (10h~17h)

- 11: Bank 3 (18h~1Fh)

- D0h.2 **OV:** ALU overflow flag

- D0h.1 **F1:** General purpose user-definable flag

- D0h.0 **P:** Parity flag. Set/cleared by hardware each instruction cycle to indicate odd/even number of "one" bits in the accumulator.

|       |         |       | PS    | W     |                 |           |               |      |    |    |     |        |       |      |    |    |      |

|-------|---------|-------|-------|-------|-----------------|-----------|---------------|------|----|----|-----|--------|-------|------|----|----|------|

| Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2           | Bit 1     | Bit 0         |      |    |    |     |        |       |      |    |    |      |

| R/W   | R/W     | R/W   | R/W   | R/W   | R/W             | R/W       | R/W           |      |    |    |     |        |       |      |    |    |      |

| CY    | AC      | FO    | RS1   | RS0   | OV              | <b>F1</b> | Р             |      |    |    |     |        |       |      |    |    |      |

|       |         |       | -     |       | $\overline{\ }$ |           |               |      |    |    |     |        |       |      |    |    | _    |

|       |         |       |       |       |                 |           |               |      |    |    | Reş | gister | : Baı | ık 3 |    |    | 1F   |

|       | RS1 RS0 |       |       |       |                 | 18h       | R0            | R1   | R2 | R3 | R4  | R5     | R6    | R7   |    |    |      |

|       |         |       |       |       |                 | Ban       |               |      |    |    | Reg | gister | ·Baı  | nk 2 |    |    | 1.71 |

|       |         |       | 1     | 1     |                 | 3         | -             | 10h  | R0 | R1 | R2  | R3     | R4    | R5   | R6 | R7 | 171  |

|       |         |       | 1     | 0     | )               | 2         | $\rightarrow$ |      |    |    | Reg | gister | Baı   | nk 1 |    |    |      |

|       |         | _     | 0     | 1     |                 | 1         |               | 08h  | R0 | R1 | R2  | R3     | R4    | R5   | R6 | R7 | 0Fł  |

|       |         |       | 0     | 0     | )               | 0         | $ \bot $      |      |    |    | Reg | gister | Baı   | nk O |    |    |      |

|       |         |       |       |       |                 |           |               |      | R0 | R1 | R2  | R3     | R4    | R5   | R6 | R7 | 071  |

|       |         |       |       |       |                 |           |               | 00h  |    |    |     |        |       |      |    |    | 1    |

|       |         |       |       |       |                 |           |               | 0011 |    |    |     |        |       |      |    |    |      |

## 2. Memory

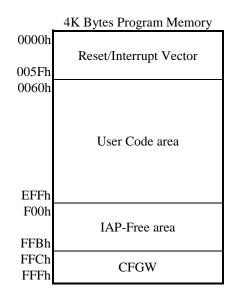

## 2.1 Program Memory

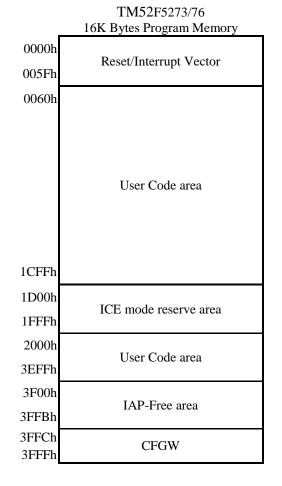

The **F5250** has a 4K Bytes Flash program memory, which can support in-circuit program (ICP), in-application program (IAP) and in-system program (ISP) function modes. The Flash write endurance is at least 50K cycles. The program memory address continuous space (0000h~FFFh) is partitioned to several sectors for device operation.

## 2.1.1 Program Memory Functional Partition

The last 4 bytes (FFCh~FFFh) of program memory is defined as chip Configuration Word (CFGW). Two of them are loaded into the device control registers upon power on reset (POR). The address space F00h~FFBh is the IAP free area, while the 0000h~005Fh is occupied by Reset/Interrupt vectors as standard 8051 definition.

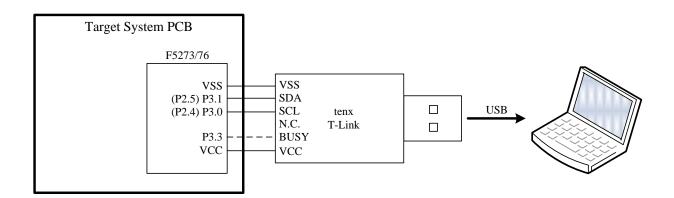

## 2.1.2 Flash ICP Mode

The Flash memory can be programmed by the tenx proprietary writer (**TWR98/TWR99**), which needs at least four wires (VCC, VSS, P3.0 and P3.1 pins) to connect to this chip. To shorten the programming time, it is recommended to connect Writer with an additional fifth wire, which is the VPP (P3.7) pin. If the user wants to program the Flash memory on the target circuit board (In Circuit Program, ICP), these pins must be reserved sufficient freedom to be connected to the Writer. More pins connected to Writer ensure more writing efficiency and speed.

| Writer wire number | Pin connection                                                                                                  |

|--------------------|-----------------------------------------------------------------------------------------------------------------|

| 4-Wire             | VCC, VSS, P3.0, P3.1                                                                                            |

| 5-Wire             | VCC, VSS, P3.0, P3.1, VPP                                                                                       |

| 7-Wire             | VCC, VSS, P3.0, P3.1, VPP, P3.3, P1.2<br><i>Note:</i> P3.2 output FRC/4 and P3.5 always output Low in this mode |

## 2.1.3 Flash IAP Mode

The **F5250** has "In Application Program" (IAP) capability, which allows software to read/write data from/to the Flash memory during CPU run time as conveniently as data EEPROM access. The IAP function is byte writable, meaning that the **F5250** does not need to erase one Flash page before write. The available IAP data space is 252 Bytes after chip reset, and can be re-defined by the "MVCLOCK" and "IAPALL" control register as shown below.

| _            | 4K Bytes Flash<br>Program memory | Flash memory | MVCLOCK | IAPALL | MOVC<br>Accessible | MOVX (IAP)<br>Accessible |

|--------------|----------------------------------|--------------|---------|--------|--------------------|--------------------------|

| 000h         |                                  |              | 1       | Х      | No                 | No                       |

|              | MOVC-Lock area                   | 000h~1FFh    | 0       | 0      | Yes                | No                       |

| 1FFh         |                                  |              | 0       | 1      | Yes                | Yes                      |

| 200h         | IAP-All area                     | 200h~EFFh    | Х       | 0      | Yes                | No                       |

| EFFh         | IAP-All alea                     | 20011~EFFII  | Х       | 1      | Yes                | Yes                      |

| F00h<br>FFBh | IAP-Free area                    | F00h~FFBh    | Х       | Х      | Yes                | Yes                      |

| FFCh         |                                  | EECh EECh    | Х       | 0      | Yes                | No                       |

|              | CFGW area                        | FFCh~FFEh    | Х       | 1      | Yes                | Yes                      |

| FFFh         |                                  | FFFh         | Х       | Х      | Yes                | No                       |

In IAP mode, the program Flash memory is separated into four sectors: MOVC-Lock area, IAP-All area, IAP-Free area, and CFGW area. These four sectors are regulated differently.

In the **MOVC-Lock area**, IAP read/write is limited by MVCLOCK bit, which can be set to control the accessibility of the MOVC and MOVX instructions to this area. The size of this area is 512 Bytes. The lock function is made to protect the main program code against unconsciously writing Flash memory in IAP mode. Locking or unlocking the function should be performed by the tenx TWR98/99 writing to the CFGW in Flash memory.

The **IAP-All area** is protected by the IAPALL register to prevent IAP mode from writing application data to the program area, resulting in a program code error that cannot be repaired. The size of this area is 3328 Bytes. Enabling IAPALL requires writing 65h to SFR SWCMD 97h to set the IAPALL control flag. Then, software can use MOVX instructions to write application data to flash memory from 0200h to EFFh. If user wants to disable IAPALL function, user can write other values to SFR SWCMD 97h to clear the IAPALL control flag. User must be careful not to overwrite program code which is already resided on the same Flash memory area.

The **IAP-Free area** has no control bit to protect. It can be used to reliably store system application data that needs to be programmed once or periodically during system operation. Other areas of Flash memory can be used to store data, but this area is usually the best. The size of this area is 252 Bytes, equivalent to an EEPROM, and Flash memory can provide byte access to read and write commands. In the past, storage of configuration data required an additional EEPROM or the other storage device. However, this functionality can now be provided by on-chip Flash, reducing the chip count of embedded applications. An external EEPROM or SRAM may not be needed.

The **CFGW area** has 4 data bytes (CFGWH, CFGWL and CFGWRx), which is located at the last 4 addresses of Flash memory. The CFGWH is not accessible to IAP, while the CFGWL and CFGWR can be read or written by IAP in case the IAPALL flag is set. CFGWL is copied to the SFR F7h after power on reset, software then take over CFGWL's control capability by modifying the SFR F7h.

TAD

## 2.1.4 IAP Mode Access Routines

**Flash IAP Write** is simply achieved by a "MOVX @DPTR, A" instruction while the DPTR contains the target Flash address (0000h~FFEh), and the ACC contains the data being written. The F5250 accepts IAP write command only when IAPWE=1. Flash IAP writing requires approximately 200~500 $\mu$ s. Meanwhile, the CPU stays in a waiting state, but all peripheral modules (Timers and others) continue running during the writing time. The software must handle the pending interrupts after an IAP write. Flash IAP writing needs higher V<sub>CC</sub> voltage, V<sub>CC</sub> > 2.8V.

Because the Program memory and the IAP data space share the same entity, a **Flash IAP Read** can be performed by the "MOVX A, @DPTR" or "MOVC" instruction as long as the target address points to the 0000h~FFEh area. A Flash IAP read does not require extra CPU wait time.

| ; IAP exa | ample code             |                                          |

|-----------|------------------------|------------------------------------------|

| ; need    | $2.8V < V_{DD} < 3.6V$ |                                          |

| MOV       | DPTR, #F00h            | ; DPTR=F00h=target IAP address           |

| MOV       | A, #5Ah                | ; A=5Ah=target IAP write data            |

| MOV       | C9h, #47h              | ; IAPWE=1                                |

| MOVX      | @DPTR, A               | ; Flash[F00h]=5Ah, after IAP write       |

|           |                        | ; 200µs~500µs H/W writing time, CPU wait |

| MOV       | C9h, #00h              | ; IAPWE=0 immediately after IAP write    |

| CLR       | А                      | ; A=0                                    |

| MOVX      | A, @DPTR               | ; A=5Ah                                  |

| CLR       | А                      | ; A=0                                    |

| MOVC      | A, @A+DPTR             | ; A=5Ah                                  |

|           |                        |                                          |

| Flash <b>FFFh</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1   | Bit 0 |

|-------------------|-------|-------|-------|-------|--------|--------|---------|-------|

| CFGWH             | PROT  | XRSTE | LV    | RE    | VCCFLT | PWRSAV | MVCLOCK | _     |

FFFh.1 MVCLOCK: If 1, the MOVC & MOVX instruction's accessibility to MOVC-Lock area is limited.

| SFR <b>97h</b> | Bit 7                                                                                           | Bit 6        | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1 |  |  |  |  |  |  |  |  |  |

|----------------|-------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| SWCMD          |                                                                                                 | IAPALL/SWRST |                                                                                           |  |  |  |  |  |  |  |  |  |

| R/W            |                                                                                                 | W            |                                                                                           |  |  |  |  |  |  |  |  |  |

| Reset          |                                                                                                 | _            |                                                                                           |  |  |  |  |  |  |  |  |  |

| 97h.7~0        | IAPALL (W): Write 65h to set IAPALL control flag; Write other value to clear IAPALL flag. It is |              |                                                                                           |  |  |  |  |  |  |  |  |  |

recommended to clear it immediately after IAP access.

97h.0 IAPALL (R): Flag indicates Flash memory sectors can be accessed by IAP or not. This bit combines with MVCLOCK to define the accessible IAP area.

| SFR C9h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| IAPWE   |       | IAPWE |       |       |       |       |       |       |  |  |  |  |

| R/W     | R/W   |       | W     |       |       |       |       |       |  |  |  |  |

| Reset   | 0     |       | _     |       |       |       |       |       |  |  |  |  |

C9h.7~0 **IAPWE (W):** Write 47h to set IAPWE control flag; Write other value to clear IAPWE flag. It is recommended to clear it immediately after IAP write.

C9h.7 IAPWE (R): Flag indicates Flash memory can be written by IAP or not, 1=IAP Write enable.

#### 2.1.5 Flash ISP Mode

The "In System Program" (ISP) usage is similar to IAP, except the purpose is to refresh the Program code. User can use UART or other method to get new Program code from external host, then writes code as the same way as IAP. ISP operation is complicated; basically it needs to assign a Boot code area to the Flash which does not change during the ISP process.

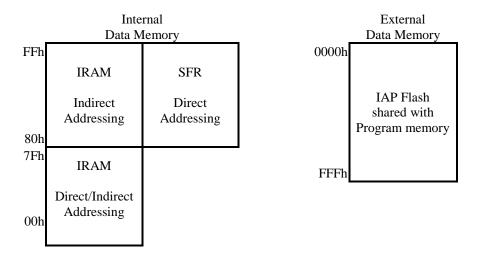

## 2.2 Data Memory

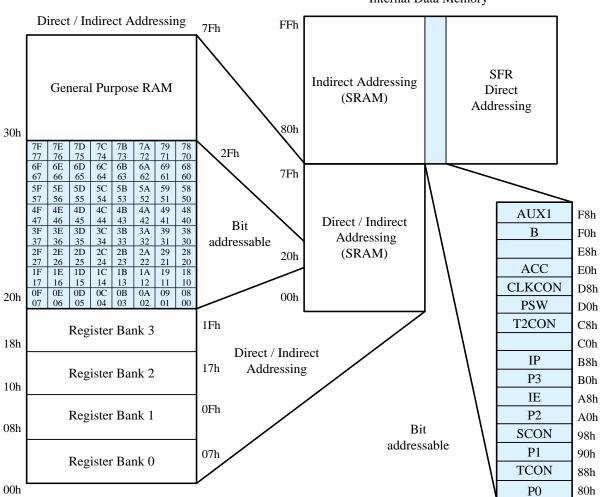

As the standard 8051, the **F5250** has both Internal and External Data Memory space. The Internal Data Memory space consists of 256 Bytes IRAM and 52 SFRs, which are accessible through a rich instruction set.

## 2.2.1 IRAM

IRAM is located in the 8051 internal data memory space. The whole 256 Bytes IRAM are accessible using indirect addressing but only the lower 128 Bytes are accessible using direct addressing. There are four directly addressable register banks (switching by PSW), which occupy IRAM space from 00h to 1Fh. The address 20h to 2Fh 16 Bytes IRAM space is bit-addressable. IRAM can be used as scratch pad registers or program stack.

## 2.2.2 SFRs

All peripheral functional modules such as I/O ports, Timers and UART operations for the chip are accessed via Special Function Registers (SFRs). These registers occupy upper 128 Bytes of direct Data Memory space locations in the range 80h to FFh. There are 14 bit addressable SFRs (which means that eight individual bits inside a single byte are addressable), such as ACC, B register, PSW, TCON, SCON, and others. The remaining SFRs are only byte addressable. SFRs provide control and data exchange with the resources and peripherals of the **F5250**. The TM52 series of microcontrollers provides complete binary code with standard 8051 instruction set compatibility. Beside the standard 8051 SFRs, the **F5250** implements additional SFRs used to configure and access subsystems such as the ADC, which are unique to the **F5250**.

|     | 8/0    | 9/1    | A/2     | B/3    | C/4     | D/5    | E/6    | F/7   |

|-----|--------|--------|---------|--------|---------|--------|--------|-------|

| F8h | AUX1   |        |         |        |         |        |        |       |

| F0h | В      |        |         |        |         |        |        | CFGWL |

| E8h |        |        |         |        |         |        |        |       |

| E0h | ACC    |        |         |        |         |        |        |       |

| D8h | CLKCON |        |         |        |         |        |        |       |

| D0h | PSW    |        |         |        |         |        |        |       |

| C8h | T2CON  | IAPWE  | RCP2L   | RCP2H  | TL2     | TH2    |        |       |

| C0h |        |        |         |        |         |        |        |       |

| B8h | IP     | IPH    | IP1     | IP1H   |         |        |        |       |

| B0h | P3     |        |         |        |         |        |        |       |

| A8h | IE     | INTE1  | ADTKDT  | ADCDH  |         |        | CHSEL  |       |

| A0h | P2     | PWMCON | P1MODL  | P1MODH | P3MODL  | P3MODH | PINMOD |       |

| 98h | SCON   | SBUF   | PWM0PRD | PWM0DH | PWM1PRD | PWM1DH |        |       |

| 90h | P1     |        |         | P2MOD  | OPTION  | INTFLG | P1WKUP | SWCMD |

| 88h | TCON   | TMOD   | TL0     | TL1    | TH0     | TH1    |        |       |

| 80h | P0     | SP     | DPL     | DPH    |         |        |        | PCON  |

## 3. Power

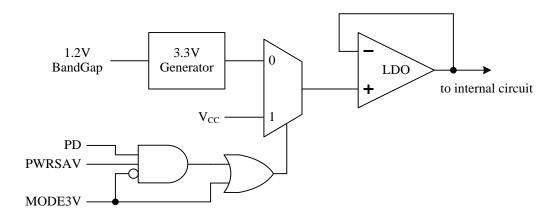

The **F5250** has a built-in internal low dropout regulator. When MODE3V=0, the voltage regulator outputs 3.3V power to the internal chip circuit. When MODE3V=1, the LDO is turned off, and the internal circuit receives a power supply directly from the VCC pin. Because the LDO consumes 150 $\mu$ A for operation, turning off LDO by setting MODE3V=1 can reduce the chip current consumption. However, setting MODE3V=1 is only valid for an operating condition of V<sub>CC</sub> <3.6V. The PWRSAV also control the LDO. When MODE3V=0 and PWRSAV=1, the LDO is turned off in Stop mode for saving power consumption. In addition, set PWRSAV will affect the LVR/LVD setting.

## MODE3V=0

| Operation    | CF     | GW   | Tiny    | LDO | LVD | LVD | E             |

|--------------|--------|------|---------|-----|-----|-----|---------------|

| Mode         | PWRSAV | LVRE | Current | LDO | LVR | LVD | Function      |

|              | Х      | 00   | -       | ON  | ON  | _   | LV Reset 2.9V |

| Fast<br>Slow | Х      | 01   | -       | ON  | ON  | -   | LV Reset 2.3V |

| Idle         | Х      | 10   | -       | ON  | ON  | -   | LV Reset 3.5V |

| idic         | Х      | 11   | -       | ON  | ON  | ON  | LV Reset 2.0V |

|              | 0      | 00   | _       | ON  | ON  | -   | LV Reset 2.9V |

|              | 0      | 01   | -       | ON  | ON  | -   | LV Reset 2.3V |

|              | 0      | 10   | _       | ON  | ON  | -   | LV Reset 3.5V |

| Stop         | 0      | 11   | -       | ON  | ON  | -   | LV Reset 2.0V |

| Stop         | 1      | 00   | Y       | OFF | ON  | -   | LV Reset 2.0V |

|              | 1      | 01   | Y       | OFF | ON  | -   | LV Reset 2.0V |

|              | 1      | 10   | Y       | OFF | ON  | -   | LV Reset 2.0V |

|              | 1      | 11   | Y       | OFF | ON  | -   | LV Reset 2.0V |

## MODE3V=1

| Operation    | CF     | GW   | Tiny    | I DO | LVD | IVD | Enn ett on    |

|--------------|--------|------|---------|------|-----|-----|---------------|

| Mode         | PWRSAV | LVRE | Current | LDO  | LVR | LVD | Function      |

|              | 0      | 00   | _       | OFF  | ON  | _   | LV Reset 2.9V |

|              | 0      | 01   | _       | OFF  | ON  | _   | LV Reset 2.3V |

| <b>F</b> (   | 0      | 10   | -       | OFF  | ON  | _   | LV Reset 3.5V |

| Fast<br>Slow | 0      | 11   | -       | OFF  | ON  | ON  | LV Reset 2.0V |

| Idle         | 1      | 00   | Idle    | OFF  | ON  | -   | LV Reset 2.0V |

| idic         | 1      | 01   | Idle    | OFF  | ON  | -   | LV Reset 2.0V |

|              | 1      | 10   | Idle    | OFF  | ON  | -   | LV Reset 2.0V |

|              | 1      | 11   | Idle    | OFF  | ON  | _   | LV Reset 2.0V |

|              | 0      | 00   | _       | OFF  | ON  | -   | LV Reset 2.9V |

|              | 0      | 01   | -       | OFF  | ON  | -   | LV Reset 2.3V |

|              | 0      | 10   | -       | OFF  | ON  | -   | LV Reset 3.5V |

| Stor         | 0      | 11   | Y       | OFF  | ON  | -   | LV Reset 2.0V |

| Stop         | 1      | 00   | Y       | OFF  | ON  | _   | LV Reset 2.0V |

|              | 1      | 01   | Y       | OFF  | ON  | -   | LV Reset 2.0V |

|              | 1      | 10   | Y       | OFF  | ON  | _   | LV Reset 2.0V |

|              | 1      | 11   | Y       | OFF  | ON  | _   | LV Reset 2.0V |

*Note:* Typical Tiny current of F5250 are Idle=5uA and Stop=3uA @VCC=3V, 32KHz *Note:* FW must turn off Bandgap to obtain Tiny Current (ADCHS  $\neq$  0b1011)

| Flash <b>FFFh</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1   | Bit 0 |

|-------------------|-------|-------|-------|-------|--------|--------|---------|-------|

| CFGWH             | PROT  | XRSTE | LV    | RE    | VCCFLT | PWRSAV | MVCLOCK | _     |

FFFh.3 VCCFLT: Set 1 to enhance the chip's power noise immunity FFFh.2

**PWRSAV:** Power save function control bit

0: Disable Power save function

1: Enable Power save function

| SFR <b>94h</b> | Bit 7                                              | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------------|----------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|--|--|

| OPTION         | UART1W                                             | MODE3V | WDT   | TPSC  | ADO   | CKS   | TM3   | SPSC  |  |  |

| R/W            | R/W                                                | R/W    | R/    | W     | R/W   |       | R/W   |       |  |  |

| Reset          | 0                                                  | 0      | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| 94h.6          | 94h.6 <b>MODE3V:</b> 3V mode selection control bit |        |       |       |       |       |       |       |  |  |

**MODE3V:** 3V mode selection control bit

If this bit is set, the chip can be only operated in the condition of  $V_{CC} < 3.6V$ , and LDO is turned off to save current

## 4. Reset

The **F5250** has five types of reset methods. Resets can be caused by Power on Reset (POR), External Pin Reset (XRST), Software Command Reset (SWRST), Watchdog Timer Reset (WDTR), or Low Voltage Reset (LVR). The CFGW controls the Reset functionality. The SFRs are returned to their default value after Reset.

## 4.1 Power on Reset

After Power on Reset, the device stays on Reset state for 40 ms as chip warm up time, then downloads the CFGW register from Flash's last two bytes (Other Reset will not reload the CFGW). The Power on Reset needs VCC pin's voltage first discharge to near VSS level, then rise beyond 2.1V.

## 4.2 External Pin Reset

External Pin Reset is active low. It needs to keep at least 2 SRC clock cycle long to be seen by the chip. External Pin Reset can be disabled or enabled by CFGW.

## 4.3 Software Command Reset

Software Reset is activated by writing the SFR 97h with data 56h.

## 4.4 Watchdog Timer Reset

WDT overflow Reset is disabled or enabled by SFR F7h. The WDT uses SRC as its counting time base. It runs in Fast/Slow mode and runs or stops in Idle/Stop mode. WDT overflow speed can be defined by WDTPSC SFR. WDT is cleared by device Reset or CLRWDT SFR bit.

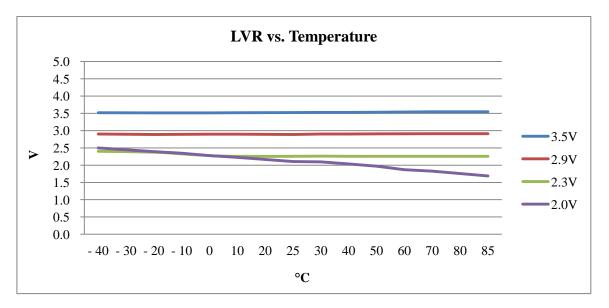

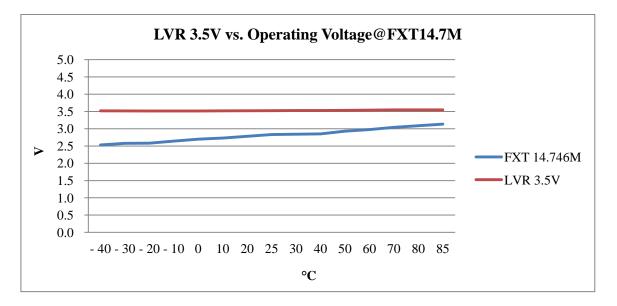

## 4.5 Low Voltage Reset

The **F5250** offers four options for LVR and Low Voltage Detection (LVD) functions. The user can make a selection by CFGW, let LVR voltages of 3.5V, 2.9V, 2.3V, and 2.0V be selected separately, and let LVD be 2.3V only. If the LVR is selected as 2.0V, the 2.3V LVD flag is available for LVD. If LVR is selected as 2.3V, 2.9V or 3.5V, the LVD flag cannot be used.

| System Clock frequency | 14.74MHz | 9.8MHz   | 5MHz     | 2.5MHz   |

|------------------------|----------|----------|----------|----------|

| Minimum LVR level      | LVR=3.5V | LVR=2.9V | LVR=2.3V | LVR=2.0V |

#### LVR setting table

*Note:* LVR must be enable, also refer to AP-TM52XXXX\_02S for LVR setting information

| Flash <b>FFFh</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1   | Bit 0 |

|-------------------|-------|-------|-------|-------|--------|--------|---------|-------|

| CFGWH             | PROT  | XRSTE | LV    | RE    | VCCFLT | PWRSAV | MVCLOCK | _     |

FFFh.6XRSTE: External Pin Reset control0: Disable External Pin Reset1: Enable External Pin ResetFFFh.5~4LVRE: Low Voltage Reset function select00: Set LVR at 2.9V01: Set LVR at 2.3V10: Set LVR at 3.5V11: Set LVR at 2.0V and LVD at 2.3V

| SFR F7h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| CFGWL   | WI    | WDTE  |       | FRCF  |       |       |       |       |  |  |

| R/W     | R/    | W     | —     | R/W   |       |       |       |       |  |  |

| Reset   | _     | _     | —     | _     | _     | —     | —     | _     |  |  |

F7h.7~6 **WDTE:** Watchdog Timer Reset control. It is automatically loaded with Flash's FFEh data at power on reset and can be read/written as any other SFR register in normal mode. So the WDT can be changed on CPU run time by S/W.

0x: Watchdog Timer Reset disable

10: Watchdog Timer Reset enable in Fast/Slow mode, disable in Idle/Stop mode

11: Watchdog Timer Reset always enable

#### Note: FW should not change FRCF while writing WDTE

| SFR 94h | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0  |  |

|---------|--------|--------|-------|--------|-------|-------|-------|--------|--|

| OPTION  | UART1W | MODE3V | WDT   | WDTPSC |       | ADCKS |       | TM3PSC |  |

| R/W     | R/W    | R/W    | R/    | W      | R/    | W     | R/    | W      |  |

| Reset   | 0      | 0      | 0     | 0      | 0     | 0     | 0     | 0      |  |

94h.5~4 WDTPSC: Watchdog Timer pre-scalar time select

00: 360ms WDT overflow rate

01: 180ms WDT overflow rate

10: 90ms WDT overflow rate

11: 45ms WDT overflow rate

| SFR <b>95h</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| INTFLG         | LVD   | —     | _     | ADIF  | —     | IE2   | P1IF  | TF3   |

| R/W            | R     | —     | _     | R/W   | —     | R/W   | R/W   | R/W   |

| Reset          | _     | —     | —     | 0     | —     | 0     | 0     | 0     |

95h.7 **LVD:** Low Voltage Detect flag

Set by H/W when a low voltage occurs. The flag is valid when LVR is 2.0V. This flag is disabled if MODE3V=1 and PWRSAV=1.

| SFR <b>97h</b> | Bit 7   | Bit 6        | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|----------------|---------|--------------|---------|-------|-------|-------|-------|-------|--|--|--|

| SWCMD          |         | IAPALL/SWRST |         |       |       |       |       |       |  |  |  |

| R/W            |         | W            |         |       |       |       |       |       |  |  |  |

| Reset          |         | _            |         |       |       |       |       |       |  |  |  |

| 0.51 5 0       | aupar w |              | C ALL I |       |       |       |       |       |  |  |  |

97h.7~0 **SWRST:** Write 56h to generate S/W Reset

| SFR F8h | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|---------|--------|--------|-------|-------|---------|-------|-------|-------|

| AUX1    | CLRWDT | CLRTM3 | —     | ADSOC | CLRPWM0 | T2SEL | T1SEL | DPSEL |

| R/W     | R/W    | R/W    | _     | R/W   | R/W     | R/W   | R/W   | R/W   |

| Reset   | 0      | 0      |       | 0     | 0       | 0     | 0     | 0     |

F8h.7 **CLRWDT:** Set to clear WDT, H/W auto clear it at next clock cycle

## 5. Clock Circuitry and Operation Mode

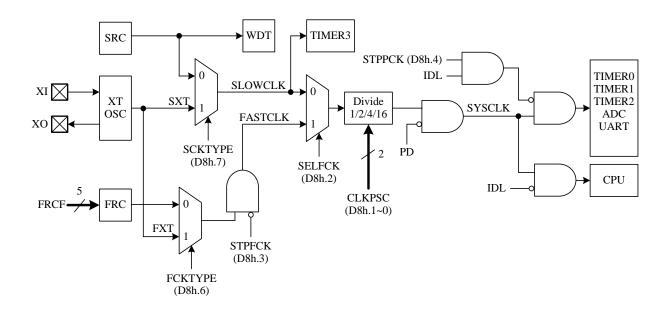

## 5.1 System Clock

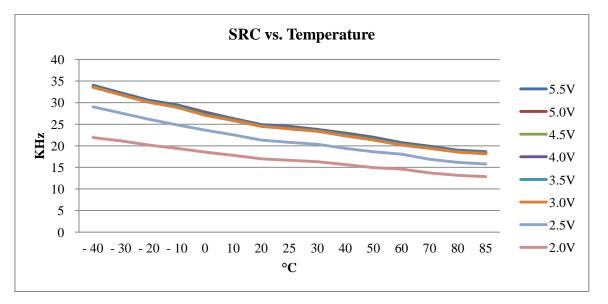

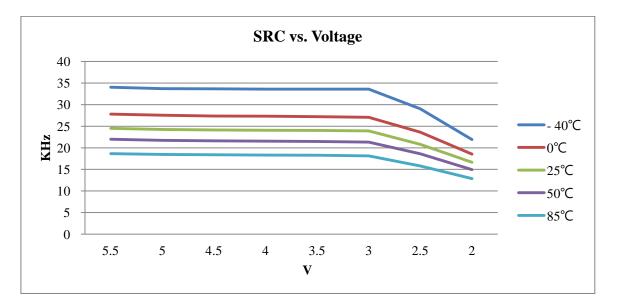

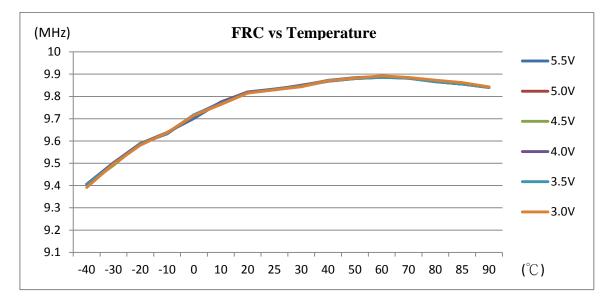

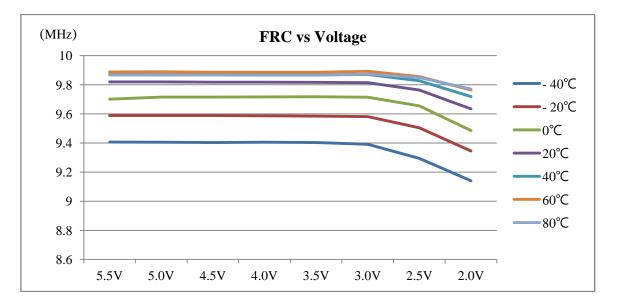

The **F5250** is designed with dual-clock system. During runtime, user can directly switch the System clock from fast to slow or from slow to fast. It also can directly select a clock divider of 1, 2, 4 or 16. The Fast clock can be selected as FXT (Fast Crystal, 1~14.746 MHz) or FRC (Fast Internal RC, 9.83 MHz). The Slow clock can be selected as SXT (Slow Crystal, 32 KHz) or SRC (Slow Internal RC, 24 KHz). Fast mode and Slow mode are defined as the CPU running at Fast and Slow clock speeds.

After Reset, the device is running at Slow mode with 24 KHz SRC. S/W should select the proper clock rate for chip operation safety. The higher  $V_{CC}$  allows the chip to run at a higher System clock frequency. In a typical condition, a 9.8 MHz System clock rate requires  $V_{CC} > 2.9V$ .

The **F5250** has an external oscillators connected to the XI/XO pins. It relies on external circuitry for the clock signal and frequency stabilization, such as a stand-alone oscillator, quartz crystal, or ceramic resonator. In Fast mode, the fast oscillator can be used in the range from 1~14.746 MHz. In Slow mode, the slow oscillator can only use a clock frequency of 32.768 KHz.

The **CLKCON** SFR controls the System clock operating. H/W automatically blocks the S/W abnormally setting for this register. S/W can only change the Slow clock type in Fast mode and change the Fast clock type in Slow mode. Never to write both STPFCK=1 & SELFCK=1. It is recommended to write this SFR bit by bit.

| Flash FFEh | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| CFGWL      | _     | _     | _     |       |       | FRCF  |       |       |

FFEh.4~0 **FRCF:** FRC frequency adjustment.

FRC is trimmed to 9.83 MHz in chip manufacturing. FRCF records the adjustment data.

| SFR F7h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

| CFGWL   | WDTE  |       | —     |       | FRCF  |       |       |       |  |  |

| R/W     | R/W   |       | —     | R/W   |       |       |       |       |  |  |

| Reset   |       | —     | —     | -     | -     | —     | —     | -     |  |  |

F7h.4~0 **FRCF:** FRC frequency adjustment. It is automatically loaded with Flash's FFEh data at power on reset and can be read/written as any other SFR register in normal mode. So the FRC clock speed can be changed on CPU run time by S/W.

00h=central frequency, 0Fh=highest frequency, 10h=lowest frequency.

| SFR D8h                                                                                               | Bit 7                                                                                  | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2        | Bit 1      | Bit 0 |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------|---------------|---------------|---------------|--------------|------------|-------|--|--|--|--|

| CLKCON                                                                                                | SCKTYPE                                                                                | FCKTYPE       |               | STPPCK        | STPFCK        | SELFCK       | CLK        | PSC   |  |  |  |  |

| R/W                                                                                                   | R/W                                                                                    | R/W           |               | R/W           | R/W           | R/W          | R/         | R/W   |  |  |  |  |

| Reset                                                                                                 | 0                                                                                      | 0             |               | 0             | 0             | 0            | 1          | 1     |  |  |  |  |

| D8h.7                                                                                                 | <b>SCKTYPE:</b> Slow clock type. This bit can be changed only in Fast mode (SELFCK=1). |               |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 0: SRC                                                                                 |               |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 1: SXT                                                                                 |               |               |               |               |              |            |       |  |  |  |  |

| D8h.6                                                                                                 | FCKTYPE: Fast clock type. This bit can be changed only in Slow mode (SELFCK=0).        |               |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 0: FRC                                                                                 | 0: FRC        |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 1: FXT                                                                                 |               |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | STPPCK: S                                                                              | -             |               |               |               |              | ode        |       |  |  |  |  |

| D8h.3                                                                                                 | STPFCK: S                                                                              | 1             |               | 1 .           | g in Slow/Idl | e mode.      |            |       |  |  |  |  |

|                                                                                                       |                                                                                        | be changed    |               |               |               |              |            |       |  |  |  |  |

| D8h.2                                                                                                 |                                                                                        | •             | source select | ion. This bit | can be chang  | ed only when | n STPFCK=0 |       |  |  |  |  |

|                                                                                                       | 0: Slow clo                                                                            |               |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 1: Fast cloc                                                                           |               |               |               |               |              |            |       |  |  |  |  |

| D8h.1~0                                                                                               | CLKPSC: S                                                                              | •             | -             |               | -             |              |            |       |  |  |  |  |

|                                                                                                       | •                                                                                      |               |               | divided by 16 | )             |              |            |       |  |  |  |  |

|                                                                                                       |                                                                                        | clock is Fast |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 10: System clock is Fast/Slow clock divided by 2                                       |               |               |               |               |              |            |       |  |  |  |  |

|                                                                                                       | 11: System clock is Fast/Slow clock divided by 1                                       |               |               |               |               |              |            |       |  |  |  |  |

| <i>Note:</i> also refer to AP-TM52XXXXX_01S and AP-TM52XXXXX_02S about System Clock Application Note. |                                                                                        |               |               |               |               |              |            |       |  |  |  |  |

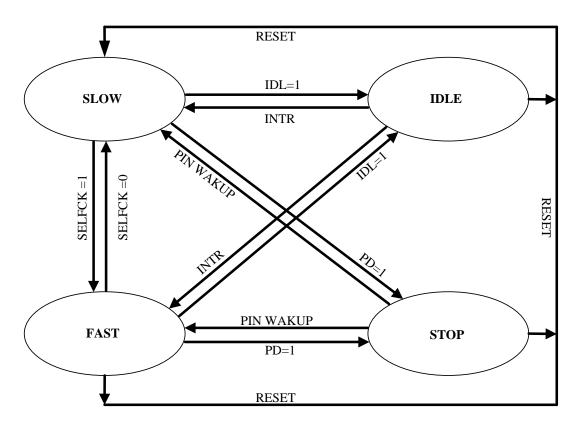

## 5.2 Operation Mode