Sample &

Buy

**TLC5954** SBVS241-APRIL 2014

# TLC5954 48-Channel, Constant-Current LED Driver with Global Brightness Control, LED Open-Short Detection, and Power-Save Mode

Technical

Documents

#### Features 1

- 48 Constant-Current Sink Output Channels with On or Off Control

- Current Capability:

- 34.9 mA for 32 Channels

- 24.4 mA 16 Channels

- No External Resistor for Current Setting

- Maximum Current Control (MC): 3 Bits (8 Steps)

- Global Brightness Control (BC) for Each Color Group: 7 Bits (128 Steps), Three Groups

- LED Power-Supply Voltage: Up to 10 V

- VCC = 3.0 V to 3.6 V

- **Constant-Current Accuracy:**

- Channel-to-Channel =  $\pm 1\%$  (typ),  $\pm 3\%$  (max)

- Device-to-Device =  $\pm 2\%$  (typ),  $\pm 4\%$  (max)

- Data Transfer Rate: 30 MHz

- BLANK Pulse Duration: 40 ns (min)

- LED Open Detection (LOD)

- LED Short Detection (LSD)

- Power-Save Mode (PSM): 7-µA Consumption, High-Speed Recovery

- Undervoltage Lockout Sets Default Data

- **Delayed Switching Minimizes Inrush Current**

- Operating Temperature: -40°C to +85°C

# 2 Applications

Tools &

Software

- LED Video Displays ٠

- Variable Message Signs (VMS)

- Illumination

#### Description 3

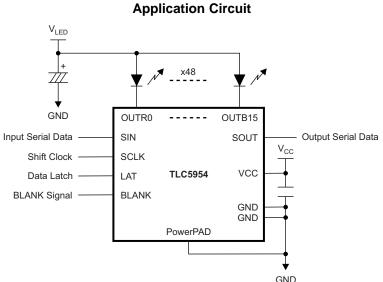

The TLC5954 is a 48-channel, constant-current sink LED driver. Each channel can be turned on or off by writing data to an internal register. The output channels (OUTXn) are grouped into three groups of 16 channels. Each channel group (R, G, and B) has a 128-step global brightness control (BC) function. The maximum current value of all 48 channels can be set with an 8-step maximum current control (MC) function. The device has two error flags: LED open detection (LOD) and LED short detection (LSD). The error flags can be read via a serial interface port. The device also has a power-save mode that sets the total current consumption to 7 µA (typ) when all outputs are off.

Support &

Community

....

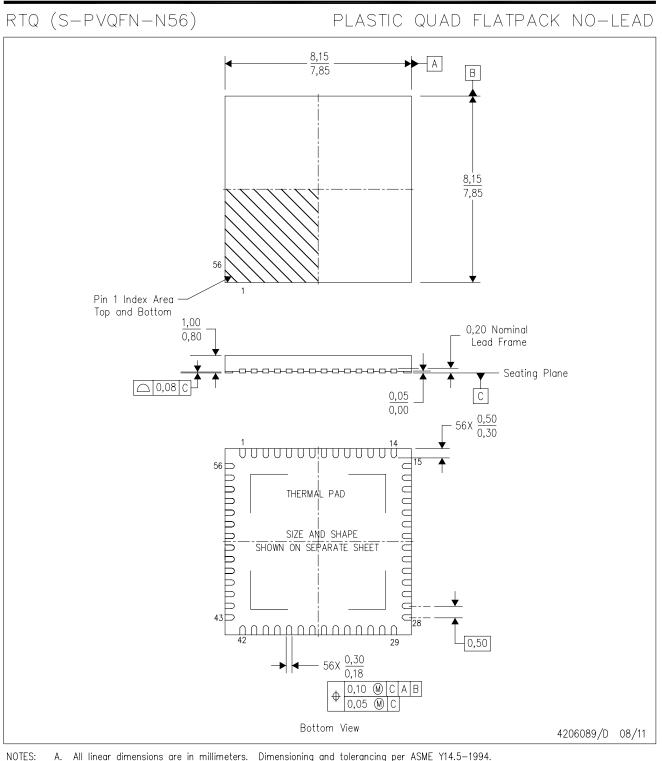

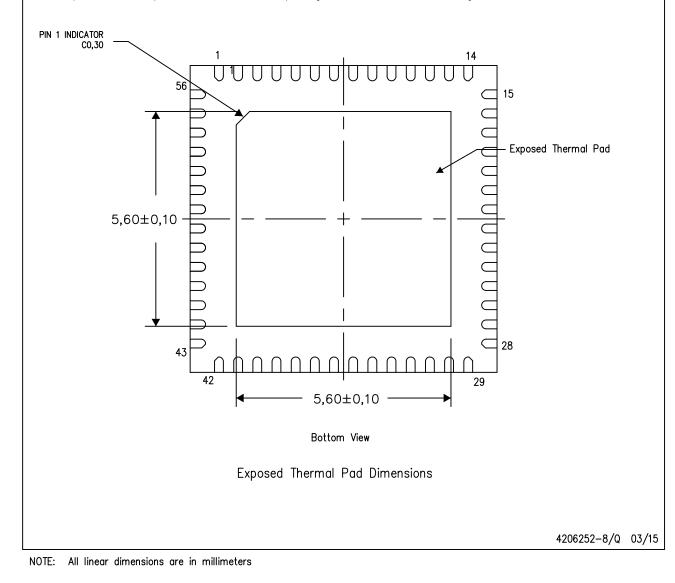

#### Device Information<sup>(1)</sup>

| DEVICE NAME | PACKAGE   | BODY SIZE   |  |

|-------------|-----------|-------------|--|

| TLC5954     | VQFN (56) | 8 mm × 8 mm |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 | Feat | tures 1                                               |

|---|------|-------------------------------------------------------|

| 2 | Арр  | lications1                                            |

| 3 | Des  | cription1                                             |

| 4 | Rev  | ision History 2                                       |

| 5 | Pin  | Configuration and Functions 3                         |

| 6 | Spe  | cifications 4                                         |

|   | 6.1  | Absolute Maximum Ratings 4                            |

|   | 6.2  | Handling Ratings 5                                    |

|   | 6.3  | Recommended Operating Conditions 5                    |

|   | 6.4  | Thermal Information 6                                 |

|   | 6.5  | Electrical Characteristics 6                          |

|   | 6.6  | Switching Characteristics 7                           |

|   | 6.7  | Typical Characteristics 8                             |

| 7 | Para | ameter Measurement Information 11                     |

|   | 7.1  | Pin Equivalent Input and Output Schematic<br>Diagrams |

|   | 7.2  | Test Circuits 11                                      |

|   | 7.3  | Timing Diagrams 12                                    |

| 8 | Deta | ailed Description 16                                  |

|    | 8.1  | Overview                          | 16              |

|----|------|-----------------------------------|-----------------|

|    | 8.2  | Functional Block Diagram          | 17              |

|    | 8.3  | Feature Description               | 18              |

|    | 8.4  | Device Functional Modes           | 23              |

|    | 8.5  | Register Maps                     | 27              |

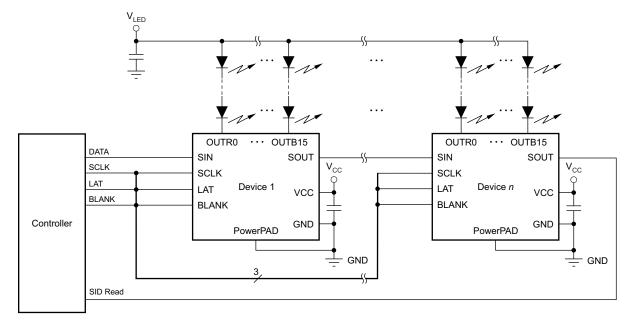

| 9  | Арр  | lications and Implementation      | 33              |

|    | 9.1  | Application Information           | 33              |

|    | 9.2  | Typical Application               | 33              |

| 10 | Pow  | ver Supply Recommendations        | 36              |

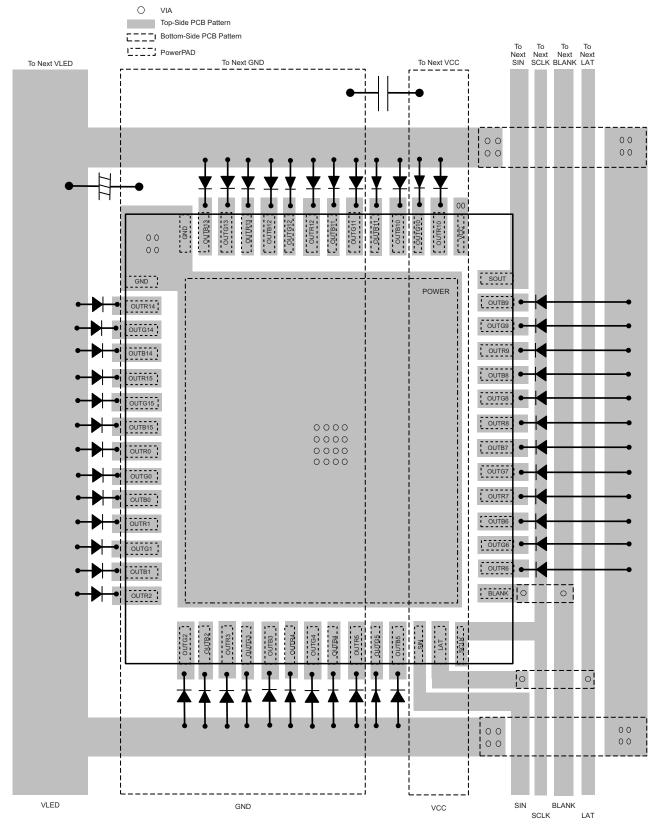

| 11 | Lay  | out                               | 36              |

|    | 11.1 | Layout Guidelines                 | 36              |

|    | 11.2 | Layout Example                    | 37              |

| 12 | Dev  | ice and Documentation Support     | 38              |

|    | 12.1 | Device Support                    | 38              |

|    | 12.2 | Documentation Support             | 38              |

|    | 12.3 | Trademarks                        | 38              |

|    | 12.4 | Electrostatic Discharge Caution   | 38              |

|    | 12.5 | Glossary                          | <mark>38</mark> |

| 13 | Mec  | hanical, Packaging, and Orderable |                 |

|    | Info | rmation                           | 38              |

|    |      |                                   |                 |

# 4 Revision History

| Date       | Revision | Notes            |  |

|------------|----------|------------------|--|

| April 2014 | *        | Initial release. |  |

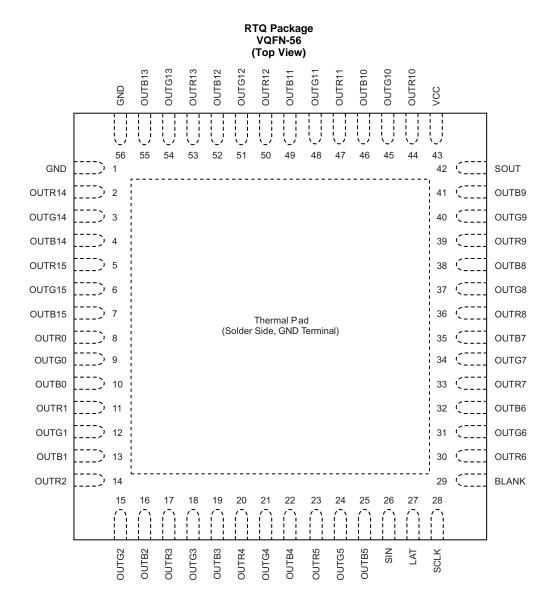

### 5 Pin Configuration and Functions

| TLC5954            |  |

|--------------------|--|

| SBVS241-APRII 2014 |  |

#### **Pin Functions**

|                    | PIN                                                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------|--------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME               | NO.                                                                | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| GND                | 1, 56                                                              | —   | Ground. All GND pins are connected internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| OUTR0 to<br>OUTR15 | 2, 5, 8, 11, 14, 17, 20,<br>23, 30, 33, 36, 39, 44,<br>47, 50, 53  | 0   | Red LED constant-current outputs (OUTR <i>n</i> ).<br>Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be<br>applied to each output. These outputs are turned on or off by the BLANK signal and the data in the output on<br>or off control data latch.                                                                                                                                                                                                                                                                 |  |

| OUTG0 to<br>OUTG15 | 3, 6, 9, 12, 15, 18, 21,<br>24, 31, 34, 37, 40, 45,<br>48, 51, 54  | 0   | Green LED constant-current outputs (OUTG <i>n</i> ).<br>Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be<br>applied to each output. These outputs are turned on or off by the BLANK signal and the data in the output on<br>or off control data latch.                                                                                                                                                                                                                                                               |  |

| OUTB0 to<br>OUTB15 | 4, 7, 10, 13, 16, 19, 22,<br>25, 32, 35, 38, 41, 46,<br>49, 52, 55 | ο   | Blue LED constant-current outputs (OUTB <i>n</i> ).<br>Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be<br>applied to each output. These outputs are turned on or off by the BLANK signal and the data in the output on<br>or off control data latch.                                                                                                                                                                                                                                                                |  |

| SIN                | 26                                                                 | I   | Serial data input of the 49-bit common shift register, Schmitt buffer input.<br>When SIN is high, the LSB is set to 1 for only one SCLK input rising edge. If two SCLK rising edges are input<br>while SIN is high, then the 49-bit shift register LSB and LSB+1 are set to 1. When SIN is low, the LSB is set to<br>0 at the SCLK input rising edge.                                                                                                                                                                                                                            |  |

| LAT                | 27                                                                 | I   | Edge-triggered latch, Schmitt buffer input.<br>The LAT rising edge latches data from the common shift register either into the output on or off data latch or<br>the maximum current control (MC), brightness control (BC), or function control (FC) data latch. When the<br>common shift register data are latched into the on or off data latch, data in the common shift register are<br>simultaneously replaced with SID, which is selected by SIDLD. Refer to the <i>Output On or Off Data Latch</i> and<br><i>Status Information Data (SID)</i> sections for more details. |  |

| SCLK               | 28                                                                 | I   | Serial data shift clock, Schmitt buffer input.<br>Data present on SIN are shifted to the 49-bit common shift register LSB with the SCLK rising edge. Data in the<br>shift register are shifted towards the MSB at each SCLK rising edge. The common shift register MSB appears<br>on SOUT.                                                                                                                                                                                                                                                                                       |  |

| BLANK              | 29                                                                 | I   | Blank all outputs, Schmitt buffer input.<br>When BLANK is high, all constant-current outputs (OUTX <i>n</i> ) are forced off. When BLANK is low, all OUTX <i>n</i> are controlled by the on or off control data in the data latch.                                                                                                                                                                                                                                                                                                                                               |  |

| SOUT               | 42                                                                 | 0   | Serial data output of the 49-bit common shift register.<br>SOUT is connected to the MSB of the register. Data are clocked out at the SCLK rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| VCC                | 43                                                                 | _   | Power-supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                    | Thermal pad                                                        | -   | Ground. The thermal pad must be connected to GND on the printed circuit board (PCB).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                               |                                                   | MIN  | MAX                   | UNIT |

|----------------------|-------------------------------|---------------------------------------------------|------|-----------------------|------|

| VCC                  | Supply voltage <sup>(2)</sup> |                                                   | -0.3 | 4.0                   | V    |

| V <sub>IN</sub>      | Input voltage range           | SIN, SCLK, LAT, BLANK                             | -0.3 | V <sub>CC</sub> + 0.3 | V    |

|                      |                               | SOUT                                              | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OUT</sub>     | Output voltage range          | OUTR0 to OUTR15, OUTG0 to OUTG15, OUTB0 to OUTB15 | -0.3 | 11                    | V    |

| T <sub>J</sub> (max) | Operating junction temperatu  | ire                                               |      | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to device ground pin.

#### 6.2 Handling Ratings

|                    |                          |                                                                                          | MIN  | MAX  | UNIT |

|--------------------|--------------------------|------------------------------------------------------------------------------------------|------|------|------|

| T <sub>stg</sub>   | Storage temperature rang | Storage temperature range                                                                |      |      | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | -200 | 2000 | V    |

|                    |                          | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -500 | 500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

At  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted.

|                         | PARAMETER                            | TEST CONDITIONS                                                                                               | MIN                 | NOM MAX             | UNIT |

|-------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------|

| DC CHARA                | CTERISTICS (VCC = 3 V to 3.6 V)      |                                                                                                               |                     |                     |      |

| V <sub>CC</sub>         | Supply voltage                       |                                                                                                               | 3.0                 | 3.6                 | V    |

| Vo                      | Voltage applied to output            | OUTR0 to OUTR15, OUTG0 to<br>OUTG15, OUTB0 to OUTB15                                                          |                     | 10                  | V    |

| V <sub>IH</sub>         | High-level input voltage             | SIN, SCLK, LAT, BLANK                                                                                         | $0.7 \times V_{CC}$ | V <sub>CC</sub>     | V    |

| V <sub>IL</sub>         | Low-level input voltage              | SIN, SCLK, LAT, BLANK                                                                                         | GND                 | $0.3 \times V_{CC}$ | V    |

| I <sub>OH</sub>         | High-level output current            | SOUT                                                                                                          |                     | -2                  | mA   |

| I <sub>OL</sub>         | Low-level output current             | SOUT                                                                                                          |                     | 2                   | mA   |

| T <sub>A</sub>          | Operating free-air temperature range |                                                                                                               | -40                 | +85                 | °C   |

| TJ                      | Operating junction temperature range |                                                                                                               | -40                 | +125                | °C   |

| AC CHARA                | CTERISTICS (VCC = 3 V to 3.6 V)      |                                                                                                               |                     |                     |      |

| f <sub>CLK</sub> (SCLK) | Data shift clock frequency           | SCLK                                                                                                          |                     | 30                  | MHz  |

| t <sub>WH0</sub>        |                                      | SCLK                                                                                                          | 10                  |                     | ns   |

| t <sub>WL0</sub>        |                                      | SCLK                                                                                                          | 10                  |                     | ns   |

| t <sub>WH1</sub>        | Pulse duration                       | LAT                                                                                                           | 15                  |                     | ns   |

| t <sub>WH2</sub>        |                                      | BLANK                                                                                                         | 60                  |                     | ns   |

| t <sub>WL2</sub>        |                                      | BLANK                                                                                                         | 40                  |                     | ns   |

| t <sub>SU0</sub>        |                                      | SIN to SCLK↑                                                                                                  | 4                   |                     | ns   |

| t <sub>SU1</sub>        |                                      | LAT↓ to SCLK↑                                                                                                 | 20                  |                     | ns   |

| t <sub>SU2</sub>        | Setup time                           | SCLK↑ resumes normal mode,<br>BLANK↓, PSMODE bit = 01b                                                        | 12                  |                     | μs   |

| t <sub>SU3</sub>        |                                      | LAT $\uparrow$ for all data latching except all 0s resumes normal mode, BLANK $\downarrow$ , PSMODE bit = 10b | 12                  |                     | μs   |

| t <sub>H0</sub>         | Lold time                            | SCLK↑ to SIN                                                                                                  | 3                   |                     | ns   |

| t <sub>H1</sub>         | Hold time                            | SCLK↑ to LAT↑                                                                                                 | 10                  |                     | ns   |

|                         |                                      |                                                                                                               |                     |                     |      |

#### 6.4 Thermal Information

|                     |                                              | TLC5954    |      |

|---------------------|----------------------------------------------|------------|------|

|                     | THERMAL METRIC <sup>(1)</sup>                | RTQ (VQFN) | UNIT |

|                     |                                              | 56 PINS    |      |

| $R_{\theta JA}$     | Junction-to-ambient thermal resistance       | 29.1       |      |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 16.3       |      |

| $R_{\theta JB}$     | Junction-to-board thermal resistance         | 7.7        | °C/W |

| $\Psi_{JT}$         | Junction-to-top characterization parameter   | 0.3        | C/VV |

| $\Psi_{JB}$         | Junction-to-board characterization parameter | 7.7        |      |

| R <sub>0JCbot</sub> | Junction-to-case (bottom) thermal resistance | 2.8        |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics

At  $T_A = -40^{\circ}$ C to +85°C and  $V_{CC} = 3.0$  V to 3.6 V, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}$ C and  $V_{CC} = 3.3$  V.

| <u></u>            | PARAMETER                                                  | TEST CONDIT                                                                                                                                                     | IONS                                                                | MIN                  | TYP                  | MAX                  | UNIT |

|--------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

| V <sub>OH</sub>    | High-level output voltage                                  | I <sub>OH</sub> = -2 mA at SOUT                                                                                                                                 |                                                                     | $V_{CC} - 0.4$       |                      | V <sub>CC</sub>      | V    |

| V <sub>OL</sub>    | Low-level output voltage                                   | I <sub>OL</sub> = 2 mA at SOUT                                                                                                                                  |                                                                     |                      |                      | 0.4                  | V    |

| $V_{LOD0}$         |                                                            | LODVLT = 000b                                                                                                                                                   |                                                                     | 0.15                 | 0.20                 | 0.25                 | V    |

| V <sub>LOD1</sub>  | LED open-detection threshold                               | LODVLT = 001b, 101b, 110b, 11                                                                                                                                   | 1b                                                                  | 0.25                 | 0.30                 | 0.35                 | V    |

| $V_{LOD2}$         |                                                            | LODVLT = 010b                                                                                                                                                   |                                                                     | 0.35                 | 0.40                 | 0.45                 | V    |

| $V_{LOD3}$         |                                                            | LODVLT = 011b                                                                                                                                                   |                                                                     | 0.45                 | 0.50                 | 0.55                 | V    |

| $V_{LOD4}$         |                                                            | LODVLT = 100b                                                                                                                                                   |                                                                     | 0.55                 | 0.60                 | 0.65                 | V    |

| V <sub>LSD0</sub>  |                                                            | LSDVLT = 00b                                                                                                                                                    |                                                                     | $0.45 \times V_{CC}$ | $0.50 \times V_{CC}$ | $0.55 \times V_{CC}$ | V    |

| V <sub>LSD1</sub>  | LED short-detection threshold                              | LSDVLT = 01b                                                                                                                                                    |                                                                     | $0.65 \times V_{CC}$ | $0.70 \times V_{CC}$ | $0.75 \times V_{CC}$ | V    |

| $V_{LSD2}$         |                                                            | LSDVLT = 10b, 11b                                                                                                                                               |                                                                     | $0.85 \times V_{CC}$ | $0.90 \times V_{CC}$ | $0.95 \times V_{CC}$ | V    |

| I <sub>IN</sub>    | Input current                                              | $V_{IN} = V_{CC}$ or GND at SIN, SCLK,                                                                                                                          | LAT, and BLANK                                                      | -1                   |                      | 1                    | μA   |

| I <sub>CC0</sub>   |                                                            | SIN, SCLK, LAT = GND, BLANK<br>BCX = 7Fh, MC = 0h $(I_{OUTRn}, I_{OU})$<br>$I_{OUTBn} = 2.0$ -mA target) <sup>(1)</sup>                                         | = VCC, V <sub>OUTXn</sub> = 1 V,<br><sub>TGn</sub> = 2.9-mA target, |                      | 15                   | 19                   | mA   |

| I <sub>CC1</sub>   |                                                            | $ \begin{array}{l} \text{SIN, SCLK, LAT = GND, BLANK} \\ \text{BCX = 7Fh, MC = 5h (I_{OUTRn}, I_{OU}) \\ \text{I}_{OUTBn} = 12.2\text{-mA target} \end{array} $ |                                                                     |                      | 17.5                 | 22                   | mA   |

| I <sub>CC2</sub>   | Supply current (V <sub>CC</sub> )                          | SIN, SCLK, LAT, BLANK = GND $V_{OUTXn}$ = 1 V, BCX = 7Fh, MC =                                                                                                  |                                                                     |                      | 17.5                 | 22                   | mA   |

| I <sub>CC3</sub>   |                                                            | SIN, SCLK, LAT, BLANK = GND<br>$V_{OUTXn} = 1 V$ , BCX = 7Fh, MC = 34.9-mA target, $I_{OUTBn} = 24.4$ -mA                                                       | 7h (I <sub>OUTRn</sub> , I <sub>OUTGn</sub> =                       |                      | 20.5                 | 25.5                 | mA   |

| I <sub>CC4</sub>   |                                                            | In power-save mode, SIN, SCLK<br>BLANK = VCC                                                                                                                    | , LAT = GND,                                                        |                      | 7                    | 60                   | μA   |

| I <sub>OLC0</sub>  | Constant output current                                    | All OUTX $n$ = on, V <sub>OUTXn</sub> = V <sub>OUTfi</sub> ,<br>MC = 7h, at OUTR0 to OUTR15<br>OUTG15                                                           |                                                                     | 32.5                 | 34.9                 | 37.3                 | mA   |

| I <sub>OLC1</sub>  |                                                            | All OUTX $n$ = on, V <sub>OUTXn</sub> = V <sub>OUTfix</sub><br>MC = 7h, at OUTB0 to OUTB15                                                                      | <sub>s</sub> = 1 V, BC = 7Fh,                                       | 22.7                 | 24.4                 | 26.1                 | mA   |

|                    |                                                            |                                                                                                                                                                 | $T_J = +25^{\circ}C$                                                |                      |                      | 0.1                  | μA   |

| I <sub>OLKG</sub>  | Output leakage current                                     | BLANK = VCC, $V_{OUTXn} = V_{OUTfix}$<br>= 10 V, MC = 7h, at OUTX <i>n</i>                                                                                      | T <sub>J</sub> = +85°C                                              |                      |                      | 0.2                  | μΑ   |

|                    |                                                            |                                                                                                                                                                 | T <sub>J</sub> = +125°C                                             |                      |                      | 0.5                  | μΑ   |

| ΔI <sub>OLC0</sub> | Constant-current error (channel-to-channel) <sup>(2)</sup> | All OUTX $n$ = on, BCX = 7Fh, V <sub>OU</sub><br>MC = 7h, at same color group (C                                                                                |                                                                     |                      | ±1%                  | ±3%                  |      |

(1) X = R, G, and B. n = 0 to 15.

6

(2) The deviation of each output in the same color group (OUTR*n*, OUTG*n*, OUTB*n*) from the average of the same OUTX*n* group constant-current. Deviation is calculated by the formula:

$$\Delta (\%) = \left[ \frac{I_{OUTXn}}{\left[ \frac{I_{OUTX0} + I_{OUTX1} + \dots + I_{OUTX14} + I_{OUTX15}}{16} \right]} - 1 \right] \times 100$$

, where X = R, G, or B, and n = 0 to 15.

Submit Documentation Feedback

#### **Electrical Characteristics (continued)**

| At $T_A = -40^{\circ}$ C to +85°C and $V_{CC} = 3.0$ V to 3.6 V, unless otherwise noted. Typical values are at $T_A = +25^{\circ}$ C and $V_{CC} = 3.3$ V. |                                                          |                                                                                                                   |     |       |     |      |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|--|

|                                                                                                                                                            | PARAMETER                                                | TEST CONDITIONS                                                                                                   | MIN | TYP   | MAX | UNIT |  |

| ΔI <sub>OLC1</sub>                                                                                                                                         | Constant-current error (device-to-device) <sup>(3)</sup> | All OUTX <i>n</i> = on, BCX = 7Fh, $V_{OUTXn} = V_{OUTfix} = 1 V$ , MC = 7h, at same color group (OUTX <i>n</i> ) |     | ±0.5% | ±3% |      |  |

| $\Delta I_{OLC2}$                                                                                                                                          | Line regulation <sup>(4)</sup>                           | All OUTX $n$ = on, BCX = 7Fh, V <sub>OUTXn</sub> = V <sub>OUTfix</sub> = 1 V, MC = 7h, at OUTX $n$                |     | ±0.5  | ±1  | %/V  |  |

| ΔI <sub>OLC3</sub>                                                                                                                                         | Load regulation <sup>(5)</sup>                           | All OUTX $n$ = on, BCX = 7Fh, V <sub>OUTXn</sub> = 1 V to 3 V, V <sub>OUTfix</sub> = 1 V, MC = 7h, at OUTX $n$    |     | ±1    | ±3  | %/V  |  |

(3) The deviation of the OUTX*n* constant-current average from the ideal constant-current value. Deviation is calculated by the formula:

|         | [ I <sub>OUTX0</sub> + I <sub>OUTX1</sub> + + I <sub>OUTX15</sub> | – (Ideal Output Current) |       |

|---------|-------------------------------------------------------------------|--------------------------|-------|

| ∆ (%) = | 16                                                                |                          | × 100 |

| ∆(70) - | Current                                                           | × 100                    |       |

Ideal current is 34.9 mA for OUTR*n* and OUTG*n*. Ideal current is 24.4 mA for OUTB*n* with MC data equal to 7h., where X = R, G, or B, and n = 0 to 15.

(4) Line regulation is calculated by the formula:

$$\Delta (\%/V) = \left[ \frac{(I_{OUTXn} \text{ at } VCC = 3.6 \text{ V}) - (I_{OUTXn} \text{ at } VCC = 3.0 \text{ V})}{I_{OUTXn} \text{ at } VCC = 3.0 \text{ V}} \right] \times \frac{100}{3.6 \text{ V} - 3.0 \text{ V}}$$

X = R, G, or B. n = 0 to 15.

(5) Load regulation is calculated by the equation:

$$\Delta (\%/V) = \left( \frac{(I_{OUTXn} \text{ at } V_{OUTXn} = 3 \text{ V}) - (I_{OUTXn} \text{ at } V_{OUTXn} = 1 \text{ V})}{I_{OUTXn} \text{ at } V_{OUTXn} = 1 \text{ V}} \right) \times \frac{100}{3 \text{ V} - 1 \text{ V}}$$

, where X = R, G, or B, and n = 0 to 15.

#### 6.6 Switching Characteristics

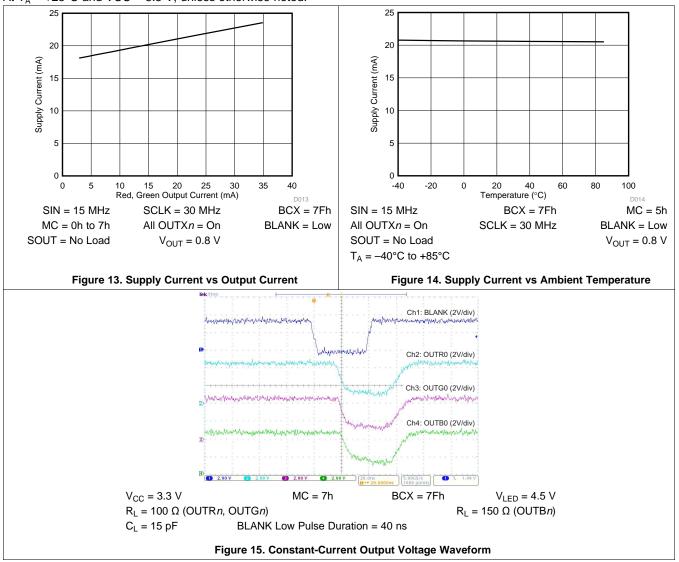

At  $T_A = -40^{\circ}$ C to +85°C,  $V_{CC} = 3.0$  V to 3.6 V,  $C_L = 15$  pF,  $R_L = 100 \Omega$  for OUTR*n* and OUTG*n*,  $R_L = 150 \Omega$  for OUTB*n*, MC = 7h, and  $V_{LED} = 4.5$  V, unless otherwise noted. Typical values at  $T_A = +25^{\circ}$ C and  $V_{CC} = 3.3$  V.

|                     | PARAMETER                           | TEST CONDITIONS                                                                                                                                | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>R0</sub>     | Dias time                           | SOUT                                                                                                                                           |     | 2   | 5   | ns   |

| t <sub>R1</sub>     | Rise time                           | OUTXn, BCX = 7Fh <sup>(1)</sup>                                                                                                                |     | 20  | 50  | ns   |

| t <sub>F0</sub>     | Foll time                           | SOUT                                                                                                                                           |     | 2   | 5   | ns   |

| t <sub>F1</sub>     | - Fall time                         | OUTX <i>n</i> , BCX = 7Fh                                                                                                                      |     | 20  | 50  | ns   |

| t <sub>D0</sub>     |                                     | SCLK↑ to SOUT                                                                                                                                  |     | 13  | 23  | ns   |

| t <sub>D1</sub>     | Propagation delay <sup>(2)</sup>    | LAT↑ to OUTR0 on to off or OUTR0 off to on, BCX = 7Fh                                                                                          |     | 30  | 60  | ns   |

| t <sub>D2</sub>     |                                     | BLANK↓↑ to OUTR0 on to off or OUTR0 off to on, BCX = 7Fh                                                                                       |     | 30  | 60  | ns   |

| t <sub>D3</sub>     |                                     | OUTR <i>n</i> on to OUTG <i>n</i> on, OUTG <i>n</i> on to OUTB <i>n</i> on, and OUTB <i>n</i> on to the next OUTR <i>n</i> on, BCX = 7Fh       |     | 1.5 | 5   | ns   |

| t <sub>D4</sub>     | _                                   | OUTR <i>n</i> off to OUTG <i>n</i> off, OUTG <i>n</i> off to OUTB <i>n</i> off, and OUTB <i>n</i> off to the next OUTR <i>n</i> off, BCX = 7Fh |     | 1.5 | 5   | ns   |

| t <sub>D5</sub>     |                                     | LAT↑ to power-save mode by writing data for all OUTXn off                                                                                      |     | 150 | 300 | ns   |

| t <sub>ON_ERR</sub> | Output on-time error <sup>(3)</sup> | OUTXn on or off data = all 1s, BCX = 7Fh, 40-ns BLANK low-level one-<br>shot pulse input                                                       | -35 |     | 35  | ns   |

(1) X = R, G, or B. n = 0 to 15.

(2)  $t_{D3}$  (OUTR*n* on to OUTG*n* on, OUTG*n* on to OUTB*n* on, and OUTB*n* on to the next OUTR*n* on) and  $t_{D4}$  (OUTR*n* off to OUTG*n* off, OUTG*n* off to OUTG*n* off to the next OUTR*n* off) are calculated by:  $t_{D3}$  (ns) = (the propagation delay between OUTR0 on to OUTB7 on) / 47 and

$t_{D3}$  (ns) = (the propagation delay between OUTR0 on to OUTB7 on) / 47 ar  $t_{D4}$  (ns) = (the propagation delay between OUTR0 off to OUTB7 off) / 47.

(3) Output on-time error ( $t_{ON\_ERR}$ ) is calculated by the formula:  $t_{ON\_ERR}$  (ns) =  $t_{OUT\_ON}$  – BLANK low-level pulse duration.  $t_{OUT\_ON}$  is the actual on-time of OUTX*n*.

TLC5954 SBVS241 – APRIL 2014 TEXAS INSTRUMENTS

www.ti.com

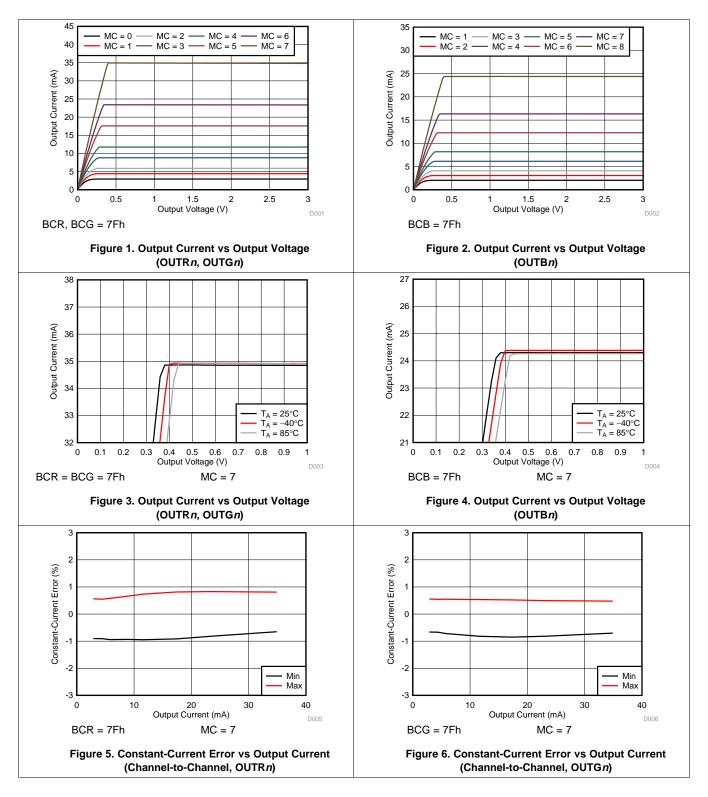

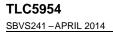

#### 6.7 Typical Characteristics

At  $T_A = +25^{\circ}C$  and VCC = 3.3 V, unless otherwise noted.

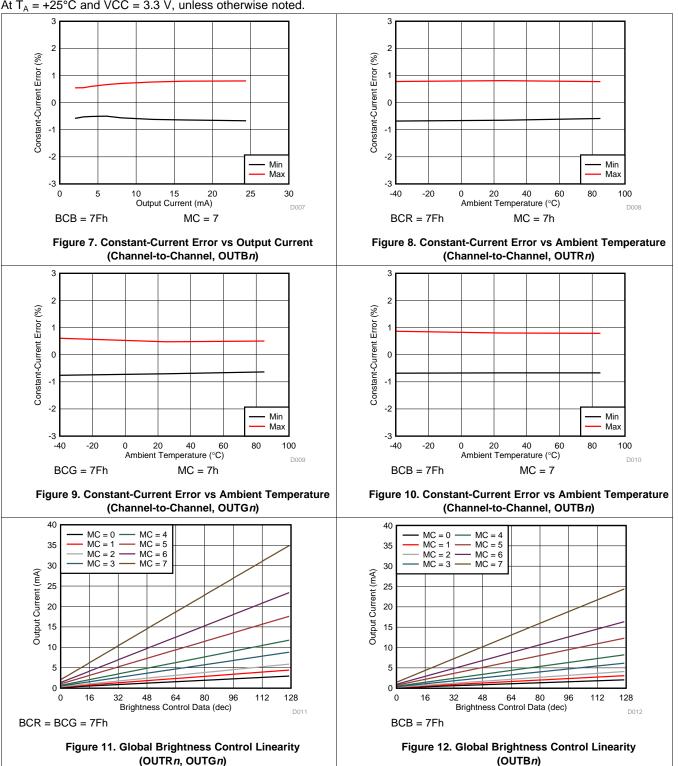

#### Typical Characteristics (continued)

At  $T_A = +25^{\circ}C$  and VCC = 3.3 V, unless otherwise noted.

#### **Typical Characteristics (continued)**

At  $T_A = +25^{\circ}C$  and VCC = 3.3 V, unless otherwise noted.

#### 7 Parameter Measurement Information

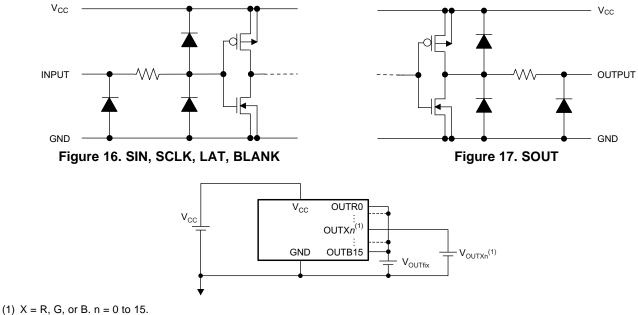

#### 7.1 Pin Equivalent Input and Output Schematic Diagrams

Figure 18. OUTXn

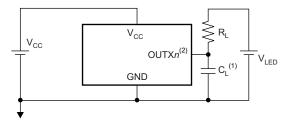

#### 7.2 Test Circuits

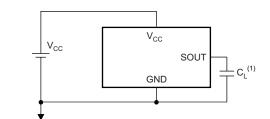

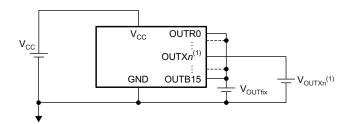

(1)  $C_L$  includes measurement probe and jig capacitance.

(2) X = R, G, or B. n = 0 to 15.

# Figure 19. Rise and Fall Time Test Circuit for OUTX*n*

(1)  $C_L$  includes measurement probe and jig capacitance.

(1) X = R, G, or B. n = 0 to 15.

**TLC5954** SBVS241 – APRIL 2014

www.ti.com

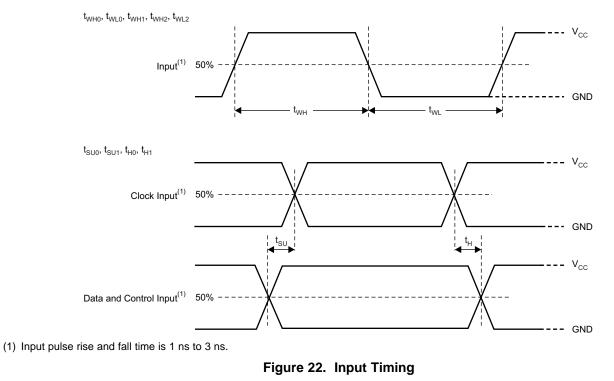

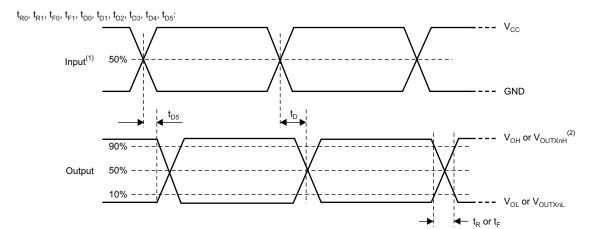

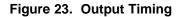

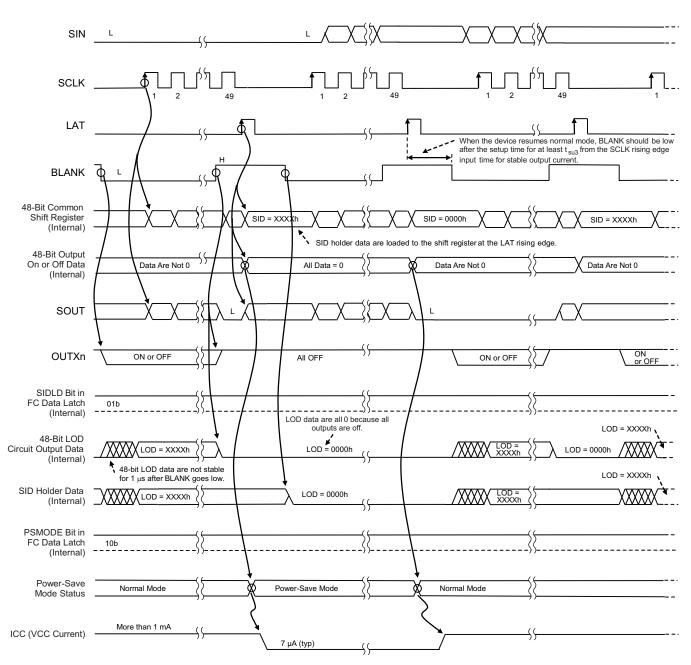

#### 7.3 Timing Diagrams

(1) Input pulse rise and fall time is 1 ns to 3 ns.

(2) X = R, G, or B. n = 0 to 15.

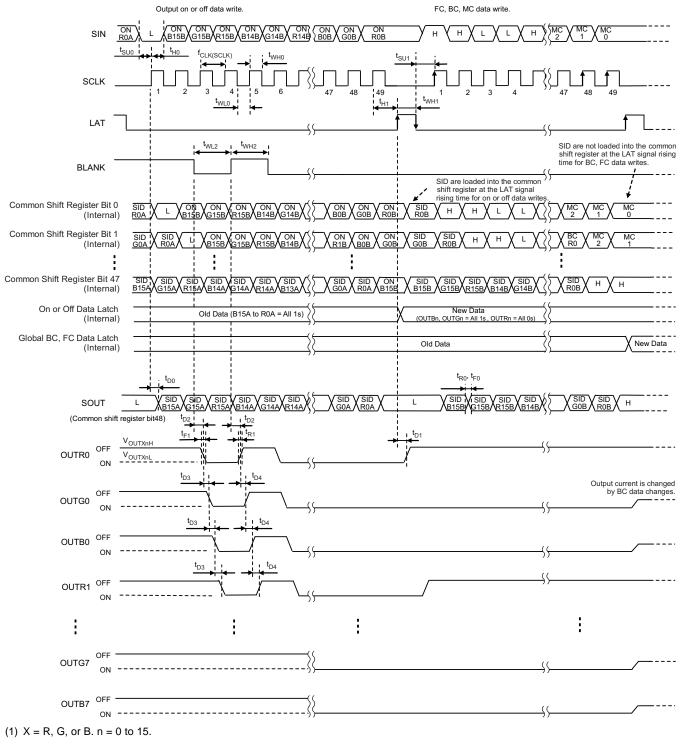

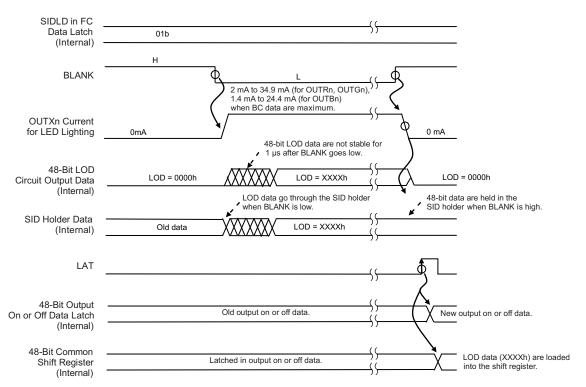

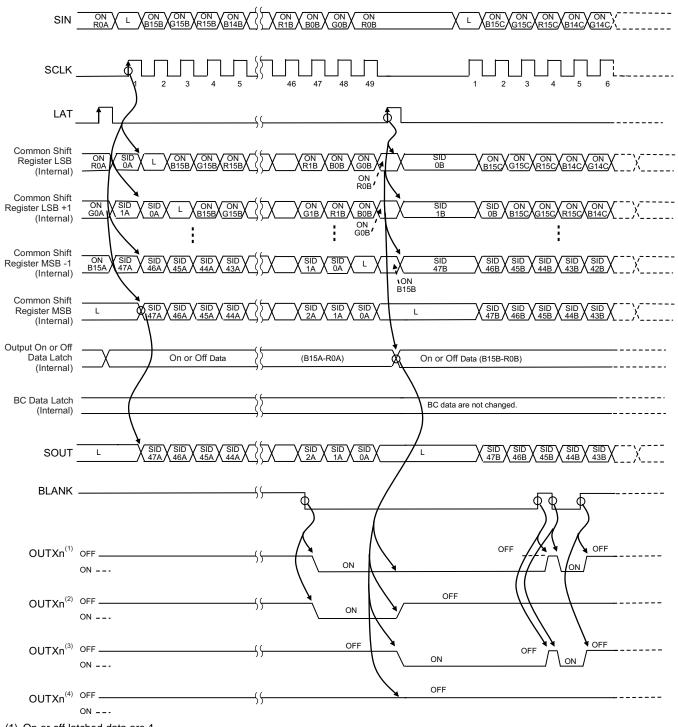

#### **Timing Diagrams (continued)**

Figure 24. Data Write and OUTX*n* On or Off Timing Diagram

TEXAS INSTRUMENTS

www.ti.com

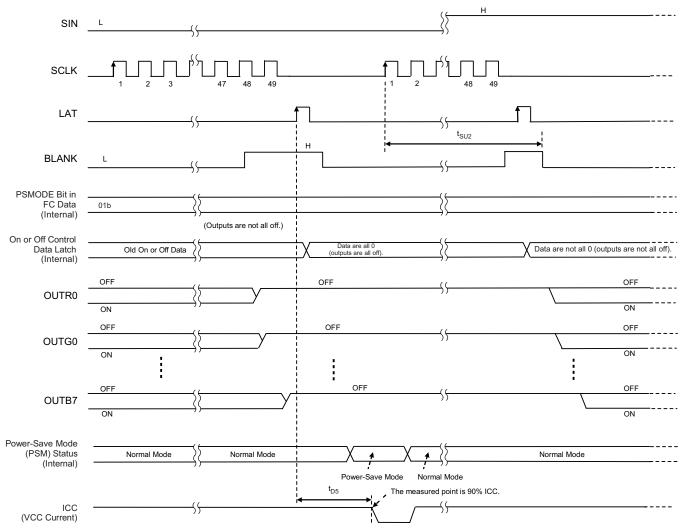

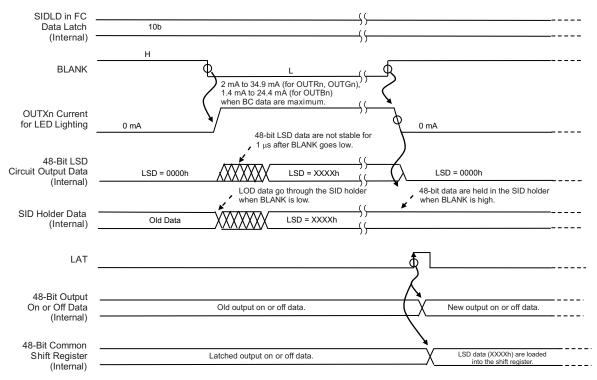

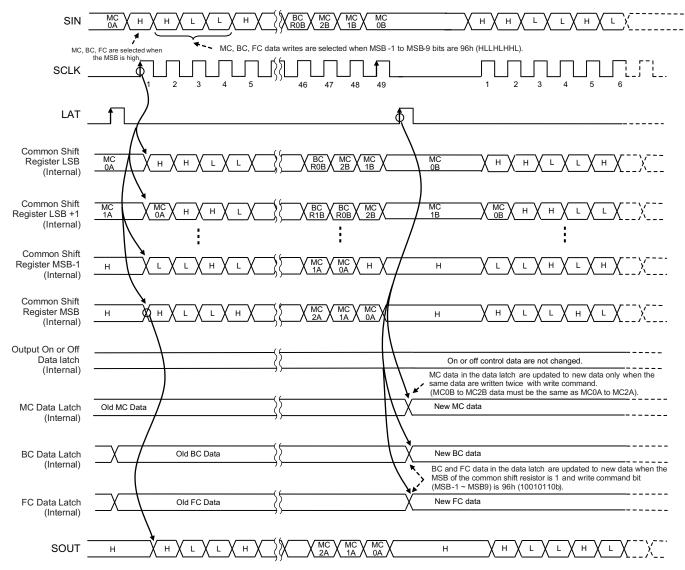

# **Timing Diagrams (continued)**

Figure 25. Power-Save Mode Timing Diagram (PSMODE = 01b)

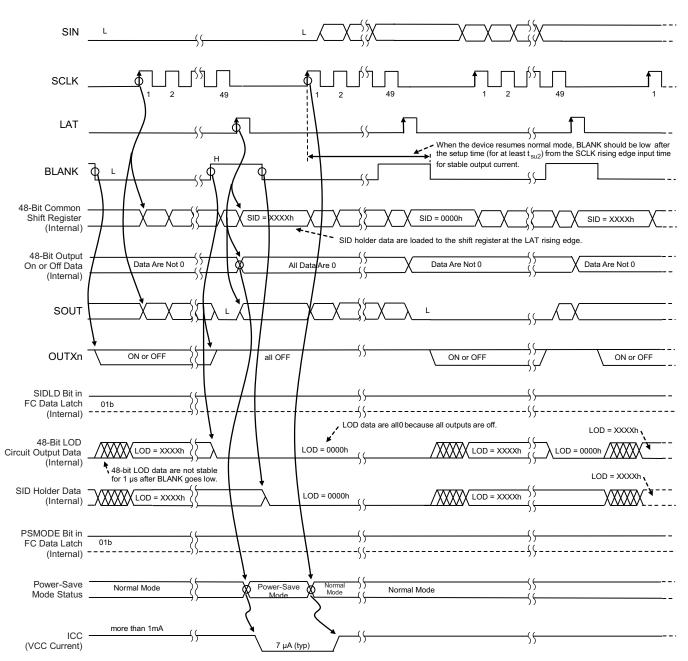

#### **Timing Diagrams (continued)**

Figure 26. Power-Save Mode Timing Diagram (PSMODE = 10b)

#### 8 Detailed Description

#### 8.1 Overview

The TLC5954 is 48-channel, 34.9-mA or 24.4-mA, constant-current LED driver that can control the LED on of off settings with the BLANK signal for grayscale (GS) control. The minimum 40-ns BLANK signal pulse duration can be input to generate very short LED on-time.

The device has a 128-step, 7-bit, output current control function termed global brightness control (BC) that can control each color group output. The BC function can adjust the red, green, and blue LED intensity for true white with constant-current control. The device contributes higher image quality to LED displays with fine white balance tuning by using these BLANK pulse durations and MC, BC functions.

The display controller can locate LED lamp failures via the device because the controller can detect LED lamp failures with the LED open detection (LOD) and LED short detection (LSD) functions. Furthermore, the reliability of the display can be improved by the LOD and LSD function.

The device maximum constant-current output value can be set by an internal register data function referred to as maximum current control (MC), instead of the general method of using an external resistor setting. Thus, any failure modes that occur from the external resistor can be eliminated. One resistor can also be eliminated with the MC function.

The device constant-current output can drive approximately 17.4 mA at a 0.32-V output voltage and a +25°C ambient temperature. This voltage is called *knee voltage*. This 0.32-V, low-knee voltage can contribute to the design of a lower-power display system.

The total number of LED drivers on one LED display panel can be reduced because 48 LED lamps can be driven by one LED driver. Therefore, designing fine-pitch LED displays is simplified.

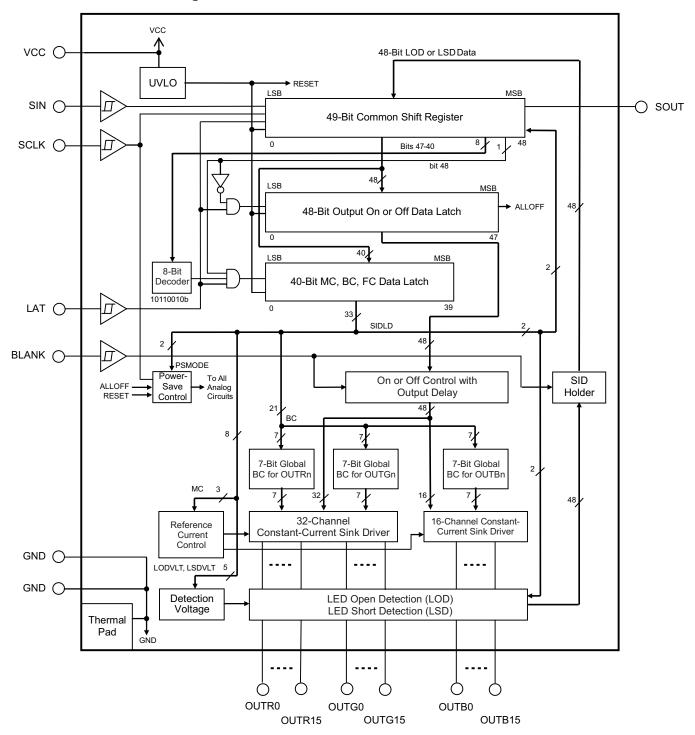

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Output Current Calculation

The output current value controlled by MC and BC can be calculated by Equation 1.

$$I_{OUTn}$$

(mA) =  $I_{OLCMax}$  (mA) ×  $\left[ 0.06 + 0.94 \times \frac{BCX}{127} \right]$

where:

- I<sub>OLCMax</sub> = the maximum constant-current value for all OUTX*n* for each color group programmed by MC data,

- BCX = the global brightness control value (0h to 7Fh),

- X = R, G, or B for the red, green, or blue color group, and

- n = 0 to 15.

(1)

Each output sinks the  $I_{OLCMax}$  current when they turn on and the global brightness control (BC) data are set to the maximum value of 7Fh (127d).

#### 8.3.2 Status Information Data (SID)

The status information data (SID) contains the status of the LED open detection (LOD) and LED short detection (LSD).

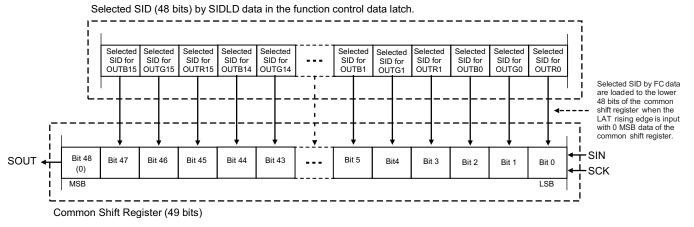

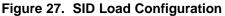

When the output on-off data latch is written, the SID selected by the SIDLD bits are loaded into lower 48 bits in the common shift register at the LAT rising edge after the original data in the common shift register are copied to the on-off data latch. When the BC and FC data are written, SID data are not loaded to the common shift register. After SID data are copied into the common shift register, new SID data are not loaded until new data are written into the common shift register even if a LAT rising edge is input.

When the device resumes normal operation after the power-save mode, a BLANK rising edge must be input after  $t_{SU2}$  or  $t_{SU3}$  elapses in order to retain correct LOD and LSD data in the SID holder because the SID analog circuit does not function during power-save mode. The SID load configuration and SID read timing are shown in Figure 27 and Figure 28, respectively.

#### Feature Description (continued)

Figure 28. SID Read Timing Diagram

#### Feature Description (continued)

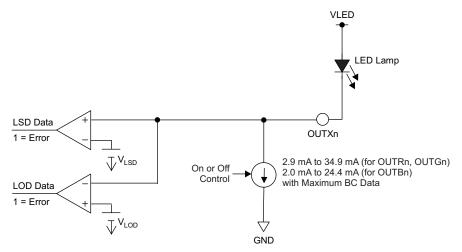

#### 8.3.3 LED Open Detection (LOD)

LOD detects a fault caused by an open circuit in the *n*th LED string, or a short from OUTX*n* to ground with low impedance, by comparing the OUTX*n* voltage to the LOD detection threshold voltage level set by LODVLT in the function control data latch (see Table 6 and Table 8). If the OUTX*n* voltage is lower than the programmed voltage, the corresponding output LOD bit is set to 1 to indicate a shorted LED. Otherwise, the LOD bit is set to 0. LOD data are only valid for outputs that are set to 1 in the output on-off data latch. LOD data are always 0 for outputs that are set to 0 in the output on-off data latch.

LOD data are stored in a 48-bit register called the SID holder (see the *Functional Block Diagram*) at the BLANK rising edge when the SIDLD bits are set to 01b (see Table 7). The loaded LOD data can be read out through the common shift register as SID data at the SOUT pin. LOD data are not valid for 1 µs after the output is turned on. If the OUTX*n* controlled by the BLANK pin is less than 1 µs, the LOD data must be ignored.

When the device resumes operation from power-save mode, all OUTX*n* can be controlled by the internal on-off control data and the BLANK level after the setup time ( $t_{SU2}$ ) elapses. LOD data are valid after the propagation delay. Figure 29 illustrates an LOD and LSD circuit, Table 1 shows the SID bit settings for LOD and LSD, and Figure 30 illustrates the LED open-detection operating timing diagram.

Figure 29. LOD, LSD Circuit

#### Table 1. LOD, LSD Truth Table

| LOD                                                       | LSD                                                                                                   | CORRESPONDING BIT<br>IN SID |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|

| LED is not open (V <sub>OUTXn</sub> > V <sub>LOD</sub> )  | LED is not shorted (V <sub>OUTXn</sub> ≤ V <sub>LSD</sub> )                                           | 0                           |

| LED is open or shorted to GND ( $V_{OUTXn} \le V_{LOD}$ ) | LED is shorted between anode and cathode, or shorted to higher voltage side ( $V_{OUTXn} > V_{LSD}$ ) | 1                           |

Figure 30. LOD Operation Timing Diagram

#### 8.3.4 LED Short Detection (LSD)

LSD data detect a fault caused by a shorted LED by comparing the OUTX*n* voltage to the LSD detection threshold voltage level set by LSDVLT in the function control data latch (see Table 6 and Table 9). If the OUTX*n* voltage is higher than the programmed voltage, the corresponding output LSD bit is set to 1 to indicate a shorted LED. Otherwise, the LSD bit is set to 0. LSD data are only valid for outputs that are set to 1 in the output on-off data latch. LSD data are always 0 for outputs that are set to 0 in the output on-off data latch.

LSD data are loaded into a 48-bit register called the SID holder at the BLANK rising edge when the SIDLD bits are set to 10b (see Table 7). The loaded LSD data can be read out through the common shift register as SID data at the SOUT pin. LSD data are not valid for 1 µs after the output is turned on. If the OUTX*n* controlled by the BLANK pin is less than 1 µs, the LSD data must be ignored.

TLC5954 SBVS241 – APRIL 2014

When the device resumes operation from power-save mode, all OUTX*n* can be controlled by the internal on-off control data and the BLANK level after the setup time ( $t_{SU2}$ ) elapses. LSD data are valid after the propagation delay. Figure 29 illustrates an LOD and LSD circuit and Figure 31 shows LED short-detection operating timing diagram.

Figure 31. LSD Operation Timing Diagram

#### 8.3.5 Noise Reduction

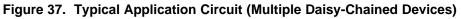

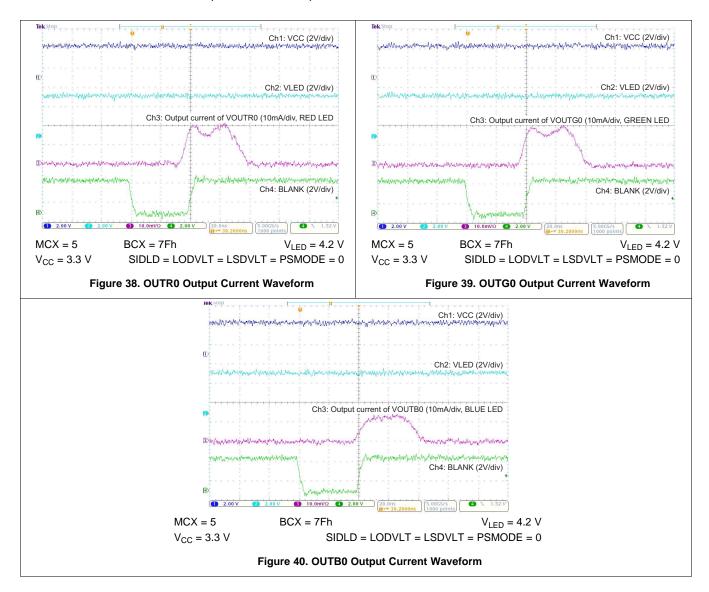

Large surge currents may flow through the device and the board on which the device is mounted if all 48 LED channels turned on simultaneously when BLANK toggles from high to low. These large current surges can induce detrimental noise and electromagnetic interference (EMI) into other circuits. The device turns on the LED channels in a series delay to provide a circuit soft-start feature. A small delay circuit is implemented between each output. When all bits of the on-off data latch are set to 1, each constant-current output turns on in the following order: OUTR0, OUTG0, OUTB0, OUTR15, OUTG15, OUTB15, OUTR1, OUTG1, OUTB1, OUTR14, OUTG14, OUTB14, OUTR2, OUTG2, OUTB2, OUTR13, OUTG13, OUTB13, OUTR3, OUTG3, OUTB3, OUTR12, OUTG12, OUTB12, OUTR4, OUTG4, OUTB4, OUTR11, OUTG11, OUTB11, OUTR5, OUTG5, OUTB5, OUTR10, OUTG10, OUTB10, OUTR6, OUTG6, OUTB6, OUTR9, OUTG9, OUTB9, OUTR7, OUTG7, OUTB7, OUTB7, OUTR8, OUTG8, and OUTB8 with a small delay for each OUTX*n* after BLANK goes low or LAT goes high, see Figure 24. Both turn-on and turn-off times are delayed.

#### 8.4 Device Functional Modes

#### 8.4.1 Maximum Constant Sink Current

The maximum output current of each channel (I<sub>OLCMax</sub>) is programmed by maximum current (MC) data and can be set by the serial interface.

$I_{OLCMax}$  is the highest current for each output. Each OUTX*n* sinks  $I_{OLCMax}$  current when they turn on with the global brightness control (BC) data set to the maximum value of 7Fh (127d). MC data are updated when the same data are written to the MC bits twice. When the device is powered on, the MC data latch is set to 0.

Table 2 shows the characteristics of the constant-current sink versus the MC control data.

|               | MC DATA     | I <sub>OLCMa</sub> | <sub>x</sub> (mA)                |               |

|---------------|-------------|--------------------|----------------------------------|---------------|

| BINARY        | DECIMAL     | HEX                | OUTR <i>n</i> ,<br>OUTG <i>n</i> | OUTB <i>n</i> |

| 000 (default) | 0 (default) | 0 (default)        | 2.9                              | 2.0           |

| 001           | 1           | 1                  | 4.4                              | 3.1           |

| 010           | 2           | 2                  | 5.8                              | 4.1           |

| 011           | 3           | 3                  | 8.7                              | 6.1           |

| 100           | 4           | 4                  | 11.6                             | 8.1           |

| 101           | 5           | 5                  | 17.4                             | 12.2          |

| 110           | 6           | 6                  | 23.2                             | 16.3          |

| 111           | 7           | 7                  | 34.9                             | 24.4          |

# Table 2. Maximum Constant-Current Output versus MC Data

#### 8.4.2 Global Brightness Control (BC) Function: Sink Current Control

The device is capable of simultaneously adjusting the output current of each color group (OUTR0 to OUTR15, OUTG0 to OUTG15, and OUTB0 to OUTB15). This function is called *global brightness control* (BC). The BC function allows the global BC data of LEDs connected to the three color groups to be adjusted. All OUTX*n* can be adjusted in 128 steps from 6% to 100% of the maximum output current, I<sub>OLCMax</sub>. The BC data are transmitted to the device by the serial interface. When BC data change, the output current also changes immediately.

Table 3 shows the BC data versus the constant-current ratio against I<sub>OLCMax</sub>.

| BC DATA  |         |     |                                             | OUTPUT CURRENT (mA, typ)                      |                                              |                                               |                                              |

|----------|---------|-----|---------------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------------|----------------------------------------------|

| BINARY   |         |     | OUTPUT                                      | OUTR <i>n</i> ,                               | OUTGn                                        | OU <sup>.</sup>                               | TB <i>n</i>                                  |

| MSB LSB  | DECIMAL | HEX | RATIO TO<br>I <sub>OLCMax</sub><br>(%, typ) | MC = 7h<br>(I <sub>OLCMax</sub> = 34.9<br>mA) | MC = 0h<br>(I <sub>OLCMax</sub> = 2.9<br>mA) | MC = 7h<br>(I <sub>OLCMax</sub> = 24.4<br>mA) | MC = 0h<br>(I <sub>OLCMax</sub> = 2.0<br>mA) |

| 000 0000 | 0       | 00  | 6.0                                         | 2.09                                          | 0.17                                         | 1.47                                          | 0.12                                         |

| 000 0001 | 1       | 01  | 6.7                                         | 2.35                                          | 0.20                                         | 1.65                                          | 0.14                                         |

| 000 0010 | 2       | 02  | 7.5                                         | 2.61                                          | 0.22                                         | 1.83                                          | 0.15                                         |

|          |         |     |                                             |                                               |                                              |                                               |                                              |

| 111 1101 | 125     | 7D  | 98.5                                        | 34.4                                          | 2.86                                         | 24.1                                          | 1.96                                         |

| 111 1110 | 126     | 7E  | 99.3                                        | 34.7                                          | 2.88                                         | 24.3                                          | 1.98                                         |

| 111 1111 | 127     | 7F  | 100.0                                       | 34.9                                          | 2.90                                         | 24.4                                          | 2.00                                         |

#### 8.4.3 Constant-Current Output On or Off Control

When BLANK is low, each OUTXn is controlled by the data in the output on or off data latch. When data corresponding to an output equal 1, the output turns on; when data corresponding to an output equal 0, the output turns off. When BLANK is high, all OUTXn are forced off. When the device is powered on, the data in the output on or off data latch are set to 0. A truth table for the on or off control data is shown in Table 4.

| ON OR OFF CONTROL DATA | CONSTANT-CURRENT OUTPUT STATUS |

|------------------------|--------------------------------|

| 0 (default)            | Off                            |

| 1                      | On                             |

#### Table 4. On or Off Control Data Truth Table

#### 8.4.4 Power-Save Mode

The power-save mode control bits are assigned in the BC and FC data latch. The device dissipation current becomes 7  $\mu$ A (typ) in this mode. In PSM, all analog circuits (such as the constant-current outputs and the LOD and LSD circuit) do not function. However, logic circuits (such as the common shift register, on-off data latch, and BC and FC data latch) do function. When the two bits in PSMODE are 01b, 10b, or 11b, the power-save mode is enabled. When the two bits are 11b, the device is always in power-save mode. When the two bits are set to 00b, the device is always in normal operation. If all 0s are written in the output on-off data latch, the device goes into power-save mode when the two bits are 01b or 10b. When a rising edge is generated at SCLK with the two PSMODE bits set to 01b, the device exits PSM and returns to normal operation. When data in the output on-off data latch are not all 0s, and when the two PSMODE bits set to 10b, the device exits PSM and returns to normal operation. All OUTX*n* are turned on after the device exits PSM. Figure 32 and Figure 33 provide power-save mode timing diagrams for PSMODE set to 01b and 10b, respectively. The BLANK level should go low after t<sub>SU2</sub> or t<sub>SU3</sub> when the device exists PSM and returns to normal mode because the output current may be unstable immediately after starting normal mode.

Figure 32. Power-Save Mode (FC Data PSMODE Bits = 01b)

TLC5954 SBVS241 – APRIL 2014

TEXAS INSTRUMENTS

www.ti.com

Figure 33. Power-Save Mode (FC Data PSMODE Bits = 10b)

#### 8.5 Register Maps

#### 8.5.1 Register and Data Latch Configuration

The device has one common shift register and four control data latches. These data latches are the output on or off data latch, the maximum current control (MC) data latch, the global brightness control (BC) data latch, and the function control (FC) data latch.

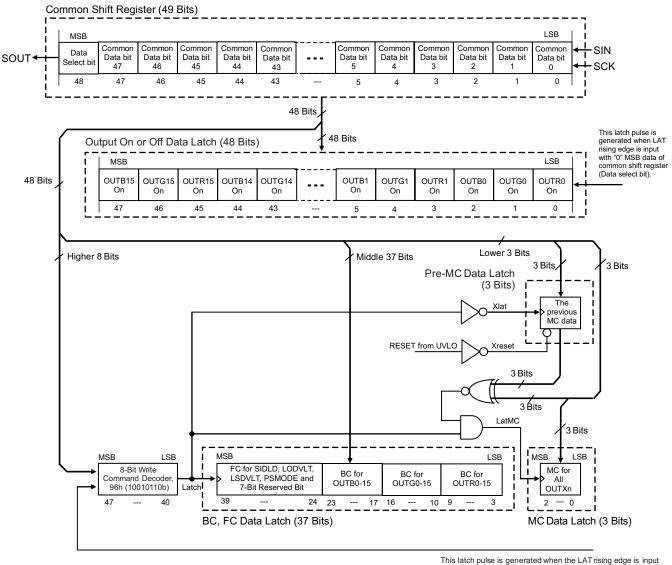

The common shift register is 49 bits long, the output on or off data latch is 48 bits long, and another 48-bit data latch is comprised of the 40-bit MC, BC, and FC data latches with an 8-bit write command decoder. If the common shift register MSB is 0, the least significant 48 bits of data from the 49-bit common shift register are latched into the output on or off data latch. If the MSB (bit 48) from the 49-bit common shift register is 1 and MSB 1 through MSB 9 (bits [47:40]) are 96h (10010110b) for the write command data, the middle 37 bits (bits [39:3]) in the common shift register are latched into the BC and FC data latch. MC data are updated when the same data are written to the MC bits twice with the write command data (96h) and the MSB (bit 48) set to 1. Figure 34 shows the configuration of the common shift register and the four data latches.

This latch pulse is generated when the LAT rising edge is input with the MSB data of the common shift register = 1 (data select bit).

#### Figure 34. Common Shift Register and Data Latch Configuration

#### **Register Maps (continued)**

#### 8.5.1.1 Common Shift Register

The 49-bit common shift register is used to shift data from the SIN pin into the device. The data shifted into the register are used for the output on or off control, MC, BC, and several FC functions, and the write command. The LSB of the common shift register is connected to SIN and the MSB is connected to SOUT. On each SCLK rising edge, the data on SIN are shifted into the LSB and all 49 bits are shifted towards the MSB. The register MSB is always connected to SOUT. In addition, the status information data (SID) selected by the SIDLD bits in the FC data latch are loaded to the lower 48 bits of the 49-bit common shift register when a rising edge is input on LAT for the output on or off control data write operation except when SIDLD = 00b and 11b (see Table 7). When the device is powered on, all 49 bits of the common shift register are set to 0.

#### 8.5.1.2 Output On or Off Data Latch

The output on or off data latch is 48 bits long and sets the on or off status for each constant-current output (OUTR*n*, OUTG*n*, OUTB*n*). When BLANK is low, the output corresponding to the specific bit in the output on or off data latch is turned on if the data are 1 and remains off if the data are 0. When BLANK is high, all outputs are forced off, but the data in the latch do not change as long as LAT does not latch in new data. When the MSB of the common shift register is set to 0, the lower 48 bits are written to the output on or off data latch on the LAT rising edge. When the device is powered on, all bits in the data latch are set to 0. The output on or off data latch bit assignment is shown in Table 5. See Figure 35 for an output on or off data write timing diagram.

| BIT<br>NUMBER | BIT NAME | CONTROL<br>LED<br>CHANNEL | DESCRIPTION                          | BIT<br>NUMBER | BIT NAME | CONTROL<br>LED<br>CHANNEL | DESCRIPTION                          |

|---------------|----------|---------------------------|--------------------------------------|---------------|----------|---------------------------|--------------------------------------|

| 0             | OUTR0ON  | OUTR0                     |                                      | 24            | OUTR8ON  | OUTR8                     |                                      |

| 1             | OUTG0ON  | OUTG0                     |                                      | 25            | OUTG8ON  | OUTG8                     |                                      |

| 2             | OUTB0ON  | OUTB0                     |                                      | 26            | OUTB8ON  | OUTB8                     |                                      |

| 3             | OUTR1ON  | OUTR1                     |                                      | 27            | OUTR9ON  | OUTR9                     |                                      |

| 4             | OUTG10N  | OUTG1                     |                                      | 28            | OUTG9ON  | OUTG9                     |                                      |

| 5             | OUTB1ON  | OUTB1                     | -                                    | 29            | OUTB9ON  | OUTB9                     |                                      |

| 6             | OUTR2ON  | OUTR2                     |                                      | 30            | OUTR10ON | OUTR10                    |                                      |

| 7             | OUTG2ON  | OUTG2                     | -                                    | 31            | OUTG10ON | OUTG10                    |                                      |

| 8             | OUTB2ON  | OUTB2                     |                                      | 32            | OUTB10ON | OUTB10                    |                                      |

| 9             | OUTR3ON  | OUTR3                     |                                      | 33            | OUTR11ON | OUTR11                    |                                      |

| 10            | OUTG3ON  | OUTG3                     | 0 = Output off<br>1 = Output on with | 34            | OUTG110N | OUTG11                    | 0 = Output off<br>1 = Output on with |

| 11            | OUTB3ON  | OUTB3                     | BLANK low.                           | 35            | OUTB11ON | OUTB11                    | BLANK low.                           |

| 12            | OUTR4ON  | OUTR4                     | When the device is                   | 36            | OUTR12ON | OUTR12                    | When the device is                   |

| 13            | OUTG4ON  | OUTG4                     | powered on, all bits are set to 0.   | 37            | OUTG12ON | OUTG12                    | powered on, all bits are set to 0.   |

| 14            | OUTB4ON  | OUTB4                     |                                      | 38            | OUTB12ON | OUTB12                    |                                      |

| 15            | OUTR5ON  | OUTR5                     |                                      | 39            | OUTR13ON | OUTR13                    |                                      |

| 16            | OUTG5ON  | OUTG5                     |                                      | 40            | OUTG13ON | OUTG13                    |                                      |

| 17            | OUTB5ON  | OUTB5                     |                                      | 41            | OUTB13ON | OUTB13                    |                                      |

| 18            | OUTR6ON  | OUTR6                     |                                      | 42            | OUTR14ON | OUTR14                    |                                      |

| 19            | OUTG6ON  | OUTG6                     | -                                    | 43            | OUTG14ON | OUTG14                    |                                      |

| 20            | OUTB6ON  | OUTB6                     |                                      | 44            | OUTB14ON | OUTB14                    |                                      |

| 21            | OUTR7ON  | OUTR7                     |                                      | 45            | OUTR15ON | OUTR15                    |                                      |

| 22            | OUTG7ON  | OUTG7                     |                                      | 46            | OUTG15ON | OUTG15                    |                                      |

| 23            | OUTB7ON  | OUTB7                     |                                      | 47            | OUTB15ON | OUTB15                    |                                      |

Table 5. On or Off Control Data Latch Bit Assignment

| BIT<br>NUMBER | BIT<br>NAME | DEFAULT<br>VALUE<br>(BINARY) | DESCRIPTION                                                                                                                                                                                                                 |

|---------------|-------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2:0]         | MAXCUR (MC) | 000b                         | Maximum current control (MC) data for all $OUTXn$<br>(data = 0h to 7h, see Table 2)                                                                                                                                         |

| [9:3]         | BCR (BC)    | _                            | Global brightness control (BC) data for RED color group<br>(data = 00h to 7Fh, see Table 3)                                                                                                                                 |

| [16:10]       | BCG (BC)    | _                            | Global brightness control (BC) data for GREEN color group<br>(data = 00h to 7Fh, see Table 3)                                                                                                                               |

| [23:17]       | BCB (BC)    | _                            | Global brightness control (BC) data for BLUE color group<br>(data = 00h to 7Fh, see Table 3)                                                                                                                                |

| [25:24]       | SIDLD (FC)  | _                            | SID load control. These two bits select the SID loaded to the common register when the LAT rising edge is input for on or off data writes. Table 7 shows the selected data truth table.                                     |

| [28:26]       | LODVLT (FC) | _                            | LOD detection voltage select. These three bits select the detection threshold voltage for the LED open detection (LOD). Table 8 shows the detect voltage truth table.                                                       |

| [30:29]       | LSDVLT (FC) | _                            | LSD detection voltage select. These two bits select the detection threshold voltage for the LED short detection (LSD). Table 9 shows the detect voltage truth table.                                                        |

| [32:31]       | PSMODE (FC) | 11b                          | Power-save mode select. These two bits select the power-save mode between the four modes. Table 10 shows the power-save mode truth table. Figure 32 and Figure 33 illustrate the power-save mode operation timing diagrams. |

| [39:33]       | RSV         | _                            | Reserved data, don't care.                                                                                                                                                                                                  |

| [47:40]       | WRTCMD      | —                            | Write command. When this data are 96h (10010110b), MC, BC, and FC data can be updated. In order to update MC data, the same data must be written twice to the MC bit.                                                       |

#### Table 7. SID Load Control Truth Table

| SIE    | DLD    | STATUS INFORMATION DATA (SID) LOADED TO THE COMMON SHIFT |  |  |

|--------|--------|----------------------------------------------------------|--|--|

| BIT 25 | BIT 24 | REGISTER                                                 |  |  |

| 0      | 0      | No data are loaded (default value)                       |  |  |

| 0      | 1      | LED open detection (LOD) data are loaded                 |  |  |

| 1      | 0      | LED short detection (LSD) data are loaded                |  |  |

| 1      | 1      | No data are loaded                                       |  |  |

## Table 8. LOD Threshold Voltage Truth Table

|        | LODVLT |        |                                            |

|--------|--------|--------|--------------------------------------------|

| BIT 28 | BIT 27 | BIT 26 | LED OPEN DETECTION (LOD) THRESHOLD VOLTAGE |

| 0      | 0      | 0      | VLOD0 (0.20 V, typ)                        |

| 0      | 0      | 1      | VLOD1 (0.30 V, typ)                        |

| 0      | 1      | 0      | VLOD2 (0.40 V, typ)                        |

| 0      | 1      | 1      | VLOD3 (0.50 V, typ)                        |

| 1      | 0      | 0      | VLOD4 (0.60 V, typ)                        |

| 1      | 0      | 1      | VLOD1 (0.30 V, typ)                        |

| 1      | 1      | 0      | VLOD1 (0.30 V, typ)                        |

| 1      | 1      | 1      | VLOD1 (0.30 V ,typ)                        |

#### Table 9. LSD Threshold Voltage Truth Table

| LSD    | VLT    |                                             |

|--------|--------|---------------------------------------------|

| BIT 30 | BIT 29 | LED SHORT DETECTION (LSD) THRESHOLD VOLTAGE |

| 0      | 0      | VLSD0 (0.50 × VCC, typ)                     |

| 0      | 1      | VLSD1 (0.70 × VCC, typ)                     |

| 1      | 0      | VLSD2 (0.90 × VCC, typ)                     |

| 1      | 1      | VLSD2 (0.90 × VCC, typ)                     |

#### Table 10. Power-Save Mode Truth Table

| PSM           | ODE         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BIT 32 BIT 31 |             | POWER-SAVE MODE FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 0             | 0           | Power-save mode is disabled in every condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 0             | 1           | When all zeroes (0s) are written to the output on or off data latch, the device goes to power-save mode. When an SCLK rising edge occurs, the device goes to normal operation and starts to control the output current. However, after the setup time ( $t_{SU2}$ ) elapses from the SCLK input timing, BLANK must go low. Otherwise, the output current may not reach the set constant-current value. If these two bits are set to 01b from 10b or 11b when the device is in power-save mode (PSM), the device remains in PSM and does not resume normal mode. When an SCLK rising edge is input after PSMODE = 01 is selected, the device returns to normal mode.                                                               |  |  |  |  |  |